### SN74ACT7203L, SN74ACT7204L, SN74ACT7205L, SN74ACT7206L $2048 \times 9$ , $4096 \times 9$ , $8192 \times 9$ , $16384 \times 9$ ASYNCHRONOUS FIRST-IN. FIRST-OUT MEMORIES

SCAS226A - FEBRUARY 1993 - REVISED SEPTEMBER 1995

- Reads and Writes Can Be Asynchronous or Coincident

- Organization:

- SN74ACT7203L 2048 × 9

- SN74ACT7204L 4096 × 9

- SN74ACT7205L 8192 × 9

- SN74ACT7206L 16383 × 9

- Fast Data Access Times of 15 ns

- Read and Write Frequencies up to 40 MHz

- Bit-Width and Word-Depth Expansion

- Fully Compatible With the IDT7203/7204

- Retransmit Capability

- Empty, Full, and Half-Full Flags

- TTL-Compatible Inputs

- Available in 28-Pin Plastic DIP (NP), Plastic Small-Outline (DV), and 32-Pin Plastic J-Leaded Chip-Carrier (RJ) Packages

### description

These devices are constructed with dual-port SRAM and have internal write and read address. counters to provide data throughput on a first-in, first-out (FIFO) basis. Write and read operations are independent and can be asynchronous or coincident. Empty and full status flags prevent underflow and overflow of memory, and depth-expansion logic allows combining the storage cells of two or more devices into one FIFO. Word-width expansion is also possible.

Data is loaded into memory by the write-enable  $(\overline{W})$  input and unloaded by the read-enable  $(\overline{R})$ input. Read and write cycle times of 25 ns (40 MHz) are possible with data access times of 15 ns.

NC - No internal connection

These devices are particularly suited for providing a data channel between two buses operating at asynchronous rates. Applications include use as rate buffers from analog-to-digital converters in data-acquisition systems, temporary storage elements between buses and magnetic or optical memories, and queues for communication systems. A 9-bit-wide data path is provided for the transmission of byte data plus a parity bit or packet-framing information. The read pointer can be reset independently of the write pointer for retransmitting previously read data when a device is not used in depth expansion.

The SN74ACT7203L, SN74ACT7204L, SN74ACT7205L, and SN74ACT7206L are characterized for operation from 0°C to 70°C.

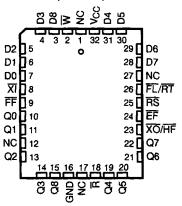

### SN74ACT7203L logic symbol<sup>†</sup>

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for the DV and NP packages.

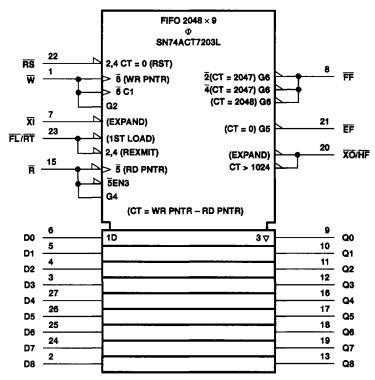

### SN74ACT7204L logic symbol<sup>†</sup>

$<sup>^\</sup>dagger$  This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for the DV and NP packages.

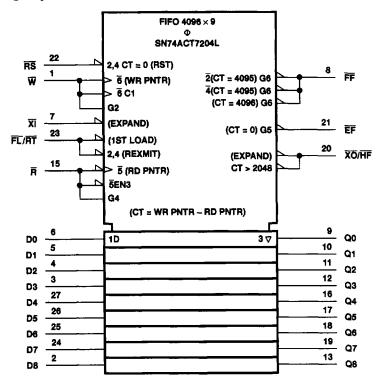

### SN74ACT7205L logic symbol<sup>†</sup>

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for the DV and NP packages.

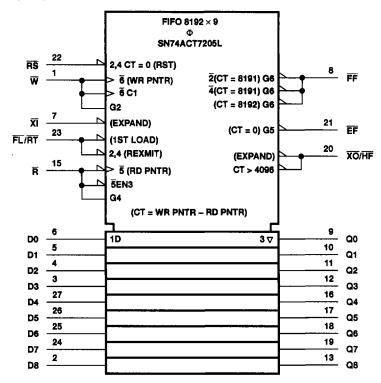

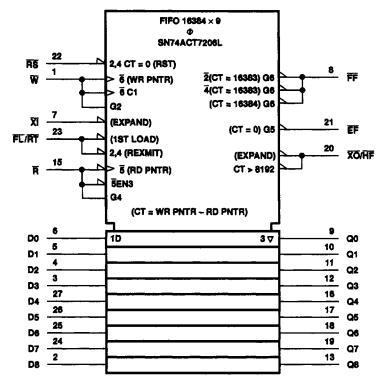

### SN74ACT7206L logic symbol<sup>†</sup>

<sup>&</sup>lt;sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for the DV and NP packages.

# SN74ACT7203L, SN74ACT7204L, SN74ACT7205L, SN74ACT7206L 2048 $\times$ 9, 4096 $\times$ 9, 8192 $\times$ 9, 16384 $\times$ 9 ASYNCHRONOUS FIRST-IN, FIRST-OUT MEMORIES SCAS226A - FEBRUARY 1993 - REVISED SEPTEMBER 1996

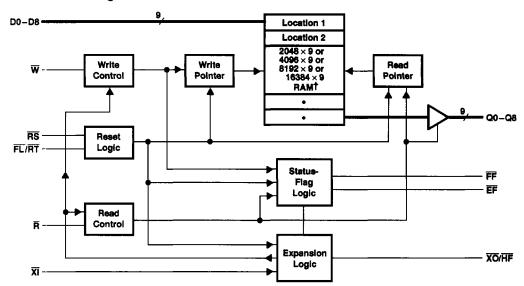

### functional block diagram

<sup>†2048 × 9</sup> for SN74ACT7203L; 4096 × 9 for SN74ACT7204L; 8192 × 9 for SN74ACT7205L; 16384 × 9 for SN74ACT7206L

### RESET AND RETRANSMIT FUNCTION TABLE (single-device depth; single-or multiple-device width)

|    | INPUTS |    | INTERNAL TO DEVICE   |                      | OUTPUTS |    |       | FINATION     |

|----|--------|----|----------------------|----------------------|---------|----|-------|--------------|

| RS | FL/RT  | Χi | READ POINTER         | WRITE POINTER        | EF      | FF | XO/HF | FUNCTION     |

| L. | X      | L  | Location zero        | Location zero        | L       | Н  | Н     | Reset device |

| Н  | L      | L  | Location zero        | Unchanged            | Х       | Х  | X     | Retransmit   |

| Н  | Н      | L  | Increment if EF high | Increment if FF high | Х       | X  | х     | Read/write   |

### **RESET AND FIRST-LOAD FUNCTION TABLE** (multiple-device depth; single-or multiple-device width)

|    | INPUTS |    | INTERNAL      | OUT           | PUTS | EUNATION. |                         |

|----|--------|----|---------------|---------------|------|-----------|-------------------------|

| RS | FLAT   | ΧI | READ POINTER  | WRITE POINTER | EF   | FF        | FUNCTION                |

| L  | L      | ‡  | Location zero | Location zero | L    | Н         | Reset first device      |

| L. | н      | ‡  | Location zero | Location zero | L    | Н         | Reset all other devices |

| Н  | X      | #  | x             | x             | X    | X         | Read/write              |

<sup>‡</sup>XI is connected to XO/HF of the previous device in the daisy chain (see Figure 15).

# SN74ACT7203L, SN74ACT7204L, SN74ACT7205L, SN74ACT7206L 2048 × 9, 4096 × 9, 8192 × 9, 16384 × 9 ASYNCHRONOUS FIRST-IN, FIRST-OUT MEMORIES SCAS226A - FEBRUARY 1993 - REVISED SEPTEMBER 1995

### **Terminal Functions**

| TERMINAL NAME | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D8         | ı   | Data inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ĒF            | 0   | Empty-flag output. $\overline{EF}$ is low when the read pointer is equal to the write pointer, inhibiting any operation initiated by a read cycle. When the FIFO is empty, a data word can be read automatically at Q0 – Q8 by holding $\overline{R}$ low when loading the data word with a low-level pulse on $\overline{W}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FF            | 0   | Full-flag output. FF is low when the write pointer is one location less than the read pointer, indicating that the device is full and inhibiting any operation initiated by a write cycle. FF goes low when the number of writes after reset exceeds the number of reads by 2048 for the SN74ACT7203L, 4096 for the SN74ACT7204L, 8192 for the SN74ACT7205L, and 16384 for the SN74ACT7206L. When the FIFO is full, a data word can be written automatically into memory by holding $\overline{W}$ low while reading out another data word with a low-level pulse on $\overline{R}$ .                                                                                                                                                                                     |

|               |     | First-load/retransmit input. FL/RT performs two separate functions. When cascading two or more devices for word-depth expansion, FL/RT is tied to ground on the first device in the daisy chain to indicate that it is the first device loaded and unloaded; it is tied high on all other devices in the depth-expansion chain.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FC/RT         | 1   | A device is not used in depth expansion when its expansion-in $(\overline{X})$ input is tied to ground. In that case, $\overline{FL/RT}$ acts as a retransmit enable. A retransmit operation is initiated when $\overline{FL/RT}$ is pulsed low. This sets the internal read pointer to the first location and does not affect the write pointer. $\overline{R}$ and $\overline{W}$ must be at a high logic level during the low-level $\overline{FL/RT}$ retransmit pulse. Retransmit should be used only when less than 2048/4096 writes are performed between resets; otherwise, an attempt to retransmit can cause the loss of unread data. The retransmit function can affect $\overline{XO/HF}$ depending on the relative locations of the read and write pointers. |

| GND           |     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Q0-Q8         | 0   | Data outputs. Q0 – Q8 are in the high-impedance state when $\overline{R}$ is high or the FIFO is empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Ā             |     | Read-enable input. A read cycle begins on the falling edge of $\overline{R}$ if $\overline{EF}$ is high. This activates Q0-Q8 and shifts the next data value to this bus. The data outputs return to the high-impedance state as $\overline{R}$ goes high. As the last stored word is read by the falling edge of $\overline{R}$ , $\overline{EF}$ transitions low but Q0-Q8 remain active until $\overline{R}$ returns high. When the FIFO is empty, the internal read pointer is unchanged by a pulse on $\overline{R}$ .                                                                                                                                                                                                                                               |

| RS            |     | Reset input. A reset is performed by taking $\overline{RS}$ low. This initializes the internal read and write pointers to the first location and sets $\overline{EF}$ low, $\overline{FF}$ high, and $\overline{HF}$ high. Both $\overline{R}$ and $\overline{W}$ must be held high for a reset during the window shown in Figure 7. A reset is required after power up before a write operation can take place.                                                                                                                                                                                                                                                                                                                                                          |

| Vcc           |     | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| W             | ı   | Write-enable input. A write cycle begins on the falling edge of $\overline{W}$ if $\overline{FF}$ is high. The value on D0 – D8 is stored in memory as $\overline{W}$ returns high. When the FIFO is full, $\overline{FF}$ is low inhibiting $\overline{W}$ from performing any operation on the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

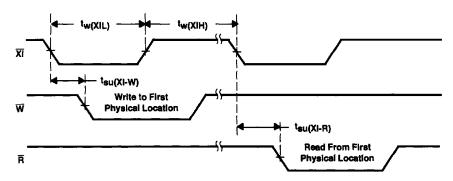

| ΧÌ            | i   | Expansion-in Input. $\overline{XI}$ performs two functions. $\overline{XI}$ is tied to ground to indicate that the device is not used in depth expansion. When the device is used in depth expansion, $\overline{XI}$ is connected to the expansion-out ( $\overline{XO}$ ) output of the previous device in the depth-expansion chain.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

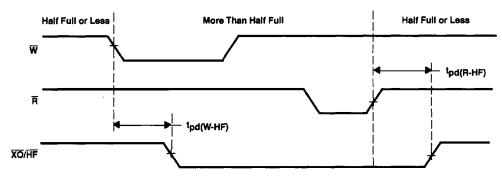

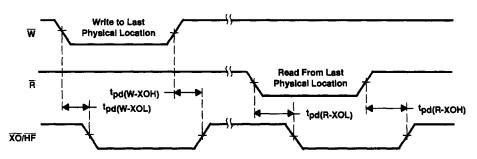

| XO/HF         | 0   | Expansion-out/half-full-flag output. $\overline{XO/HF}$ performs two functions. When the device is not used in depth expansion (i.e., when $\overline{XI}$ is tied to ground), $\overline{XO/HF}$ indicates when half the memory locations are filled. After half of the memory is filled, the falling edge on $\overline{W}$ for the next write operation drives $\overline{XO/HF}$ low. $\overline{XO/HF}$ remains low until a rising edge of $\overline{R}$ reduces the number of words stored to exactly half of the total memory.                                                                                                                                                                                                                                    |

|               |     | When the device is used in depth expansion, $\overline{XO/HF}$ is connected to $\overline{XI}$ of the next device in the daisy chain. $\overline{XO/HF}$ drives the daisy chain by sending a pulse to the next device when the previous device reaches the last memory location.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## SN74ACT7203L, SN74ACT7204L, SN74ACT7205L, SN74ACT7206L 2048 $\times$ 9, 4096 $\times$ 9, 8192 $\times$ 9, 16384 $\times$ 9 ASYNCHRONOUS FIRST-IN, FIRST-OUT MEMORIES

SCAS226A - FEBRUARY 1993 - REVISED SEPTEMBER 1995

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)   |              |

|------------------------------------------------------|--------------|

| Input voltage range (any input), V <sub>1</sub>      | 0.5 V to 7 V |

| Continuous output current, IO                        | 50 mA        |

| Voltage applied to a disabled 3-state output         |              |

| Operating free-air temperature range, T <sub>A</sub> | 0°C to 70°C  |

| Storage temperature range, T <sub>sto</sub>          |              |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to GND.

### recommended operating conditions

|       |                                |              | MIN | NOM | MAX | UNIT |

|-------|--------------------------------|--------------|-----|-----|-----|------|

| Vcc   | Supply voltage                 |              | 4.5 | 5   | 5.5 | V    |

| VIH   | High lavel inner a colored     | XI           | 2.6 |     |     | .,   |

|       | High-level input voltage       | Other inputs | 2   |     |     | ٧    |

| VIL   | Low-level input voltage        |              |     |     | 8.0 | ν    |

| ЮН    | High-level output current      |              |     |     | -2  | _mA  |

| loL   | Low-level output current       |              |     |     | 8   | mA   |

| $T_A$ | Cperating free-air temperature |              | 0   |     | 70  | ပံ့  |

### electrical characteristics over recommended operating free-air temperature range, $V_{CC}$ = 5.5 V (unless otherwise noted)

| PARAMETER         |                                          | TEST CONDITIO           | ONS       | MIN | MAX | UNIT |

|-------------------|------------------------------------------|-------------------------|-----------|-----|-----|------|

| VOH               | $V_{CC} = 4.5 \text{ V},$                | I <sub>OH</sub> = −2 mA |           | 2.4 |     | ٧    |

| VOL               | V <sub>CC</sub> = 4.5 V,                 | i <sub>OL</sub> = 8 mA  |           |     | 0.4 | V    |

| lozн              | Vo = Vcc,                                | ਸ≥V <sub>IH</sub>       |           |     | ±10 | μА   |

| lozi.             | V <sub>O</sub> = 0.4 V,                  | R≥VIH                   |           |     | ±10 | μА   |

| ΙĮ                | V <sub>I</sub> = 0 to 5.5 V              |                         |           | -1  | 1   | μА   |

| ICC1 <sup>‡</sup> | f <sub>clock</sub> = 20 MHz              |                         |           |     | 120 | mA   |

| lcc2 <sup>‡</sup> | R, W, RS, and FL/RT                      | at V <sub>IH</sub>      |           |     | 12  | mA   |

| 1003 <sup>‡</sup> | V <sub>I</sub> = V <sub>CC</sub> - 0.2 V |                         |           | ,   | 2   | mA   |

| C <sub>i</sub> §  | V <sub>I</sub> = 0,                      | T <sub>A</sub> = 25°C,  | f = 1 MHz |     | 10  | pF   |

| C <sub>o</sub> §  | V <sub>O</sub> = 0,                      | T <sub>A</sub> = 25°C,  | f = 1 MHz |     | 10  | pF   |

<sup>‡</sup> I<sub>CC1</sub> = supply current; I<sub>CC2</sub> = standby current; I<sub>CC3</sub> = power-down current. I<sub>CC</sub> measurements are made with outputs open (only capacitive loading).

<sup>§</sup> This parameter is sampled and not 100% tested.

### SN74ACT7203L, SN74ACT7204L, SN74ACT7205L, SN74ACT7206L 2048 × 9, 4096 × 9, 8192 × 9, 16384 × 9 ASYNCHRONOUS FIRST-IN, FIRST-OUT MEMORIES SCAS226A - FEBRUARY 1993 - REVISED SEPTEMBER 1995

## timing requirements over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                       |                                                                   | FIGURE  | ACT7203L-15<br>ACT7204L-15<br>ACT7205L-15<br>ACT7206L-15<br>MIN MAX | 'ACT7203L-25<br>'ACT7204L-25<br>'ACT7205L-25<br>'ACT7206L-25<br>MIN MAX | 'ACT7203L-50<br>'ACT7204L-50<br>'ACT7205L-50<br>'ACT7206L-50<br>MIN MAX | UNIT |

|-----------------------|-------------------------------------------------------------------|---------|---------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|------|

| fclock                | Clock frequency, $\widehat{\mathbf{R}}$ or $\widehat{\mathbf{W}}$ | 1       | 40                                                                  | 28.5                                                                    | 15                                                                      | MHz  |

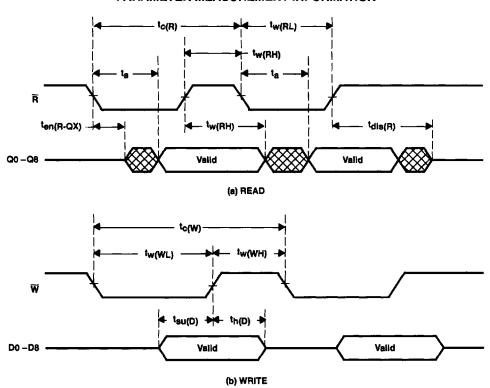

| tc(R)                 | Cycle time, read                                                  | 1(a)    | 25                                                                  | 35                                                                      | 65                                                                      | ns   |

| t <sub>C</sub> (W)    | Cycle time, write                                                 | 1(b)    | 25                                                                  | 35                                                                      | 65                                                                      | ns   |

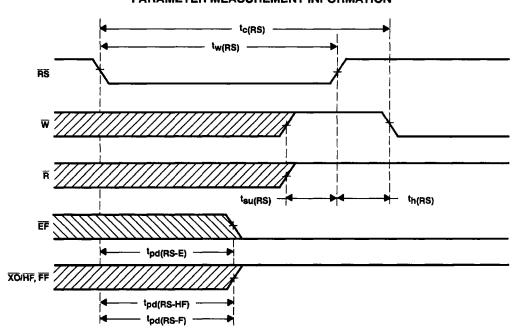

| tc(RS)                | Cycle time, reset                                                 | 7       | 25                                                                  | 35                                                                      | 65                                                                      | ns   |

| <sup>t</sup> c(RT)    | Cycle time, retransmit                                            | 4       | 25                                                                  | 35                                                                      | 65                                                                      | ns   |

| tw(RL)                | Pulse duration, R low                                             | 1(a)    | 15                                                                  | 25                                                                      | 50                                                                      | ns   |

| tw(WL)                | Pulse duration, W low                                             | 1(b)    | 15                                                                  | 25                                                                      | 50                                                                      | ns   |

| tw(RH)                | Pulse duration, R high                                            | 1(a)    | 10                                                                  | 10                                                                      | 15                                                                      | ns   |

| tw(WH)                | Pulse duration, W high                                            | 1(b)    | 10                                                                  | 10                                                                      | 15                                                                      | ns   |

| tw(RT)                | Pulse duration, FL/RT low                                         | 4       | 15                                                                  | 25                                                                      | 50                                                                      | ns   |

| tw(RS)                | Pulse duration, RS low                                            | 7       | 15                                                                  | 25                                                                      | 50                                                                      | ns   |

| tw(XIL)               | Pulse duration, XI low                                            | 10      | 15                                                                  | 25                                                                      | 50                                                                      | ns   |

| tw(XIH)               | Pulse duration, XI high                                           | 10      | 10                                                                  | 10                                                                      | 10                                                                      | ns   |

| tsu(D)                | Setup time, data before W↑                                        | 1(b), 6 | 11                                                                  | 15                                                                      | 30                                                                      | ns   |

| t <sub>Su(RT)</sub>   | Setup time, R and W high before FL/RT↑↑                           | 4       | 15                                                                  | 25                                                                      | 50                                                                      | ns   |

| tsu(RS)               | Setup time, R and W high before RS↑↑                              | 7       | 15                                                                  | 25                                                                      | 50                                                                      | ns   |

| t <sub>su(XI-R)</sub> | Setup time, XI low before R↓                                      | 10      | 10                                                                  | 10                                                                      | 15                                                                      | ns   |

| tsu(XI-W)             | Setup time, XI low before W↓                                      | 10      | 10                                                                  | 10                                                                      | 15                                                                      | ns   |

| th(D)                 | Hold time, data after W↑                                          | 1(b), 6 | 0                                                                   | 0                                                                       | 5                                                                       | ns   |

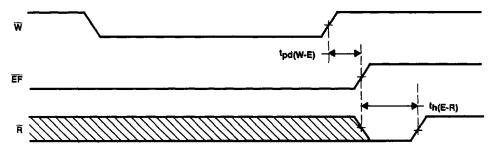

| th(E-R)               | Hold time, R low after EF↑                                        | 5, 11   | 15                                                                  | 25                                                                      | 50                                                                      | ns   |

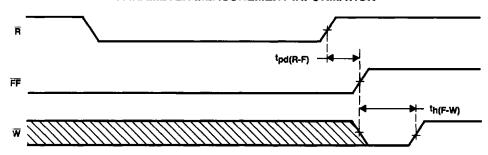

| <sup>f</sup> h(F-W)   | Hold time, W low after FF1                                        | 6, 12   | 15                                                                  | 25                                                                      | 50                                                                      | ns   |

| ¹a(RT)                | Hold time, R and W high after FL/RT↑                              | 4       | 10                                                                  | 10                                                                      | 15                                                                      | ns   |

| tn(RS)                | Hold time, R and W high after RS↑                                 | 7       | 10                                                                  | 10                                                                      | 15                                                                      | ns   |

<sup>†</sup> These values are characterized but not currently tested.

## SN74ACT7203L, SN74ACT7204L, SN74ACT7205L, SN74ACT7206L 2048 $\times$ 9, 4096 $\times$ 9, 8192 $\times$ 9, 16384 $\times$ 9 ASYNCHRONOUS FIRST-IN, FIRST-OUT MEMORIES SCAS226A - FEBRUARY 1993 - REVISED SEPTEMBER 1995

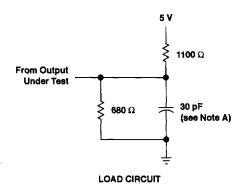

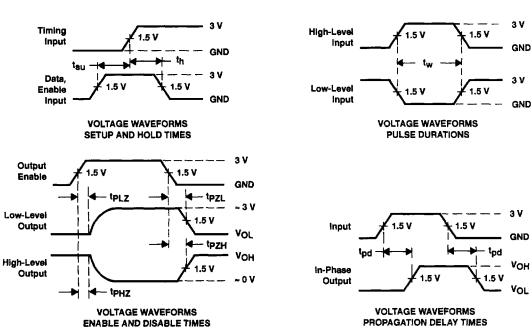

### switching characteristics over recommended ranges of supply voltage and operating free-air temperature (see Figure 13)

|                        | PARAMETER                                                                                                        |            | 'ACT7203L-15<br>'ACT7204L-15<br>'ACT7205L-15<br>'ACT7206L-15 |     | 'ACT7203L-25<br>'ACT7204L-25<br>'ACT7205L-25<br>'ACT7206L-25 |     | 'ACT72 'ACT72 'ACT72 'ACT72 | UNIT |    |

|------------------------|------------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------|-----|--------------------------------------------------------------|-----|-----------------------------|------|----|

|                        |                                                                                                                  |            | MIN                                                          | MAX | MIN                                                          | MAX | MIN                         | MAX  |    |

| t <sub>a</sub>         | Access time, R                                                                                                   | 1(a), 3, 5 |                                                              | 15  |                                                              | 25  |                             | 50   | ns |

| t <sub>V</sub> (RH)    | Valid time, data out valid after R↑                                                                              | 1(a)       | 5                                                            |     | 5                                                            |     | 5                           |      | ns |

| ten(R-QX)              | Enable time, R↓ to Q outputs at low impedance†                                                                   | 1(a)       | 5                                                            |     | 5                                                            |     | 10                          |      | ns |

| ten(W-QX)              | Enable time, W↑ to Q outputs at low impedance†‡                                                                  | 5          | 5                                                            |     | 5                                                            |     | 15                          |      | ns |

| <sup>†</sup> dis(R)    | Disable time, R↑ to Q outputs at high impedance t                                                                | 1(a)       |                                                              | 15  |                                                              | 18  |                             | 30   | ns |

| <sup>t</sup> w(FH)     | Pulse duration, FF high in automatic-write mode                                                                  | 6          |                                                              | 15  |                                                              | 25  |                             | 45   | ns |

| <sup>t</sup> w(EH)     | Pulse duration, EF high in automatic-read mode                                                                   | 5          |                                                              | 15  |                                                              | 25  |                             | 45   | ns |

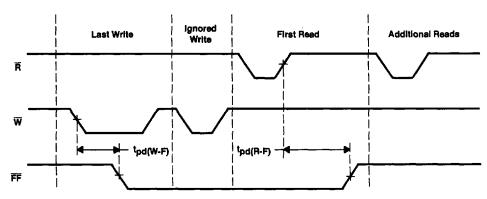

| <sup>t</sup> pd(W-F)   | Propagation delay time, W↓ to FF low                                                                             | 2          |                                                              | 15  |                                                              | 25  |                             | 45   | ns |

| tpd(R-F)               | Propagation delay time, R1 to FF high                                                                            | 2, 6, 12   |                                                              | 15  |                                                              | 25  |                             | 45   | ns |

| tpd(RS-F)              | Propagation delay time, RS↓ to FF high                                                                           | 7          |                                                              | 25  |                                                              | 35  |                             | 65   | ns |

| <sup>t</sup> pd(RS-HF) | Propagation delay time, RS↓ to XO/HF high                                                                        | 7          |                                                              | 25  |                                                              | 35  |                             | 65   | ns |

| <sup>†</sup> pd(W-E)   | Propagation delay time, W to EF high                                                                             | 3, 5, 11   |                                                              | 15  |                                                              | 25  |                             | 45   | ns |

| tpd(R-E)               | Propagation delay time, R↓ to EF low                                                                             | 3          |                                                              | 15  |                                                              | 25  |                             | 45   | ns |

| <sup>t</sup> pd(RS-E)  | Propagation delay time, RS↓ to EF low                                                                            | 7          |                                                              | 25  |                                                              | 35  |                             | 65   | ns |

| t <sub>pd</sub> (W-HF) | Propagation delay time, W↓ to XO/HF low                                                                          | 8          |                                                              | 25  |                                                              | 35  |                             | 65   | ns |

| <sup>t</sup> pd(R-HF)  | Propagation delay time, R↑ to XO/HF high                                                                         | 8          |                                                              | 25  |                                                              | 35  |                             | 65   | ns |

| <sup>t</sup> pd(R-XOL) | Propagation delay time, $\overline{\mathbf{R}}\downarrow$ to $\overline{\mathbf{XO}}/\overline{\mathbf{HF}}$ low | 9          |                                                              | 15  |                                                              | 25  | !                           | 50   | ns |

| <sup>t</sup> pd(W-XOL) | Propagation delay time, W↓ to XO/HF low                                                                          | 9          |                                                              | 15  |                                                              | 25  |                             | 50   | ns |

| <sup>t</sup> pd(R-XOH) | Propagation delay time, R↑ to XO/HF high                                                                         | 9          |                                                              | 15  |                                                              | 25  |                             | 50   | ns |

| <sup>t</sup> pd(W-XOH) | Propagation delay time, $\overline{W}\uparrow$ to $\overline{XO}/\overline{HF}$ high                             | 9          |                                                              | 15  |                                                              | 25  |                             | 50   | ns |

| <sup>t</sup> pd(RT-FL) | Propagation delay time,<br>FL/RT↓ to HF, EF, FF valid                                                            | 4          |                                                              | 25  |                                                              | 35  |                             | 65   | ns |

<sup>†</sup> These values are characterized but not currently tested.

<sup>‡</sup> Only applies when data is automatically read

Figure 1. Asynchronous Waveforms

Figure 2. Full-Flag Waveforms

SCAS226A - FEBRUARY 1993 - REVISED SEPTEMBER 1996

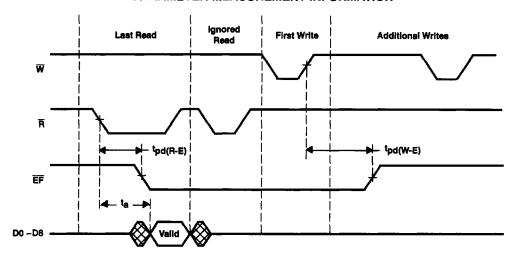

Figure 3. Empty-Flag Waveforms

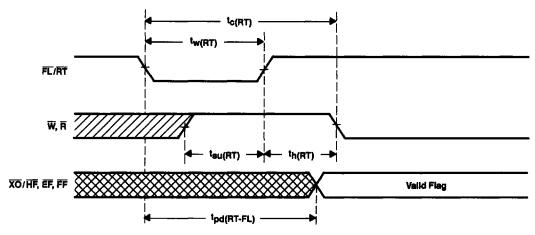

NOTE A: The EF, FF, and XO/HF status flags are valid after completion of the retransmit cycle.

Figure 4. Retransmit Waveforms

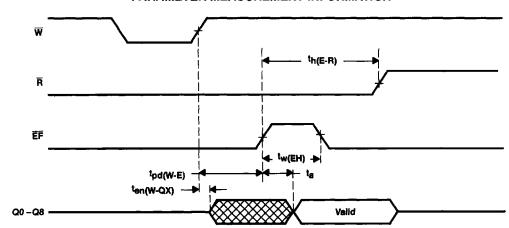

Figure 5. Automatic-Read Waveforms

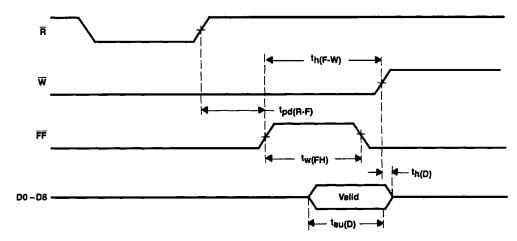

Figure 6. Automatic-Write Waveforms

SCAS226A - FEBRUARY 1993 - REVISED SEPTEMBER 1995

Figure 7. Master-Reset Waveforms

Figure 8. Half-Full Flag Waveforms

Figure 9. Expansion-Out Waveforms

Figure 10. Expansion-in Waveforms

Figure 11. Minimum Timing for an Empty-Flag Coincident-Read Pulse

Figure 12. Minimum Timing for a Full-Flag Coincident-Write Pulse

NOTE A: Includes probe and jig capacitance

Figure 13. Load Circuit and Voltage Waveforms

## SN74ACT7203L, SN74ACT7204L, SN74ACT7205L, SN74ACT7206L 2048 $\times$ 9, 4096 $\times$ 9, 8192 $\times$ 9, 16384 $\times$ 9 ASYNCHRONOUS FIRST-IN, FIRST-OUT MEMORIES SCAS220A - FEBRUARY 1993 - REVISED SEPTEMBER 1996

#### APPLICATION INFORMATION

Combining two or more devices to create one FIFO with a greater number of memory bits is accomplished in two different ways. Width expansion increases the number of bits in each word by connecting FIFOs with the same depth in parallel. Depth expansion uses the built-in expansion logic to daisy-chain two or more devices for applications requiring more than 2048, 4096, 8192, or 16384 words of storage. Width expansion and depth expansion can be used together.

### width expansion

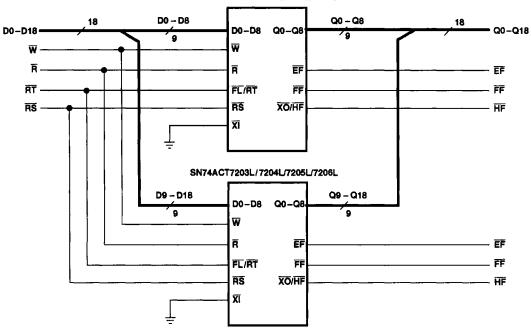

Word-width expansion is achieved by connecting the corresponding input control to multiple devices with the same depth. Status flags ( $\overline{EF}$ ,  $\overline{FF}$ , and  $\overline{HF}$ ) can be monitored from any one device. Figure 14 shows two FIFOs in a width-expansion configuration. Both devices have their expansion-in ( $\overline{XI}$ ) inputs tied to ground. This disables the depth-expansion function of the device, allowing the first-load/retransmit ( $\overline{FL/RT}$ ) input to function as a retransmit ( $\overline{RT}$ ) input and the expansion-out/half-full ( $\overline{XO/HF}$ ) output to function as a half-full ( $\overline{HF}$ ) flag.

### depth expansion

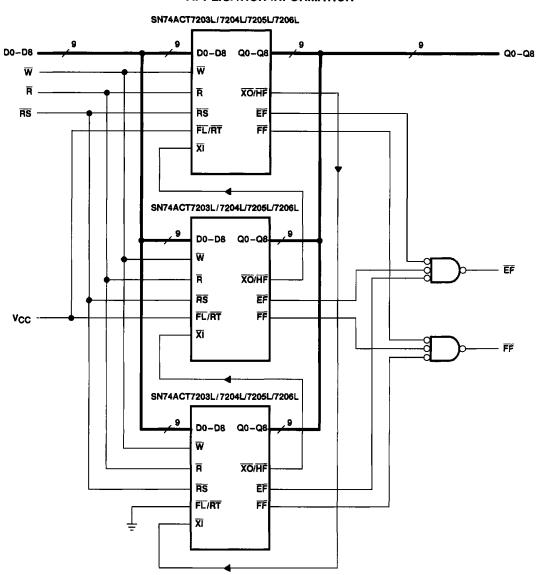

The SN74ACT7203L/7204L/7205L/7206L are easily expanded in depth. Figure 15 shows the connections used to depth expand three SN74ACT7203L/7204L/7205L/7206L devices. Any depth can be attained by adding additional devices to the chain. The SN74ACT7203L/7204L/7205L/7206L operate in depth expansion under the following conditions:

- The first device in the chain is designated by connecting FL to ground.

- All other devices have their FL inputs at a high logic level.

- XO of each device must be connected to XI of the next device.

- External logic is needed to generate a composite FF and EF. All FF outputs must be ORed together, and all EF outputs must be ORed together.

- RT and HF functions are not available in the depth-expanded configuration.

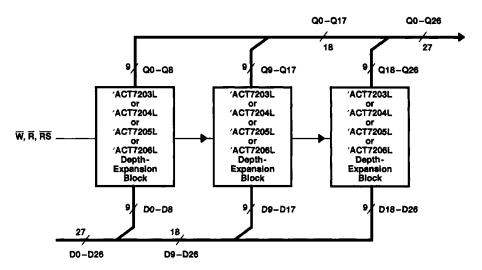

#### combined depth and width expansion

Both expansion techniques can be used together to increase depth and width. This is done by creating depth-expanded units and then connecting them in a width-expanded configuration (see Figure 16).

### **APPLICATION INFORMATION**

### SN74ACT7203L/7204L/7205L/7206L

Figure 14. Word-Width Expansion: 2048/4096 Words × 18 Bits

### **APPLICATION INFORMATION**

Figure 15. Word-Depth Expansion: 6144/12288/24576/49152 Words  $\times$  9 Bits

### **APPLICATION INFORMATION**

Figure 16. Word-Depth Plus Word-Width Expansion