Wired Communications

Never stop thinking.

Edition 2000.09.04

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 5. 9. 00. All Rights Reserved.

### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

ANIC

Analog Network Interface Circuit

PSB 4450 Version 1.2

PSB 4451 Version 1.2

Wired Communications

ANIC Preliminary

Revision History: 2000.09.04 DS8

| Revision F | listory: 2000.09.04                                                                                                                                                                                                                                      | DS8                         |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|

| Previous V | ersion: Data Sheet DS7                                                                                                                                                                                                                                   |                             |  |  |

| Page       | Subjects (major changes since last revision)                                                                                                                                                                                                             |                             |  |  |

| Page 15    | Table "Pin Descriptions PSB 4450" on Page 15: "LINE-" connected to pin 1, "LINE+" connected to pin 2                                                                                                                                                     |                             |  |  |

| Page 17    | Table "Pin Descriptions PSB 4451" on Page 17: t <sub>RESET,min</sub> changed from 500 n to 300 ns, f <sub>DATCLK</sub> min. changed from 256 kHz to 512 kHz                                                                                              |                             |  |  |

| Page 22    | Figure "Voice Path" on Page 22: ANIC-D loop removed                                                                                                                                                                                                      |                             |  |  |

| Page 36    | Chapter "Data Loops" on Page 36: ANIC-D loop remove                                                                                                                                                                                                      | ed, description changes     |  |  |

| Page 51    | Table "Register Overview" on Page 51: register index 0, renamed to ANIC-A_LOOP                                                                                                                                                                           | offset 10: bit 2 CIF_LOOP   |  |  |

| Page 92    | Chapter "RESET (Basic Setting Mode)" on Page 92 : t <sub>RESET,min</sub> changed from 500 ns to 300 ns. Chapter "IDLE Mode" on Page 92: note added                                                                                                       |                             |  |  |

| Page 94    | Chapter "CONVERSATION Mode" on Page 94: descript                                                                                                                                                                                                         | ion added                   |  |  |

| Page 96    | Table "Selectable Values for R" on Page 96: values mo                                                                                                                                                                                                    | odified                     |  |  |

| Page 98    | Table "Ringer Impedance" on Page 98: values modified                                                                                                                                                                                                     |                             |  |  |

| Page 102   | Table "DC Characteristics PSB 4450" on Page 102: conditions for supply curr changed                                                                                                                                                                      |                             |  |  |

| Page 104   | Table "DC Characteristics PSB 4451" on Page 104: condition on 5 V tole added, values and conditions for supply current changed, internal pull-up r ranges added (footnote)                                                                               |                             |  |  |

| Page 106   | Test conditions partially modified                                                                                                                                                                                                                       |                             |  |  |

| Page 122   | Chapter "Input/ Output Waveform for AC Tests" on Page 122: figure and description changes                                                                                                                                                                |                             |  |  |

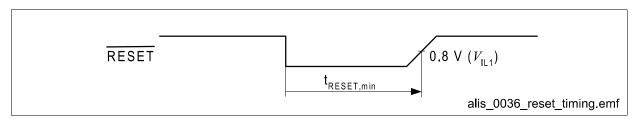

| Page 122   | Chapter "Reset Timing" on Page 122: figure and descrip                                                                                                                                                                                                   | otion changes               |  |  |

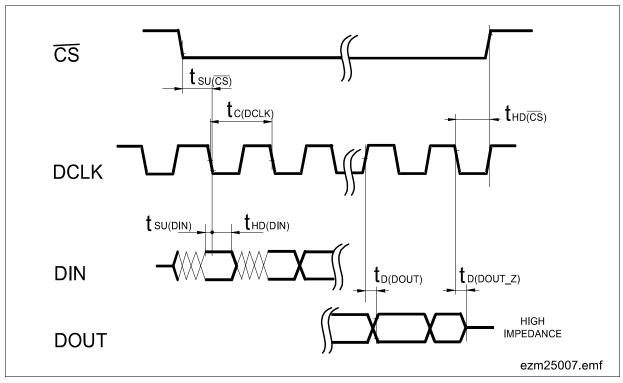

| Page 123   | Figure "Serial Control Interface Timing" on Page 123:                                                                                                                                                                                                    | minor changes               |  |  |

| Page 124   | Table "Serial Control Interface Switching Characteristics" on Page 124: value and description for $t_{D(DOUT\_Z)}$ and other parameters changed, parameter DCLK frequency added, note on pull-up resistor added, sentence about DCLK in header added     |                             |  |  |

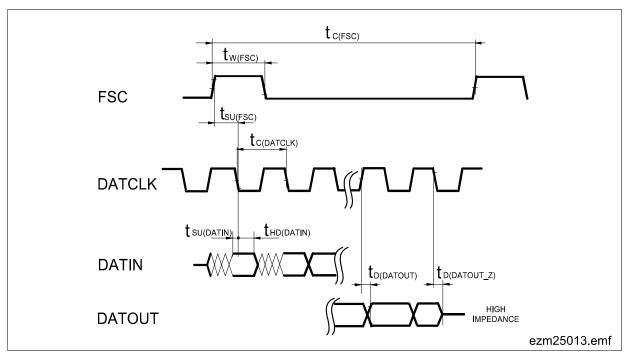

| Page 125   | Figure "PCM Interface Timing" on Page 125: minor cha                                                                                                                                                                                                     | nges, note added            |  |  |

| Page 126   | Table "PCM Interface Switching Characteristics" on P values and description for $t_{SU(DATIN)}$ , $t_{HD(DATIN)}$ and $t_{D(DATIN)}$ note on pull-up resistor added, parameters DATCLK clock frequency added, $t_{SU(FSC)}$ min. changed to $4*T_{MCLK}$ | <sub>TOUT_Z)</sub> changed, |  |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

| Table of                                                                                                | Contents                                                                                                                                                                                                                                                                                                                                      | Page                                            |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| <b>1</b><br>1.1                                                                                         | Overview                                                                                                                                                                                                                                                                                                                                      |                                                 |

| <b>2</b><br>2.1<br>2.2                                                                                  | Pin DescriptionsPin Descriptions PSB 4450Pin Descriptions PSB 4451                                                                                                                                                                                                                                                                            | 15                                              |

| <b>3</b><br>3.1                                                                                         | Typical Applications                                                                                                                                                                                                                                                                                                                          |                                                 |

| 4.1 4.2 4.2.1 4.3 4.3.1 4.3.2 4.3.3 4.4 4.5 4.6 4.7 4.8 4.9 4.9.2 4.9.2.1 4.9.2.2 4.10 4.11 4.11.1 4.12 | Functional Description Functional Block Diagram General Description Impedance Voice Path Receive Path Transmit Path Loops Ring Path DC Measurement Path Tone Detection Metering Ring Detect Interrupt Structure Interrupt-Handling Interrupt Sources Static Interrupts Dynamic Interrupts ANIC Clocking Test Modes Data Loops Support Package | 20 21 21 23 23 23 24 24 25 26 26 27 33 36 36 36 |

| 5<br>5.1<br>5.2<br>5.2.1<br>5.3<br>5.3.1<br>5.3.1.1<br>5.3.1.2<br>5.4                                   | Digital Interfaces Sample Rates PCM Interface PCM Interface Timing Examples Serial Control Interface Programming of ANIC via the Serial Control Interface Example for Write Operation Example for Read Operation Digital Isolation Interface                                                                                                  | 38<br>39<br>43<br>45<br>47<br>48<br>49          |

| 6                                                                                                       | Programming                                                                                                                                                                                                                                                                                                                                   | !                                               |

| Table of                                                                                                           | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page                                                                             |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 6.1<br>6.1.1<br>6.1.2                                                                                              | Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51                                                                               |

| 7 7.1 7.2 7.2.1 7.2.2 7.2.3 7.2.3.1 7.2.4 7.2.5 7.3 7.3.1 7.4                                                      | Operating Modes of ANIC System On-hook RESET (Basic Setting Mode) IDLE Mode RING Mode RING - Automatic State Transitions ON-HOOK CONVERSATION Mode ON-HOOK RECEIVE Mode Off-hook CONVERSATION Mode PULSE COMMAND Mode                                                                                                                                                                                                                              | 91<br>92<br>92<br>92<br>92<br>94<br>94<br>94<br>94                               |

| 8<br>8.1<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.3<br>8.3.1<br>8.4.1<br>8.4.2                                       | Electrical Characteristics Programmable Filters DC Characteristics DC Termination Programming Ranges for DC Termination Line Current in PULSE COMMAND Mode AC Termination Ringer Impedance DC Measurement Ring Detect Levels and Frequencies On-hook and Off-hook Settling Time                                                                                                                                                                    | 95<br>95<br>95<br>96<br>97<br>98<br>98<br>98                                     |

| 9.1<br>9.2<br>9.3<br>9.3.1<br>9.3.2<br>9.4<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.5<br>9.4.6<br>9.4.7 | Electrical Performance Characteristics  Absolute Maximum Ratings  Recommended Operating Conditions  DC Characteristics  PSB 4450  PSB 4451  AC Transmission Characteristics  Absolute Gain Error Off-hook  Absolute Gain Error On-hook  Gain Tracking Off / On-hook  Idle Channel Noise  Out of Band Idle Channel Noise at TIP/RING  Harmonic Distortion plus Noise Off-hook  Harmonic Distortion plus Noise On-hook  Harmonic Distortion Off-hook | 100<br>101<br>102<br>102<br>104<br>106<br>106<br>107<br>108<br>108<br>109<br>110 |

| Table of | Contents                                                | Page |

|----------|---------------------------------------------------------|------|

| 9.4.9    | Harmonic Distortion On-hook                             | 111  |

| 9.4.10   | Total Distortion                                        | 112  |

| 9.4.10.1 | Total Distortion Measured with Sine Wave                | 112  |

| 9.4.10.2 | Total Distortion Measured with Noise According to CCITT | 113  |

| 9.4.11   | Return Loss                                             | 114  |

| 9.4.12   | Frequency Response                                      | 115  |

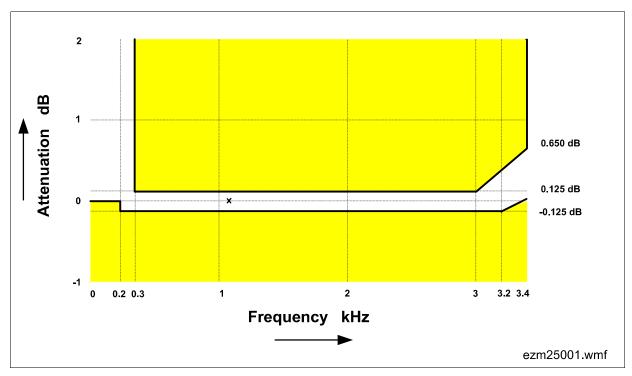

| 9.4.12.1 | Receive                                                 | 115  |

| 9.4.12.2 | Transmit                                                | 116  |

| 9.4.13   | Group Delay                                             | 117  |

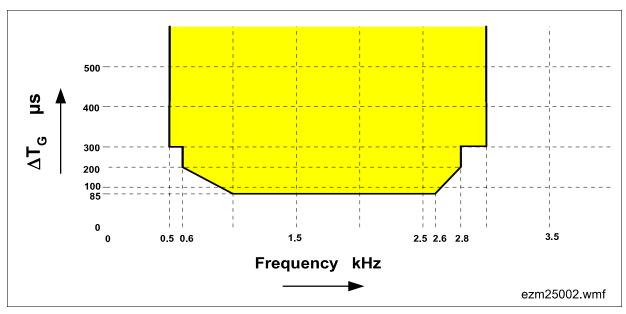

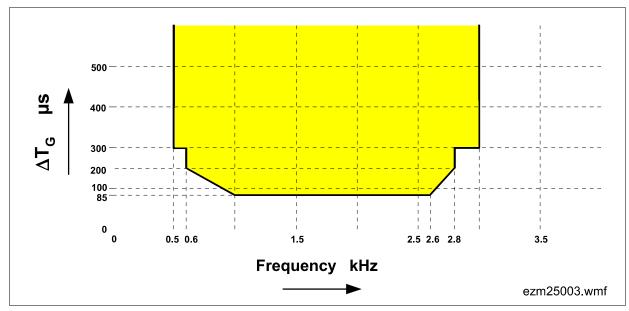

| 9.4.13.1 | Group Delay Absolute Values                             | 117  |

| 9.4.13.2 | Group Delay Distortion                                  | 117  |

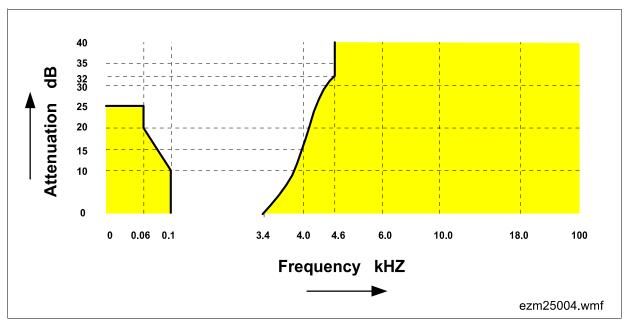

| 9.4.14   | Out-of-Band Signals at TIP-RING Receive                 | 119  |

| 9.4.15   | Out-of-Band Signals at TIP-RING Transmit                | 120  |

| 9.4.16   | Trans-Hybrid Loss                                       | 120  |

| 9.4.17   | Metering Detection Sensibility                          | 121  |

| 9.5      | AC Timing Characteristics                               | 122  |

| 9.5.1    | Input/ Output Waveform for AC Tests                     | 122  |

| 9.5.2    | Reset Timing                                            | 122  |

| 9.5.3    | Serial Control Interface Timing                         | 123  |

| 9.5.4    | PCM Interface Timing                                    | 125  |

| 10       | Application Circuit                                     | 127  |

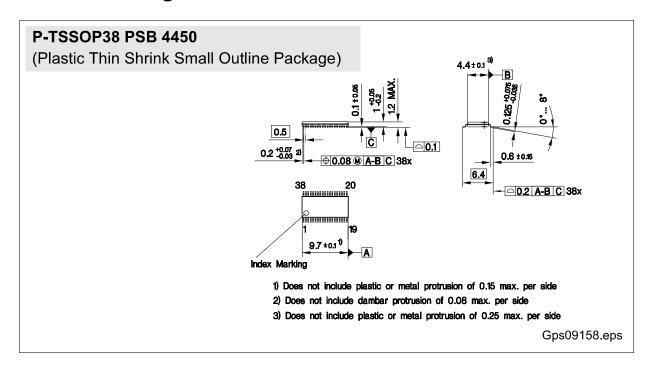

| 11       | Package Outlines                                        | 128  |

| 12       | Glossary                                                | 129  |

| 13       | Index                                                   | 130  |

| List of Fig | ures                                                           | Page |

|-------------|----------------------------------------------------------------|------|

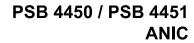

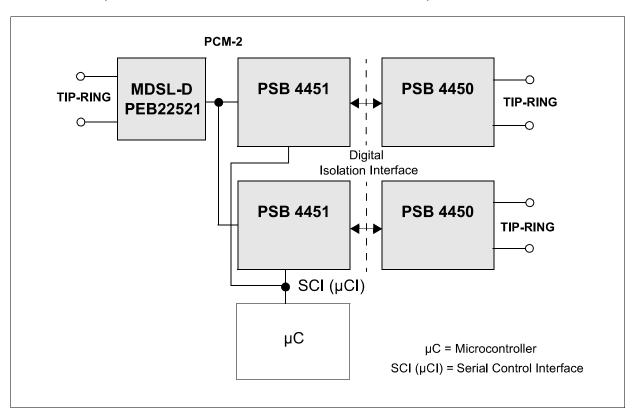

| Figure 1    | Block Diagram of the ANIC Chip Set                             | . 11 |

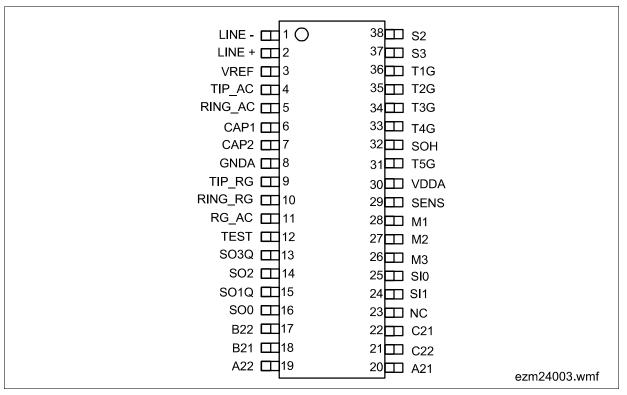

| Figure 2    | Pinning Diagram PSB 4450 (ANIC-A)                              | . 14 |

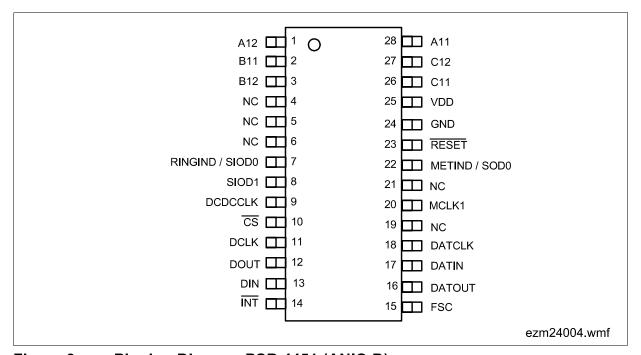

| Figure 3    | Pinning Diagram PSB 4451 (ANIC-D)                              |      |

| Figure 4    | ANIC Application in a COT                                      | . 19 |

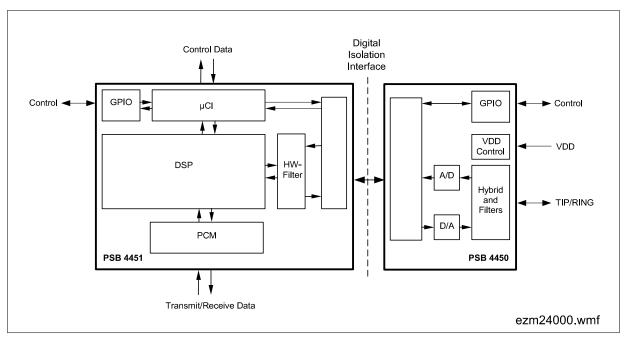

| Figure 5    | Functional Block Diagram of the PSB 4450/PSB 4451 Chip Set     | . 20 |

| Figure 6    | Voice Path                                                     | . 22 |

| Figure 7    | DC Measurement Path                                            | . 24 |

| Figure 8    | Interrupt Structure                                            |      |

| Figure 9    | Interrupts on the pins SI0, SI1, RINGIND/SIOD0 and SIOD1       | . 28 |

| Figure 10   | Ring Interrupt by Detection of a Voltage above a Threshold     | . 29 |

| Figure 11   | Ring Interrupt by Detection of Valid Ring                      |      |

| Figure 12   | Ring Signal Detection in ANIC-A                                | . 30 |

| Figure 13   | Metering Interrupt                                             |      |

| Figure 14   | Tone Interrupt                                                 |      |

| Figure 15   | Example for Consecutive Tone Interrupts                        |      |

| Figure 16   | Threshold Interrupt: TIP-RING                                  |      |

| Figure 17   | Example for Consecutive Threshold Interrupts                   |      |

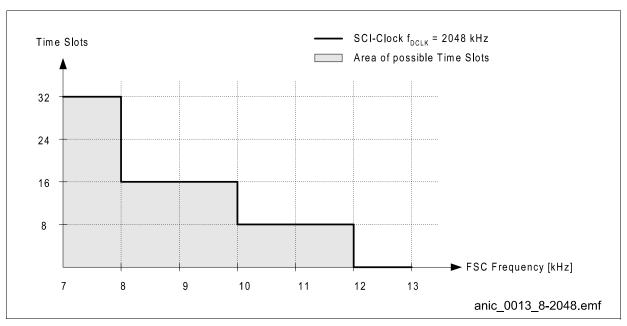

| Figure 18   | Time Slots for 8 k Sampling Mode and SCI-Clock 2048 kHz        |      |

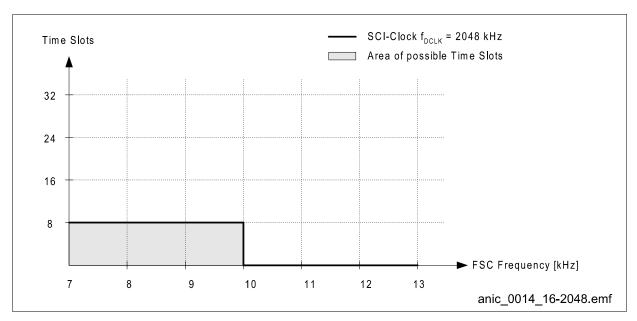

| Figure 19   | Time Slots for 16 k Sampling Mode and SCI-Clock 2048 kHz       |      |

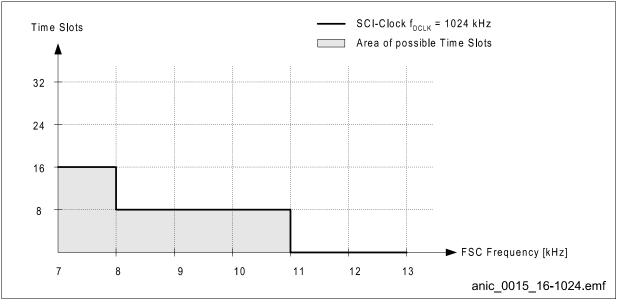

| Figure 20   | Time Slots for 16 k Sampling Mode and SCI-Clock 1024 kHz       |      |

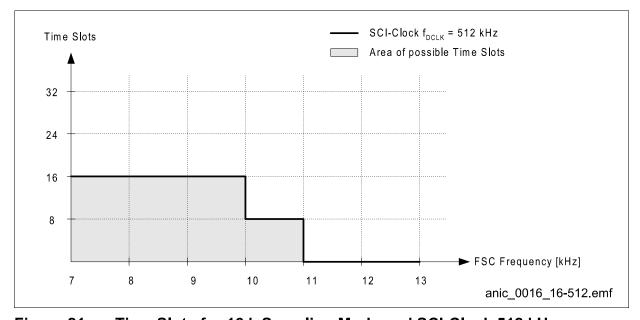

| Figure 21   | Time Slots for 16 k Sampling Mode and SCI-Clock 512 kHz        |      |

| Figure 22   | Example for Single Clock Rate, 512 kb/s                        |      |

| Figure 23   | Mapping of Linear and Companded Data into PCM Slots for 8 kHz. |      |

| Figure 24   | Mapping of Linear Data into PCM Slots for 16 kHz               |      |

| Figure 25   | PCM Interface Frames                                           |      |

| Figure 26   | Example for a Write Access                                     |      |

| Figure 27   | Example for a Read Access                                      |      |

| Figure 28   | Isolation by Capacitive Interface                              |      |

| Figure 29   | Isolation by Inductive Interface                               |      |

| Figure 30   | Ring Detect                                                    |      |

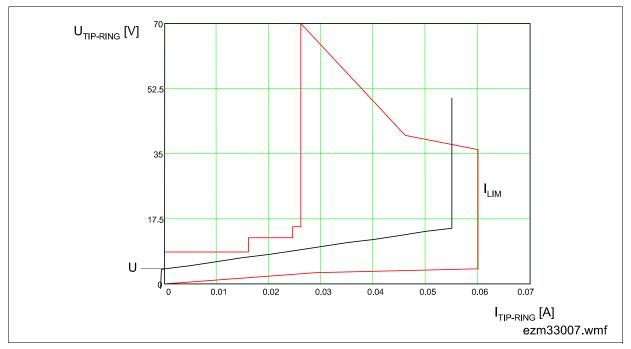

| Figure 31   | DC Termination Characteristics                                 |      |

| Figure 32   | DC Characteristics for France                                  |      |

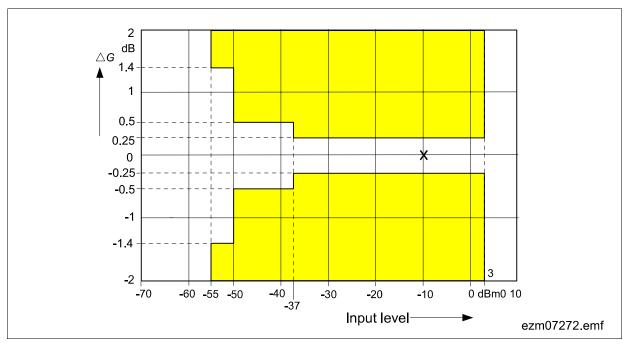

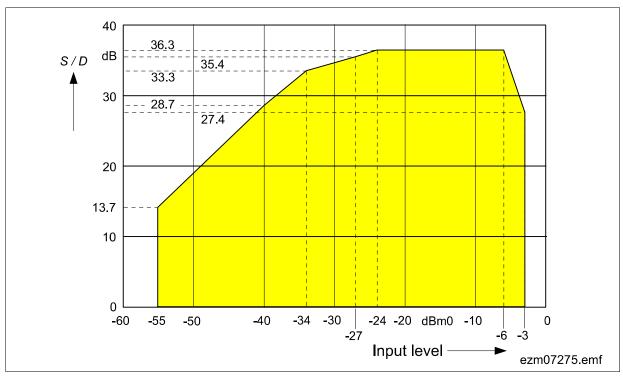

| Figure 33   | Gain Tracking Off / On-hook (Receive or Transmit)              |      |

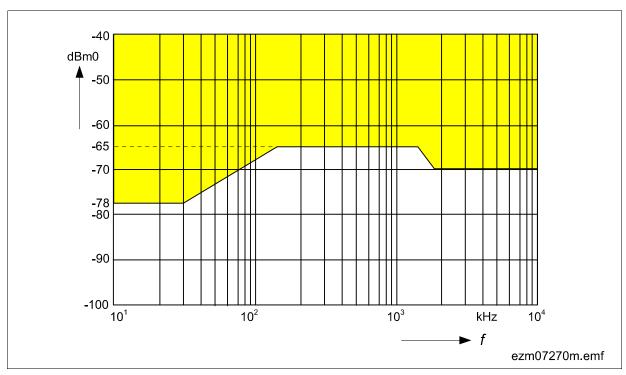

| Figure 34   | Out of Band Idle Channel Noise                                 | 109  |

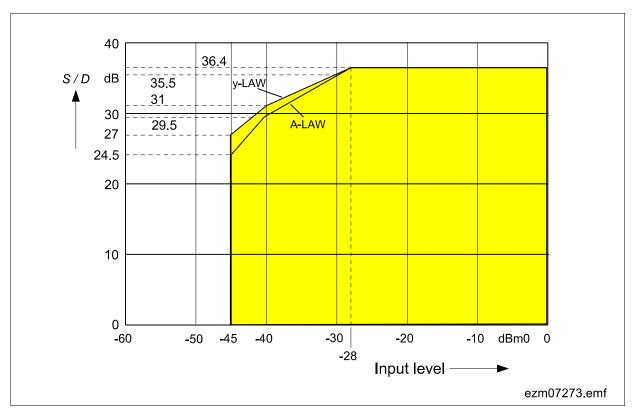

| Figure 35   | Total Distortion Receive or Transmit                           | 112  |

| Figure 36   | Total Distortion Receive                                       | 113  |

| Figure 37   | Total Distortion Transmit                                      | 113  |

| Figure 38   | Return Loss                                                    | 114  |

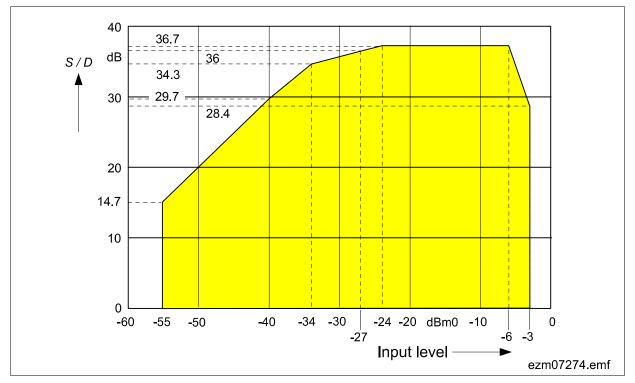

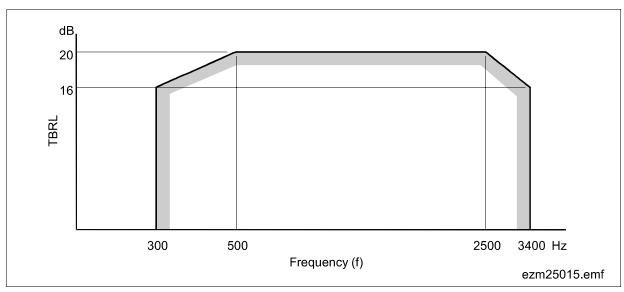

| Figure 39   | Frequency Response Receive                                     | 115  |

| Figure 40   | Frequency Response Transmit (HPX is off)                       | 116  |

| Figure 41   | Group Delay Distortion Receive                                 | 118  |

| Figure 42   | Group Delay Distortion Transmit                                | 118  |

Data Sheet 8 2000.09.04

## PSB 4450 / PSB 4451 ANIC

| List of Figures |                                                 |       |

|-----------------|-------------------------------------------------|-------|

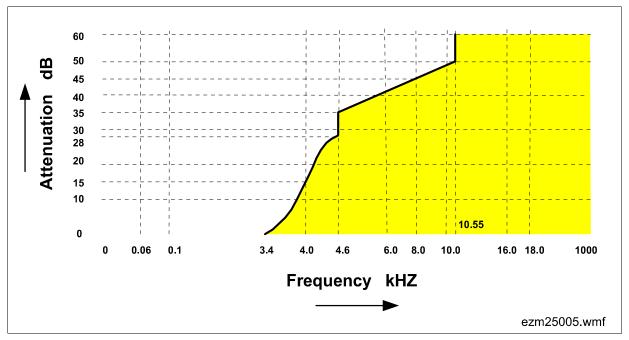

| Figure 43       | Out of Band Receive Discrimination              | . 119 |

| Figure 44       | Out of Band Transmit Discrimination             | . 120 |

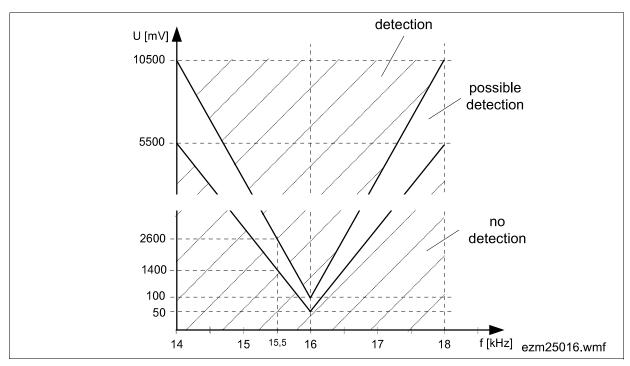

| Figure 45       | Metering Detection Sensibility 16 kHz (Typical) | . 121 |

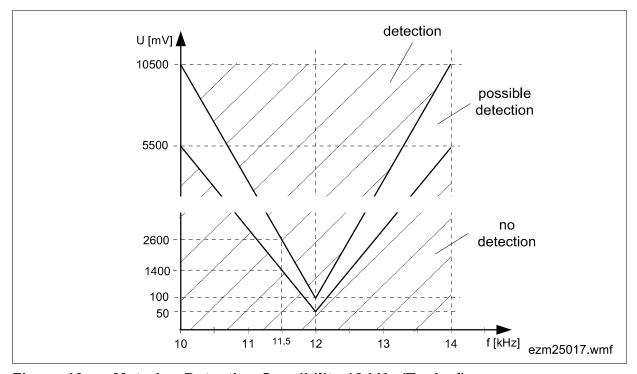

| Figure 46       | Metering Detection Sensibility 12 kHz (Typical) | . 121 |

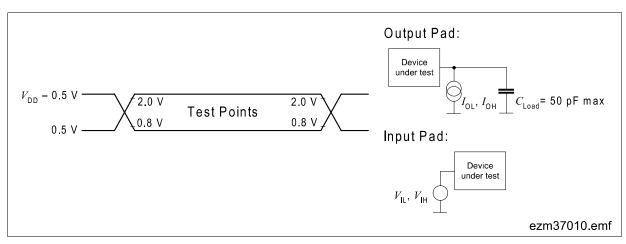

| Figure 47       | Waveform for AC Tests                           | . 122 |

| Figure 48       | Reset Timing                                    | . 122 |

| Figure 49       | Serial Control Interface Timing                 | . 123 |

| Figure 50       | PCM Interface Timing                            | . 125 |

Data Sheet 9 2000.09.04

## PSB 4450 / PSB 4451 ANIC

| List of Tables |                                                              |       |  |

|----------------|--------------------------------------------------------------|-------|--|

| Table 1        | Pin Descriptions PSB 4450                                    | 15    |  |

| Table 2        | Pin Descriptions PSB 4451                                    | 17    |  |

| Table 3        | PCM Interface Pins                                           | 39    |  |

| Table 4        | 8 kHz Sampling Rate (8 k sampling mode, fFSC = 8 kHz)        | 40    |  |

| Table 5        | 16 kHz Sampling Rate (16 k sampling mode, fFSC = 8 kHz)      | 40    |  |

| Table 6        | SCI-Clock, FSC, Sampling Mode and Time Slot Interdependency. | 40    |  |

| Table 7        | Serial Control Interface Pins                                | 45    |  |

| Table 8        | Register Overview                                            | 51    |  |

| Table 9        | CRAM Definitions for Coefficients                            | 54    |  |

| Table 10       | CRAM Definitions for Coefficients (see <b>Table 9</b> )      | 55    |  |

| Table 11       | RAM Definitions for Coefficients (see Table 12)              | 55    |  |

| Table 12       | RAM Definitions for Coefficients                             | 56    |  |

| Table 13       | Measurement Result Examples                                  | 66    |  |

| Table 14       | Operating Modes                                              | 91    |  |

| Table 15       | Selectable Values for ILIM                                   | 96    |  |

| Table 16       | Selectable Values for U0                                     | 96    |  |

| Table 17       | Selectable Values for R                                      | 96    |  |

| Table 18       | DC Characteristics PSB 4450                                  | . 102 |  |

| Table 19       | DC Characteristics PSB 4451                                  | . 104 |  |

| Table 20       | Serial Control Interface Switching Characteristics           | . 124 |  |

| Table 21       | PCM Interface Switching Characteristics                      | . 126 |  |

Preliminary Overview

### 1 Overview

ANIC is a chip set to interface analog voice signals to digital terminals such as DSL transceivers. Its technology and design make it especially suitable for the use throughout the world for applications such as

- DAML (Digital Added Main Line) interface between a central office and digital line transceivers,

- PBX trunks,

- Universal DLC (Digital Loop Carrier) systems.

Figure 1 Block Diagram of the ANIC Chip Set

Note: The block diagram is described in more detail in the section "Functional Description" on Page 20.

The ANIC chip set is an ideal analog front end to convert digital information into analog signals and vice versa for communication via telephone lines.

Reliability in digital processing is much better than in analog communications. The new design of the ANIC chip set has transferred processing that was previously done on the analog side to the digital part. Digital filters ensure great precision and virtually no fluctuation.

The use of digital filter processing in combination with software algorithms ensures excellent transmission performance and adaptability. The ANIC chip set is programmable to adapt to different countries' requirements. Coefficient sets can be downloaded to the ANIC chip set to comply with specifications throughout the world.

Data Sheet 11 2000.09.04

## PSB 4450 / PSB 4451 ANIC

Preliminary Overview

The ANIC chip set replaces the traditional Data Access Arrangement (DAA) with voice band transformer and discrete components. The use of digital signal processing and filtering approaches provides the user not only more features and programmability, but also better system performance.

As a result of the Analog-to-Digital Converter (ADC) and Digital-to-Analog Converter (DAC) technology used, the linearity of the ANIC chip set is limited only by second-order parasitic effects.

The main functional blocks of the ANIC are:

- Data Access Arrangement (DAA)

- Selectable A-law, μ-law, and 16-bit linear coder/decoder (codec)

- TIP-RING-GROUND voltage measurements to identify, e.g., polarity reversal

- · Time slot assignment for PCM-highway interface

The technology used for the two chips is:

- PSB 4450 (analog) low-power 0.8 µm BiCMOS

- PSB 4451 (digital) 0.35 μm CMOS

Infineon Technologies offers a range of reference and evaluation tools for the ANIC chip set. For appropriate tools, please contact your nearest Infineon Technologies representative.

Data Sheet 12 2000.09.04

# Analog Network Interface Circuit ANIC

PSB 4450 PSB 4451

#### Version 1.2

### 1.1 Features

- The ANIC chip set replaces the traditional Data Access Arrangement (DAA), codec and hybrid components.

- · On-hook transmission.

- DC measurements of TIP-RING, RING-GROUND and TIP-GROUND voltage.

- · General purpose I/O pins.

- Works with a large range of clock frequencies from 16.384 MHz to 33 MHz.

- Supports sample rates from 6 kHz up to 24 kHz

- 3 V technology for the PSB 4451.

- Output pins are TTL and CMOS compatible.

- Input pins are 5 V tolerant.

- On chip VDD control for the PSB 4450.

#### International features:

- Programmable ring detection: country-specific frequencies and levels. Coefficients for frequencies and levels are downloadable.

- Programmable country-specific DC characteristics.

- · Detection of metering signals.

- PCM encoded digital voice transmission (A-Law or μ-Law) according G.711.

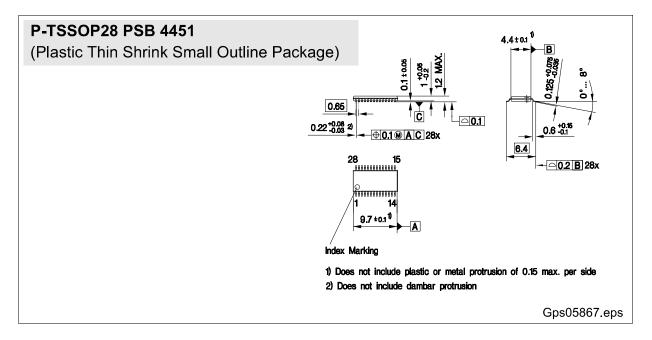

| Туре     | Package   |

|----------|-----------|

| PSB 4450 | P-TSSOP38 |

| PSB 4451 | P-TSSOP28 |

Preliminary Pin Descriptions

## 2 Pin Descriptions

Figure 2 Pinning Diagram PSB 4450 (ANIC-A)

Figure 3 Pinning Diagram PSB 4451 (ANIC-D)

Data Sheet 14 2000.09.04

## **Pin Descriptions**

## 2.1 Pin Descriptions PSB 4450

Table 1 Pin Descriptions PSB 4450

| Pin No. | Symbol  | Function | Description                                                     |

|---------|---------|----------|-----------------------------------------------------------------|

| 30      | VDDA    | Power    | + 5 V supply for analog circuitry                               |

| 3       | VREF    |          | Filtering reference voltage                                     |

| 8       | GNDA    | Power    | Ground analog. All signals are referenced to this pin.          |

| 1       | LINE-   | I        | Voltage sense input from TIP                                    |

| 2       | LINE+   | I        | Voltage sense input from RING                                   |

| 9       | TIP_RG  | I        | Voltage sense input for ringing                                 |

| 10      | RING_RG | I        | Voltage sense input for ringing                                 |

| 4       | TIP_AC  | I        | Voltage sense input for AC signals                              |

| 5       | RING_AC | I        | Voltage sense input for AC signals                              |

| 11      | RG_AC   | I        | Voltage sense input for AC signals in ON-HOOK CONVERSATION mode |

| 38      | S2      | I        | Sense inputs for ringer impedance loop                          |

| 37      | S3      | I        | Sense inputs for ringer impedance loop                          |

| 16      | SO0     | 0        | General purpose output                                          |

| 15      | SO1Q    | 0        | General purpose output                                          |

| 14      | SO2     | 0        | General purpose output                                          |

| 13      | SO3Q    | 0        | General purpose output                                          |

| 12      | TEST    | I        | Must be connected to GND                                        |

| 25      | SI0     |          | General purpose input                                           |

| 24      | SI1     | I        | General purpose input                                           |

| 36      | T1G     | 0        | Control pin for transistor T1                                   |

| 35      | T2G     | 0        | Control pin for transistor T2                                   |

| 34      | T3G     | 0        | Control pin for transistor T3                                   |

| 33      | T4G     | 0        | Control pin for transistor T4                                   |

| 31      | T5G     | 0        | Control pin for transistor T5                                   |

| 11      | NC      | -        | unused                                                          |

| 29      | SENS    | I        | Voltage sense for VDD control                                   |

| 32      | SOH     | I        | Current sensing for on-hook transmission                        |

|         |         |          |                                                                 |

## **Pin Descriptions**

Table 1 Pin Descriptions PSB 4450 (Continued)

| Pin No. | Symbol | Function | Description                                                                                           |

|---------|--------|----------|-------------------------------------------------------------------------------------------------------|

| 28      | M1     | I        | Measurement input GROUND                                                                              |

| 27      | M2     | I        | Measurement input TIP                                                                                 |

| 26      | M3     | I        | Measurement input RING                                                                                |

| 6       | CAP1   | 0        | External low pass filter                                                                              |

| 7       | CAP2   | 0        | External low pass filter                                                                              |

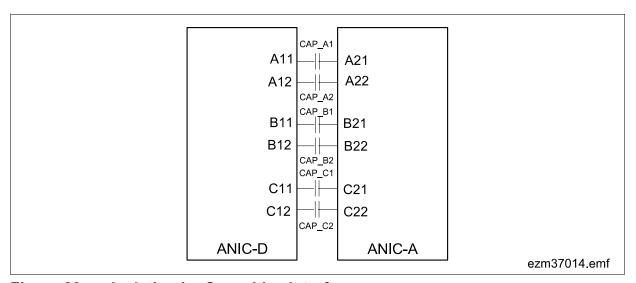

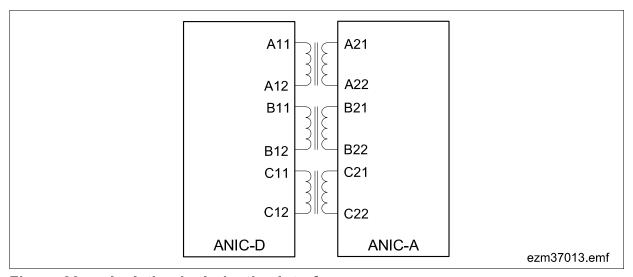

| 20      | A21    | I        | Digital isolation interface to PSB 4451:<br>Must be connected to pin A11 of PSB 4451<br>(see Page 50) |

| 19      | A22    | I        | Digital isolation interface to PSB 4451:<br>Must be connected to pin A12 of PSB 4451<br>(see Page 50) |

| 18      | B21    | 0        | Digital isolation interface to PSB 4451:<br>Must be connected to pin B11 of PSB 4451<br>(see Page 50) |

| 17      | B22    | 0        | Digital isolation interface to PSB 4451:<br>Must be connected to pin B12 of PSB 4451<br>(see Page 50) |

| 22      | C21    | I        | Digital isolation interface to PSB 4451:<br>Must be connected to pin C11 of PSB 4451<br>(see Page 50) |

| 21      | C22    | I        | Digital isolation interface to PSB 4451:<br>Must be connected to pin C12 of PSB 4451<br>(see Page 50) |

| 23      | NC     | _        | unused                                                                                                |

Note: For further details see Application Note "Understanding the External Components of the ANIC Chip Set".

## **Pin Descriptions**

## 2.2 Pin Descriptions PSB 4451

Table 2 Pin Descriptions PSB 4451

| Pin No. | Symbol  | Function | Description                                                                                                                           |

|---------|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| 25      | VDD     | Power    | + 3.3 Volt supply for the digital & analog circuitry.                                                                                 |

| 24      | GND     | Power    | Ground digital. All signals are referenced to this pin.                                                                               |

| 20      | MCLK1   | I        | Master Clock1: this pin must be driven by an external clock of e.g. 16.384 MHz                                                        |

| 23      | RESET   | I        | Reset input: resets the device (low active) Reset is considered valid if asserted active longer than t <sub>RESET,min</sub> = 300 ns. |

| 15      | FSC     | 1        | Frame Synchronization Clock                                                                                                           |

| 17      | DATIN   | I        | PCM Interface: receive data 8-bit timeslots.                                                                                          |

| 16      | DATOUT  | 0        | PCM Interface: transmit data, tristate if not active                                                                                  |

| 18      | DATCLK  | I        | Data clock 512 to 2048 kHz: determines the rate at which data is transferred to and from the PCM Interface.                           |

| 14      | ĪNT     | 0        | Interrupt output pin (open drain, low active, internal pull up with 32 kOhm).                                                         |

| 11      | DCLK    | I        | Serial Control Interface: clock for control data.                                                                                     |

| 10      | CS      | I        | Serial Control Interface: chip select                                                                                                 |

| 13      | DIN     | I        | Serial Control Interface: receive control data from the µC / DSP                                                                      |

| 12      | DOUT    | 0        | Serial Control Interface: transmit control data to the µC / DSP                                                                       |

| 9       | DCDCCLK | 0        | Output for DCDC switching clock                                                                                                       |

| 28      | A11     | 0        | Digital isolation interface to PSB 4450:<br>Must be connected to pin A21 of PSB 4450<br>(see Page 50)                                 |

| 1       | A12     | 0        | Digital isolation interface to PSB 4450:<br>Must be connected to pin A22 of PSB 4450<br>(see Page 50)                                 |

## **Pin Descriptions**

Table 2 Pin Descriptions PSB 4451 (Continued)

| Pin No. | Symbol             | Function | Description                                                                                           |

|---------|--------------------|----------|-------------------------------------------------------------------------------------------------------|

| 2       | B11                | I        | Digital isolation interface to PSB 4450:<br>Must be connected to pin B21 of PSB 4450<br>(see Page 50) |

| 3       | B12                | I        | Digital isolation interface to PSB 4450:<br>Must be connected to pin B22 of PSB 4450<br>(see Page 50) |

| 26      | C11                | 0        | Digital isolation interface to PSB 4450:<br>Must be connected to pin C21 of PSB 4450<br>(see Page 50) |

| 27      | C12                | 0        | Digital isolation interface to PSB 4450:<br>Must be connected to pin C22 of PSB 4450<br>(see Page 50) |

| 22      | METIND /<br>SOD0   | 0        | Metering indication or general purpose output pin (active high).                                      |

| 8       | SIOD1              | Ю        | General purpose I/O pin.                                                                              |

| 7       | RINGIND /<br>SIOD0 | Ю        | Ring indication or general purpose I/O pin (active high).                                             |

| 6       | NC                 | _        | Unused                                                                                                |

| 21      | NC                 | _        | Unused                                                                                                |

| 19      | NC                 | _        | Unused                                                                                                |

| 4       | NC                 | _        | Unused                                                                                                |

| 5       | NC                 | _        | Unused                                                                                                |

**Typical Applications**

## 3 Typical Applications

As mentioned in the overview, one of the ANIC applications is in central office terminals (COT) serving as interface between voice signals of the CO's analog line card and the digital line transceivers connected to the network.

In typical implementations, the innovative digital isolation interface renders a transformer redundant, reducing weight and space requirements.

## 3.1 ANIC Chip Set in the Central Office Terminal (COT)

The ANIC chip set forms the front end between a MDSL chip set and the TIP-RING line.

Figure 4 ANIC Application in a COT

The MDSL chip set is both source and destination of digital signals which are transferred to and from the digital chip PSB 4451 via the PCM Interface. The Serial Control Interface (SCI) enables external control of the ANIC chip set. The SCI gives transparent access to ANIC commands and signalling pins so that precalculated coefficient sets can be downloaded from the system to the on-chip coefficient RAM (CRAM) to program the filters.

Data Sheet 19 2000.09.04

### **Functional Description**

## 4 Functional Description

The functional description consists of a block diagram with explanation of the building blocks followed by a description of the chip set's basic principles of operation.

## 4.1 Functional Block Diagram

The chip set consists of two chips, PSB 4450 and PSB 4451. **Figure 5** shows the main building blocks:

Figure 5 Functional Block Diagram of the PSB 4450/PSB 4451 Chip Set

#### **PSB 4450:**

**VDD Control:** regulates the supply voltage for the PSB 4450 and can be connected to an isolated 5 V or by the use of an external transistor to an unregulated DC voltage (VDD).

**Hybrid and Filters:** the hybrid provides two-wire to four-wire conversion, and the analog anti-aliasing pre-filters and smoothing post-filters provide signal conditioning.

The voice data path is routed from the filters to the digital isolation interface through the **Analog-to-Digital** (A/D) or the **Digital-to-Analog** (D/A) converters: These are oversampling converters based on a  $\Delta$ – $\Sigma$  modulation approach. The oversampling technique provides signals with low signal-to-noise ratio and high conversion resolution. **Digital Isolation Interface:** Used for isolation of PSB 4451 from PSB 4450.

**G**eneral **P**urpose **I/Os (GPIOs):** PSB 4450 has 2 inputs (SI0, SI1) and 2 outputs (SO2, SO3Q). The inputs can be used as interrupt sources. The outputs can be used to control external switches for the connection of terminal impedance.

Data Sheet 20 2000.09.04

### **Functional Description**

#### **PSB 4451:**

**Hardware filters:** The HW filters are interpolating transmit and decimating receive digital filters. See also **Figure 6** for details.

**Digital Signal Processing Unit (DSP):** The DSP does equalization, gain adjustment, impedance matching, and other DAA functions, in accordance with the downloaded coefficient set.

**PCM Interface:** Via the PCM Interface transmit and receive data are transferred between the PSB 4451 and the digital transceiver (e.g. MDSL chip set).

**Serial Control Interface (SCI)**: The Serial Control Interface allows external control of the ANIC features and provides transparent access to ANIC commands and signalling pins, so that pre-calculated coefficient sets can be downloaded from the system to the on-chip Coefficient RAM (CRAM) to program the filters.

**G**eneral **P**urpose **I/Os (GPIOs)**: PSB 4451 has two input/output pins (SIOD1, RINGIND/SIOD0) and one output pin (METIND/SOD0) to control external components.

## 4.2 General Description

### 4.2.1 Impedance

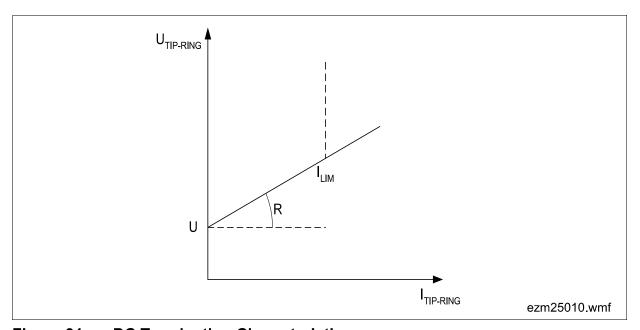

ANIC requires an external transistor T1 to control the DC and AC loop current. T1 must be able to handle 100 mA of continous current.

On the TIP/RING side, ANIC applies voltage sensing and current feeding. There is a feedback loop between the receive and the transmit path to synthesize input impedance. This means the voltage is multiplied by a transfer function and fed back as a current to the line. This transfer function synthesizes the ANIC input impedance for AC, DC and RING. Within that functionallity, the ANIC acts as the required passive network.

### 4.3 Voice Path

These filters are programmable according to the selected specification by downloading the appropriate sets of coefficients. The converted signal is available at the PCM output every 125  $\mu$ s. Decoding can be either selected according G.711 (A- /  $\mu$ -law) or 16-bit linear 2´s complement. Similarly, digital data in the transmit direction are shifted in and processed by programmable filters for the selected specification. The results are sent to the interpolating transmit filter and are converted to an analog signal by the oversampling D/A converter.

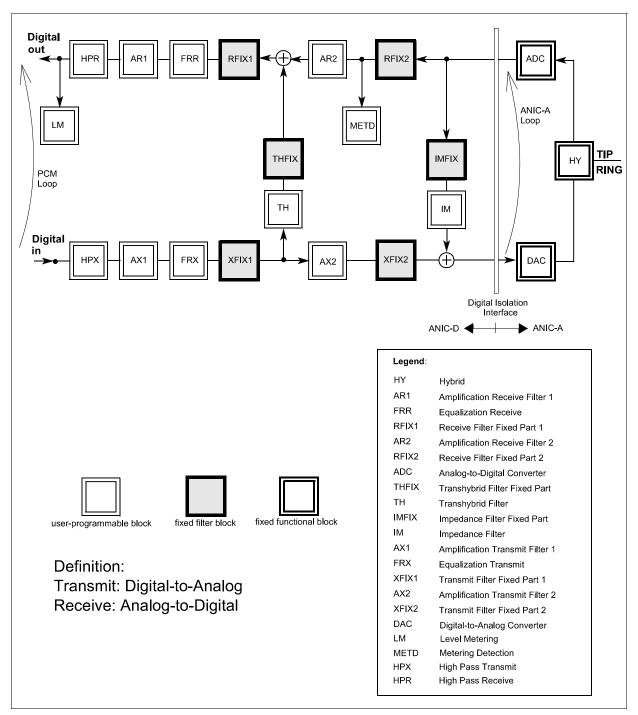

**Figure 6** shows the voice path through the digital filter structure. Some filters are fixed while others are user programmable.

Data Sheet 21 2000.09.04

## **Functional Description**

Figure 6 Voice Path

Data Sheet 22 2000.09.04

## **Functional Description**

### 4.3.1 Receive Path

The analog signal proceeds from TIP/RING to PSB 4450 with an anti-aliasing pre-filter. The Analog-to-Digital Converter (ADC) is a sigma-delta converter, which converts the signal to a 1-bit digital data stream. The signal is then passed to the PSB 4451 where the first stage of down-sampling is performed in hardware, for better performance, in the digital filter RFIX2.

Subsequent stages of processing are done by microcode in the digital filter structure, to allow adaptability. Gain adjustment is provided in the two stages AR1 and AR2. The switchable high pass HPR is used to suppress low frequent noise.

A decimation stage is located inbetween to reduce the sampling rate to the 8/16 kHz PCM rate, and a low-pass filter to band-limit the signal in accordance with ITU-T G.714 and Q.552 recommendations; and an equalization stage (in FRR).

Finally, the signal will be A-law or  $\mu$ -law coded and transferred out to the PCM Interface.

The ANIC meets or exceeds all ITU and ETSI recommendations on attenuation, distortion and group delay.

A metering function is included on the receive path.

#### 4.3.2 Transmit Path

The digital input signal is received from the PCM Interface and decoded from A–law or  $\mu$ –law. Most processing steps are done in microcode in the digital filter structure, which is programmable and therefore flexible.

There are two gain adjustment stages, in AX1 and AX2. The switchable high pass HPX is used to suppress low frequent noise.

Located inbetween, there is an equalization stage (in FRX), a high-pass filter and a low-pass filter to band-limit the signal (in XFIX1); and a first stage of interpolation.

Further up-sampling is done by hardware (in XFIX2), and the 1-bit data stream is converted to analog in the DAC and smoothed by a post-filter, followed by an analog gain stage before the signal is converted to a two-wire signal.

## 4.3.3 Loops

ANIC implementation includes two loops. One is used to generate the AC-termination impedance (IM, IMFIX), the ring impedance and the AC impedance for on-hook transmission and the other is used to perform accurate hybrid balancing (TH, THFIX).

### 4.4 Ring Path

The ringer impedance is synthesized in the same way as the AC impedance using a feedback loop.

Data Sheet 23 2000.09.04

### **Functional Description**

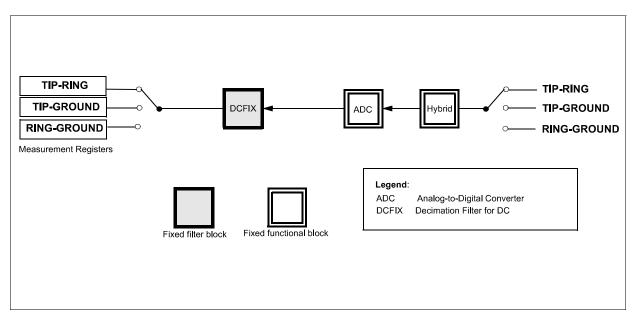

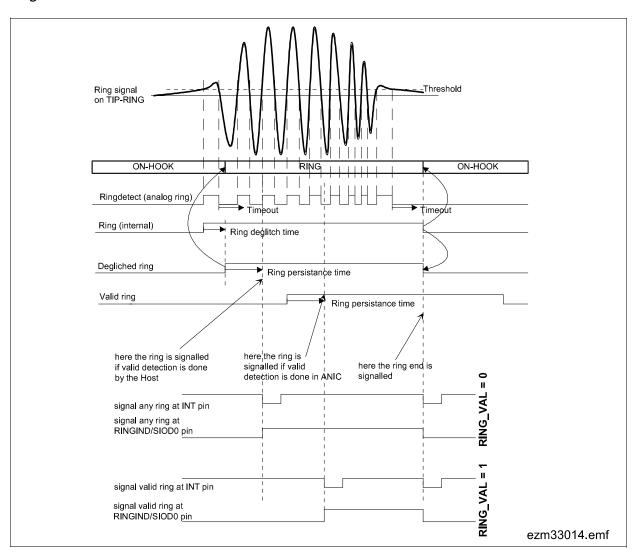

### 4.5 DC Measurement Path

To measure the DC voltage between TIP-RING, TIP-GROUND and RING-GROUND, a filter structure similar to that of the voice receive path is used. Each voltage is measured for an interval of 375  $\mu$ s (3 times 1/8000 Hz) and stored in the corresponding register (2's complements, see register 7 to register 9). These registers are updated every 1.125 milliseconds. The voltage is measured in four selectable ranges with 8 bit resolution (see register 25)

Each measurement provides individual programmable thresholds (registers 19 & 20 for RING-GROUND, registers 21 & 22 for TIP-GROUND and registers 15 to 18 for TIP-RING). Any voltage exceeding these thresholds will trigger a maskable interrupt. The measured value can be used to detect line reversal and disconnection of the line.

Figure 7 DC Measurement Path

## 4.6 Tone Detection<sup>1)</sup>

ANIC is equipped with two programmable tone detectors to detect modem and CALLER ID alert tones. Both of them can generate an interrupt.

Data Sheet 24 2000.09.04

<sup>1)</sup> Coefficients will be computed by the ANICOS Software. By downloading these coefficients to the ANIC using the ANICON software, the desired functionality will be provided.

### **Functional Description**

## 4.7 Metering<sup>1)</sup>

Metering frequencies of 12 and 16 kHz are filtered out by the PSB 4451. Signals with level less than 2.5 Vrms can be applied directly to ANIC. However, an external notch filter is necessary to attenuate metering signals that exceed 2.5 Vrms.

ANIC is capable of signalling metering information via interrupt. Longitudinal 50 Hz metering can be realized usings ANICs measurement cabability.

## 4.8 Ring Detect<sup>2)</sup>

ANIC can be programmed to detect ring signals and will indicate them with an interrupt. The ring threshold as well as the ring frequency can be programmed.

Data Sheet 25 2000.09.04

<sup>1)</sup> Coefficients will be computed by the ANICOS Software. By downloading these coefficients to the ANIC using the ANICON software, the desired functionality will be provided.

Coefficients will be computed by the ANICOS Software. By downloading these coefficients to the ANIC using the ANICON software, the desired functionality will be provided.

### **Functional Description**

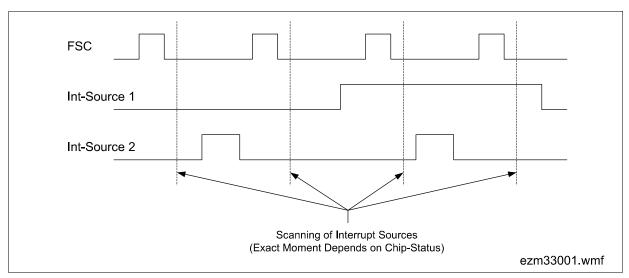

## 4.9 Interrupt Structure

## 4.9.1 Interrupt-Handling

All interrupt sources are polled at a time intervall of at least  $t_{FSC}$  = 125 µs for FSC = 8 kHz (depending on the load of the controller). That means that an interrupt source must be stable for a minimum of this period to be detected.

Figure 8 Interrupt Structure

In the above example the change of the Int-Source 1 is detected. Int-Source 2 is not detected by the Interrupt-controller and therefore will be ignored.

The host can enable the  $\overline{\text{INT}}$  output by setting register 2. Following power-up, register 2 is cleared, i.e., all interrupt sources are disabled and  $\overline{\text{INT}}$  is in high impedance state.

INT, when asserted low, indicates an interrupt. The host reads the register 1 to determine the source of the interrupt. Reading the interrupt status register 1 clears the register content. All interrupt sources have equal priority.

Data Sheet 26 2000.09.04

### **Functional Description**

## 4.9.2 Interrupt Sources

| TYPE    | NAME                     | MEANING                                                                                                  |

|---------|--------------------------|----------------------------------------------------------------------------------------------------------|

| Static  | SI0, SI1                 | Detection of changes on this GPI's of ANIC-A via the digital isolation interface                         |

| Static  | RINGIND/<br>SIOD0, SIOD1 | Detection of changes on this GPIO's of ANIC-D, when they are configured as inputs                        |

| Static  | RING                     | Detection of ring signal                                                                                 |

| Static  | MET                      | Detection of metering signals by ANIC DSP software                                                       |

| Dynamic | TONE                     | Detection of programmed tone                                                                             |

| Dynamic | THRESHOLD                | Detection if actual programmed threshold value on TIP-RING, RING-GROUND or TIP-GROUND has been exceeded. |

### **Polling:**

If all interrupts are disabled in register 2 there is still a possibility to poll the events that otherwise would have caused an indication at the  $\overline{\text{INT}}$  pin. The occurrence of an interrupt can always be detected by reading the register 1.

There are two types of interrupts:

## 4.9.2.1 Static Interrupts

Static interrupts take place on signal changes of the following signals:

- Static interrupt sources on pins SI0, SI1, RINGIND / SIOD0 and SIOD1

- Detection of ring signals

- · Detection of metering signals

Every detected signal change is reflected by an logic 1 in the corresponding bit in the register 1. Unlike dynamic interrupts there is also an interrupt produced at the end of the event or signal.

Data Sheet 27 2000.09.04

## **Functional Description**

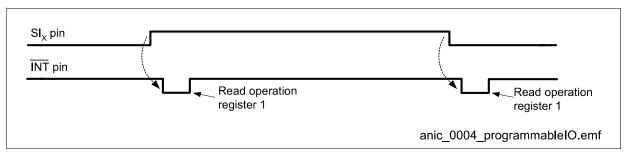

### Interrupts on the pins SI0, SI1, RINGIND/SIOD0 and SIOD1:

Interrupts on the GPI pins SI0 and SI1 use the following bits:

- Bits SIA0 and SIA1 in register 5 indicate the value of the pins SI0 and SI1.

- Bits SIA0 and SIA1 in register 1 show that a signal on the pins SI0 and SI1 was the cause for an interrupt indication on the INT pin. Reading register 1 sets the INT pin back to inactive (high).

For detecting interrupts on the GPIO pins RINGIND/SIOD0 and SIOD1 it is necessary to configure them as inputs in register 10. The following bits are used:

- Bits SIOD0\_I and SIOD1\_I in register 5 indicate the value of the pins RINGIND/SIOD0 and SIOD1.

- Bits SIOD0 and SIOD1 in register 1 show that a signal on the pins RINGIND/SIOD0 and SIOD1 was the cause for an interrupt indication on the INT pin. Reading register 1 sets the INT pin back to inactive (high).

**Figure 9** shows the status of the  $\overline{INT}$  output in relation to the static interrupt sources  $SI_X$  input pins.

Figure 9 Interrupts on the pins SI0, SI1, RINGIND/SIOD0 and SIOD1

Data Sheet 28 2000.09.04

### **Functional Description**

### **Ring Interrupt:**

There are two possibilities for ring detection on TIP/RING:

1. Ring interrupt by detection of a voltage above the ring threshold

Since only a voltage detection takes place, the validation according to amplitude and frequency of the ring signal has still to be done by the host.

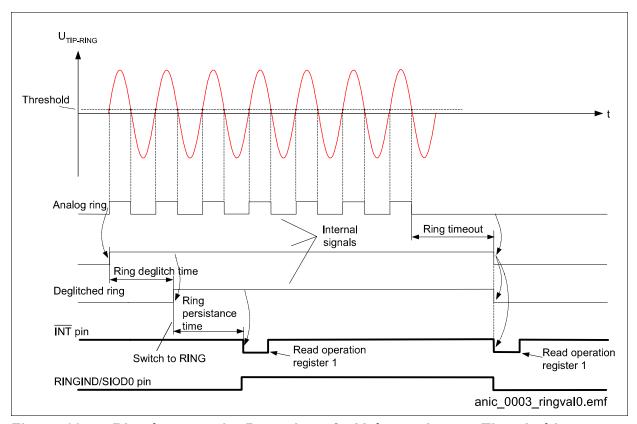

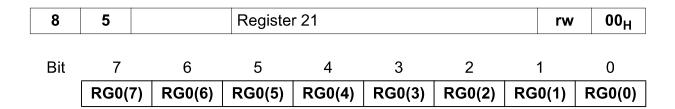

The ring interrupt indication on the RINGIND/SIOD0 pin derives from internal signals which allow checking for spike rejection (ring deglitch time, see register 27), suppression of short rings (ring persistance time, see register 26) and ring interruptions (ring timeout, see register 103) as shown in **Figure 10**.

Figure 10 Ring Interrupt by Detection of a Voltage above a Threshold

Data Sheet 29 2000.09.04

### **Functional Description**

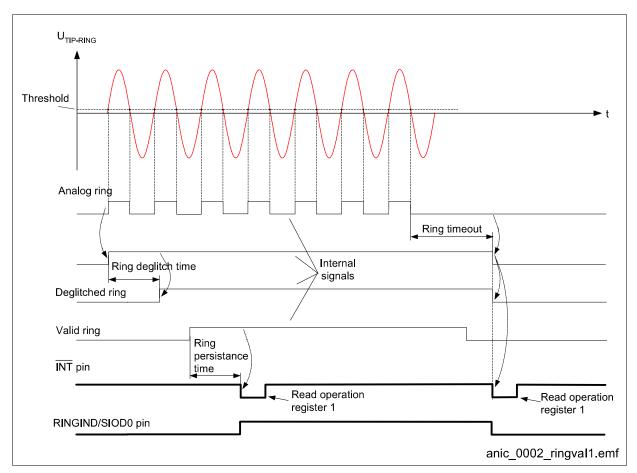

### 2. Ring interrupt by detection of valid ring

Figure 11 shows a ring interrupt with internal validation in the ANIC according to amplitude and frequency defined by programmed CRAM coefficients.

Figure 11 Ring Interrupt by Detection of Valid Ring

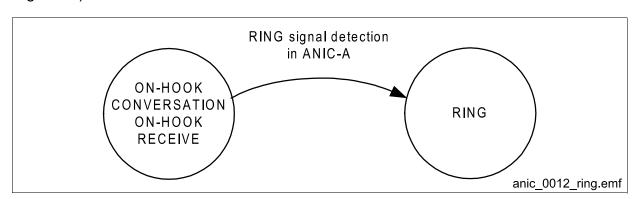

According to Figure 12, ring signal detection in ANIC-A causes an automatic transition from the ON-HOOK CONVERSATION or ON-HOOK RECEIVE to the RING state (see register 5).

Figure 12 Ring Signal Detection in ANIC-A

Data Sheet 30 2000.09.04

### PSB 4450 / PSB 4451 ANIC

### **Preliminary**

### **Functional Description**

Both possiblities for ring detection use the following bits:

- Bit SHOW\_RING in register 24 enables the indication of the ring status on pin RINGIND/SIOD0, if this pin is configured as output (register 10).

- Bit RING in register 5 indicates if either a voltage above a ring threshold or a valid ring was detected or finished (depending of bit RING\_VAL in register 10).

- Bit RING in register 1 shows that a ring detection was the cause for an interrupt indication on the  $\overline{\text{INT}}$  pin. Reading register 1 sets the  $\overline{\text{INT}}$  pin back to inactive (high).

### **Functional Description**

### **Metering Interrupt:**

Metering interrupts use the following bits:

- Bit SHOW\_MET in register 24 enables indication of metering signals on pin METIND/ SOD0.

- Bit MET in register 1 shows that a metering detection was the cause for an interrupt indication on the  $\overline{\text{INT}}$  pin. Reading register 1 sets the  $\overline{\text{INT}}$  pin back to inactive (high).

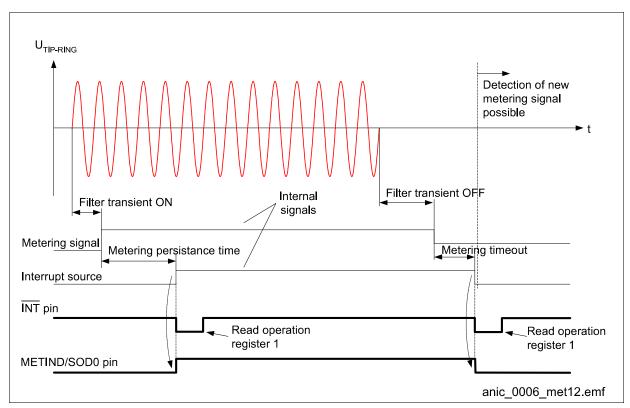

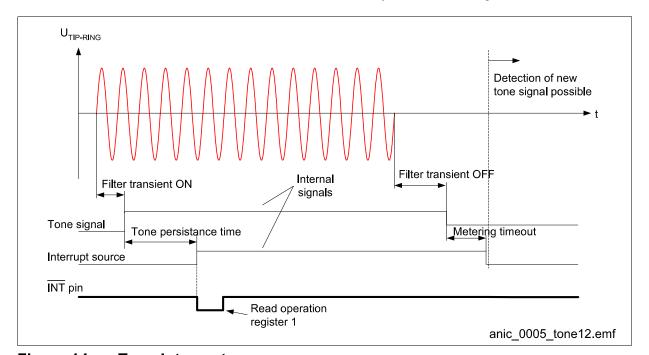

The metering interrupt indication on the METIND/SOD0 pin derives from internal signals which allow checking for suppression of short metering signals (metering persistance time, see register 28) and metering signal interruptions (metering timeout, see register 104) as shown in **Figure 13**. The filter transient ON and OFF times are defined by CRAM settings.

Figure 13 Metering Interrupt

Data Sheet 32 2000.09.04

### **Functional Description**

## 4.9.2.2 Dynamic Interrupts

Dynamic interrupts are caused by the following events:

- · Detection of tone signals

- Passing of programmed threshold voltages at TIP-RING, RING-GROUND and TIP-GROUND.

Unlike static interrupts there is no interrupt produced at the end of the event. Every detected event is reflected by a logic 1 in the corresponding bit of register 1 (details in register 2 and register 5).

### **Tone Interrupt:**

Tone interrupts can be used for fax or modem alert tone detection.

The following bits are used:

- Bits E\_TONE(0) and E\_TONE(1) in register 24 enable the detection of the tone sources tone 0 or tone 1.

- Bits TONE(0) and TONE(1) in register 5 indicate the detection of the tone sources tone 0 or tone 1. Reading register 5 clears the bits TONE(0) and TONE(1).

- Bit TONE in register 1 shows that a tone detection was the cause for an interrupt indication on the  $\overline{\text{INT}}$  pin. Reading register 1 sets the  $\overline{\text{INT}}$  pin back to inactive (high).

The tone interrupt indication on the  $\overline{\text{INT}}$  pin derives from internal signals which allow checking for suppression of short metering signals (tone persistance time, see register 28) and tone signal interruptions (tone timeout, see register 104) as shown in **Figure 14**. The filter transient ON and OFF times are defined by CRAM settings.

Figure 14 Tone Interrupt

Data Sheet 33 2000.09.04

### **Functional Description**

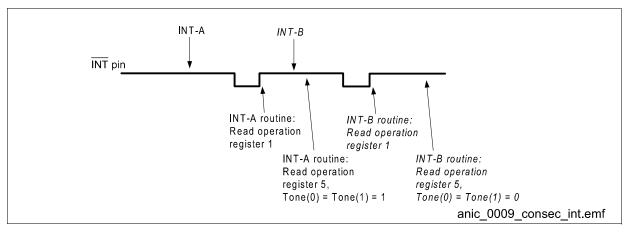

When there are two consecutive tone interrupts (e.g. "INT-A" followed by "INT-B", see **Figure 15**) and INT-B happens before the interrupt service routine of INT-A could read register 5, the source of INT-B will be read together with the source of INT-A in register 5 (Bits TONE(0) = TONE(1) = 1). As reading register 5 clears the bits TONE(0) and TONE(1), the later starting interrupt service routine of INT-B can't find a source for this interrupt in register 5 (Bits TONE(0) = TONE(1) = 0). Therefore, the host must ignore the interrupt service routine of INT-B and use the values of the former routine.

Figure 15 Example for Consecutive Tone Interrupts

### Threshold Interrupt:

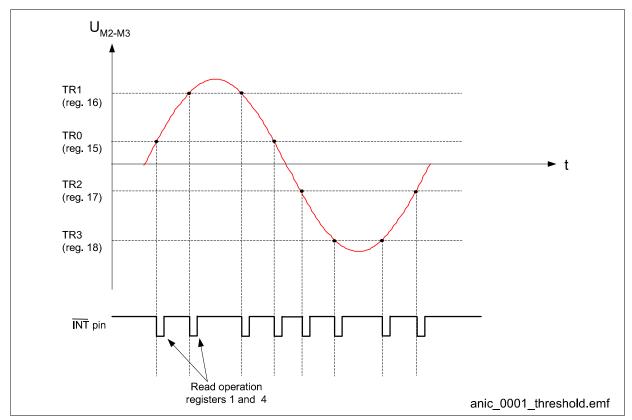

Threshold interrupts can be used to detect line reversal, disconnect or 50 Hz metering signals on TIP-RING, RING-GROUND or TIP-GROUND line voltages. An interrupt is detected, when the line voltage passes a programmable threshold voltage (see registers 15 to 22).

TIP-RING, RING-GROUND and TIP-GROUND threshold interrupts use the following bits:

- Bits E\_TR(x), E\_RG(x) and E\_TG(x) in register 23 enable the detection of TIP-RING, RING-GROUND or TIP-GROUND line voltage threshold indications.

- Bits TR(x), RG(x) and TG(x) in register 4 indicate the TIP-RING, RING-GROUND and TIP-GROUND voltages passing a programmed threshold value. Reading register 4 clears the bits TR(x), RG(x) and TG(x).

- Bit THR in register 1 shows that passing a voltage threshold was the cause for an interrupt indication on the  $\overline{\text{INT}}$  pin. Reading register 1 sets the  $\overline{\text{INT}}$  pin back to inactive (high).

**Figure 16** shows an example for a TIP-RING threshold interrupt with the threshold voltages TR0 to TR3 (registers 15 to 18). A programmable measurement persistance time (see register 29) helps to avoid threshold indications caused by spikes.  $U_{M2-M3}$  is the voltage between the pins M2 and M3 which derives from TIP and RING.

Data Sheet 34 2000.09.04

### **Functional Description**

Figure 16 Threshold Interrupt: TIP-RING

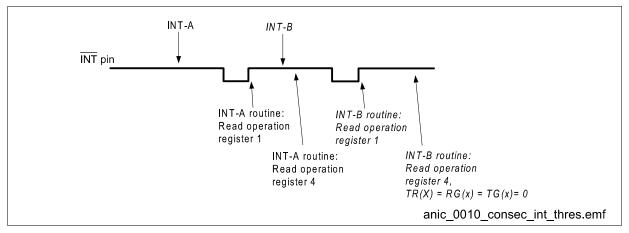

When there are two consecutive threshold interrupts (e.g. "INT-A" followed by "INT-B", see **Figure 17**) and INT-B happens before the interrupt service routine of INT-A could read register 4, the source of INT-B will be read together with the source of INT-A in register 4 (Bits TR(x), RG(x) and TG(x)). As reading register 4 clears the bits TONE(0) and TONE(1), the later starting interrupt service routine of INT-B can't find a source for this interrupt in register 4 (Bits TR(x) = RG(x) = TG(x) = 0). Therefore, the host must ignore the interrupt service routine of INT-B and use the values of the former routine.

Figure 17 Example for Consecutive Threshold Interrupts

Data Sheet 35 2000.09.04

### **Functional Description**

## 4.10 ANIC Clocking

Any master clock frequency between 16.384 MHz and 33 MHz can be used as the ANIC synchronizes to the incoming frame sync (FSC).

The DCDCCLK or a synchronous clock should be used to clock a DCDC converter to supply the ANIC-A. This will prevent intermodulation in between the VDDA and the A/D or D/A converters of the ANIC-A.

### 4.11 Test Modes

## 4.11.1 Data Loops

To test the chip datapath the following digital loops are available (see Figure 6):

- PCM loop to test the correct connection to the PCM Interface (see bit PCM\_LOOP in register 10). The PCM input data will be send back exactly in the next PCM frame.

- ANIC-A loop to test the ANIC-A and ANIC-D (see bit ANIC-A\_LOOP in register 10).

Functional test loop. The functionallity of the ANIC-D and the digital isolation interface of the ANIC-A can be checked.

## 4.12 Support Package

The ANIC can be programmed to pass individual country specific requirements. This can be done by downloading different coefficients into the CRAM using the ANICON control software. For the calculation of these coefficients a coefficient computing program called ANICOS will be provided.

The ANICOS software is a project-oriented Windows-based program. On-line help is available and the validity of user inputs checked automatically, enabling users to obtain optimized sets of coefficients to program the ANIC quickly and easily.

ANICOS calculates coefficients for the following filters.

#### AC Filters:

- Impedance matching to adapt the system to the required line impedance of the local loop (return loss calculation),

- Frequency response correction for both receive and transmit paths,

- Level adjustment for both receive and transmit paths,

- Transhybrid balancing

#### DC Filters:

DC characteristic

Data Sheet 36 2000.09.04

## Preliminary Functional Description

#### Ringing:

- Ringer impedance

- Ring detect (level and frequency)

#### Miscellaneous:

- · Ringing signal

- · Level Metering

- Metering signals detection (level and frequency)

After defining the required inputs for ANICOS, the user can start calculating the filter coefficients. All calculation results are stored in the result file which can be displayed in the ANICOS program. Some of the calculations are also displayed graphically to enable the product designer to verify the required behaviour quickly, and make any additional optimization manually.

The following calculations are displayed graphically:

- · Return loss.

- · Input impedance,

- Frequency response in receive and transmit path (locus diagram),

- Transhybrid loss.

ANICOS produces both a result file and a byte file. The byte file contains the programming bytes, including the filter coefficients. An important feature of the ANICOS software is the automatic verification of the calculated coefficients against criteria necessary to maintain overall system stability.

Data Sheet 37 2000.09.04

**Digital Interfaces**

## 5 Digital Interfaces

The digital interfaces consist of a Serial Control Interface (SCI) and a PCM Interface. Both interfaces operate up to 2048 kHz.

As described in **Chapter 4.10**, ANIC uses master clock frequencies from 16.384 up to 33 MHz. In this document, functionality is described for  $f_{MCLK} = 24.576$  MHz.

## 5.1 Sample Rates

The internal datapath clock is synchronized to the frame synchronization (FSC) signal. For PCM frame based systems this clock is 8 kHz.

In this document, functionality is described using this 8 kHz FSC.

However, the ANIC can be synchronized to all frame synchronization (FSC) signals between 6 and 12 kHz, although the used FSC frequencies are in a range between 8 and 12 kHz as shown in **Table 6**. The FSC limits can be computed:

Example: f<sub>MCLK</sub> = 24.576 MHz, no predivider is used

$f_{FSC} = f_{FRAC} / 2048$

with

$f_{FRAC,min} = f_{MCLK} / [1+32767/32768] > f_{MCLK} / 2$

$f_{FRAC.max} = f_{MCLK} / [1+1/65536)] < f_{MCLK}$

Therefore:

Frame sync lower limit:  $f_{FSC,min} > f_{MCLK} / 4096 = 6 \text{ kHz}$ Frame sync upper limit:  $f_{FSC,max} < f_{MCLK} / 2048 = 12 \text{ kHz}$

Within one frame the ANIC can be programmed to provide one (8 k sampling mode) ore two (16 k sampling mode) samples (see register 14, bit 16k).

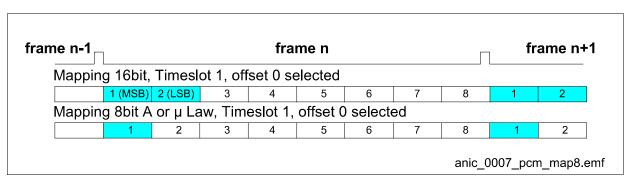

Following power-up ANIC is programmed to the 16-bit linear mode and 8 k sampling mode. If the companding mode is switched on (register 14, bit COMP = 1), ANIC sends and receives the 8 bit A-law companded data on one PCM slot.

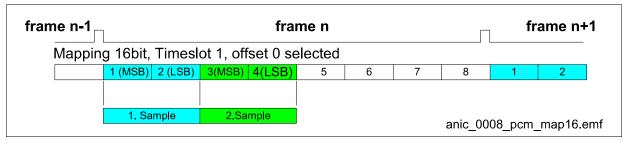

Using the 16 kHz mode, the PCM decimation filter from 16 to 8 kHz is switched off and four consecutive time slots are used to provide these two samples. Within that mode, **only** the 16 bit linear data transmission is possible.

Data Sheet 38 2000.09.04

**Digital Interfaces**

#### 5.2 PCM Interface

A serial PCM Interface is used for voice transfer. The PCM Interface consists of 4 pins:

Table 3 PCM Interface Pins

| DATCLK | PCM-Clock, 512 kHz to 2048 kHz        |

|--------|---------------------------------------|

| FSC    | Frame Synchronization Clock           |

| DATIN  | Receive Voice input for PCM Highway   |

| DATOUT | Transmit Voice output for PCM Highway |

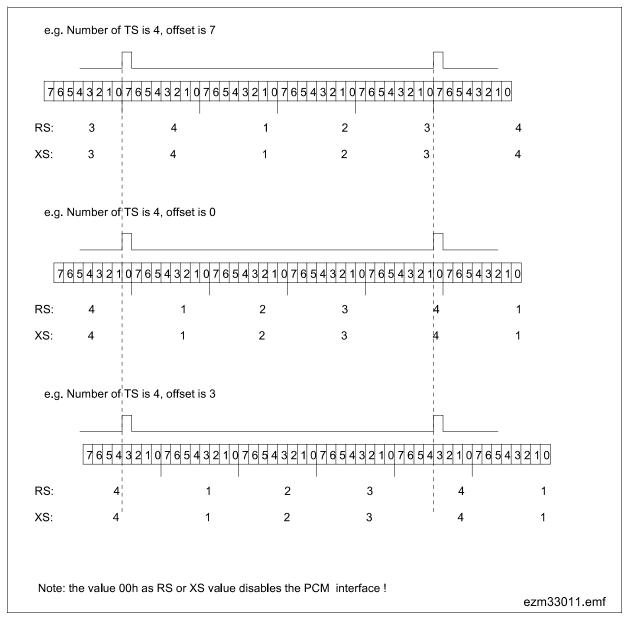

The data rate of the interface can vary from 512 kb/s to 2048 kb/s. A frame may consist of up to 32 time slots of 8 bits each. Receive and transmit time slots can be programmed individually in normal mode (PCM) and in linear mode. An extra delay of up to 7 clocks, valid for all channels, as well as the sampling slope<sup>1)</sup> may be programmed. In order to provide high bandwith for modem and fax application also a sample rate of 16 kHz can be programmed. In this mode the ANIC will use four consecutive timeslots for the two 16 kHz linear coded samples within one frame.

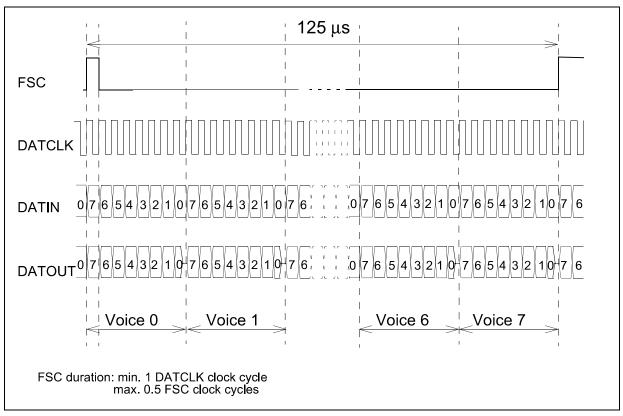

The frame sync (FSC) input determines the beginning of the receive and transmit time slots. The FSC must have a minimum duration of one DATCLK cycle (see Chapter 9.5.4). The DATCLK clock is the signal to synchronize the voice transfer on both lines DATOUT and DATIN. Bytes in all channels are serialized to 8 bit width (normal mode) or 16 bit width (linear mode) and MSB first. For configuration of the PCM Interface see register 14.

Note: In order to avoid bus contention, bit 0 (LSB) at DATOUT is only asserted during the positive half-cycle of DATCLK, and is high-impedance during the negative half-cycle of DATCLK. At power up, the PCM interface is inactive (tri-state condition) until the relevant registers are programmed.

**Table 4** and **Table 5** list the possible clock rates for the PCM Interface at  $f_{FSC}$  = 8 kHz. Clock rates such as 768 kHz and 1536 kHz are also supported.

**Table 6** shows the FSC frequency and number of time slots per PCM frame for a given SCI-clock f<sub>DCLK</sub> and the 8 k or 16 k sampling mode. **Figure 18** to **Figure 21** are graphical illustrations of the values in **Table 6**.

Figure 22, Table 4 and Table 5 illustrate the PCM Interface timing and time slots mapping, respectively.

**Figure 25** shows examples of time slot offset referenced to FSC. The recieve and transmit time slots are offset by the same amount of DATCLK periods.

Data Sheet 39 2000.09.04

<sup>1)</sup> Data can be sampled at the rising or falling edge of the clock.

**Digital Interfaces**

Table 4 8 kHz Sampling Rate (8 k sampling mode, f<sub>FSC</sub> = 8 kHz)

|         | PCM-Clock<br>Frequency (kHz) | Time Slots (per highway) | Datarate<br>(kbits/s per highway) |

|---------|------------------------------|--------------------------|-----------------------------------|

|         | 512                          | 8                        | 512                               |

|         | 1024                         | 16                       | 1024                              |

|         | 2048                         | 32                       | 2048                              |

| Formula | f                            | f/64                     | f                                 |

Table 5 16 kHz Sampling Rate (16 k sampling mode, f<sub>FSC</sub> = 8 kHz)

|         | PCM-Clock<br>Frequency (kHz) | Time Slots (per highway) | Datarate<br>(kbits/s per highway) |

|---------|------------------------------|--------------------------|-----------------------------------|

|         | 512                          | 4                        | 512                               |

|         | 1024                         | 8                        | 1024                              |

|         | 2048                         | 16                       | 2048                              |

| Formula | f                            | f/128                    | f                                 |

Table 6 SCI-Clock, FSC, Sampling Mode and Time Slot Interdependency<sup>1)</sup>

| SCI-Clock <sup>2)</sup> f <sub>DCLK</sub> (kHz) /<br>Sampling Mode | maximum<br>FSC Frequency<br>f <sub>FSC</sub> (kHz) | Time Slots<br>per Frame | Figure        |  |

|--------------------------------------------------------------------|----------------------------------------------------|-------------------------|---------------|--|

|                                                                    | 8                                                  | 32                      |               |  |

| 2048 / 8 k                                                         | 10                                                 | 16                      | see Figure 18 |  |

|                                                                    | 12                                                 | 8                       |               |  |

| 2048 / 16 k                                                        | 10                                                 | 8                       | see Figure 19 |  |

| 1004 / 16 k                                                        | 8                                                  | 16                      | ooo Figure 20 |  |

| 1024 / 16 k                                                        | 11                                                 | 8                       | see Figure 20 |  |

| E10 / 16 k                                                         | 10                                                 | 16                      | F: 04         |  |

| 512 / 16 k                                                         | 11                                                 |                         | see Figure 21 |  |

<sup>1)</sup> for  $f_{MCLK} = 24.576 \text{ MHz}$

Data Sheet 40 2000.09.04

$<sup>^{2)}\,</sup>$  Serial Control Interface SCI-Clock on pin DCLK (f\_{DCLK})

## **Digital Interfaces**

Figure 18 Time Slots for 8 k Sampling Mode and SCI-Clock 2048 kHz

Figure 19 Time Slots for 16 k Sampling Mode and SCI-Clock 2048 kHz

Data Sheet 41 2000.09.04

### **Digital Interfaces**

Figure 20 Time Slots for 16 k Sampling Mode and SCI-Clock 1024 kHz

Figure 21 Time Slots for 16 k Sampling Mode and SCI-Clock 512 kHz

Data Sheet 42 2000.09.04

Preliminary Digital Interfaces

## **5.2.1 PCM Interface Timing Examples**

Figure 22 Example for Single Clock Rate, 512 kb/s

For special purposes the DATIN and DATOUT pins may be strapped together, and form a bi-directional datapin.

Figure 23 Mapping of Linear and Companded Data into PCM Slots for 8 kHz

Data Sheet 43 2000.09.04

#### **Digital Interfaces**

Figure 24 Mapping of Linear Data into PCM Slots for 16 kHz

Note: Using the 16 kHz sampling mode only the linear mode is availble.

Figure 25 PCM Interface Frames

Data Sheet 44 2000.09.04

**DOUT**

**Digital Interfaces**

#### 5.3 Serial Control Interface

Data output

The Serial Control Interface is used to communicate with an external host, e.g., a microcontroller.

The internal configuration registers, the auxiliary ports, and the Coefficient RAM (CRAM) of the ANIC are programmable via the Serial Control Interface. This Interface consists of 4 pins:

| Table 7 | Serial Control Interface Pins                          |

|---------|--------------------------------------------------------|

| CS      | Chip select input, for enabling interface (active low) |

| DCLK    | SCI-Clock input, f <sub>DCLK</sub> = 1 kHz to 2048 kHz |

| DIN     | Data input                                             |

The host asserts  $\overline{\text{CS}}$  low to initialize a communication with ANIC. Following a falling edge of  $\overline{\text{CS}}$  the first 8 bits received at DIN determine the command type. The CLK clocks can be continously running or gated. However, there must be 16 low CLK pulses within the  $\overline{\text{CS}}$  low interval to complete a READ or WRITE transaction.

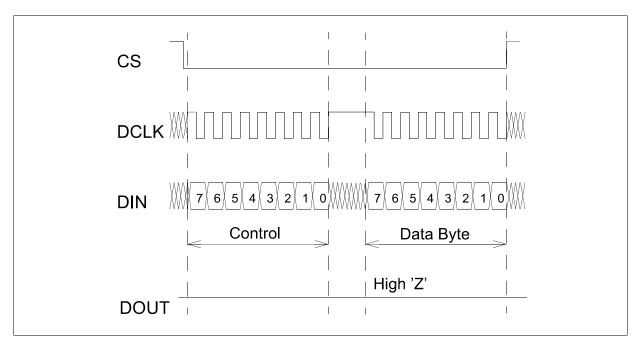

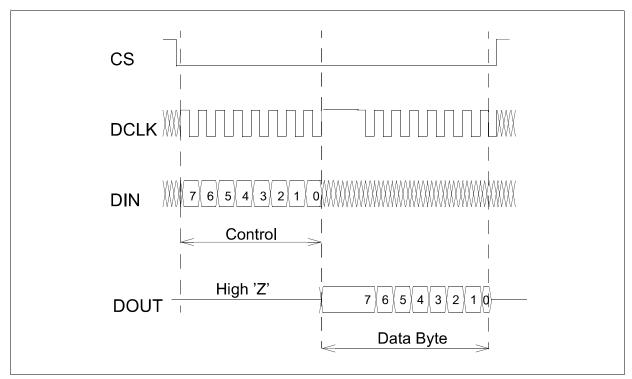

Figure 26 Example for a Write Access

Data Sheet 45 2000.09.04

**Digital Interfaces**

If the first eight bits received via DIN specify a read-command, the ANIC will start to response via DOUT with its specific register byte

Figure 27 Example for a Read Access

Note: In order to avoid bus contention, bit 0 (LSB) at DOUT is only asserted during the positive half-cycle of DCLK, and is high-impedance during the negative half-cycle of DCLK.

The data transfer is synchronized by DCLK. DIN is latched at the falling edge of DCLK, while DOUT changes with the rising edge of DCLK. During execution of a command which is followed by output data (read command), the device will not accept any new command via DIN. The data transfer sequence can be interrupted by setting CS to high.

To reduce the number of connections to the  $\mu$  Controller DIN and DOUT may be strapped together to a bidirectional datapin.

Data Sheet 46 2000.09.04

#### **Digital Interfaces**

## 5.3.1 Programming of ANIC via the Serial Control Interface

|     |                    |   | CMD co | CMD command word |            |            |   |   |

|-----|--------------------|---|--------|------------------|------------|------------|---|---|

| Bit | 7                  | 6 | 5      | 1                | 3          | 2          | 1 | 0 |

| Dit |                    |   |        |                  |            |            |   |   |

|     | R/nW <sup>1)</sup> | I | А3     | <b>A2</b>        | <b>A</b> 1 | <b>A</b> 0 | 1 | x |

<sup>1)</sup> R/nW is the MSB and will be transferred first.

| x<br>A[3:0] |               | Don't care Offset address for basic and indexed addressing mode.     |

|-------------|---------------|----------------------------------------------------------------------|

|             | A[3:0] = 0000 | Offset 0                                                             |

|             |               |                                                                      |

|             | A[3:0] = 1111 | Offset 15                                                            |

| I           |               | Use of index register                                                |

|             | <b>I</b> = 0  | Use offset address A[3:0] (Basic addressing mode)                    |

|             | I = 1         | Use Index register + offset address A[3:0] (Indexed addressing mode) |

| R/nW        |               | Read or write data                                                   |

|             | R/nW = 0      | Write Data to ANIC                                                   |

· RAM address of Indexregister: 0

R/nW = 1

256 Byte RAM: Oh to FFh

128 Byte CRAM: 100h to 17Fh

• Calculating the Index (I) and Offset (O) out of the C/RAM-address (Adr):

Read data from ANIC

I = INT (Adr / 16) \* 8 (I must be a multiple of 8)

O = Adr - 2 \* I (O must be between 0 and 15)

0 **X**

Preliminary Digital Interfaces

## 5.3.1.1 Example for Write Operation

Write data value FBh to RAM-address AFh = 10101111

#### First Step:

Write Indexregister.

• Write Command on DIN:

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----|---|---|---|---|---|---|---|---|--|

|     | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X |  |

Index on DIN:

I = INT (Adr / 16) \* 8 = INT (AFh / 16) \* 8 = 01010000 = 50h.

Bit

| ſ | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|

|   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

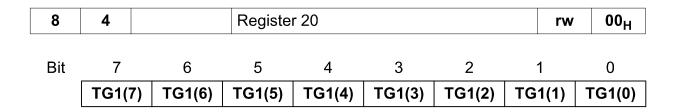

#### **Second Step:**