Wire bondable Low profile vertical SiCap WLSC528.247 0201

# General description

WLSC Capacitors targets power supplies decoupling and filtering of active devices. They are based on PICS Integrated Passive technology.

This product is a single 47pF capacitor in a 0201 package size. Other capacitance values and other package size are available as a single die or capacitor array; please feel free to contact us.

WLSC capacitors are directly mounted on the PCB application using die bonding and wire bonding processes. Standard FR4 PCB can be used. The bottom electrode is in Ti (0.1 µm)/Ni (0.3µm)/Au (0.2µm) and the top electrode is in gold. Other top finishings such as Aluminum are available on request.

#### Key features

- · Compatible with MLCC footprint

- Ultra-high stability of capacitance value:

- Temperature 70ppm/K (-55 °C to +150 °C)

- Voltage <0.02%/Volt</li>

- o Negligible capacitance loss through ageing

- Low profile 0.1mm

- Small size 0.5 x 0.25 mm (0201 format)

- Break down voltage: 150V

- Low leakage current

- High reliability

- High operating temperature (up to 150 °C)

- Compatible with high temperature cycling during manufacturing operations (exceeding 300 °C)

- Compatible with EIA 0201 footprint

- Applicable for standard wire bonding assembly (ball and wedge)

#### Key applications

- Any demanding applications, such as medical, aerospace, automotive industrial...

- Supply decoupling / filtering of active device

- High reliability applications

- Battery operated devices

- High temperature applications

- High volumetric efficiency (i.e. capacitance per unit volume)

Rev. 1.09

Rev. 1.09

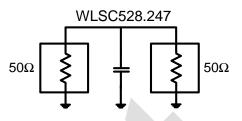

#### Functional diagram

The next figure provides implementation set-up diagram.

Figure 1 Block Diagram

# Electrical performances

| Symbol            | Parameter                         | Conditions                               | Min. | Тур. | Max.                                  | Unit              |

|-------------------|-----------------------------------|------------------------------------------|------|------|---------------------------------------|-------------------|

| С                 | Capacitance value                 | @+25°C                                   | -    | 47   | -                                     | pF                |

| $\Delta C_{P}$    | Capacitance tolerance (1)         | @+25°C                                   | -15  | 1    | +15                                   | %                 |

| T <sub>OP</sub>   | Operating temperature             |                                          | -55  | 20   | 150                                   | °C                |

| T <sub>STG</sub>  | Storage temperature (2)           |                                          | -70  | -    | 165                                   | °C                |

| $\Delta C_{T}$    | Capacitance temperature variation | -55 °C to 150 °C                         | -    | 70   | -                                     | ppm/K             |

| $RV_{DC}$         | Rated voltage (3)                 |                                          | -    | -    | 68 <sup>4)</sup><br>61 <sup>(5)</sup> | $V_{DC}$          |

| BV                | Break down voltage                | @+25°C                                   | 150  | -    | -                                     | V                 |

| $\Delta C_{RVDC}$ | Capacitance voltage variation     | From 0 V to RV <sub>DC</sub> ,<br>@+25°C | -    | -    | 0.02                                  | %/V <sub>DC</sub> |

| IR                | Insulation resistor               | @RV <sub>DC</sub> , +25°C, 120s          | -    | 10   | -                                     | GΩ                |

| ESL               | Equivalent Serial Inductance (6)  | @+25°C, SRF shunt<br>mode                | -    | 5    | -                                     | рН                |

| ESD               | HBM stress (7)                    | JS-001-2017                              | 500  | -    | -                                     | V                 |

Table 1 - Electrical performances

- (1): other tolerance available upon request

(2): without packaging

(3): Lifetime is voltage and temperature dependent, please refer to application note 'Lifetime of 3D capacitors'

- (4): 10 years of intrinsic life time prediction at 100°C continuous operation

- (5): 10 years of intrinsic life time prediction at 150°C continuous operation

- (6): Measured

- (7): please refer to application note 'ESD Challenge in 3D Murata Integrated Passive technology'

# Impedance characteristic of 47pF WLSC in Shunt mode

# (muo) N 10<sup>2</sup> 10<sup>2</sup> 10<sup>3</sup> 10<sup>9</sup> 10<sup>1</sup> Freq. Hz

Figure 2 - 47pF WLSC measurement results (Impedance characteristic versus Frequency in shunt mode)

# Schematic of 47pF of WLSC in Shunt mode

Figure 3 - 47pF WLSC measurement schematic

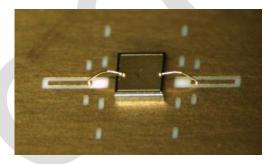

# **Example of surface mounted 0101**

Figure 4 - micro picture of 0101 WLSC mounted on board

# Pinning definition

Figure 5 Pinning definition

| pin # | Symbol  | Coordinates X / Y |

|-------|---------|-------------------|

| 1     | Signal1 | 0.0 / 0.0         |

| 2     | GND     | Backside          |

Table 2 - Pining description. Reference (0,0) located at the centre of the die.

# **Ordering Information**

Murata Integrated Passive Devices delivers products with AQL level II (0.65). Tighter quality levels are available upon request.

| Part number         | Package                    |                   |                                                              |  |  |

|---------------------|----------------------------|-------------------|--------------------------------------------------------------|--|--|

| (16NC)              | Packaging                  | Finishing         | Description                                                  |  |  |

| 935 146 528 247-F1T | 6" FFC <sup>(1)</sup>      | Au <sup>(2)</sup> | 47pF/0201 – 1 bondpad – 0.5 x 0.25mm x 0.10mm <sup>(3)</sup> |  |  |

| 935 146 528 247-F2T | 8" FFC <sup>(1)</sup>      | Au <sup>(2)</sup> | 47pF/0201 – 1 bondpad – 0.5 x 0.25mm x 0.10mm <sup>(3)</sup> |  |  |

| 935 146 528 247-E1T | 6" grip ring <sup>1)</sup> | Au <sup>(2)</sup> | 47pF/0201 – 1 bondpad – 0.5 x 0.25mm x 0.10mm <sup>(3)</sup> |  |  |

| 935 146 528 247-W0T | Waffle pack<br>400 units   | Au <sup>(2)</sup> | 47pF/0201 – 1 bondpad – 0.5 x 0.25mm x 0.10mm <sup>(3)</sup> |  |  |

Table 3 - Packaging and ordering information

- (1) Other film frame carrier are possible on request

- (2) Au = TiW (0.3 $\mu$ m) / Au (3 $\mu$ m)

- (3) Refer to Figure 7

| Product Name<br>(12NC) | Die Name  | Description                                              |

|------------------------|-----------|----------------------------------------------------------|

| WLSC528.247            | WO0201247 | WLSC 47pF/0201/BV150 – 1 bondpad – 0.5 x 0.25mm x 0.10mm |

Table 4 - Die information

#### Pad Metallization

This wire bondable capacitor is delivered as standard with the bottom electrode in TiNiAu (Ti (0.1 µm)/Ni (0.3µm)/Au (0.2µm)) and top electrode in TiWAu (TiW (0.3µm) / Au (3µm)).

Other Metallization, such as thick Gold or Aluminum top pads are possible on request.

Silicon dies are not sensitive to humidity, please refer to applications notes 'Assembly Notes' section 'Handling precautions and storage'.

#### Material regulation

This product is RoHS compliant at the time of publication. For further information about regulation compliancy, please ask your sales representative.

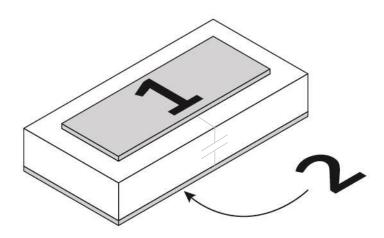

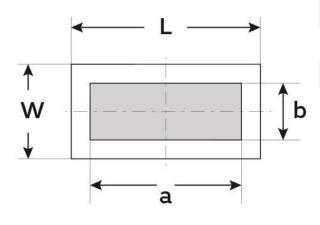

# Package outline

The product is delivered as a bare silicon die.

Figure 6 - Layout view

| L (mm)    | W (mm)     | T (mm)                 | a (mm) | b (mm) |

|-----------|------------|------------------------|--------|--------|

| 0.5 ±0.03 | 0.25 ±0.03 | 0.10 <sub>±0.015</sub> | 0.357  | 0.150  |

Table 5 - Dimensions and tolerances

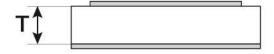

Figure 7 - Package outline drawing

Figure 8 - Package isometric view

Rev. 1.09

#### Assembly

Wire bondable Silicon capacitors are directly mounted on the PCB application using die bonding and wire bonding.

It is applicable for standard wire bonding assembly (ball and wedge).

For further information, please see our mounting application note.

The attachment techniques recommended by Murata on the customer's substrates are fully detailed in specific documents available on our website. To assure the correct use and proper functioning of Murata capacitors please download the assembly instructions on <a href="https://www.murata.com/en-us/products/capacitor/siliconcapacitors">https://www.murata.com/en-us/products/capacitor/siliconcapacitors</a> and read them carefully.

Figure 9 Scan this QR Code to access the Murata Silicon Capacitor web page

#### Packaging format

Please refer to application note 'Products Storage Conditions and Shelf Life'.

# **Film Frame Carrier:**

With UV curable dicing tape (UV performed).

Good dies are identified using the SINF electronic mapping format. No ink is added on wafer to label other dies.

A A B B S MARITA

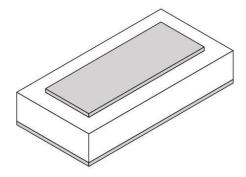

Figure 10 FF070 Frame with a 6" wafer

Figure 11 FF108 Frame with a 6" wafer

| Frame<br>Reference   | Frame<br>Style | Inside<br>diameter<br>A | Outside<br>diameter<br>B | Width<br>C | Thickness | Pin<br>location<br>E | Pin<br>location<br>F |

|----------------------|----------------|-------------------------|--------------------------|------------|-----------|----------------------|----------------------|

| FF070 <sup>(1)</sup> | DTF-2-6-1      | 7.638"                  | 8.976"                   | 8.346"     | 0.048"    | 2.370"               | 2.5"                 |

| FF108 (1)            | DTF-2-8-1      | 9.842"                  | 11.653"                  | 10.866"    | 0.048"    | 2.381"               | 2.5"                 |

Table 6 - Frame dimensions (inches)

(1) or equivalent

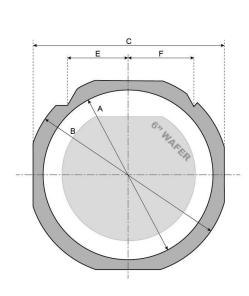

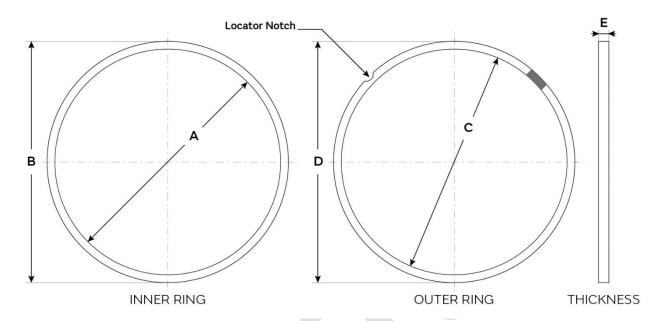

# **Expander grip ring 6" diameter:**

With UV curable dicing tape (UV not performed)

Good dies are identified using the SINF electronic mapping format. No ink is added on wafer to label other dies.

Figure 12 - Grip Ring drawing

| Grip Ring Style | А      | В      | С      | D      | E      | Locator<br>Notch |

|-----------------|--------|--------|--------|--------|--------|------------------|

| GRP-2620-6 (1)  | 7.670" | 7.973" | 7.975" | 8.280" | 0.236" | None             |

Table 7 - Frame dimensions (inches)

(1) or equivalent

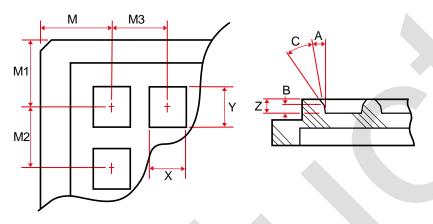

# Waffle pack:

Please refer to application note 'Waffle Pack Chip Carrier Handling & Opening Procedure'. Dies are not flipped in the waffle pack cavity (wire bond pad up).

Table 8 - Waffle pack drawing

| External dimensions | Max. capacity | Pocket<br>length X | Pocket<br>width Y | Pocket<br>depth Z |

|---------------------|---------------|--------------------|-------------------|-------------------|

| 2 inches            | 20 x 20       | 0.61 ±0.05         | 0.43 ±0.05        | 0.23 ±0.05        |

Table 9 - Waffle pack dimensions (mm)

| M                     | M1                    | M2                    | М3                    | Α        |

|-----------------------|-----------------------|-----------------------|-----------------------|----------|

| 6.40 <sub>±0.08</sub> | 6.40 <sub>±0.08</sub> | 2.01 <sub>±0.05</sub> | 2.01 <sub>±0.05</sub> | 5° ±1/2° |

Table 10 - Waffle pack dimensions (mm)

Rev. 1.09

#### **Definitions**

#### Data sheet status

Objective specification: This data sheet contains target or goal specifications for product development.

**Preliminary specification:** This data sheet contains preliminary data; supplementary data may be published later.

**Product specification:** This data sheet contains final product specifications.

#### Limiting values

Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those given in the Electrical performances sections of this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### Application information

Where application information is given, it is advisory and does not form part of the specification.

#### **Revision history**

| Revision | Date       | Description    | Author |

|----------|------------|----------------|--------|

| 1.00     | 06/08/2011 | Creation       | OGA    |

| 1.09     | 21/09/2020 | General update | OGA    |

#### Disclaimer / Life support applications

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Murata customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Murata for any damages resulting from such improper use or sale.

Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights.

Murata Integrated Passive Solutions S.A. makes no representation that the use of its products in the circuits described herein, or the use of other technical information contained herein, will not infringe upon existing or future patent rights. The descriptions contained herein do not imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith. Specifications are subject to change without notice.