# PART NUMBER 54164DMB-ROCV

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

Qualified Suppliers List of Distributors (QSLD)

Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

T-46-09-05

## 54164/DM74164 8-Bit Serial In/Parallel Out Shift Registers

#### **General Description**

These 8-bit shift registers feature gated serial inputs and an asynchronous clear. A low logic level at either serial input inhibits entry of the new data, and resets the first flip-flop to the low level at the next clock pulse, thus providing complete control over incoming data. A high logic level on either input enables the other input, which will then determine the state of the first flip-flop. Data at the serial inputs may be changed while the clock is high or low, but only information meeting the setup and hold time requirements will be entered. Clocking occurs on the low-to-high level transition of the clock input. All inputs are diode-clamped to minimize transmission-line effects.

#### **Features**

- Gated (enable/disable) serial inputs

- Fully buffered clock and serial inputs

- Asynchronous clear

- Typical clock frequency 36 MHz

- Typical power dissipation 185 mW

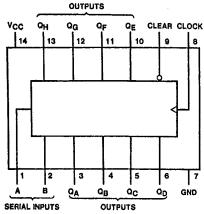

#### **Connection Diagram**

#### Dual-in-Line Package

#### TL/F/6552-1

Order Number 54164DMQB, 54164FMQB or DM74164N See NS Package Number J14A, N14A or W14B

#### **Function Table**

| Inputs |          |   |   | Outputs         |                 |     |                 |  |

|--------|----------|---|---|-----------------|-----------------|-----|-----------------|--|

| Clear  | Clock    | A | В | QA              | QB              |     | QH              |  |

| L      | Х        | х | X | L               | L               | ,   | L               |  |

| Н      | L        | Х | Х | Q <sub>A0</sub> | Q <sub>B0</sub> |     | $Q_{H0}$        |  |

| Н      | 1 ↑      | H | Н | н               | $Q_{An}$        |     | $Q_{Gn}$        |  |

| H      | 1        | L | Х | L               | $Q_{An}$        |     | $Q_{Gn}$        |  |

| H      | <u> </u> | X | L | L               | Q <sub>An</sub> | ••• | Q <sub>Gn</sub> |  |

H = High Level (steady state), L = Low Level (steady state)

X = Don't Care (any input, including transitions)

Transition from low to high level

$Q_{AO}$ ,  $Q_{BO}$ ,  $Q_{HO}$  = The level of  $Q_{A}$ ,  $Q_{B}$ , or  $Q_{H}$ , respectively, before the indicated steady-state input conditions were established.

$Q_{An},\,Q_{Gn}=$  The level of  $Q_A$  or  $Q_G$  before the most recent  $\, \uparrow \,$  transition of the clock; indicates a one-bit shift.

4

5.5V

Absolute Maximum Ratings (Note)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage Input Voltage

Operating Free Air Temperature Range

-55°C to +125°C **DM74**

Storage Temperature Range

-65°C to +150°C

0°C to +70°C

#### T-46-09-05

Note: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

#### **Recommended Operating Conditions**

| Symbol          | Parameter                      |            | 54164 |     |      | DM74164 |     |      | Units |

|-----------------|--------------------------------|------------|-------|-----|------|---------|-----|------|-------|

|                 |                                |            | Min   | Nom | Max  | Min     | Nom | Max  | Units |

| Vcc             | Supply Voltage                 |            | 4.5   | 5   | 5.5  | 4.75    | 5   | 5.25 | ٧     |

| V <sub>IH</sub> | High Level Input Voltage       |            | 2     |     |      | 2       |     |      | ٧     |

| VIL             | Low Level input                | Voltage    |       |     | 0.8  |         |     | 0.8  | ٧     |

| Іон             | High Level Outp                | ut Current |       |     | -0.4 |         |     | -0.4 | mA    |

| loL             | Low Level Outpu                | ut Current |       |     | 8    |         |     | 8    | mA    |

| fclk            | Clock Frequency                | (Note 4)   |       |     | 25   | 0       |     | 25   | MHz   |

| tw              | Pulse Width<br>(Note 4)        | Clock      | 20    |     |      | 20      |     |      | ns    |

|                 |                                | Clear      | 20    |     |      | 20      |     |      |       |

| tsu             | Data Setup Time (Note 4)       |            | 15    |     |      | 15      |     |      | ns    |

| t <sub>H</sub>  | Data Hold Time (Note 4)        |            | 0     |     |      | 5       |     |      | ns    |

| TA              | Free Air Operating Temperat@re |            | -55   |     | 125  | 0       |     | 70   | °C    |

# Electrical Characteristics over recommended operating free air temperature range (unless otherwise noted)

| Symbol           | Parameter                            | Conditions                                                                      |                     | Min | Typ<br>(Note 1) | Max   | Units |

|------------------|--------------------------------------|---------------------------------------------------------------------------------|---------------------|-----|-----------------|-------|-------|

| VI               | Input Clamp Voltage                  | V <sub>CC</sub> = Min, I <sub>1</sub>                                           | = -14 mA            |     |                 | -1.5  | ٧     |

| V <sub>OH</sub>  | High Level Output<br>Voltage         | V <sub>CC</sub> = Min, I <sub>O</sub><br>V <sub>IL</sub> = Max, V <sub>II</sub> |                     | 2.4 | 3.2             |       | ٧     |

| VoL              | Low Level Output<br>Voltage          | V <sub>CC</sub> = Min, I <sub>O</sub><br>V <sub>IH</sub> = Min, V <sub>IL</sub> |                     |     | 0.2             | 0.4   | ٧     |

| lı .             | Input Current @ Max<br>Input Voltage | V <sub>CC</sub> = Max, V                                                        | <sub>j</sub> = 5.5V |     |                 | 1     | mA    |

| l <sub>H</sub>   | High Level Input Current             | V <sub>CC</sub> = Max, V                                                        | ı = 2.4V            |     |                 | 40    | μΑ    |

| l <sub>I</sub> L | Low Level Input Current              | $V_{CC} = Max, V_1 = 0.4V$                                                      |                     |     |                 | -1.6  | mA    |

| los              | Short Circuit<br>Output Current      | V <sub>CC</sub> = Max                                                           | 54                  | -10 |                 | -27.5 | 4     |

|                  |                                      | (Note 2)                                                                        | DM74                | -9  |                 | -27.5 | mA    |

| lcc              | Supply Current                       | V <sub>CC</sub> = Max (Note 3)                                                  |                     |     | 37              | 54    | mA    |

Note 1: All typicals are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

Note 2: Not more than one output should be shorted at a time.

Note 3: I/Co is measured with all outputs open, SERIAL Inputs grounded, the CLOCK Input at 2.4V, and a momentary ground, then 4.5V, applied to the CLEAR input. Note 4:  $T_A = 25$ °C and  $V_{CC} = 5V$ .

# $\textbf{Switching Characteristics} \text{ at V}_{\text{CC}} = 5 \text{V and T}_{\text{A}} = 25 ^{\circ} \text{C (See Section 1 for Test Waveforms and Output Load)}$

| Symbol           | Parameter                                          | From (Input)<br>To (Output) | $R_L = 800\Omega$      |     |                        | T-46-09-05 |       |  |

|------------------|----------------------------------------------------|-----------------------------|------------------------|-----|------------------------|------------|-------|--|

|                  |                                                    |                             | C <sub>L</sub> = 15 pF |     | C <sub>L</sub> = 50 pF |            | Units |  |

|                  |                                                    |                             | Min                    | Max | Min                    | Max        |       |  |

| fMAX             | Maximum Clock Frequency                            |                             | 25                     |     |                        |            | MHz   |  |

| tpLH             | Propagation Delay Time<br>Low to High Level Output | Clock to<br>Output          |                        | 27  |                        | 30         | ns    |  |

| t <sub>PHL</sub> | Propagation Delay Time<br>High to Low Level Output | Clock to<br>Output          |                        | 32  |                        | 37         | ns    |  |

| t <sub>PHL</sub> | Propagation Delay Time<br>High to Low Level Output | Clear to<br>Output          |                        | 36  |                        | 42         | ns    |  |

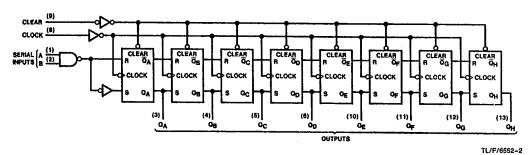

### **Logic Diagram**

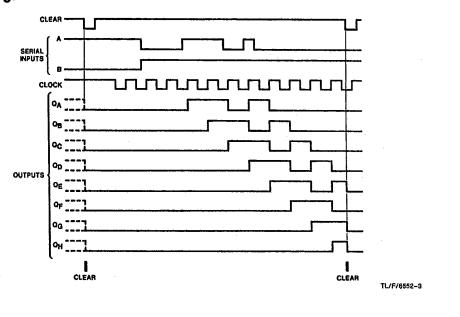

# **Timing Diagram**

4-169