# **ICs for Communications**

Mini IOM®-2 Controller MICO

PEF 2015 Version 1.1

Data Sheet 12.97

| PEF 2015<br>Revision His         | story:                      | Current Version: Data Sheet 12.97                                                                                                       |  |  |

|----------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Previous Ver                     | sion: Prelimi               | nary Data Sheet 05.97                                                                                                                   |  |  |

| Page<br>(in previous<br>Version) | Page<br>(in new<br>Version) | Subjects (major changes since last revision)                                                                                            |  |  |

| 34, 58                           | 34, 58                      | MFAIR: new reset value = 00xx xxxx <sub>B</sub>                                                                                         |  |  |

| 34, 60                           | 34, 60                      | CIFIFO: new reset value = 0xxx xxxx <sub>B</sub>                                                                                        |  |  |

| 34, 69, 70                       | 34, 69, 70                  | VNSR register: Reset value corrected to 02H (Version bits for MICO V1.1: 0010)                                                          |  |  |

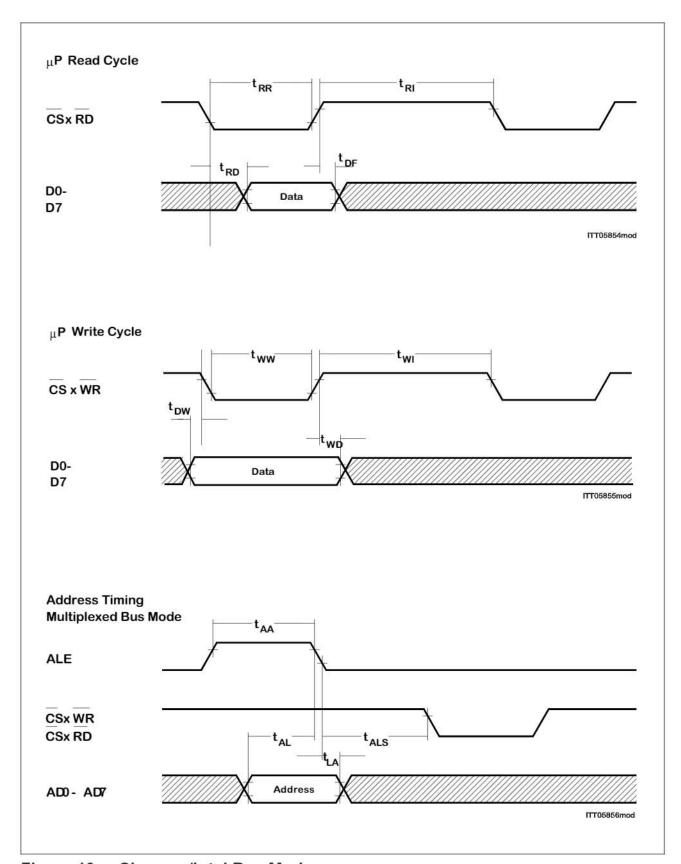

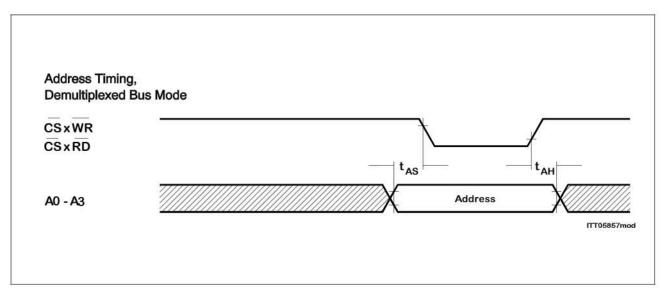

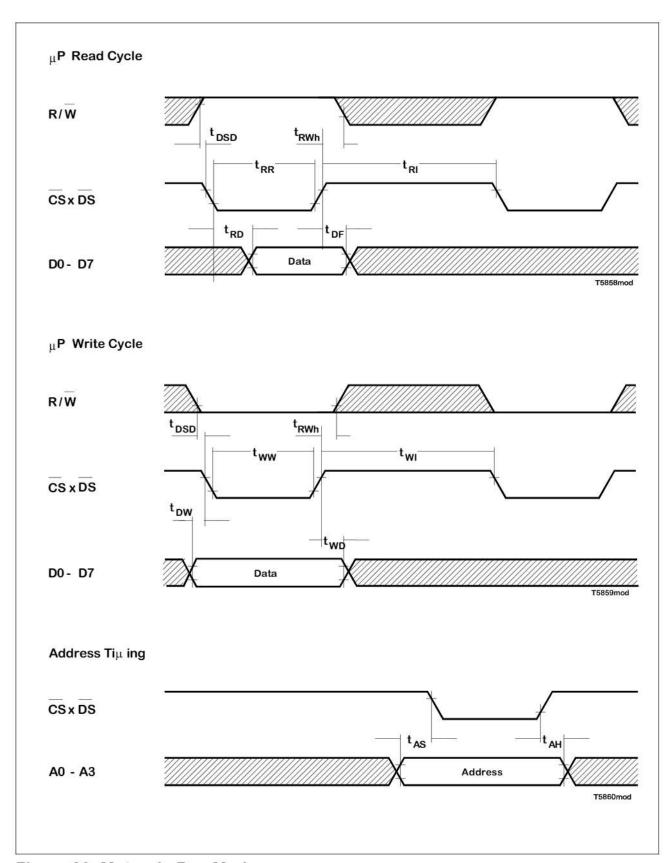

| -                                | 75, 78                      | New timing in Motorola mode: $t_{RWh} = 10$ ns max. (R/W hold time from DS)                                                             |  |  |

| 77, 78, 80                       | 75, 76, 78                  | Timing value and definition changed: $t_{DW}$ = 0 ns min. (Data set-up time to $\overline{CSxWR}$ / $\overline{CSxDS}$ in write access) |  |  |

|                                  |                             |                                                                                                                                         |  |  |

|                                  |                             |                                                                                                                                         |  |  |

|                                  |                             |                                                                                                                                         |  |  |

|                                  |                             |                                                                                                                                         |  |  |

|                                  |                             |                                                                                                                                         |  |  |

|                                  |                             |                                                                                                                                         |  |  |

#### Edition 12.97

This edition was realized using the software system FrameMaker→.

Published by Siemens AG,

HL DT CE

© Siemens AG 1997.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5                                                              | Overview Features Pinning Diagram (top view) 8 Pin Description Logic Symbol Functional Block Diagram                                                                                                                                                                                                                  | 9                                      |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                                                  | Functional Description Configurable Interface CFI Serial PCM Interface Microprocessor Interface Memory Structure and Switching Pre-processed Channels, Layer-1 Support Special Functions                                                                                                                              | 14<br>15<br>15                         |

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.4.1<br>3.4.2                                              | Operational Description  Microprocessor Interface Operation Clocking Reset  MICO Operation PCM-Interface Configurable Interface                                                                                                                                                                                       | 18<br>19<br>19<br>20                   |

| 3.4.3<br>3.4.4<br>3.5<br>3.5.1<br>3.5.2<br>3.5.2.1<br>3.5.2.2<br>3.5.2.3<br>3.5.2.4<br>3.5.3 | Switching Functions Special Functions Initialization Procedure Hardware Reset MICO Initialization Register Initialization Control Memory Reset Initialization of Pre-processed Channels Initialization of the Upstream Data Memory (DM) Tristate Field Activation of the PCM- and CFI-Interfaces                      | 24<br>29<br>29<br>29<br>29<br>30<br>31 |

| 4.1<br>4.2<br>4.2.1<br>4.2.1.1<br>4.2.1.2<br>4.2.1.3<br>4.2.1.4<br>4.2.1.5<br>4.2.1.6        | Registers Summary Register Address Arrangement Detailed Register Description PCM-Interface Registers PCM-Mode Register (PMOD) Bit Number per PCM-Frame (PBNR) PCM-Offset Downstream Register (POFD) PCM-Offset Upstream Register (POFU) PCM-Clock Shift Register (PCSR) PCM-Input Comparison Mismatch Register (PICM) | 33<br>35<br>35<br>35<br>36<br>36       |

| 4.2.2   | Configurable Interface Registers                            | 39 |

|---------|-------------------------------------------------------------|----|

| 4.2.2.1 | Configurable Interface Mode Register 1 (CMD1)               | 39 |

| 4.2.2.2 | Configurable Interface Mode Register 2 (CMD2)               | 41 |

| 4.2.2.3 | Configurable Interface Bit Number Register (CBNR)           | 44 |

| 4.2.2.4 | Configurable Interface Time Slot Adjustment Register (CTAR) | 44 |

| 4.2.2.5 | Configurable Interface Bit Shift Register (CBSR)            | 45 |

| 4.2.2.6 | Configurable Interface Subchannel Register (CSCR)           | 47 |

| 4.2.3   | Memory Access Registers                                     | 48 |

| 4.2.3.1 | Memory Access Control Register (MACR)                       |    |

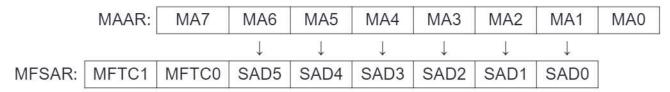

| 4.2.3.2 | Memory Access Address Register (MAAR)                       | 52 |

| 4.2.3.3 | Memory Access Data Register (MADR)                          |    |

| 4.2.4   | Synchronous Transfer Registers                              | 54 |

| 4.2.4.1 | Synchronous Transfer Data Register (STDA)                   | 54 |

| 4.2.4.2 | Synchronous Transfer Data Register B (STDB)                 | 54 |

| 4.2.4.3 | Synchronous Transfer Receive Address Register A (SARA)      | 55 |

| 4.2.4.4 | Synchronous Transfer Receive Address Register B (SARB)      | 56 |

| 4.2.4.5 | Synchronous Transfer Transmit Address Register A (SAXA)     | 56 |

| 4.2.4.6 | Synchronous Transfer Transmit Address Register B (SAXB)     | 57 |

| 4.2.4.7 | Synchronous Transfer Control Register (STCR)                |    |

| 4.2.5   | Monitor/Feature Control Registers                           | 58 |

| 4.2.5.1 | MF-Channel Active Indication Register (MFAIR)               | 58 |

| 4.2.5.2 | MF-Channel Subscriber Address Register (MFSAR)              | 59 |

| 4.2.5.3 | Monitor/Feature Control Channel FIFO (MFFIFO)               | 60 |

| 4.2.6   | Status/Control Registers                                    | 60 |

| 4.2.6.1 | Signaling FIFO (CIFIFO)                                     | 60 |

| 4.2.6.2 | Timer Register (TIMR)                                       |    |

| 4.2.6.3 | Status Register (STAR)                                      | 62 |

| 4.2.6.4 | Command Register (CMDR)                                     |    |

| 4.2.6.5 | Interrupt Status Register (ISTA)                            | 65 |

| 4.2.6.6 | Mask Register MICO (MASK)                                   |    |

| 4.2.6.7 | Operation Mode Register (OMDR)                              |    |

| 4.2.6.8 | Version Number Status Register (VNSR)                       |    |

| 4.3     | Register Changes compared to the EPIC                       |    |

| 4.3.1   | PMOD                                                        | 70 |

| 4.3.2   | PCSR                                                        |    |

| 4.3.3   | PICM                                                        |    |

| 4.3.4   | CMD1                                                        |    |

| 4.3.5   | CSCR                                                        |    |

| 4.3.6   | ISTA                                                        |    |

| 4.3.7   | MASK                                                        |    |

| 4.3.8   | VSNR                                                        | 70 |

| 5       | Application Examples                                        | 71 |

12.97

| 5.1 | Access Network             |

|-----|----------------------------|

| 6   | Electrical Characteristics |

| 7   | Package Outlines           |

5

Overview

#### 1 Overview

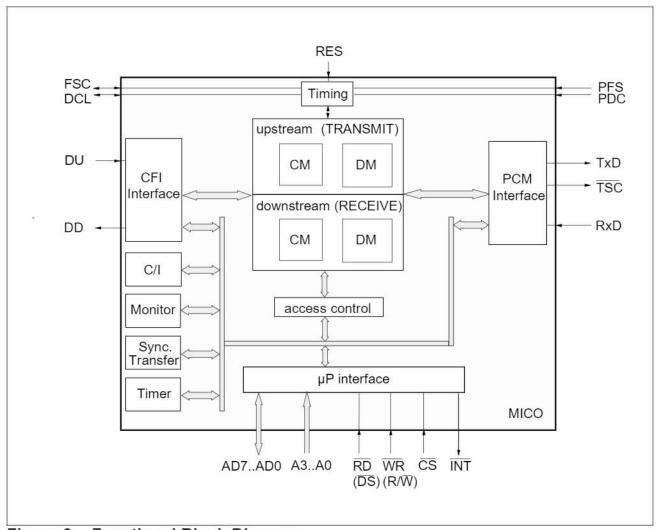

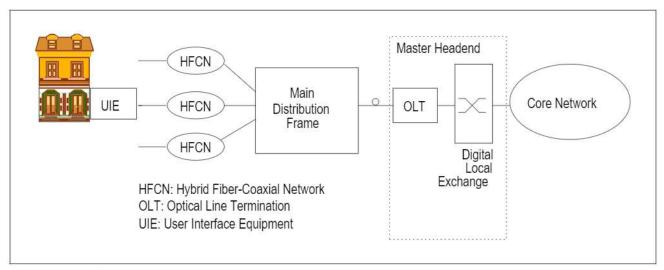

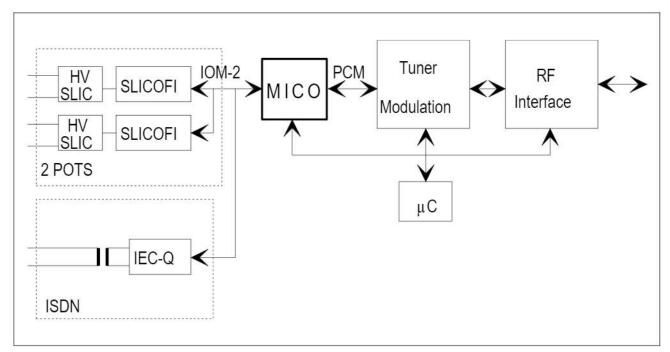

The Mini IOM-2 Controller MICO (PEF 2015) is an interface controller optimized for small line card applications or Intelligent NTs. It is derived from the EPIC core. The MICO supports up to 16 analog subscribers (up to 8 using the SLICOFI) or up to 8 ISDN-BA subscribers.

The MICO is used as an interface device on linecards between the subscriber circuits and the network. Therefore it provides one IOM-2 interface for connection of up to 8 ISDN-BA subscribers or up to 16 analog subscribers (up to 8 using the SLICOFI). The MICO also provides one PCM interface for connection to the main system. Additionally the MICO is used to control the subscriber circuits via the C/I and monitor channel as specified in the IOM-2 specification. A parallel  $\alpha P$  interface is provided for device programming.

Furthermore the MICO contains a nonblocking switching unit with a flexible time slot assignment between the IOM-2 and the PCM interface.

The MICO may substitute the EPIC (PEB 2055) or EPIC-S (PEB 2054) in applications that deal with a maximum number of 8 ISDN or 16 analog (8 using the SLICOFI) subscribers connected via one IOM-2 port.

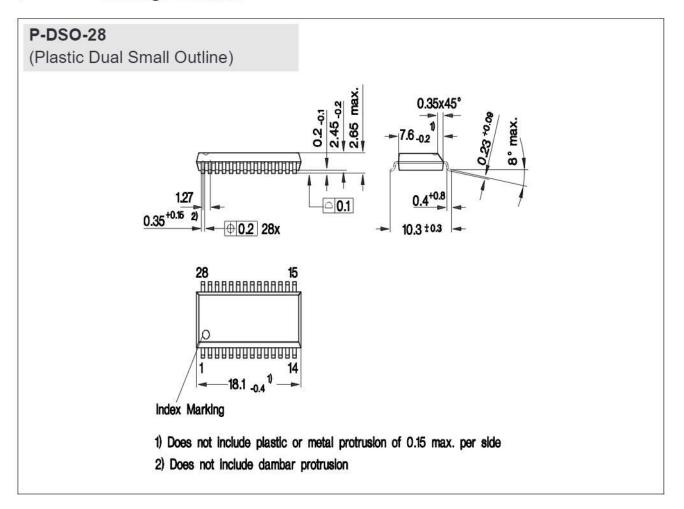

The MICO is fabricated using SIEMENS advanced CMOS technology and is available in a P-DSO-28 package.

### Mini IOM<sup>®</sup>-2 Controller MICO

**PEF 2015**

#### Data Sheet for the Version 1.1

**CMOS**

#### 1.1 Features

#### **Functions**

- Interface controller between IOM-2 and PCM for up to 8 ISDN-BA or 16 analog subscribers (up to 8 analog subscribers using the SLICOFI)

- B-channel (64 kbit/s) and D-channel (16 kbit/s) switching

- Configurable Interface (1 port)

- Configurable for IOM-, SLD- and PCM-applications

- Programmable clock shift

- Single or double data clock

- PCM interface (1 port)

- Freely programmable time slot assignment to up to 128 PCM time slots

- Tristate control signal for external driver

- Single or double data clock

- C/I-channel Handler with a 9-Byte FIFO

- Buffered Monitor Handler with a 16-Byte FIFO

- 7-bit hardware timer

#### General

- Siemens/Intel or Motorola type ∞P interface

- Supply Voltage: 5 V

- Extended temperature range -40°C to +85°C

- P-DSO-28 package

| Туре     | Package  |

|----------|----------|

| PEF 2015 | P-DSO-28 |

Overview

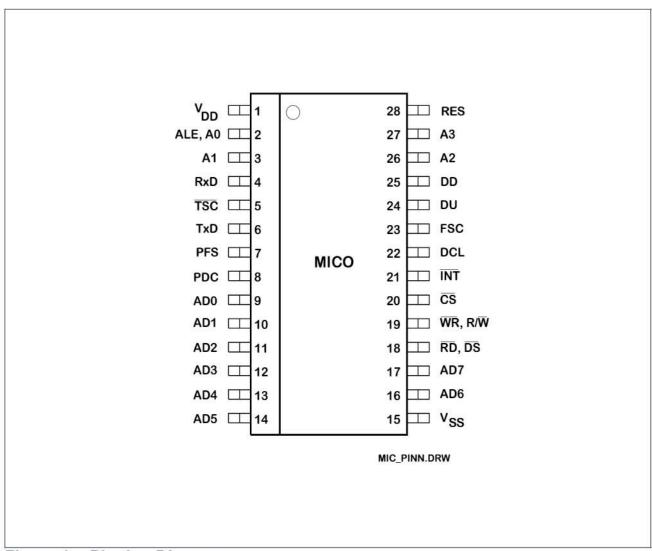

### 1.2 Pinning Diagram

(top view)

8

Figure 1 Pinning Diagram

12.97

Overview

## 1.3 Pin Description

| Pin<br>No. | Symbol   | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                  |  |

|------------|----------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 23         | FSC      | I/O                     | Frame Synchronization Input or output in IOM-configuration. Direction indication in SLD-mode.                                                                                                                                                                                             |  |

| 22         | DCL      | I/O                     | Data Clock Input or output in IOM-configuration. Slave clock in SLD mode. Single or double data rate in IOM-configuration, single data rate in SLD-mode.                                                                                                                                  |  |

| 24         | DU, SIP4 | I, I/O (OD)             | Data Upstream, Input IOM- or PCM-configuration. Serial Interface Port, SLD configuration.                                                                                                                                                                                                 |  |

| 25         | DD, SIP0 | O, I/O (OD)             | Data Downstream, Output IOM- or PCM-configuration Serial Interface Port, SLD configuration.  Depending on the bit OMDR:COS this line has push-pull or open drain characteristic.  For unused or unassigned channels or when bit OMDR:CSB is reset the pin is in the state high impedance. |  |

| 7          | PFS      | I                       | PCM-Interface Frame Synchronization                                                                                                                                                                                                                                                       |  |

| 8          | PDC      | I                       | PCM-Interface Data Clock Single or double data rate.                                                                                                                                                                                                                                      |  |

| 6          | TxD      | 0                       | Transmit PCM-Interface Data Time-slot oriented data is shifted out of the MICOs upstream data memory on this line. For time-slots which are flagged in the tristate data memory or when bit OMDR:PSB is reset the pin is set in the state high impedance.                                 |  |

| 5          | TSC      | 0                       | Tristate Control Supplies a control signal for an external driver. This line is 'low' when corresponding TxD outputs are valid. During reset this line is high.                                                                                                                           |  |

| 4          | RxD      | I                       | Receive PCM-Interface Data Time-slot oriented data is received on this pin and forwarded into the downstream data memory of the MICO.                                                                                                                                                     |  |

#### Overview

| Pin<br>No.                                  | Symbol                                                                               | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                  |  |

|---------------------------------------------|--------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9<br>10<br>11<br>12<br>13<br>14<br>16<br>17 | AD0, D0<br>AD1, D1<br>AD2, D2<br>AD3, D3<br>AD4, D4<br>AD5, D5<br>AD6, D6<br>AD7, D7 | I/O                     | Address/Data Bus; multiplexed bus mode. Transfers addresses from the $\alpha P$ to the MICO and data between the $\alpha P$ and the MICO.  Data Bus; demultiplexed bus mode. Transfers data between the $\alpha P$ and the MICO.  When driving data the pins have push pull characteristic, otherwise they are in the state high impedance.               |  |

| 2<br>3<br>26<br>27                          | A0/ALE<br>A1<br>A2<br>A3                                                             |                         | Address Bus, demultiplexed mode. Transfers addresses from the ∞P to the MICO.  Address Latch Enable, multiplexed mode. ALE controls the on chip address latch in multiplexed bus mode. While ALE is 'high' the latch is transparent. The falling edge latches the current address.  Note: During reset A0 and A1 are evaluated to determine the bus mode. |  |

| 18                                          | RD, DS                                                                               | 1                       | Read, active low, Siemens/Intel bus mode. When 'low' a read operation is indicated.  Data Strobe, Motorola bus mode. A rising edge marks the end of a read or write operation.                                                                                                                                                                            |  |

| 19                                          | WR,<br>R/W                                                                           | I                       | Write, active low, Siemens/Intel bus mode. When 'low' a write operation is indicated.  Read/Write, Motorola bus mode. When 'high' a valid ¤P access identifies a read operation, when 'low' it identifies a write access.                                                                                                                                 |  |

| 20                                          | CS                                                                                   | I                       | Chip Select, active 'low'. A low on this line selects the MICO for a read/write operation.                                                                                                                                                                                                                                                                |  |

#### Overview

| Pin<br>No.           | Symbol          | Input (I)<br>Output (O) | Function                                                                                                                                                                                  |  |

|----------------------|-----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 21 <u>INT</u> O (OD) |                 | O (OD)                  | Interrupt, active low. This line is activated when the MICO requests an interrupt. Due to the open drain (OD) characteristic of INT multiple interrupt sources can be connected together. |  |

| 28                   | RES             | I                       | Reset A 'high' forces the MICO into reset state.                                                                                                                                          |  |

| 15                   | V <sub>SS</sub> | 1                       | Ground (0 V)                                                                                                                                                                              |  |

| 1                    | V <sub>DD</sub> | 1                       | Supply Voltage (5 V +/- 5%)                                                                                                                                                               |  |

Overview

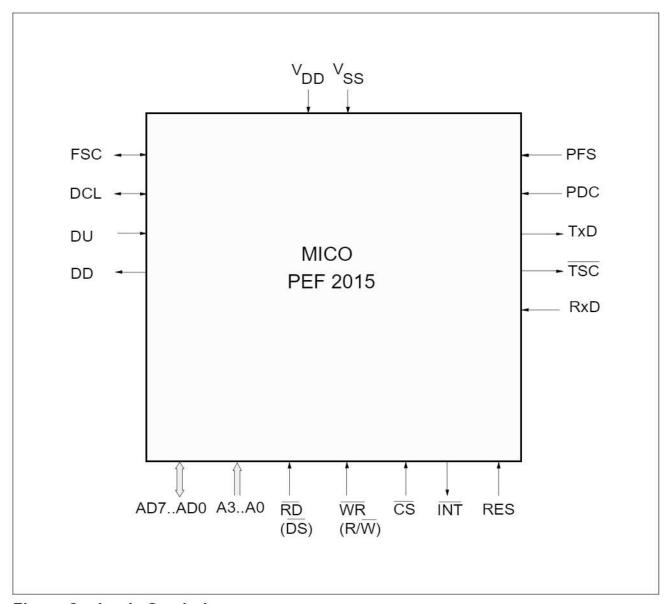

### 1.4 Logic Symbol

Figure 2 Logic Symbol

Overview

### 1.5 Functional Block Diagram

Figure 3 Functional Block Diagram

**Functional Description**

#### 2 Functional Description

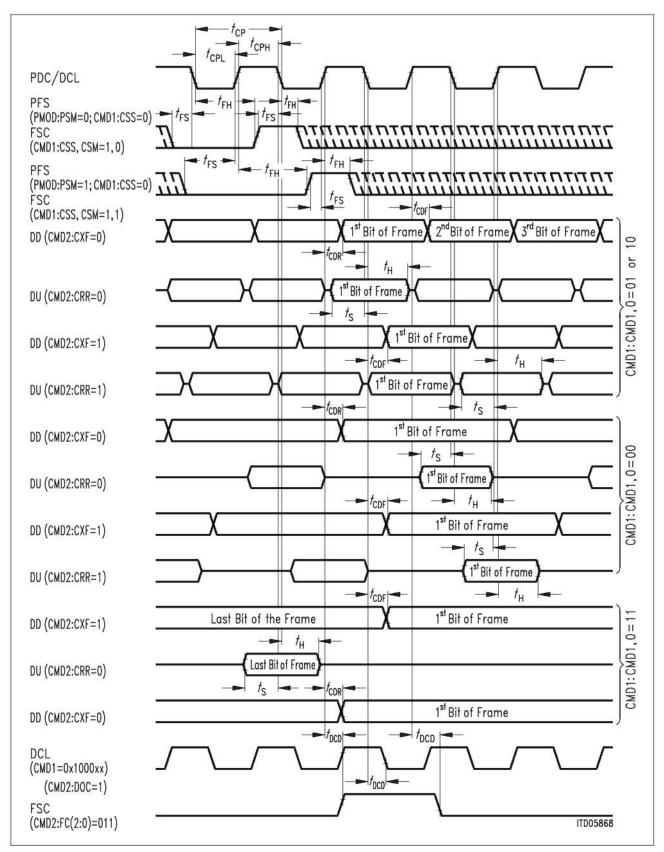

#### 2.1 Configurable Interface CFI

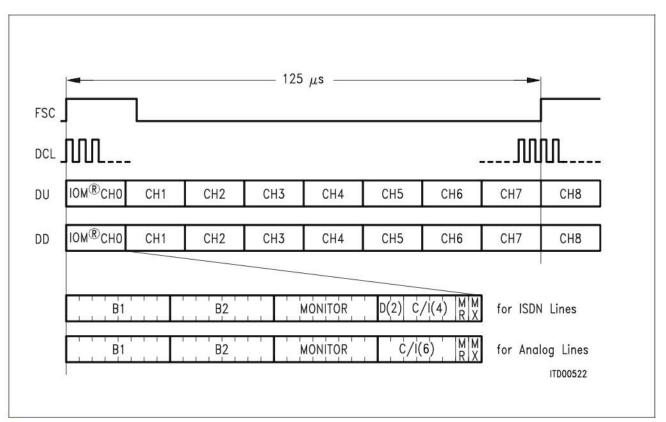

The integrated CFI is a one port serial interface. It comprises two serial data lines (upstream DU and downstream DD), a data clock input or output DCL and a frame sync input or output FSC in IOM-applications. The clock frequency is either equal to the data rate or twice the data rate. The CFI can be configured to data rates up to 8.192 Mbit/s.

The CFI is typically used in IOM-2 or SLD configuration to connect layer-1 devices.

Figure 4 shows the IOM-2 Interface structure in Line Card Mode:

Figure 4 IOM®-2 Frame Structure with 2.048 Mbit/s Data Rate

#### 2.2 Serial PCM Interface

The PCM interface formats the data transmitted or received at the PCM-highways. It consists of one port comprising a data receive (RxD), a data transmit (TxD) and an output tristate indication line (TSC). The PCM interface is supplied with a frame signal (PFS) and a PCM clock (PDC).

Data rates up to 8.192 Mbit/s are supported. To properly clock the PCM interface a PDC signal with a frequency equal or twice the data rate has to be applied to the MICO.

#### **Functional Description**

#### 2.3 Microprocessor Interface

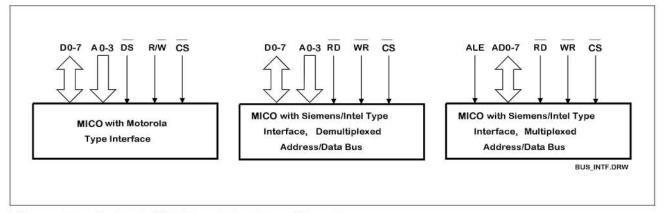

The MICO supports Siemens/Intel and Motorola type microprocessors. In the Siemens/Intel type  $\alpha P$  interface either a multiplexed or a demultiplexed bus structure may be chosen.

The interface type is selected by pulling up or down two address pins during the reset state (refer to **Table 1**, "**Selection of Bus Interface**," on page 18). Pulling-up the appropriate pins selects the Motorola type  $\alpha P$  interface, fixing them to ground chooses the Siemens/Intel type  $\alpha P$  interface mode. In case of a multiplexed Siemens/Intel bus structure address pin A0 takes over the ALE functionality.

The microprocessor interface consists of the following lines:

- Data Bus, 8-bit wide, AD7..AD0

- · Address bus, 4-bit wide, A3..A0

- Chip select, CS

- Two read/write control lines: RD and WR (Intel mode) or DS and R/W (Motorola mode)

- Interrupt, INT

- · Reset, RES

Figure 5 Selectable Bus Interface Structures

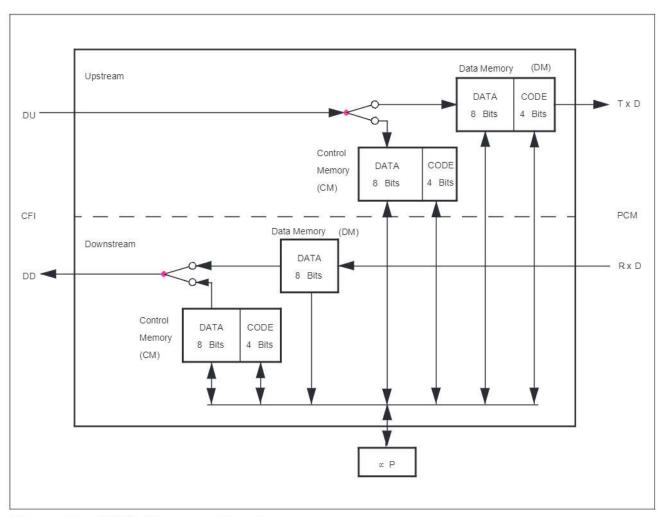

#### 2.4 Memory Structure and Switching

The memory block of the MICO performs the switching functionality. It consists of four sub blocks:

- Upstream data memory

- Downstream data memory

- Upstream control memory

- Downstream control memory.

The PCM-interface reads periodically from the upstream (writes periodically to the downstream) data memory (cyclical access), see **figure 6**.

The CFI reads periodically the control memory and uses the extracted values as a pointers to write to the upstream (read from the downstream) data memory (random

#### **Functional Description**

access). In the case of C/l- or signaling channel applications the corresponding data is stored in the control memory. In order to select the application of choice, the control memory provides a code portion.

The control memory is accessible via the  $\infty$ P-interface. In order to establish a connection between CFI time slot A and PCM-interface time slot B, the B-pointer has to be loaded into the control memory location A.

Figure 6 MICO Memory Structure

#### **Functional Description**

#### 2.5 Pre-processed Channels, Layer-1 Support

The MICO supports the monitor/feature control and control/signaling channels according to SLD- or IOM-2 interface protocol.

The monitor handler controls the data flow on the monitor/feature control channel either with or without active handshake protocol. To reduce the dynamic load of the CPU a 16-byte transmit/receive FIFO is provided.

The signaling handler supports different schemes (D-channel + C/l-channel, 6-bit signaling, 8-bit signaling).

In downstream direction the relevant content of the control memory is transmitted in the appropriate CFI time slot. In the case of centralized ISDN D-channel handling, a 16-kbit/s D-channel received at the PCM-interface is included.

In upstream direction the signaling handler monitors the received data. Upon a change it generates an interrupt, the channel address is stored in the 9-byte deep C/I FIFO and the actual value is stored in the control memory. In 6-bit and 8-bit signaling schemes a double last look check is provided.

#### 2.6 Special Functions

- Synchronous transfer.

- This utility allows the synchronous  $\alpha P$ -access to two independent channels on the PCM- or CFI-interface. Interrupts are generated to indicate the appropriate access windows.

- 7-bit hardware timer.

The MICO offers one hardware timer. It can be used to cyclically interrupt the CPU, to determine the double last look period or to generate a proper CFI-multiframe synchronization signal.

- Frame length checking.

The PFS-period is internally checked against the programmed frame length.

#### 3 Operational Description

The MICO, designed as a flexible line-card controller, has the following main applications:

- Digital line cards, with the CFI typically configured as IOM-2, IOM-1 (MUX) or SLD.

- Analog line cards, with the CFI typically configured as IOM-2 or SLD.

- Intelligent NTs, where the MICO's ability to configure the CFI as a PCM interface is utilized.

To operate the MICO the user must be familiar with the device's microprocessor interface, interrupt structure and reset logic.

The device is derived from the EPIC core. With some restrictions it is therefore programmable like the EPIC.

#### 3.1 Microprocessor Interface Operation

The MICO is programmed via an 8-bit parallel interface that can be selected to be

- (1) Motorola type, with control signals DS, R/W, and CS.

- (2) Siemens / Intel non-multiplexed bus type, with control signals WR, RD, and CS.

- (3) Siemens / Intel multiplexed address/data bus type, with control signals ALE, WR, RD, and CS.

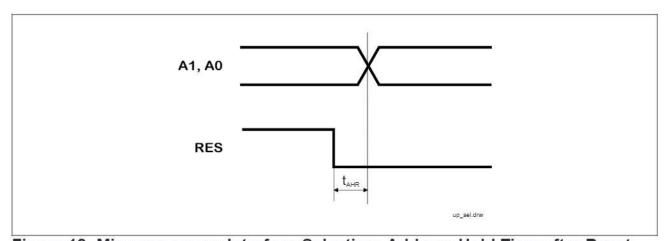

The selection is performed via supplying address pins A0 and A1 during reset as follows:

Table 1 Selection of Bus Interface

| A1, A0 during reset | Bus Interface                                                                     |

|---------------------|-----------------------------------------------------------------------------------|

| 11                  | Motorola type (1)                                                                 |

| 00                  | Siemens / Intel type, non-multiplexed (2)                                         |

| 01 or 10            | Siemens / Intel type, multiplexed (3) Pin A0 will take over the ALE functionality |

Note: When selecting the multiplexed bus mode, it has to be ensured that during a MICO device reset the A0/ALE pin receives the appropriate level and no ALE transfers by the  $\infty$ C affect the interface type selection (refer also to figure **18**, page 75).

When using the Siemens / Intel multiplexed interface, the MICO is addressed with even addresses only (i.e. AD0 always 0), which allows data always to be transferred in the low data byte. This simplifies the use of 16 bit Siemens / Intel type processors.

For a non-multiplexed bus structure the OMDR:RBS bit is needed in addition to the address lines A3..0. OMDR:RBS (Register Bank Selection) selects one of two register banks.

18

RBS = '1' selects a set of registers used for device initialization (e.g. CFI and PCM interface initialization).

RBS = '0' switches to a group of registers necessary during operation (e.g. connection programming).

The OMDR register containing the RBS bit can be accessed with either value of RBS.

#### Interrupts

An interrupt of the MICO is indicated by activating the INT-line. The detailed cause of the request can be determined by reading the ISTA register.

The INT-output is level active. It stays active until all interrupt sources have been serviced. If a new status bit is set while an interrupt is being serviced, the INT stays active. However, for the duration of a write access to the MASK-register the INT-line is deactivated. When using an edge-triggered interrupt controller, it is thus recommended to rewrite the MASK-register at the end of any interrupt service routine.

Every interrupt source can be selectively masked by setting the respective bit of the MASK-register. Such masked interrupts will not be indicated in the ISTA-register, nor will they activate the  $\overline{\text{INT}}$ -line.

#### 3.2 Clocking

To operate properly, the MICO always requires a PDC-clock.

To synchronize the PCM-side, the MICO should normally also be provided with a PFS-strobe. In most applications, the DCL and FSC will be output signals of the MICO, derived from the PDC via prescalers.

If the required CFI-data rate cannot be derived from the PDC, DCL and FSC can also be programmed as input signals. This is achieved by setting the MICO CMD1:CSS-bit. Frequency and phase of DCL and FSC may then be chosen almost independently of the frequency and phase of PDC and PFS. However, the CFI-clock source **must** still be synchronous to the PCM-interface clock source; i.e. the clock source for the CFI-interface and the clock source for the PCM-interface must be derived from the same master clock.

#### 3.3 Reset

A reset pulse of at least 4 PDC clock cycles has to be applied at the RES pin. The reset pulse sets all registers to their reset values described in **section 4**.

The MICO is now in CM-reset mode (refer to **4.2.6.7**). As the hardware reset does not affect the MICO memories CM and DM, a 'software reset' of the CM has to be performed.

Subsequently the MICO can be programmed to CM-initialization, normal operation or test mode.

During reset the address pins A0 and A1 are evaluated to determine the bus interface type.

**Operational Description**

#### 3.4 MICO Operation

The MICO is principally an intelligent switch of PCM-data between two serial interfaces, the system interface (PCM-interface) and the configurable interface (CFI). Up to 128 channels per direction can be switched dynamically between the CFI and the PCM-interfaces. The MICO performs non-blocking space and time switching for these channels which may have a bandwidth of 16, 32, 64 or 128 kbit/s on a per device basis.

Both interfaces can be programmed to operate at different data rates of up to 8.192 Mbit/s. The PCM-interface consists of one duplex port with a tristate control signal. The configurable interface can be selected to provide either one duplex port or two bidirectional (I/O) ports.

The configurable interface incorporates a control block (layer-1 buffer) which allows the  $\propto P$  to gain access to the control channels of an IOM- (ISDN-Oriented Modular) or SLD- (Subscriber Line Data) interface. The MICO can handle the layer-1 functions buffering the C/I and monitor channels for IOM compatible devices and the feature control and signaling channels for SLD compatible devices. The layer-1 and codec devices are connected to the CFI, which is then configured to operate as IOM-2, SLD or multiplexed IOM-1 interface.

The configurable interface of the MICO can also be configured as plain PCM-interface i.e. without IOM- or SLD-frame structure. Since it's possible to operate the two serial interfaces at different data rates, the MICO can then be used to adapt two different PCM-systems.

The MICO can handle up to 8 ISDN-subscribers with their 2B+D channel structure or up to 16 analog subscribers with their 1B channel structure in IOM-configuration. In SLD-configuration up to 4 analog subscribers can be accommodated.

The system interface is used for the connection to a PCM-back plane. On a typical digital line card, the MICO switches the ISDN B-channels and, if required, also the D-channels to the PCM-back plane. Due to its capability to dynamically switch the 16-kbit/s D-channel, the MICO is one of the fundamental building blocks for networks with either central, decentral or mixed signaling and packet data handling architecture.

#### 3.4.1 PCM-Interface

The serial PCM-interface provides one port consisting of a data transmit (TxD), a data receive (RxD) and a tristate control ( $\overline{TSC}$ ) line. The transmit direction is also referred to as the upstream direction, whereas the receive direction is referred to as the downstream direction.

Data is transmitted and received at normal TTL /CMOS-levels, the output drivers being of the tristate type. Unassigned time slots may either be tristated, or programmed to transmit a defined idle value. The selection of the states "high impedance" and "idle value" can be performed with a two bit resolution. This tristate capability allows several devices to be connected together for concentrator functions. If the output driver

capability of the MICO should prove to be insufficient for a specific application, an external driver controlled by the  $\overline{\sf TSC}$  can be connected.

The **PCM-standby function** makes it possible to switch all PCM-output lines to high impedance with a single command. Internally, the device still works normally. Only the output drivers are switched off.

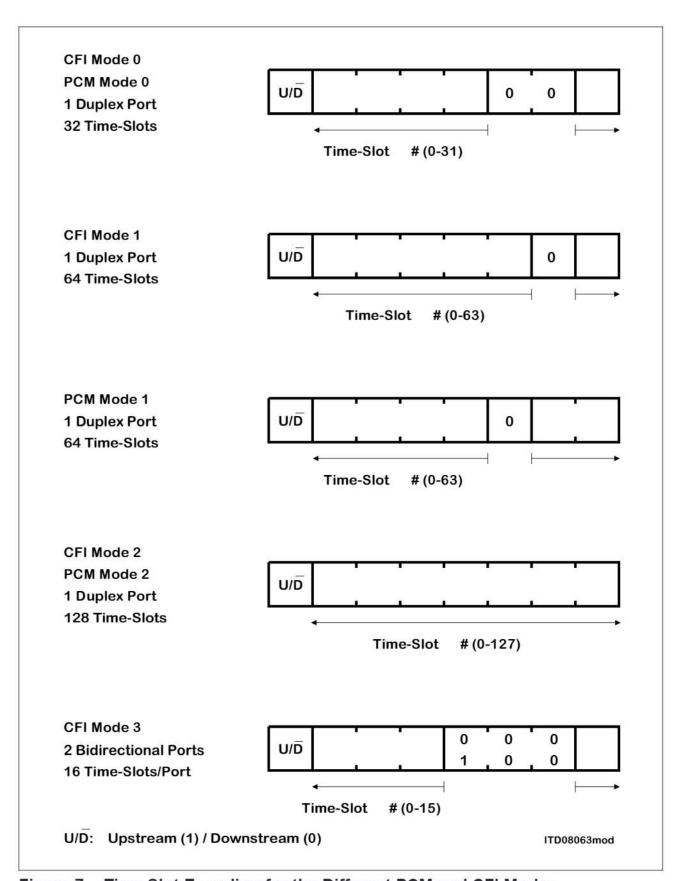

The number of time slots per 8-kHz frame is programmable in a wide range (from 4 to 128). In other words, the **PCM-data rate can range between 256 kbit/s up to 8.192 Mbit/s**. For time slot encoding refer to **figure 7**.

The number of bits per frame is defined by the **PCM-mode**. There are three PCM-modes.

The timing characteristics at the PCM-interface (data rate, bit shift, etc.) can be varied in a wide range.

The PCM-interface has to be clocked with a **PCM-Data Clock (PDC)** signal having a frequency equal to or twice the selected PCM-data rate. In **single clock rate** operation, a frame consisting of 32 time slots, for example, requires a PDC of 2048 kHz. In **double clock rate** operation, however, the same frame structure would require a PDC of 4096 kHz.

For the synchronization of the time slot structure to an external PCM-system, a PCM-Framing Signal (PFS) must be applied. The MICO evaluates the rising PFS edge to reset the internal time slot counters. In order to adapt the PFS-timing to different timing requirements, the MICO can latch the PFS-signal with either the rising or the falling PDC-edge. The PFS-signal defines the position of the first bit of the internal PCM-frame. The actual position of the external upstream and downstream PCM-frames with respect to the framing signal PFS can still be adjusted using the PCM-offset function of the MICO. The offset can then be programmed such that PFS marks any bit number of the external frame.

Furthermore it is possible to select either the rising or falling PDC-clock edge for transmitting and sampling the PCM-data.

Usually, the repetition rate of the applied framing pulse PFS is identical to the frame period ( $125~\infty$ s). If this is the case, the **loss of synchronism indication function** can be used to supervise the clock and framing signals for missing or additional clock cycles. The MICO checks the PFS-period internally against the duration expected from the programmed data rate. If, for example, double clock operation with 32 time slots per frame is programmed, the MICO expects 512 clock periods within one PFS-period. The synchronous state is reached after the MICO has detected two consecutive correct frames. The synchronous state is lost if one bad clock cycle is found. The synchronization status (gained or lost) can be read from an internal register and each status change generates an interrupt.

#### **Operational Description**

Figure 7 Time Slot Encoding for the Different PCM and CFI Modes

#### 3.4.2 Configurable Interface

The serial configurable interface (CFI) can be operated either in duplex modes or in a bidirectional mode.

In **duplex modes** the MICO provides one port consisting of a data output (DD) and a data input (DU) line. The output pin is called "Data Downstream" pin and the input pin is called "Data Upstream" pin. These modes are especially suited to realize a standard serial PCM-interface (PCM-highway) or to implement an IOM (ISDN-Oriented Modular) interface. The IOM-interface generated by the MICO offers all the functionality like C/I-and monitor channel handling required for operating all kinds of IOM compatible layer-1 and codec devices.

In **bi-directional mode** the MICO provides two bi-directional ports (SIP). Each time slot at any of these ports can individually be programmed as input or output. This mode is mainly intended to realize an SLD-interface (Serial Line Data). In case of an SLD-interface the frame consists of eight time slots where the first four time slots serve as outputs (downstream direction) and the last four serve as inputs (upstream direction). The SLD-interface generated by the MICO offers signaling and feature control channel handling.

Data is transmitted and received at normal TTL/CMOS-levels at the CFI. **Tristate or open-drain output drivers** can be selected. In case of open-drain drivers, external pull-up resistors are required. Unassigned output time slots may be switched to high impedance or be programmed to transmit a defined idle value. The selection between the states "high impedance" or "idle value" can be performed on a per time slot basis.

The **CFI-standby function** switches all CFI-output lines to high impedance with a single command. Internally the device still works normally, only the output drivers are switched off.

The number of time slots per 8-kHz frame is programmable from 2 to 128. In other words, the **CFI-data rate can range between 128 kbit/s up to 8.192 Mbit/s**. Since the MICO offers one CFI-port the number of usable memory locations depends on the selected data rate. In duplex modes port '0' has to be programmed, in bi-directional mode I/O port '0' and '4' have to be programmed. For details refer to **figure 7**.

The timing characteristics at the CFI (data rate, bit shift, etc.) can be varied in a wide range.

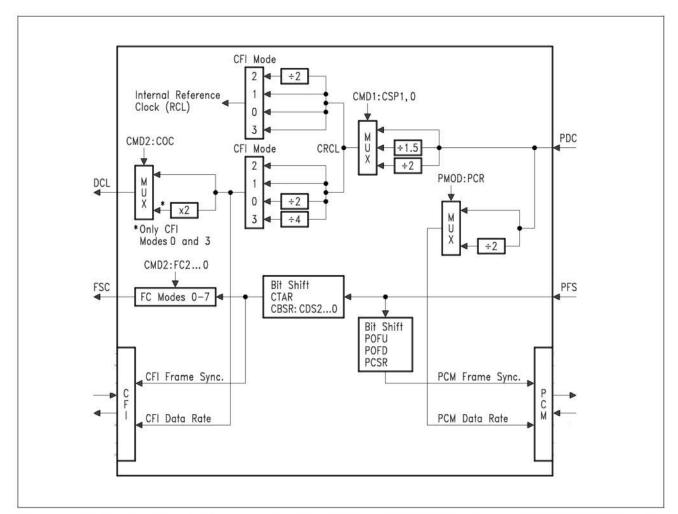

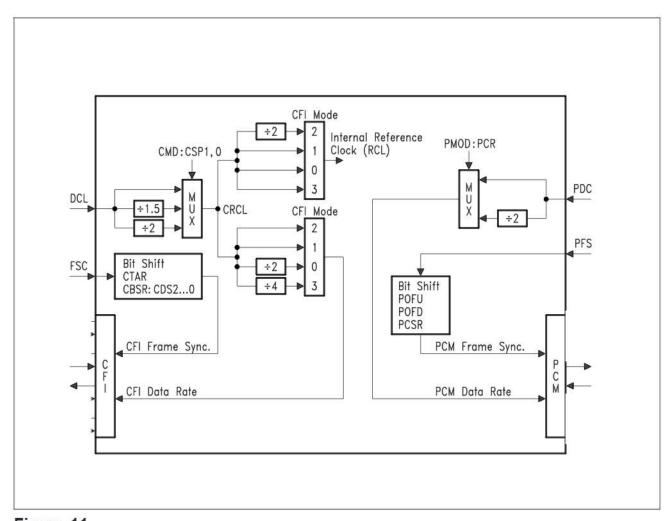

The clock and framing signals necessary to operate the configurable interface may be derived either from the clock and framing signals of the PCM-interface (PDC and PFS pins), or may be fed in directly via the DCL- and FSC-pins.

In the first case, the CFI-data rate is obtained by internally dividing down the PCM-clock signal PDC. Several prescaler factors are available to obtain the most commonly used data rates. A CFI reference clock (CRCL) is generated out of the PDC-clock. The PCM-framing signal PFS is used to synchronize the CFI-frame structure. Additionally, the MICO generates clock and framing signals as outputs to operate the connected

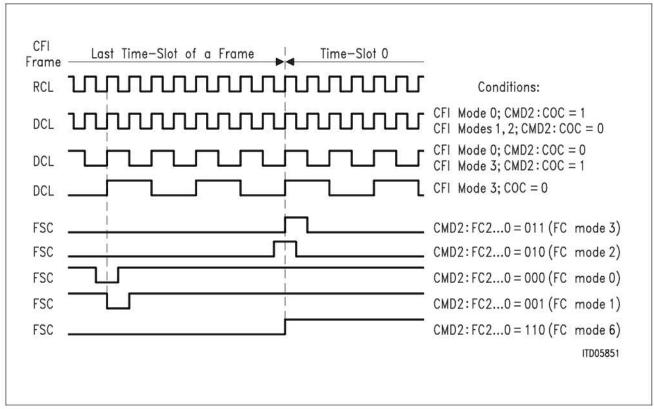

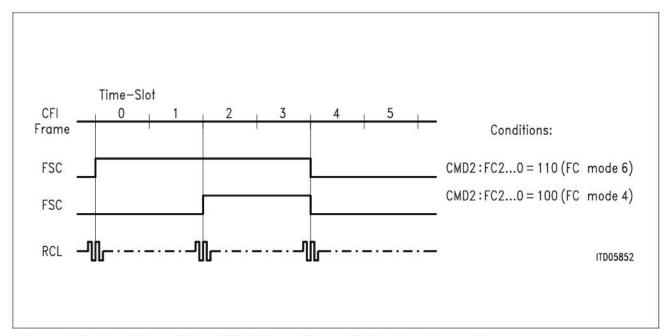

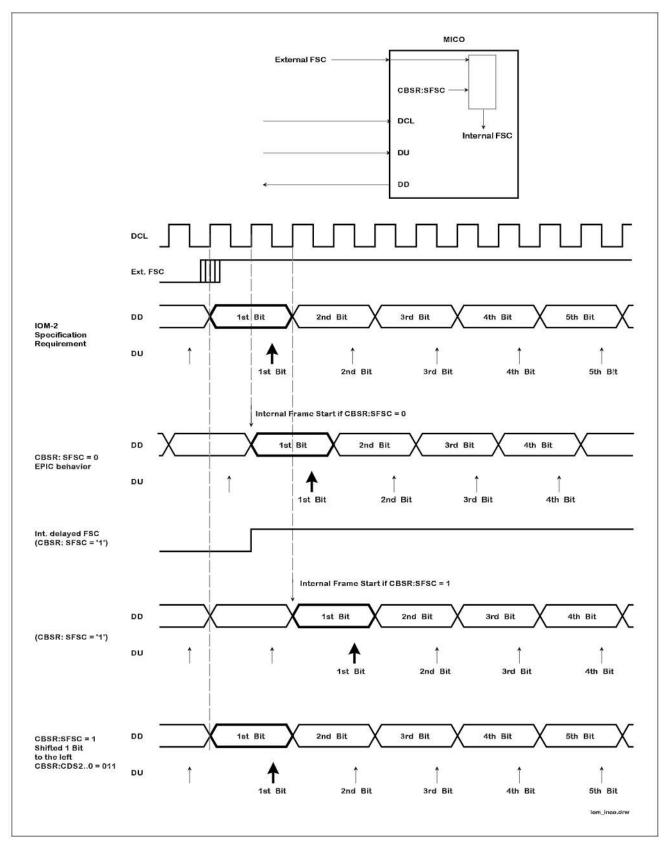

subscriber circuits such as layer-1 and codec filter devices. The generated data clock DCL has a frequency equal to or twice the CFI-data rate. The generated framing signal FSC can be chosen from a great variety of types to suit the different applications: IOM-2, multiplexed IOM-1, SLD, etc.

Note that if PFS is selected as the framing signal source, the FSC-signal is an output with a fixed timing relationship with respect to the CFI-data lines. The relationship between FSC and the CFI-frame depends only on the selected FSC-output wave form (CMD2-register). The CFI-offset function shifts both the frame and the FSC-output signal with respect to the PFS-signal.

In the second case, the CFI-data rate is derived from the DCL-clock, which is now used as an input signal. The DCL-clock may also first be divided down by internal prescalers before it serves as the CFI reference clock CRCL and before defining the CFI-data rate. The framing signal FSC is used to synchronize the CFI-frame structure.

#### 3.4.3 Switching Functions

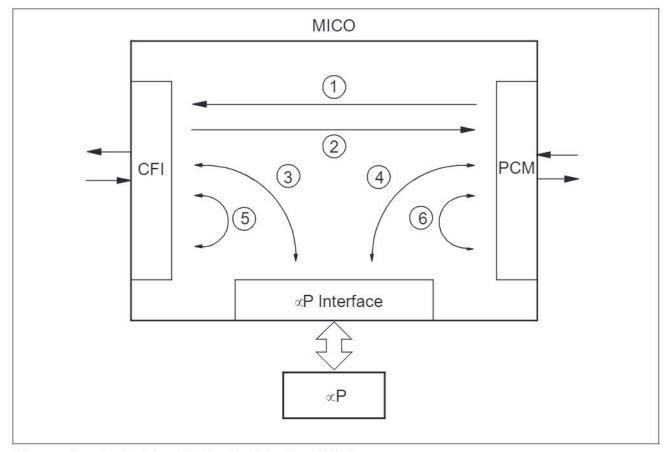

The major tasks of the MICO is to dynamically switch PCM-data between the serial PCM-interface, the serial configurable interface (CFI) and the parallel  $\infty$ P-interface. All possible switching paths are shown in **figure 8**.

Figure 8 Switching Paths Inside the MICO

Note that the time slot selections in upstream direction are completely independent of the time slot selections in downstream direction.

#### CFI - PCM Time Slot Assignment

Switching paths 1 and 2 of **figure 8** can be realized for a total number of up to 128 channels per path, i.e. up to 128 time slots in upstream and up to 128 time slots in downstream direction. To establish a connection, the  $\alpha P$  writes the addresses of the involved CFI and PCM time slots to the control memory. The actual transfer is then carried out frame by frame without further  $\alpha P$ -intervention.

The switching paths 5 and 6 can be realized by programming time slot assignments in the control memory. The total number for such loops is limited to the number of available time slots at the respective opposite interface, i.e. looping back a time slot from CFI to CFI requires a spare upstream PCM time slot and looping back a time slot from PCM to PCM requires a spare downstream and upstream CFI time slot.

Time slot switching is always carried out on 8-bit time slots, the actual position and number of transferred bits can however be limited to 4-bit or 2-bit sub time slots within these 8-bit time slots. On the CFI-side, only one sub time slot per 8-bit time slot can be switched, whereas on the PCM-interface up to 4 independent sub time slots can be switched.

Examples are given in section 4 of the EPIC Application Manual 10.92.

#### Sub Time Slot Switching

Sub time slot positions at the PCM-interface can be selected at random, i.e. each single PCM time slot may contain any mixture of 2- and 4-bit sub time slots. A PCM time slot may also contain more than one sub time slot. On the CFI however, two restrictions must be observed:

- Each CFI time slot may contain one and only one sub time slot.

- The sub-slot position for a given bandwidth within the time slot is fixed on a per port basis and therefore on a per device basis.

For more detailed information on sub-channel switching please refer to **chapter 5.2** of the EPIC-1 Application Manual 10.92.

#### ∞P-Transfer

Switching paths 3 and 4 of **figure 8** can be realized for all available time slots. Path 3 can be implemented by defining the corresponding CFI time slots as " $\alpha$ P-channels" or as "pre-processed channels".

Each single time slot can individually be declared as " $\infty$ P-channel". If this is the case, the  $\infty$ P can write a static 8-bit value to a downstream time slot which is then transmitted repeatedly in each frame until a new value is loaded. In upstream direction, the  $\infty$ P can read the received 8-bit value whenever required, no interrupts being generated.

#### Operational Description

The "pre-processed channel" option must always be applied to two consecutive time slots. The first of these time slots must have an even time slot number. If two time-slots are declared as "pre-processed channels", the first one can be accessed by the monitor/ feature control handler, which gives access to the frame via a 16-byte FIFO. Although this function is mainly intended for IOM- or SLD-applications, it could also be used to transmit or receive a "burst" of data to or from a 64-kbit/s channel. The second pre-processed time slot, the odd one, is also accessed by the  $\infty$ P. In downstream direction a 4-, 6- or 8-bit static value can be transmitted. In upstream direction the received 8-bit value can be read. Additionally, a change detection mechanism will generate an interrupt upon a change in any of the selected 4, 6 or 8 bits.

Pre-processed channels are usually programmed after Control Memory (CM) reset during device initialization. Resetting the CM sets all CFI time slots to unassigned channels (CM code '0000'). Of course, pre-processed channels can also be initialized or re-initialized in the operational phase of the device.

To program a pair of pre-processed channels the correct code for the selected handling scheme must be written to the CM. **Figure 9** gives an overview of the available pre-processing codes and their application. For further detail, please refer to **chapter 5.5** of the EPIC User's Manual 02.97.

#### **Operational Description**

| DD Application                                           | Even Control Memory Address MAAR = 00  Code Field Data Field MACR = 0111 MADR = | Odd Control Memory Address  MAAR = 01  Code Field Data Field  MACR = 0111 MADR = | Output at the Configurable Interface  Downstream Preprocessed Channels  Even Time-Slot  Odd Time-Slot |

|----------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Decentral<br>D Channel<br>Handling                       | 1 0 0 0 1 1 C/I 1 1                                                             | 1.0.1.1 [X.X.X.X.X.X.X.X.X.X.X.X.X.X.X.X.X.X.X.                                  | m,m,m,m,m,m,m,m, - , - , C/I , m,m <br>  Monitor Channel Control Channel                              |

| Central<br>D Channel<br>Handling                         | 1 0 1 0 1 1 C/I 1 1                                                             | PCM Code for a 2Bit Sub. Time—Slot                                               | Monitor Channel Control Channel                                                                       |

| 6 Bit<br>Signaling<br>(e.g. analog<br>IOM <sup>®</sup> ) | 1 0 1 0 SiG 1 1                                                                 | 1011 [XXXXXXXX                                                                   | Monitor Channel Control Channel                                                                       |

| 8 Bit<br>Signaling<br>(e.g. SLD)                         | 1 0 1 0 SIG                                                                     | 1011 [XXXXXXXX                                                                   | mmmmmmmm SIG                                                                                          |

| DU Application                              | Even Control Memory Address MAAR = 10  Code Field Data Field MACR = 0111 MADR = | Odd Control Memory Address  MAAR = 11  Code Field Data Field  MACR = 0111 MADR = | Input from the Configurable Interface Upstream Preprocessed Channels Even Time-Slot Odd Time-Slot |

|---------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Decentral<br>D Channel<br>Handling          | 1 0 0 0 1 1 C/I 1 1                                                             |                                                                                  | m,m,m,m,m,m,m,-,-, C/I, m,m <br> Monitor Channel Control Channel                                  |

| Central<br>D Channel<br>Handling            | 1000 11 C/I 11                                                                  | PCM Code for a 2Bit Sub. Time-Slot                                               | m,m,m,m,m,m,m,D,D, C/I, m,m <br>  Monitor Channel Control Channel                                 |

| 6 Bit<br>Signaling<br>(e.g. analog<br>IOM®) | 1 0 1 0 SIG Actual Value X X                                                    | SIG Stable Value X X                                                             | m,m,m,m,m,m,m, SIG, m,m <br>  Monitor Channel Control Channel                                     |

| 8 Bit<br>Signaling<br>(e.g. SLD)            | 1 0 1 1 SIG Actual Value                                                        | 1 0 1 1 SIG Stable Value                                                         | mmmmmmmmm SIG SIG Feature Control Channel Signaling Channel                                       |

m : Monitor channel bits, these bits are treated by the monitor/feature control handler

: Inactive sub. time-slot, in downstream direction these bits are tristated (OMDR:COS = 0) or set to logical 1 (OMDR:COS = 1)

C/I : Command/Indication channel, these bits are exchanged between the CFI in/output and the CM data field. A change of the C/I bits in upstream direction causes an interrupt (ISTA:SFI). The address of the change is stored in the CIFIFO

D : D channel, these D channel bits are transparently switched to and from the PCM interface,

SIG : Signaling Channel, these bits are exchanged between the CFI in/output and the CM data field. The SIG value which was present in the last frame is stored as the actual value in the even address CM location. The stable value is updated if a valld change in the actual value has been detected according to the last look algorithm. A change of the SIG stable value in upstream direction causes an Interrupt (ISTA: CFI). The address of the change is stored in the CIFIFO.

ITD05846

Figure 9 Pre-processed Channel Codes

#### **Operational Description**

#### Synchronous Transfer

For two channels, all switching paths of **figure 8** can also be realized using Synchronous Transfer. The working principle is that the  $\infty P$  specifies an input time slot (source) and an output time slot (destination). Both source and destination time slots can be selected independently from each other at either the PCM- or CFI-interfaces. In each frame, the MICO first transfers the serial data from the source time slot to an internal data register from where it can be read and if required overwritten or modified by the  $\infty P$ . This data is then fed forward to the destination time slot.

Chapter 8 of the EPIC Application Manual 10.92 provides examples of such transfers.

#### 3.4.4 Special Functions

#### **Hardware Timer**

The MICO provides one hardware timer which continuously interrupts the  $\propto P$  after a programmable time period. The timer period can be selected in the range of 250  $\propto s$  up to 32 ms in multiples of 250  $\propto s$ . Beside the interrupt generation, the timer can also be used to determine the last look period for 6 and 8-bit signaling channels on IOM-2 and SLD-interfaces and for the generation of an FSC-multiframe signal (see **chapter 9.1** of the EPIC Application Manual 10.92).

#### Power and Clock Supply Supervision

The Connection Memory CM is supervised to data falsfication due to clock or power failure. If such an inappropriate clocking or power failure occurs, the  $\infty P$  is requested to reinitialize the device.

#### 3.5 Initialization Procedure

For proper initialization of the MICO the following procedure is recommended:

#### 3.5.1 Hardware Reset

A reset pulse can be applied at the RES-pin for at least 4 PDC-clock cycles. The reset pulse sets all registers to their reset values (refer to **section 4.1**).

Note that in this state DCL and FSC do not deliver any clock signals.

#### 3.5.2 MICO Initialization

#### 3.5.2.1 Register Initialization

The PCM- and CFI-configuration registers (PMOD, PBNR, ..., CMD1, CMD2, ...) should be programmed to the values required for the application. The correct setting of the PCM- and CFI-registers is important in order to obtain a reference clock (RCL) which is consistent with the externally applied clock signals.

The state of the operation mode (OMDR:OMS1..0 bits) does not matter for this programming step.

PMOD = PCM-mode, timing characteristics, etc.

PBNR = Number of bits per PCM-frame

POFD = PCM-offset downstream POFU = PCM-offset upstream

PCSR = PCM-timing

CMD1 = CFI-mode, timing characteristics, etc.

CMD2 = CFI-timing

CBNR = Number of bits per CFI-frame

CTAR = CFI-offset (time slots)

CBSR = CFI-offset (bits)

CSCR = CFI-sub channel positions

#### 3.5.2.2 Control Memory Reset

Since the hardware reset does not affect the MICO memories (Control and Data Memories), it is mandatory to perform a "software reset" of the CM. The CM-code '0000' (unassigned channel) should be written to each location of the CM. The data written to the CM-data field is then don't care, e.g.  $FF_H$ .

OMDR:OMS1..0 must be to '00'<sub>B</sub> for this procedure (reset value).

$MADR = FF_H$   $MACR = 70_H$ Wait for STAR:MAC = 0

The resetting of the complete CM takes 256 RCL-clock cycles. During this time, the STAR:MAC-bit is set to logical 1.

#### 3.5.2.3 Initialization of Pre-processed Channels

After the CM-reset, all CFI time slots are unassigned. If the CFI is used as a plain PCM-interface, i.e. containing only switched channels (B-channels), the initialization steps below are not required. The initialization of pre-processed channels applies only to IOM-or SLD-applications.

An IOM- or SLD-"channel" consists of four consecutive time slots. The first two time slots, the B-channels need not be initialized since they are already set to unassigned channels by the CM-reset command. Later, in the application phase of the software, the B-channels can be dynamically switched according to system requirements. The last two time slots of such an IOM- or SLD-channel, the pre-processed channels must be initialized for the desired functionality. There are four options that can be selected:

Table 2 Pre-Processed Channel Options at the CFI

| Even CFI Time Slot              | Odd CFI Time Slot                                                        | Main<br>Application                  |

|---------------------------------|--------------------------------------------------------------------------|--------------------------------------|

| Monitor/feature control channel | 4-bit C/I-channel, D-channel not switched (decentral D-channel handling) | IOM-1 or IOM-2<br>digital subscriber |

| Monitor/feature control channel | 4-bit C/I-channel, D-channel switched (central D-ch. handling)           | IOM-1 or IOM-2<br>digital subscriber |

| Monitor/feature control channel | 6-bit SIG-channel                                                        | IOM-2, analog subscriber             |

| Monitor/feature control channel | 8-bit SIG/channel                                                        | SLD, analog subscriber               |

Also refer to figure 9.

#### Example

In CFI-mode 0 the CFI-port shall be initialized as IOM-2 port with a 4-bit C/I-field. CFI time slots 0, 1, 4, 5, 8, 9 ... 28, 29 are B-channels and need not to be initialized. CFI time slots 2, 3, 6, 7, 10, 11, ..., 30, 31 are pre-processed channels and need to be initialized:

#### CFI-port, time slot 2 (even), downstream

```

MADR = FF_H; the C/I-value '1111' will be transmitted upon CFI-activation

```

MAAR =  $08_H$ ; addresses ts 2 down MACR =  $7A_H$ ; CM-code '1010'

Wait for STAR:MAC = 0

#### CFI-port, time slot 3 (odd), downstream

```

MADR = FF_H; don't care

```

$MAAR = 09_{H}$ ; addresses ts 3 down MACR =  $7B_{H}$ ; CM-code '1011'

Wait for STAR:MAC = 0

#### CFI-port, time slot 2 (even), upstream

```

MADR = FF_H; the C/I-value '1111' is expected upon CFI-activation

```

MAAR =  $88_H$ ; address ts 2 up MACR =  $78_H$ ; CM-code '1000'

Wait for STAR:MAC = 0

#### CFI-port, time slot 3 (odd), upstream

$MADR = FF_H$ ; don't care

MAAR =  $89_H$ ; address ts 3 up MACR =  $70_H$ ; CM-code '0000'

Wait for STAR:MAC = 0

Repeat the above programming steps for the remaining CFI-time slots.

This procedure can be speeded up by selecting the CM-initialization mode (OMDR:OMS1..0=10). If this selection is made, the access time to a single memory location is reduced to 2.5 RCL-cycles. The complete initialization time for 8 IOM-2 channels is then reduced to  $32 \cdot 0.61 \, \alpha s = 19.5 \, \alpha s$

#### 3.5.2.4 Initialization of the Upstream Data Memory (DM) Tristate Field

For each PCM time slot the tristate field defines whether the contents of the DM-data field are to be transmitted (low impedance), or whether the PCM time slot shall be set to high impedance. The content of the tristate field is not modified by a hardware reset. In order to have all PCM time slots set to high impedance upon the activation of the PCM-interface, each location of the tristate field must be loaded with the value '0000'. For this purpose, the "tristate reset" command can be used:

```

OMDR = C0_H; OMS1..0 = 11, normal mode

```

MADR =  $00_{H}$ ; code field value '0000'<sub>B</sub>

MACR =  $68_{H}$ ; MOC-code to initialize all tristate locations (1101<sub>B</sub>)

Wait for STAR:MAC = 0

The initialization of the complete tristate field takes 1035 RCL-cycles.

Note: It is also possible to program the value '1111' to the tristate field in order to have all time slots switched to low impedance upon the activation of the PCM-interface.

Note: While OMDR:PSB = 0, all PCM-output drivers are set to high impedance, regardless of the values written to the tristate field.

#### 3.5.3 Activation of the PCM- and CFI-Interfaces

With the MICO configured to the system requirements, the PCM- and CFI-interface can be switched to the operational mode.

The OMDR:OMS1..0 bits must be set (if this has not already be done) to the normal operation mode (OMS1..0 = 11). When doing this, the PCM-framing interrupt (ISTA:PFI) will be enabled. If the applied clock and framing signals are in accordance with the values programmed to the PCM-registers, the PFI-interrupt will be generated (if not masked). When reading the status register, the STAR:PSS-bit will be set to logical 1.

To enable the PCM-output drivers set OMDR:PSB = 1. The CFI-interface is activated by programming OMDR:CSB = 1. This enables the output clock and framing signals (DCL and FSC), if these have been programmed as outputs. It also enables the CFI-output drivers. The output driver type can be selected between "open drain" and "tristate" with the OMDR:COS-bit.

**Example:** Activation of the MICO for a typical IOM-2 application:

OMDR =  $EE_H$ ; Normal operation mode (OMS1..0 = 11)

PCM-interface active (PSB = 1)

PCM-test loop disabled (PTL = 0)

CFI-output drivers: open drain (COS = 1)

Monitor handshake protocol selected (MFPS = 1)

CFI active (CSB = 1)

Access to MICO registers via address pins A3..A0, used in

demultiplexed mode only, normal operation (RBS = 0)

### **Registers Summary**

## 4 Registers Summary

### 4.1 Register Address Arrangement

| Group          | Reg Name | Access | Address<br>mux<br>AD70 | Address<br>demux<br>OMDR:RBS/<br>A30 | Reset<br>Value  | Comment                       | refer to<br>page |

|----------------|----------|--------|------------------------|--------------------------------------|-----------------|-------------------------------|------------------|

| 1. MICO        | PMOD     | RD/WR  | 20 <sub>H</sub>        | 1/0 <sub>H</sub>                     | 00 <sub>H</sub> | PCM-mode reg.                 | 35               |

| PCM            | PBNR     | RD/WR  | 22 <sub>H</sub>        | 1/1 <sub>H</sub>                     | FF <sub>H</sub> | PCM-bit number reg.           | 36               |

|                | POFD     | RD/WR  | 24 <sub>H</sub>        | 1/2 <sub>H</sub>                     | 00 <sub>H</sub> | PCM-offset downstream reg.    | 36               |

|                | POFU     | RD/WR  | 26 <sub>H</sub>        | 1/3 <sub>H</sub>                     | 00 <sub>H</sub> | PCM-offset upstream reg.      | 37               |

|                | PCSR     | RD/WR  | 28 <sub>H</sub>        | 1/4 <sub>H</sub>                     | 00 <sub>H</sub> | PCM-clock shift reg.          | 38               |

|                | PICM     | RD     | 2A <sub>H</sub>        | 1/5 <sub>H</sub>                     | хх <sub>Н</sub> | dummy                         | 38               |

| 2. MICO        | CMD1     | RD/WR  | 2C <sub>H</sub>        | 1/6 <sub>H</sub>                     | 00 <sub>H</sub> | CFI-mode reg. 1               | 39               |

| CFI            | CMD2     | RD/WR  | 2E <sub>H</sub>        | 1/7 <sub>H</sub>                     | 00 <sub>H</sub> | CFI-mode reg. 2               | 41               |

|                | CBNR     | RD/WR  | 30 <sub>H</sub>        | 1/8 <sub>H</sub>                     | FF <sub>H</sub> | CFI-bit number reg.           | 44               |

|                | CTAR     | RD/WR  | 32 <sub>H</sub>        | 1/9 <sub>H</sub>                     | 00 <sub>H</sub> | CFI time slot adjustment reg. | 44               |

|                | CBSR     | RD/WR  | 34 <sub>H</sub>        | 1/A <sub>H</sub>                     | 00 <sub>H</sub> | CFI-bit shift reg.            | 45               |

|                | CSCR     | RD/WR  | 36 <sub>H</sub>        | 1/B <sub>H</sub>                     | 00 <sub>H</sub> | CFI-subchannel reg.           | 47               |

| 3. MICO memory | MACR     | RD/WR  | 00 <sub>H</sub>        | 0/0 <sub>H</sub>                     | xx <sub>H</sub> | memory access control reg.    | 48               |

| access         | MAAR     | RD/WR  | 02 <sub>H</sub>        | 0/1 <sub>H</sub>                     | xx <sub>H</sub> | memory access address reg.    | 52               |

|                | MADR     | RD/WR  | 04 <sub>H</sub>        | 0/2 <sub>H</sub>                     | xx <sub>H</sub> | memory access data reg.       | 53               |

## Registers Summary

| Group              | Reg Name | Access | Address<br>mux<br>AD70             | Address<br>demux<br>OMDR:RBS/<br>A30 | Reset<br>Value  | Comment                                         | refer to<br>page |

|--------------------|----------|--------|------------------------------------|--------------------------------------|-----------------|-------------------------------------------------|------------------|

| 4. MICO synchro    | STDA     | RD/WR  | 06 <sub>H</sub>                    | 0/3 <sub>H</sub>                     | xx <sub>H</sub> | synchron transfer<br>data reg. A                | 54               |

| nous<br>transfer   | STDB     | RD/WR  | 08 <sub>H</sub>                    | 0/4 <sub>H</sub>                     | хх <sub>Н</sub> | synchron transfer data reg. B                   | 54               |

| uansiei            | SARA     | RD/WR  | 0A <sub>H</sub>                    | 0/5 <sub>H</sub>                     | хх <sub>Н</sub> | synchron transfer receive address reg. A        | 55               |

|                    | SARB     | RD/WR  | 0C <sub>H</sub>                    | 0/6 <sub>H</sub>                     | хх <sub>Н</sub> | synchron transfer receive address reg. B        | 56               |

|                    | SAXA     | RD/WR  | 0E <sub>H</sub>                    | 0/7 <sub>H</sub>                     | хх <sub>Н</sub> | synchron transfer<br>transmit address reg.<br>A | 56               |

|                    | SAXB     | RD/WR  | 10 <sub>H</sub>                    | 0/8 <sub>H</sub>                     | хх <sub>Н</sub> | synchron transfer<br>transmit address reg.<br>B | 57               |

|                    | STCR     | RD/WR  | 12 <sub>H</sub>                    | 0/9 <sub>H</sub>                     | 00xxxx<br>xx    | synchron transfer control reg.                  | 57               |

| 5. MICO monitor/   | MFAIR    | RD     | 14 <sub>H</sub>                    | 0/A <sub>H</sub>                     | 00xxxx<br>xx    | MF-channel active indication reg.               | 58               |

| feature<br>control | MFSAR    | WR     | 14 <sub>H</sub>                    | 0/A <sub>H</sub>                     | 00 <sub>H</sub> | MF-channel subscriber address reg.              | 59               |

|                    | MFFIFO   | RD/WR  | 16 <sub>H</sub>                    | 0/B <sub>H</sub>                     | xx <sub>H</sub> | MF-channel FIFO                                 | 60               |

| 6. MICO status/    | CIFIFO   | RD     | 18 <sub>H</sub>                    | 0/C <sub>H</sub>                     | 0xxxxx<br>xx    | signaling channel FIFO                          | 60               |

| control            | TIMR     | WR     | 18 <sub>H</sub>                    | 0/C <sub>H</sub>                     | 00 <sub>H</sub> | timer reg.                                      | 61               |

|                    | STAR     | RD     | 1A <sub>H</sub>                    | 0/D <sub>H</sub>                     | 05 <sub>H</sub> | status register                                 | 62               |

|                    | CMDR     | WR     | 1A <sub>H</sub>                    | 0/D <sub>H</sub>                     | 00 <sub>H</sub> | command reg.                                    | 63               |

|                    | ISTA     | RD     | 1C <sub>H</sub>                    | 0/E <sub>H</sub>                     | 00 <sub>H</sub> | interrupt status                                | 65               |

|                    | MASK     | WR     | 1C <sub>H</sub>                    | 0/E <sub>H</sub>                     | 04 <sub>H</sub> | mask register                                   | 66               |

|                    | OMDR     | RD/WR  | 1E <sub>H</sub><br>3E <sub>H</sub> | x/F <sub>H</sub>                     | 00 <sub>H</sub> | operation mode reg.                             | 67               |

|                    | VNSR     | RD     | 3A <sub>H</sub>                    | 1/D <sub>H</sub>                     | 02 <sub>H</sub> | version number status register                  | 69               |

Registers Summary

#### 4.2 Detailed Register Description

Unused bits and registers are accessible as described below to facilitate software portation from existing EPIC designs. They have to be programmed to the specified values. Writing other than the specified values may cause undefined behaviour.

#### 4.2.1 PCM-Interface Registers

#### 4.2.1.1 PCM-Mode Register (PMOD)

Access in demultiplexed  $\alpha P$ -interface mode: read/write address:  $0_H$ ,

OMDR:RBS = 1

Access in multiplexed ∞P-interface mode: read/write address: 20<sub>H</sub>

Reset value: 00<sub>H</sub>

| bit 7 |      |     |     |   |   |   | bit 0 |  |

|-------|------|-----|-----|---|---|---|-------|--|

| PMD1  | PMD0 | PCR | PSM | 0 | 0 | 0 | 0     |  |

**PMD1..0** PCM-Mode. Defines the actual number of PCM-ports, the data rate range and the data rate stepping.

| PMD10 | PCM-Mode | 1    | Data Rate<br>Stepping |          |

|-------|----------|------|-----------------------|----------|

|       |          | min. | max.                  | [kbit/s] |

| 00    | 0        | 256  | 2048                  | 256      |

| 01    | 1        | 512  | 4096                  | 512      |

| 10    | 2        | 1024 | 8192                  | 1024     |

#### PCR PCM-Clock Rate.

- single clock rate, data rate is identical with the clock frequency supplied on pin PDC.

- 1... double clock rate, data rate is half the clock frequency supplied on pin PDC.

Note: Only single clock rate is allowed in PCM-mode 2!

#### **PSM** PCM Synchronization Mode.

A rising edge on PFS synchronizes the PCM-frame. PFS is not evaluated directly but is sampled with PDC.

- 0... the external PFS is evaluated with the falling edge of PDC. The internal PFS (internal frame start) occurs with the next rising edge of PDC.

- 1... the external PFS is evaluated with the rising edge of PDC. The internal PFS (internal frame start) occurs with this rising edge of PDC.

#### **Registers Summary**

#### 4.2.1.2 Bit Number per PCM-Frame (PBNR)

Access in demultiplexed ¤P-interface mode: read/write address: 1H

OMDR:RBS = 1

Access in multiplexed ∞P-interface mode: read/write address: 22<sub>H</sub>

Reset value: FFH

bit 7

| BNF7 BNF6 BNF5 BNF4 BNF3 BNF2 BNF1 BNF0 |  | BNF7 | BNF6 | BNF5 | BNF4 | BNF3 | BNF2 | BNF1 | BNF0 |

|-----------------------------------------|--|------|------|------|------|------|------|------|------|

|-----------------------------------------|--|------|------|------|------|------|------|------|------|

#### BNF7..0 Bit Number per PCM Frame.

PCM-mode 0: BNF7..0 = number of bits – 1

PCM-mode 1: BNF7..0 = (number of bits - 2) / 2PCM-mode 2: BNF7..0 = (number of bits - 4) / 4

The value programmed in PBNR is also used to check the PFS-period.

#### 4.2.1.3 PCM-Offset Downstream Register (POFD)

Access in demultiplexed  $\infty P$ -interface mode: read/write address:  $2_H$

OMDR:RBS = 1

Access in multiplexed ∞P-interface mode: read/write address: 24<sub>H</sub>

Reset value: 00<sub>H</sub>

bit 7 bit 0

| OFD9 | OFD8 | OFD7 | OFD6 | OFD5 | OFD4 | OFD3 | OFD2 |

|------|------|------|------|------|------|------|------|

|------|------|------|------|------|------|------|------|

#### **OFD9..2** Offset Downstream bit 9...2.

These bits together with PCSR:OFD1..0 determine the offset of the PCM-frame in downstream direction. The following formulas apply for calculating the required register value. BND is the bit number in downstream direction marked by the rising internal PFS-edge. BPF denotes the actual number of bits constituting a frame.

PCM-mode 0: OFD9..2 =  $mod_{BPF}$  (BND - 17 + BPF)

PCSR:OFD1..0 = 0

PCM-mode 1:  $PFD9..1 = mod_{RPF} (BND - 33 + BPF)$

PCSR: PFD0 = 0

PCM-mode 2: OFD9..0 =  $mod_{BPF}$  (BND - 65 + BPF)

SIEMENS PEF 2015

### **Registers Summary**

# 4.2.1.4 PCM-Offset Upstream Register (POFU)

Access in demultiplexed ∞P-interface mode: read/write address: 3<sub>H</sub>

OMDR:RBS = 1

Access in multiplexed ∞P-interface mode: read/write address: 26<sub>H</sub>

Reset value: 00<sub>H</sub>

bit 7 bit 0

| OFU | OFU8 | OFU7 | OFU6 | OFU5 | OFU4 | OFU3 | OFU2 |  |

|-----|------|------|------|------|------|------|------|--|

|-----|------|------|------|------|------|------|------|--|

### **OFU9..2** Offset Upstream bit 9...2.

These bits together with PCSR:OFU1..0 determine the offset of the PCM-frame in upstream direction. The following formulas apply for calculating the required register value. BNU is the bit number in upstream direction marked by the rising internal PFS-edge. BPF denotes the actual number of bits constituting a frame.

PCM-mode 0: OFU9..2 =  $mod_{BPF}$  (BNU + 23)

PCSR:OFU1..00 = 0

PCM-mode 1: OFU9..1 =  $mod_{RPF}$  (BNU + 47)

PCSR:OFU0 = 0

PCM-mode 2: OFU9..0 =  $mod_{BPF}$  (BNU + 95)

### 4.2.1.5 PCM-Clock Shift Register (PCSR)

Access in demultiplexed  $\infty$ P-interface mode: read/write address: 4<sub>H</sub>

OMDR:RBS = 1

Access in multiplexed ∞P-interface mode: read/write address: 28<sub>H</sub>

Reset value: 00<sub>H</sub>

bit 7 bit 0

| DR | CS OFD1 | OFD0 | DRE | ADSRO | OFU1 | OFU0 | URE |

|----|---------|------|-----|-------|------|------|-----|

|----|---------|------|-----|-------|------|------|-----|

DRCS Double Rate Clock Shift.

0...the PCM-input and output data are not delayed

1...the PCM-input and output data are delayed by one PDC-clock cycle

**OFD1..0** Offset Downstream bits 1...0, see **POFD-register**.

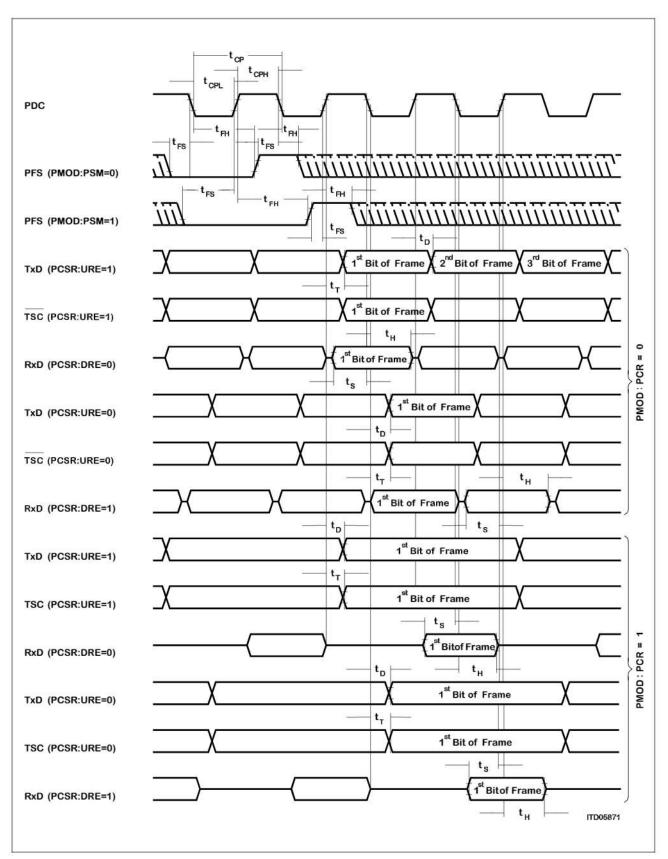

DRE Downstream Rising Edge.

0...the PCM-data is sampled with the falling edge of PDC1...the PCM-data is sampled with the rising edge of PDC

ADSRO Add Shift Register on Output.

0...the PCM-output data are not delayed

1...the PCM-output data are delayed by one PDC-clock cycle.

Note: If both DRCS and ADSRO are set to logical 1, the PCM-output data are delayed by two PDC-clock cycles.

**OFU1..0** Offset Upstream bits 1...0, see **POFU-register**.

**URE** Upstream Rising Edge.

0...the PCM-data is transmitted with the falling edge of PDC1...the PCM-data is transmitted with the rising edge of PDC

## 4.2.1.6 PCM-Input Comparison Mismatch Register (PICM)

Access in demultiplexed ∞P-interface mode: read address: 5<sub>H</sub>

OMDR:RBS = 1

Access in multiplexed ∞P-interface mode: read address: 2A<sub>H</sub>

Reset value: xx<sub>H</sub>

Note: This register does not provide valid values for operation. It is a dummy register to facilitate software portation from the EPIC to the MICO.

### 4.2.2 Configurable Interface Registers

### 4.2.2.1 Configurable Interface Mode Register 1 (CMD1)

Access in demultiplexed  $\infty$ P-interface mode: read/write address: 6<sub>H</sub>

OMDR:RBS = 1

Access in multiplexed ∞P-interface mode: read/write address: 2C<sub>H</sub>

Reset value: 00<sub>H</sub>

| bit 7 |     |      |      |      |      |   | bit 0 |

|-------|-----|------|------|------|------|---|-------|

| CSS   | CSM | CSP1 | CSP0 | CMD1 | CMD0 | 0 | 0     |

### CSS Clock Source Selection.

- 0...PDC and PFS are used as clock and framing source for the CFI. Clock and framing signals derived from these sources are output on DCL and FSC.

- 1...DCL and FSC are selected as clock and framing source for the CFI.

### **CSM** CFI-Synchronization Mode.

The rising FSC-edge synchronizes the CFI-frame.

- 0...FSC is evaluated with every falling edge of DCL.

- 1...FSC is evaluated with every rising edge of DCL.

Note: If CSS = 0 is selected, CSM and PMOD:PSM must be programmed identical.

### **CSP1..0** Clock Source Prescaler 1,0.

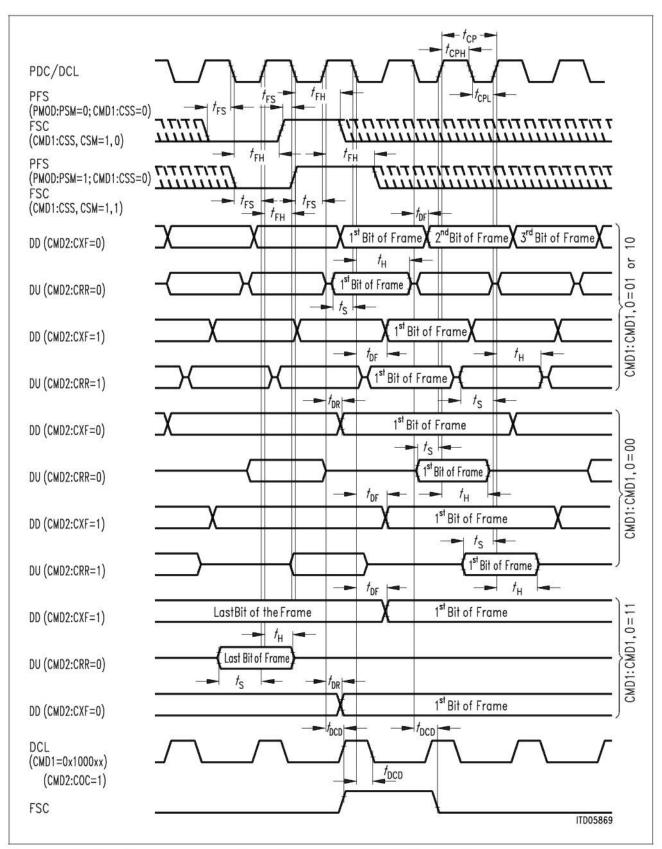

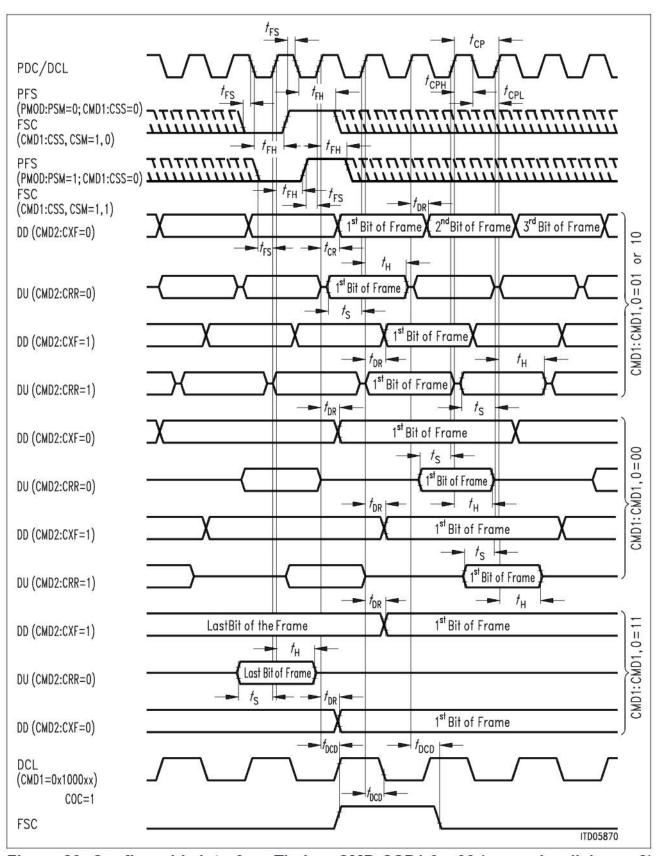

The clock source frequency is divided according to the following table to obtain the CFI-reference clock CRCL (refer to **figures 10 and 11**).

| CSP1,0 | Prescaler Divisor |  |  |

|--------|-------------------|--|--|

| 00     | 2                 |  |  |

| 01     | 1.5               |  |  |

| 10     | 1                 |  |  |

| 11     | not allowed       |  |  |

**CMD1..0** CFI-Mode1,0.

Defines the actual configuration of the CFI-port.

| CMD10 | CFI<br>Mode | CFI-Data Rate<br>[kbit/s] |      | Min. Required<br>CFI-Data Rate        | Necessary<br>Reference | DCL-Output<br>Frequencies |  |

|-------|-------------|---------------------------|------|---------------------------------------|------------------------|---------------------------|--|

|       |             | min.                      | max. | [kbit/s] Relative<br>to PCM-Data Rate | Clock (RCL)            | CMD1:CSS = 0              |  |

| 00    | 0           | 128                       | 2048 | 32N/3                                 | 2xDR                   | DR, 2xDR                  |  |