# PART NUMBER 54198DMB-ROC

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

Qualified Suppliers List of Distributors (QSLD)

Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# V54/74198 010748

### 8-BIT R/L SHIFT REGISTER

**DESCRIPTION** — The '198 features synchronous parallel load, hold, shift right and shift left modes, as determined by the Select  $(S_0, S_1)$  inputs. State changes are initiated by the rising edge of the clock. An asynchronous Master Reset  $(\overline{MR})$  input overrides all other inputs and clears the register. The '198 is useful for serial-serial, serial-parallel, parallel-serial and parallel-parallel register transfers.

- PARALLEL IN/PARALLEL OUT

- SYNCHRONOUS PARALLEL LOAD

- SHIFT RIGHT AND SHIFT LEFT CAPABILITY

- ASYNCHRONOUS OVERRIDING CLEAR

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                             | PKG  |

|--------------------|-----|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|

| PKGS               | ОПТ | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{C to} +125^{\circ}\text{C}$ | TYPE |

| Plastic<br>DIP (P) | Α   | 74198PC                                                                                  |                                                                                            | 9N   |

| Ceramic<br>DIP (D) | Α   | 74198DC                                                                                  | 54198DM                                                                                    | 6N   |

| Flatpak<br>(F)     | Ά.  | 74198FC                                                                                  | 54198FM                                                                                    | 4M   |

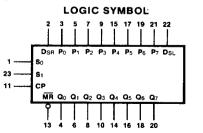

# CONNECTION DIAGRAM PINOUT A

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                       | DESCRIPTION                                  | <b>54/74 (U.L.)</b><br>HIGH/LOW |  |

|---------------------------------|----------------------------------------------|---------------------------------|--|

| S <sub>0</sub> , S <sub>1</sub> | Mode Select Inputs                           | 1.0/1.0                         |  |

| Po — P7                         | Parallel Data Inputs                         | 1.0/1.0                         |  |

| DsR                             | Serial Data Input (Shift Right)              | 1.0/1.0                         |  |

| D <sub>SL</sub>                 | Serial Data Input (Shift Left)               | 1.0/1.0                         |  |

| CP                              | Clock Pulse Input (Active Rising Edge)       | 1.0/1.0                         |  |

| CP<br>MR                        | Asynchronous Master Reset Input (Active LOW) | 1.0/1.0                         |  |

| Q <sub>0</sub> — Q <sub>7</sub> | Flip-flop Outputs                            | 20/10                           |  |

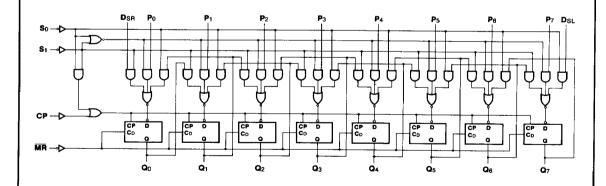

V<sub>CC</sub> = Pin 24 GND = Pin 12 **FUNCTIONAL DESCRIPTION** — The '198 contains eight edge-triggered D-type flip-flops and the interstage gating required to perform synchronous parallel load, shift right, and shift left operations. Serial data enters at DSR for shift right and at DSL for shift left operations. Parallel data is applied to the  $P_0 - P_7$  inputs. State changes are initiated by the rising edge of the clock. The DSR, DSL and  $P_0 - P_7$  inputs can change when the clock is in either state, provided only that the recommended setup and hold times are observed.

The operating mode is determined by  $S_0$  and  $S_1$ , as shown in the Mode Select Table. Clocking of the flip-flops is inhibited when both  $S_0$  and  $S_1$  are LOW. To avoid inadvertently clocking the register, the Select inputs should only be changed while CP is HIGH. A LOW signal on  $\overline{MR}$  overrides all other inputs and forces the outputs LOW.

#### **MODE SELECT TABLE**

| INPUTS |       |                                   |       | RESPONSE                                                                                                                     |  |  |

|--------|-------|-----------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| MR     | СР    | S <sub>0</sub> * S <sub>1</sub> * |       | MESI CNOL                                                                                                                    |  |  |

|        | ×\\\× | X<br>H<br>L<br>H                  | XHHLL | Asynchronous Reset; Outputs = LOW Parallel Load; Pn Qn Shift Right; DsR Q0, Q0 Q1, etc. Shift Left; DsL Q7, Q7 Q6, etc. Hold |  |  |

<sup>\*</sup>Select inputs should be changed only while CP is HIGH

#### LOGIC DIAGRAM

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

## DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER            | 54/74 |     | UNITS      | CONDITIONS |                                                                                      |

|--------|----------------------|-------|-----|------------|------------|--------------------------------------------------------------------------------------|

|        |                      | Min   | Max | 00         | CONDITIONS |                                                                                      |

| lcc    | Power Supply Current | XC    |     | 116<br>104 | mA         | $V_{CC} = Max; S_0, S_1 = 4.5 \text{ V}$<br>$CP = J\Gamma; \overline{MR}, P_0 = Gnd$ |

## AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ} \text{C}$ (See Section 3 for waveforms and load configurations)

| ,            |                                           | 54/74  CL = 15 pF  RL = 400 Ω |          | UNITS | CONDITIONS      |

|--------------|-------------------------------------------|-------------------------------|----------|-------|-----------------|

| SYMBOL       | PARAMETER                                 |                               |          |       |                 |

|              |                                           | Min                           | Max      | 1     |                 |

| fmax         | Maximum Shift Frequency                   | 25                            |          | MHz   | Figs. 3-1, 3-8  |

| tPLH<br>tPHL | Propagation Delay<br>CP to Q <sub>n</sub> |                               | 26<br>30 | ns    | Figs. 3-1, 3-8  |

| tPHL         | Propagation Delay<br>MR to Qn             |                               | 35       | ns    | Figs. 3-1, 3-16 |

## AC OPERATING REQUIREMENTS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ} \text{ C}$

| SYMBOL                                   | PARAMETER                                            | 54/74    |     | UNITS    | CONDITIONS |

|------------------------------------------|------------------------------------------------------|----------|-----|----------|------------|

|                                          |                                                      | Min      | Max | 1 0,4113 | CONDITIONS |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>Pn, DsL, DsR to CP         | 20<br>20 |     | ns       |            |

| th (H)<br>th (L)                         | Hold Time HIGH or LOW<br>Pn, DsL, DsR to CP          | 0        |     | ns       | Fig. 3-6   |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>So or S <sub>1</sub> to CP | 30<br>30 |     | ns       | - Fig. 3-6 |

| th (H)<br>th (L)                         | Hold Time HIGH or LOW<br>So or S <sub>1</sub> to CP  | 0        |     | ns       | ]          |

| tw (H)                                   | CP Pulse Width HIGH                                  | 20       |     | ns       | Fig. 3-8   |

| tw (L)                                   | MR Pulse Width LOW                                   | 20       |     | ns       | Fig. 3-16  |