## MC1405, MC1505

## Dual Ramp A/D Converter Subsystem

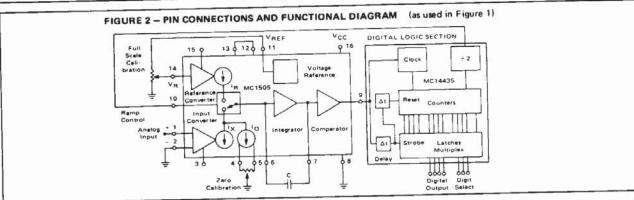

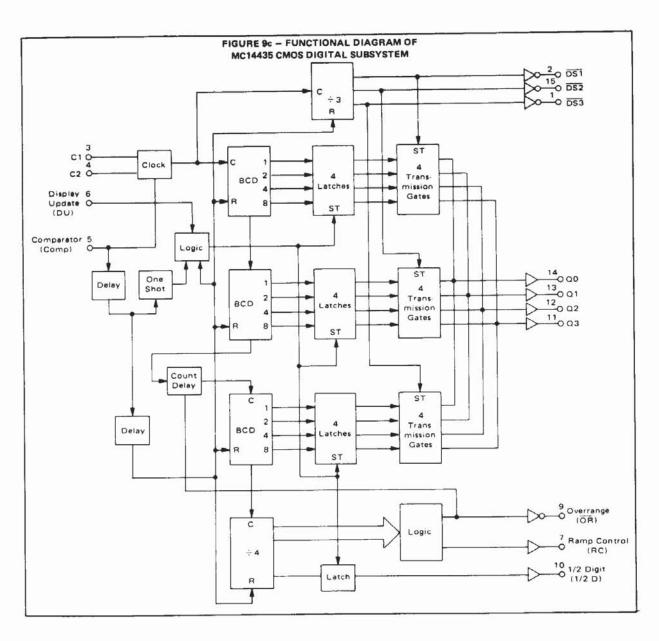

The MC1405/MC1505 is intended to perform the dual ramp function for either a 3-1/2 or 4-1/2 digit DVM or use as a general-purpose analog-to-digital (A/D) converter. It can be combined with the CMOS MC14435 logic system to produce the complete 3-1/2 digit DVM function.

The MC1505 uses the proven dual ramp A/D conversion technique. The subsystem consists of an on-chip voltage reference, a pair of voltage/current converters, an integrator, a comparator, a current switch and associated control and calibration circuitry. Only one capacitor and two calibration potentiometers are required for normal operation.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

## MC1405 MC1505

#### DUAL RAMP A/D CONVERTER SUBSYSTEM

The MC1505/MC1405 is intended to perform the dual ramp function for either a 3-1/2 or 4-1/2 digit DVM or use as a general-purpose analog-to-digital (A/D) converter. It can be combined with the CMOS MC14435 logic system to produce the complete 3-1/2 digit DVM function.

The MC1505 uses the proven dual ramp A/D conversion technique. The subsystem consists of an on-chip voltage reference, a pair of voltage/current converters, an integrator, a comparator, a current switch and associated control and calibration circuitry. Only one capacitor and two calibration potentiometers are required for normal operation.

- Accuracies to 13 Bits

- Low Power Consumption: 42 mW @ +5.0 V

- Single Power Supply Operation +5.0 V to +15 V

- Low Power Supply and Temperature Sensitivity

- Digital Inputs and Outputs Compatible with Both MTTL and **CMOS**

- Accepts Either Positive or Negative Input Voltages

- Combines with MC14435 to Produce 3-1/2 Digit A/D Converter

#### FIGURE 1 - COMPLETE A/D CONVERTER SYSTEM VCC 9+50 to +15 V Clack Integrator 41 Digital Subsystem 5 Analog Subsyster Ramp Control ntegrator Display Overrange

#### ANALOG-TO-DIGITAL CONVERTER SUBSYSTEM

SILICON MONOLITHIC INTEGRATED CIRCUIT

#### TYPICAL APPLICATIONS

BCD A/D Converter: 2-1/2 to 4-1/2 Digits (LSI or MSI Logic)

Panel Maters Digital Voltmeters Portable Instruments

Industrial Measurement and Control

Binary A/D Converter: 8-to-13 Bits (LSI or MSI Logic)

Industrial Measurement and Control

High Noise Environments (Integrating Converter with MTTL, MHTL, and CMOS Compatibility)

#### Other Uses:

Data Acquisition Systems with Remote MC1505 Voltage to Frequency Conversion Delta Modulation and Signal Generation

#### **MAXIMUM RATINGS**

| Chefecteristic                                                                                                    | Symbol           | Value                   | Unit                     |  |

|-------------------------------------------------------------------------------------------------------------------|------------------|-------------------------|--------------------------|--|

| Power Supply Voltage                                                                                              | Vcc              | +16.5                   | Vdc                      |  |

| Digital Input Voltage                                                                                             | V <sub>10</sub>  | +16.5                   | Volts                    |  |

| Reference Input Voltage                                                                                           | VR               | 2.0                     | Volts                    |  |

| Unknown Input Voltage Range                                                                                       | V1               | ±5.0                    | Volts                    |  |

|                                                                                                                   | V2               | ±5.0                    |                          |  |

| Zero Calibration Control Pin Voltage                                                                              | V4               | 5.0                     | Volts                    |  |

| Power Dissipation (Package Limitation) Ceramic Dual In-Line Package Derate above $T_{\hat{A}}$ = +25 $^{\circ}$ C | PD               | 1000<br>6.0             | mW<br>mW/ <sup>o</sup> C |  |

| Operating Ambient Temperature Range<br>MC1505L<br>MC1405L                                                         | Тд               | -55 to +125<br>0 to +70 | °C                       |  |

| Storage Temperature Range                                                                                         | T <sub>stg</sub> | -65 to +150             | °c                       |  |

|                                                                                                                   |                  |                         |                          |  |

ELECTRICAL CHARACTERISTICS ( $V_{CC}$  = +15 Vdc,  $V_R$  = 1.000 Vdc, V1 = 2.000 Vdc, V2 = 0.000 Vdc, V10  $\geqslant$  2.0 Vdc,  $T_A$  = 25°C unless otherwise noted.)

| Characteristic                                                                         | Symbol            | Figure   | MC1505          |             |        | MC1405        |             |        |         |

|----------------------------------------------------------------------------------------|-------------------|----------|-----------------|-------------|--------|---------------|-------------|--------|---------|

|                                                                                        |                   |          | Min             | Тур         | Max    | Min           | Тур         | Max    | Unit    |

| A/D CONVERSION SYSTEM (1)                                                              |                   |          |                 |             |        |               |             |        |         |

| Linearity: Deviation from Straight<br>Line through Zero and Full Scale (2)             | Er                | 9,<br>11 | -               | ±0.01       | ±0.05  | -             | ±0.01       | ±0.05  | %F.S.   |

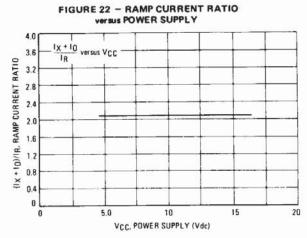

| Mid-Scale Power Supply Sensitivity<br>(PSS of IR-(IX + IQ), V1 = 1.0 V)                | PSSF              | 3        | -               | 0.002       | ±0.02  | -             | 0.002       | ±0.02  | %/%     |

| Zero Calibration Power Supply Sensitivity<br>(V1 = V2 = 0 V)                           | PSSZ              | 9        | -               | 0.001       | -      | s <del></del> | 0.001       | -      | %F.S./  |

| Input Common Mode Sensitivity (V <sub>X</sub> = 2.0 V, V <sub>CM</sub> = V2 is varied) | CMSI <sub>X</sub> | 3        | <del>- Ti</del> | 0.0006      | 0.0012 | -             | 0.0006      | 0.0018 | %/mV    |

| Full Scale Temperature Drift (3)                                                       | TCF               | 9        | -               | 0.004       | -      | -             | 0.004       | - 1    | %/°C    |

| Zero Calibration Temperature Drift (3)                                                 | TCZ               | 9        | -               | 0.001       | _      | -             | 0.001       | -      | %F.S./0 |

| VOLTAGE REFERENCE                                                                      |                   |          |                 |             |        |               |             |        |         |

| Reference Voltage, Pin 11                                                              | VREF              | 3        | 1.15            | 1.25        | 1.35   | 1,1           | 1.25        | 1.4    | Vdc     |

| Reference Voltage Power Supply Sensitivity                                             | PSSVREF           | 3        | -               | 0.003       | ±0.01  | -             | 0.003       | ±0.02  | %/%     |

| Reference Voltage Temperature Drift                                                    | TCVREF            | 3        | =               | 0.015       |        | -             | 0.015       | -      | %/°C    |

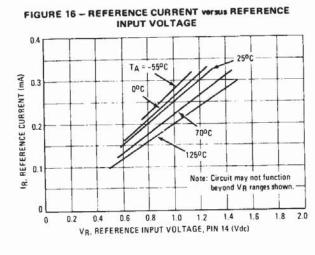

| REFERENCE CURRENT CONVERTER                                                            |                   |          |                 |             |        |               |             |        |         |

| Reference Current                                                                      | I <sub>R</sub>    | 3        | -               | 250         | -      | -             | 250         | -      | μА      |

| Input Bias Current                                                                     | 114               | 3        | -               | 10          | 40     | -             | 10          | 40     | nA      |

| Input Range of VR                                                                      | V14               | 3        | 0.8             | -           | 1.2    | 0.8           |             | 1.2    | Vdc     |

| Input Offset Voltage (V14–V15)                                                         | [VRR]             | 3        |                 | 1.0         | 2.5    | -             | 2.0         | 5.5    | m∨      |

| INPUT CURRENT CONVERTER                                                                |                   |          |                 |             |        |               |             |        |         |

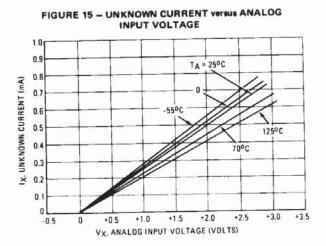

| Unknown Current                                                                        | 1x                | 3        | 2               | 500         | - 1    | -             | 500         | -      | μА      |

| Input Resistance                                                                       | RI                | 3        | -               | 4.0         | _      | -             | 4.0         | _      | kΩ      |

| Input Differential Range                                                               | V <sub>X</sub>    | 3,10     | 0               | 2.0         | -      | 0             | 2.0         | -      | Volts   |

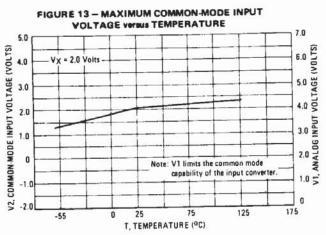

| Input Common Mode Range                                                                | CMR               | 3,10,12  | -1.5            | -           | +1.5   | -1.5          | -           | +1.5   | Volts   |

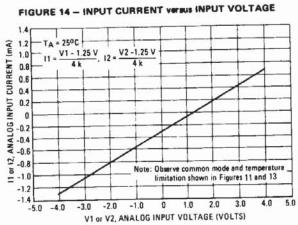

| Input Bies Currents                                                                    | 11<br>12          | 3,9      | -               | 200<br>-300 | -      | -             | 200<br>-300 | _      | μА      |

| Input Offset Voltage (V13-V3)                                                          | V <sub>X</sub> X  | 3        |                 | 1.0         | 2.5    | -             | 2.0         | 5.5    | mV      |

| RAMP OFFSET SOURCE                                                                     | •                 |          |                 |             |        | -             |             |        |         |

| Ramp Offset Current                                                                    | 10                | 4        | - 1             | 25          | - 1    |               | 25          | _      | μА      |

<sup>(1)</sup> System parameters measured using external voltage reference, independent of V11 = VREF.

Integrator Capacitor = 2.0 µF

Clock Frequency = 30 kHz

Vcc = 15 V

<sup>(2)</sup> Does not include quantizing error. See Figure 10 for calibration.

ELECTRICAL CHARACTERISTICS (VCC = +15 Vdc, VR = 1.000 Vdc, V1 = 2.000 Vdc, V2 = 0.000 Vdc, V10 > 2.0 Vdc,

| Cheracteristic                                                                                                  | = 25°C unless<br>Symbol              | Figure       | MC1505 |              |              | MC1406 |              |              |            |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------|--------|--------------|--------------|--------|--------------|--------------|------------|

|                                                                                                                 |                                      |              | Min    | Тур          | Max          | Min    | Тур          | Max          | Unit       |

| CURRENT SWITCH                                                                                                  |                                      |              |        |              |              |        |              |              | T -        |

| Digital Input Logic Levels, Pin 10 High Level, Logic "1" Low Level, Logic "Q"                                   | V <sub>IH</sub><br>V <sub>IL</sub>   | 3,18<br>3,18 | 2.0    |              | _<br>0.8_    | 2.0    | -            | 0.8          | Vdc<br>Vdc |

| Digital Input Current<br>High Level, Logic "1"<br>Low Level, Logic "0"                                          | I <sub>IH</sub>                      | 3 3          |        | 0<br>-5.0    | 1.0<br>-50   |        | 0<br>-5.0    | 1.0<br>-50   | μA<br>μA   |

| INTEGRATOR                                                                                                      |                                      |              | 2      |              |              |        |              |              |            |

| Input Bias Current                                                                                              | 16                                   | 5            | -      | 10           | 30           |        | 10           | 50           | nA         |

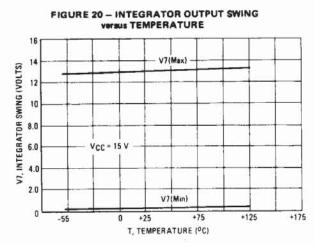

| Output Voltage Swing High Low                                                                                   | V7                                   | -            | 12.8   | 13.0<br>0.2  | 0.35         | 12.8   | 13.0<br>0.2  | 0.35         | Volts      |

| COMPARATOR                                                                                                      |                                      |              |        |              |              |        |              |              | Volt       |

| Output Logic Levels, Pin 9 High Level, Logic "1" Low Leve, Logic "0" TA = Tlow to Thigh (Sink Current = 1.6 mA) | V <sub>O</sub> H<br>V <sub>O</sub> L | 3            | 13.5   | 14.0<br>0.35 | 0.5          | 13.5   | 14.0<br>0.35 | 0.5          | Volt       |

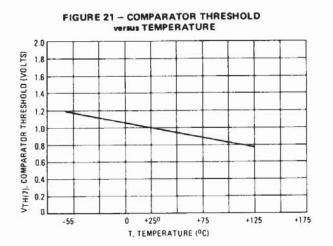

| Input Threshold                                                                                                 | VTH(7)                               |              | 0.9    | 1.0          | 1.1          | 0.9    | 1.0          | 1.1          | VOIL       |

| POWER SUPPLY                                                                                                    |                                      |              |        |              |              | т —    |              | 1            | T A        |

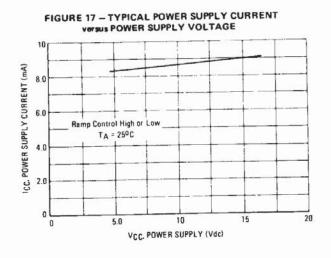

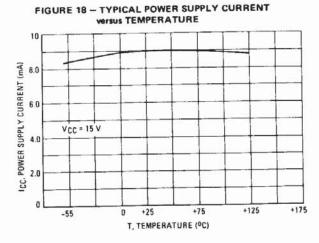

| Power Supply Current<br>(V <sub>CC</sub> = +5.0 Vdc)<br>(V <sub>CC</sub> = +15.0 Vdc)                           | lcc                                  | 3            | _      | 8.4<br>9.0   | 12.0<br>13.0 | -      | 8.4<br>9.0   | 12.0<br>13.0 | mA<br>Vdd  |

| Power Supply Voltage Range                                                                                      | Vcc                                  | -            | 4.75   |              | 16.5         | 4.75   |              | 10.5         | mW         |

| Power Consumption (V <sub>CC</sub> = +5.0 Vdc) (V <sub>CC</sub> = +15.0 Vdc)                                    | PC                                   | -            | _      | 42<br>135    | 60<br>195    | _      | 42<br>135    | 60<br>195    | linvi      |

T<sub>low</sub> = -55°C for MC1505L, 0°C for MC1405L T<sub>high</sub> = +125°C for MC1505L, +70°C for MC1405L

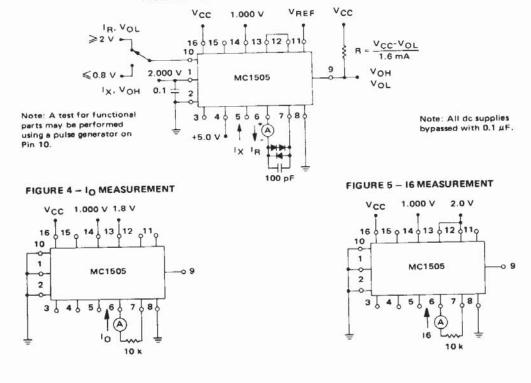

#### FIGURE 3 - STANDARD TEST CONFIGURATION

#### GENERAL INFORMATION

#### **Dual Ramp Analog-to-Digital Conversion**

The dual ramp method of A/D conversion is a proven system which is capable of very high accuracy. The conversion is an integrating process which offers high noise rejection and immunity to changes in the clock rate and integrator capacitor value. The particular method used in the MC1505 is a noniterating dual slope technique which produces an accurate result after one conversion period.

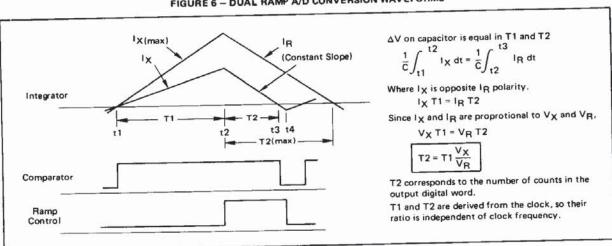

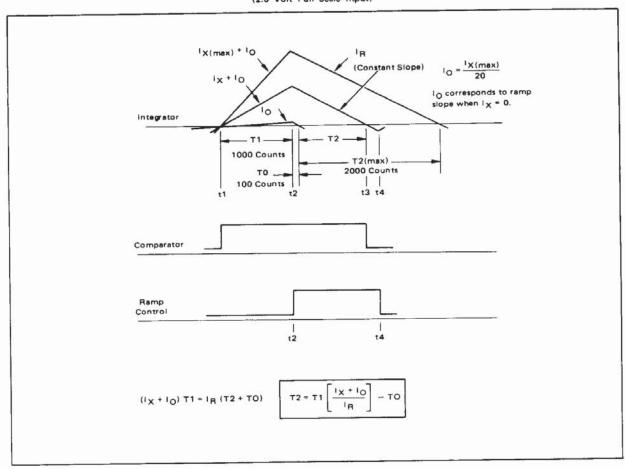

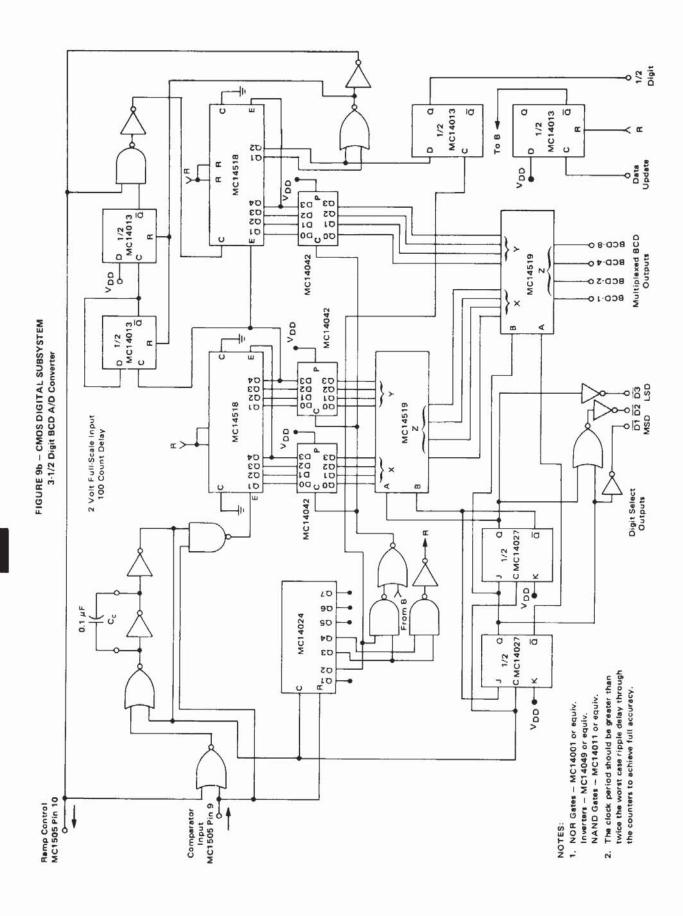

Dual ramp conversion is accomplished with the system of Figure 2. The conversion begins at time t1, when current IX causes the integrator output, or ramp, to cross the comparator threshold, as shown in Figure 6. The clock is activated and the counters begin counting from zero. The system counts for a fixed period T, with a ramp slope which depends on the input voltage, i.e., a steep slope is caused by a high input voltage. When the counters have reached full scale, the overflow count triggers a ÷ 2 flipflop which changes the ramp control polarity current. IR

#### A/D Subsystem Circuit Description

The MC1505 incorporates special circuit features which allow all the analog functions of the dual ramp system to be performed on a single monolithic chip using standard bipolar processing.

Voltage-to-current conversion for both the input and reference voltages allows the use of a high-speed current switch and single supply operation. The unbuffered differential inputs have sufficiently high input impedance for power supply monitoring applications, and provide flexibility for other input formats since they will accept either positive or negative voltages.

The voltage reference, shown in Figure 7, is one of the six basic circuits in the subsystem. It provides a low impedance output which has excellent temperature stability, and high power supply rejection. Biasing for the other circuits in the MC1505 is derived from the voltage reference circuitry.

FIGURE 6 - DUAL RAMP A/D CONVERSION WAVEFORMS

now controls the integrator and the down ramp begins at t2. This ramp continues at a fixed slope for a time period which depends on the amplitude achieved by the up ramp. Thus T2 is determined by the input voltage. When the ramp crosses the comparator threshold at t3, the clock stops and the counter holds a digital value which is proportional to the unknown input voltage.

After the down ramp crosses the comparator threshold, a timing sequence in the digital section strobes the latches to store the data, resets the counters, and reverses the ramp at t4 to begin a new conversion.

Since the voltage change across the capacitor is equal on the up and down ramps, an equal amount of charge is exchanged. The equations of Figure 6 show that the system output is the ratio of the unknown and reference currents, and long term changes in the clock rate and integrator capacitor do not effect the reading.

The same basic amplifier circuit is used in both the reference and input voltage-to-current converters. It is an extremely well balanced amplifier with low input offset voltage temperature drift. The reference converter uses a pair of PNP transistors to derive current IR, in conjunction with a reference resistor which has the same temperature coefficient as those used in the input converter. The value of the reference current is VR/R5. The collectors of transistors Q1, Q2 and Q3 in Figure 7 all track with a two diode temperature coefficient, which assures constant current ratios.

The reference resistor value can vary by 30% of 4.0  $k\Omega$  due to process variations. Moreover, these variations will also affect the input bridge resistors. Thus, the ratio of reference to unknown current has a close tolerance for a wide range of resistor values.

The input voltage-to-current converter is a bridge or bilateral current source whose output current is VX/R1. If the bridge is perfectly balanced, its output impedance and common mode rejection are infinite. However, the design has the ability to tolerate bridge mismatches of approximately 0.5%. In order to tolerate this mismatch, the output of the bridge current source is connected to the current switch which is a low temperature coefficient, low impedance source of 1.25 volts. This technique effectively eliminates output current changes due to finite output impedance which is caused by resistor mismatch. This input current converter makes possible the use of a single supply voltage and differential inputs which can be used at or below ground potential.

An important feature of the MC1505 is the ramp offset current source which is added to the unknown current and does not allow the ramp to reach zero slope when the input voltage is zero. The ramp range is shown in Figure 8. The ramp offset current has a value of IR/10, so that the minimum ramp slope is 5% of the full scale slope. This allows reliable conversion at low input voltages by assuring a nearly constant comparator propagation delay and a good ramp signal-to-noise ratio. It also prevents turn-off

of the diode in the current switch at low levels, restricting the voltage change at the output of the resistor bridge. Still another feature is that it provides a convenient temperature compensated zero adjust which can correct errors in the resistor bridge and input buffer amplifiers when they are used. The ramp offset current is compensated by 100 extra counts in the digital logic during ramp down, so it does not appear in the digital output (see Figure 8).

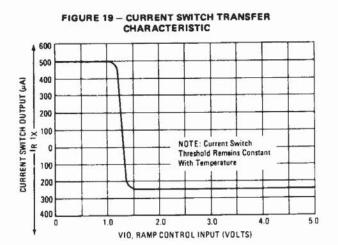

The current switch uses current steering for very high speed operation. A smooth transition occurs as one current is turned on while the other is turned off. This minimizes error during the ramp reversal at its peak, especially since the reference current source has a very high output impedance and does not change value when switched. The settling time of the input current converter is not a factor in system accuracy. At the ramp peak, Ix is turned off, so the amplifier settles after the unknown current is decoupled from the integrator. When the ramp is below the comparator threshold, the unknown current is switched on and thus the current can settle before the ramp enters the active conversion range. The switch operates into a voltage of 1.95 volts and is translated by a follower so its input

V<sub>C</sub>C Reference Output VREF = 1.25 V 16 Voltage Reference 2X 2 X Reference Input V R 03 01 02 Reference 15 o Test Reference 85 V-I Converter 1.25 V + VBE Comparator Current Output Switch Ramp 100 Control Integrator Comparator Input 10 V-I Converter VX = V1-V2 4.0 k VR = V14 R4 R2 VREF = V11 1.0 k Analog (-) 2 o input (+) 1 o R1 1x = Vx/R1 4.0 k 1R = VA/R5 1.0 k 10 = 18/10 4 5 12 6 3 13 O Input Output Input Zero Test Adjust Integrator

FIGURE 7 - A/D CONVERTER ANALOG SUBSYSTEM

FIGURE 8 - MC1505 SYSTEM TIMING DIAGRAM

(2.0 Volt Full Scale Input)

threshold is 1.25 volts.

The integrator is a single stage, wide bandwidth amplifier. Its low propagation delay and low output impedance minimize ramp spikes due to output current reversal during ramp turn-around. The input bias current is typically one part in 50,000 of the full scale current, so that its temperature change contributes negligible error. Gain and input offset voltage are not critical since the integrator is driven from current sources.

The comparator is designed for low hysteresis by maintaining a constant power dissipation regardless of output state. This hysteresis is typically 0.1 mV and remains constant with temperature variations, so that no measurable system error is contributed. Temperature vari-

ations in the value of the comparator threshold are not an error factor, since the only requirement is that the threshold remain constant during a given conversion cycle. Voltage gain of the comparator is 2,000,000 when driving CMOS, and 40,000 with one TTL load. The comparator output is slew rate controlled to provide output rise and fall times of approximately 80 ns. This minimizes noise generation which could affect system stability.

The system is zeroed and full scale calibrated by potentiometers which provide temperature compensation. All the other resistors are diffused in close proximity, yielding reference and unknown currents which have a closely tracking resistive temperature coefficient.

#### 8

#### APPLICATIONS INFORMATION

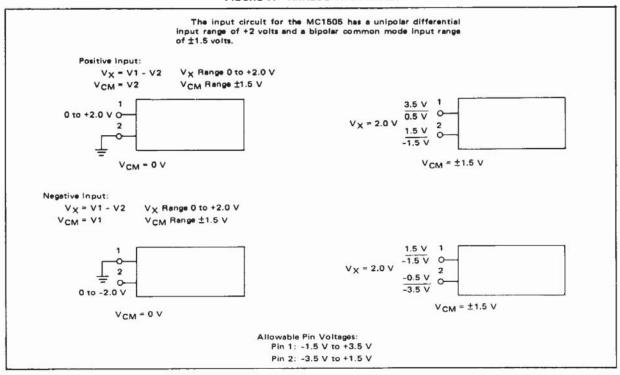

The input configurations for the MC1505 are shown in Figure 11. Note that the differential input voltage must always remain the same polarity with Pin 1 positive with respect to Pin 2. Figures 11 and 13 will aid in the understanding of the input circuitry.

The input common mode rejection of the MC1505 is high enough to maintain rated accuracy with small changes in common mode voltage, such as would be seen with ground errors and noise. The system must be recalibrated, however, for larger changes in common mode input voltage.

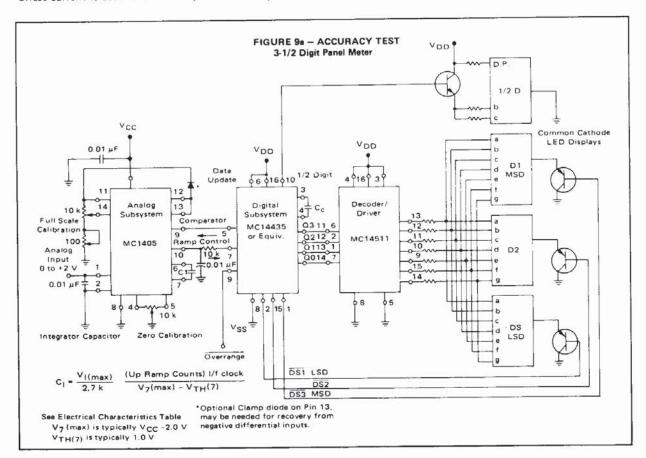

The MC1505 is arranged so that  $I_X = I_R$  when  $V_X = V_R$ , or so that the ramp slopes are equal for input and reference voltages of 1 volt. As shown in Figure 8, a system with a 2 volt full-scale input requires twice as many digital counts during T2 as for T1. A system with a 1 volt full scale would require an equal number of counts in T1 and T2. Figure 9 illustrates a 3-1/2 digit system, but typical accuracies of the MC1505 allow its use in 4 digit applications. It can also be used in systems which require 4-1/2 digit resolution.

The ramp offset current and 100 count delay are shown in Figure 8. In certain applications, a different number of counts may be used. The system will not always operate properly, however, with a 10 count delay since the ramp offset current is used to zero the system and compensate

for error in the input resistor bridge. This error, known as IXO, is current which flows to or from the input converter with zero volts applied to the input. It is typically between  $\pm 5.0~\mu$ A, which is 1% of full scale in a 2 volt system. A 10 count delay would need a 0.5% ramp offset current, which would not always be able to cancel this error. Also, a 10 count delay does not provide enough signal-to-noise margin for consistently accurate low-level conversion.

The integrating capacitor is chosen with the equations shown in Figure 9. The maximum ramp voltage should be used for best signal-to-noise ratio, but temperature changes in IX, IR and the capacitor should be anticipated to prevent integrator saturation. Variations in clock frequency should also be considered. A polar capacitor with Pin 7 at the + terminal may be used. However, settling time will be increased when electrolytics are used, Tantalum electrolytics are preferred.

The lower half of the diode current switch is split with separate diodes for IX and IO. In most applications Pins 12 and 13 will be connected so that the two device emitters are effectively one, since the main purpose of these pins is for testing. Connecting these pins allows proper system zero adjustment and prevents turn-off of the switch diode with low unknown current levels. This yields better conversion accuracy.

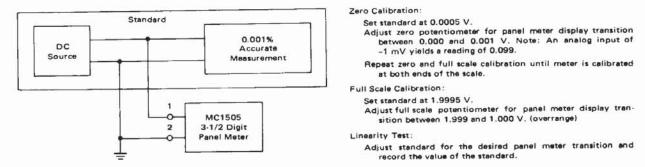

FIGURE 10 - CALIBRATION SET-UP

At initial turn-on, set Pin 14 to ≈1.0 Volt with full scale potentiometer.

#### FIGURE 11 - ANALOG INPUT RANGE

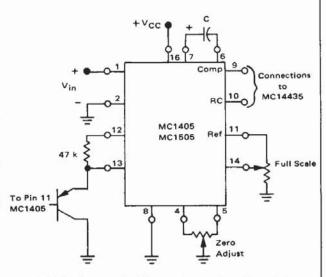

FIGURE 12 – CIRCUIT TO PREVENT POSSIBLE LATCHUP WITH APPLICATION OF NEGATIVE INPUT VOLTAGES

The MC1405/1505 A/D analog subsystem is intended for positive input voltages only (i.e., pin 1 positive with respect to pin 2). However, should pin 2 become more than 100 mV positive with respect to pin 1, the internal input amplifier may go into a latchup mode which will require that the system power be turned off and then reapplied to reset the system. To prevent this problem a PNP transistor can be used as shown in the accompanying figure. The base-emitter junction of the transistor clamps pin 13 at one diode drop above the reference voltage (pin 11) to prevent the latchup. The gain of the transistor insures that the reference need not sink more than 500 µA of current.

The 47  $k\Omega$  resistor is required only if the A/D system is to continue to convert under reverse polarity conditions such as for autopolarity schemes.

\*47 k $\Omega$  resistor required if conversions are to continue during input polarity reversal, otherwise tie pins 12 and 13 together.

#### TYPICAL PERFORMANCE CURVES

If a voltage drop of  $2.0~\rm V$  full scale can be tolerated the resistors may be increased by a factor of ten and a unity gain buffer may be employed.

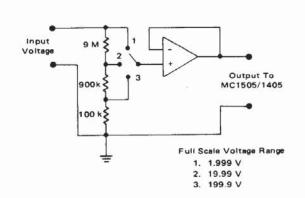

#### FIGURE 24 - DVM VOLTAGE RANGING

Overrange 2 IO X S\1 ETACOM The clock period should be greater than twice the worst case ripple delay through the counters to achieve full accuracy. Notes: 1. NAND Gates = MC7400 or equiv. NOR Gates = MC7402 or equiv. VCC Inverters = MC7404 or equiv. The counter delay should be approximately 10% of T1, hence 512 counts. 2 IO ⊼ 2\1 2\12 MC7473M 0 0 2/r 67479M Q IQ ,cc Vcc MSB ST MC7475 00 01 02 03 DO D1 D2 D3 ü 6 6 6 A4 A3 A2 A MC7493 ej ri 80 8 0 0 0 A7 A6 A5 ST MC7475 C1 Q0 Q1 Q2 Q3 Binary Outputs DO 01 D2 D3 8 FIGURE 25 — MTTL DIGITAL SUBSYSTEM 12 Bit Binary A/D Converter (1.0 Volt Full Scale, 512 Count Delay) 98 89 00 ST MC7475 C1 00 01 02 03 0 0 0 0 A12A11A10A9 DO D1 D2 D3 Oco RO To A **▼** To R Strobe LSB Clock Frequency ≥ 250 kHz 6.2 k 0.001 µF 00 0102 03 C1 MC7493 80 00 0.001 µF 6.2 K 111 Comparator Input of MC1505 (Pin 9) Ramp Control of MC1505 (Pin 10) 1

FIGURE 26 - 12-BIT BINARY A/D LOGIC SUBSYSTEM

5