# **AM79C984A**

# Enhanced Integrated Multiport Repeater (eIMR)

The enhanced Integrated Multiport Repeater (eIMR) device is a VLSI integrated circuit that provides a system-level solution to designing non-managed multiport repeaters. The device integrates the repeater functions specified in Section 9 of the IEEE 802.3 standard and Twisted Pair Transceiver functions complying with the 10BASE-T standard.

The device is fabricated in CMOS technology and requires a single +5-V supply.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# AMDA

# Am79C984A

## enhanced Integrated Multiport Repeater (eIMR™)

#### **DISTINCTIVE CHARACTERISTICS**

- Repeater functions comply with IEEE 802.3 Repeater Unit specifications

- Four integral 10BASE-T transceivers with onchip filtering that eliminate the need for external filter modules on the 10BASE-T transmit-data (TXD) and receive-data (RXD) lines

- One Reversible Attachment Unit Interface (RAUI™) port that can be used either as a standard IEEE-compliant AUI port for connection to a Medium Attachment Unit (MAU), or as a reversed port for direct connection to a Media Access Controller (MAC)

- Low cost suitable for non-managed multiport repeater designs

- Expandable to increase number of repeater ports with support for up to seven elMR devices without the need for an external arbiter

- All ports can be individually isolated (partitioned) in response to excessive collision conditions or fault conditions.

- Full LED support for individual port status LEDs and network utilization LEDs

- Programmable extended distance mode on the RXD lines, allowing connection to cables longer than 100 meters

- Twisted Pair Link Test capability conforming to the 10BASE-T standard. The Link Test function and the transmission of Link Test pulses can be optionally disabled through the control port to allow devices that do not implement the Link Test function to work with the eIMR device.

- Programmable option of automatic polarity detection and correction permits automatic recovery due to wiring errors

- Full amplitude and timing regeneration for retransmitted waveforms

- CMOS device with a single +5-V supply

#### **GENERAL DESCRIPTION**

The enhanced Integrated Multiport Repeater (eIMR) device is a VLSI integrated circuit that provides a system-level solution to designing non-managed multiport repeaters. The device integrates the repeater functions specified in Section 9 of the IEEE 802.3 standard and Twisted Pair Transceiver functions complying with the 10BASE-T standard.

The eIMR device provides four Twisted Pair (TP) ports and one RAUI port for direct connection to a MAC. The total number of ports per repeater unit can be increased by connecting multiple eIMR devices through their expansion ports, hence, minimizing the total cost per repeater port.

The device is fabricated in CMOS technology and requires a single +5-V supply.

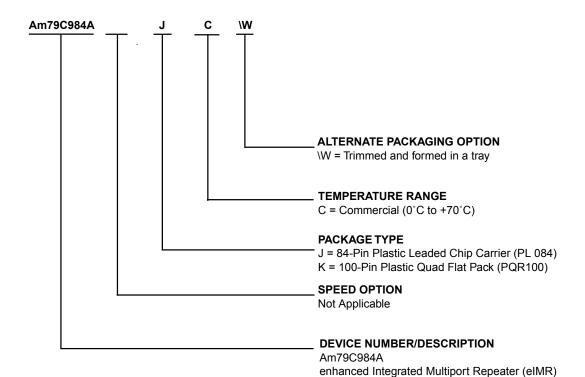

### **ORDERING INFORMATION**

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

| Valid Combinations |          |  |  |  |  |

|--------------------|----------|--|--|--|--|

| Am79C984A          | JC, KC\W |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

2 Am79C984A

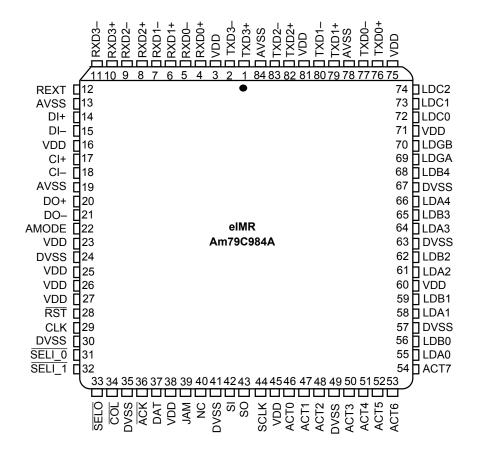

### **CONNECTION DIAGRAM (PL 084)**

20650B-2

Am79C984A 7

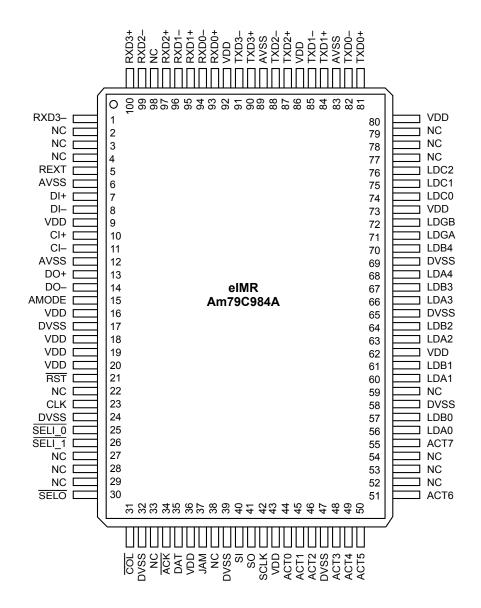

## **CONNECTION DIAGRAM (PQR100)**

20650B-3

### **ABSOLUTE MAXIMUM RATINGS**

Storage Temperature .........-65° C to +150° C Ambient Temperature Under Bias ..... 0° C to +70° C Supply Voltage referenced to  $AV_{SS}$  or  $DV_{SS}$  ( $AV_{DD}$ ,  $DV_{DD}$ )......-0.3 V to +6.0 V

Stresses above those listed under ABSOLUTE MAXI-MUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect reliability. Programming conditions may

### **OPERATING RANGES**

### Commercial (C) Devices

Operating ranges define those limits between which the functionality of the device is guaranteed.

## DC CHARACTERISTICS over operating ranges unless otherwise specified

| Parameter<br>Symbol  | Parameter Description                                        | Test Conditions                                     | Min                   | Max                   | Unit |

|----------------------|--------------------------------------------------------------|-----------------------------------------------------|-----------------------|-----------------------|------|

| Digital I/O          |                                                              |                                                     |                       |                       |      |

| V <sub>IL</sub>      | Input LOW Voltage                                            | V <sub>SS</sub> = 0.0 V                             | -0.5                  | 0.8                   | V    |

| V <sub>IH</sub>      | Input HIGH Voltage                                           | V <sub>SS</sub> = 0.0 V                             | 2.0                   | 0.5 + V <sub>DD</sub> | V    |

| V <sub>OL</sub>      | Output LOW Voltage                                           | I <sub>OL</sub> = 4.0 mA                            | _                     | 0.4                   | V    |

| V <sub>OH</sub>      | Output HIGH Voltage                                          | I <sub>OH</sub> = -0.4 mA                           | 2.4                   | -                     | V    |

| I <sub>IL</sub>      | Input Leakage Current                                        | $V_{SS} < V_{IN} < V_{DD}$                          | _                     | 10                    | μΑ   |

| I <sub>ILSTR</sub>   | Input Leakage Current for STR pin                            | V <sub>SS</sub> <v<sub>IN<v<sub>DD</v<sub></v<sub>  | _                     | 50                    | μΑ   |

| $V_{OLOD}$           | Open Drain Output LOW Voltage (LED pins)                     | $I_{OLOD}$ = 12 mA                                  | _                     | 0.4                   | V    |

| AUI Ports            |                                                              |                                                     |                       |                       |      |

| $I_{IAXD}$           | Input Current at DI± and CI± Pairs                           | $V_{SS}$ < $V_{IN}$ < $V_{DD}$                      | -500                  | 500                   | μΑ   |

| V <sub>AICM</sub>    | DI±, CI± Open Circuit Input Voltage Range                    | I <sub>IN</sub> = 0                                 | V <sub>DD</sub> – 3.0 | V <sub>DD</sub> – 1.0 | V    |

| $V_{AIDV}$           | Differential Mode Input Voltage Range (DI, CI)               | V <sub>DD</sub> = 5.0 V                             | -2.5                  | +2.5                  | V    |

| V <sub>ASQ</sub>     | DI, CI Squelch Threshold                                     | _                                                   | -275                  | -160                  | mV   |

| V <sub>ATH</sub>     | DI Switching Threshold                                       | (Note 1)                                            | -35                   | +35                   | mV   |

| V <sub>AOD</sub>     | Differential Output Voltage   (DO+) – (DO)                   | R <sub>L</sub> = 78 Ω                               | 620                   | 1100                  | mV   |

| V <sub>AOC</sub>     | Differential Output Voltage   (CI+) – (CI–)   (Reverse Mode) | $R_L = 78 \Omega$                                   | 620                   | 1100                  | mV   |

| V <sub>AODI</sub>    | DO Differential Output Voltage Imbalance                     | R <sub>L</sub> = 78 Ω                               | -25                   | +25                   | mV   |

| V <sub>AOD</sub> OFF | DO Differential Idle Output Voltage                          | $R_L = 78 \Omega$                                   | -40                   | +40                   | mV   |

| I <sub>AOD</sub> OFF | DO Differential Idle Output Current                          | R <sub>L</sub> = 78 Ω (Note 1)                      | -1.0                  | +1.0                  | mA   |

| V <sub>AOCM</sub>    | DO+, DO- Common Mode Output Voltage                          | R <sub>L</sub> = 78 Ω                               | 2.5                   | V <sub>DD</sub>       | V    |

| Twisted Pa           | ir Ports                                                     |                                                     |                       |                       |      |

| I <sub>IRXD</sub>    | Input Current at RXD± and Cl± Pairs                          | AV <sub>SS</sub> <v<sub>IN<v<sub>DD</v<sub></v<sub> | -500                  | 500                   | μΑ   |

| R <sub>RXD</sub>     | RXD Differential Input                                       | (Note 1)                                            | 10                    | -                     | kΩ   |

| $V_{TIVB}$           | RXD+, RXD– Open Circuit Input Voltage (bias)                 |                                                     | V <sub>DD</sub> – 3.0 | V <sub>DD</sub> – 1.5 | V    |

| $V_{TID}$            | Differential Mode Input<br>Range (RXD)                       | V <sub>DD</sub> = 5.0 V                             | -3.1                  | +3.1                  | V    |

32 Am79C984A

# **DC CHARACTERISTICS (continued)**

| Parameter<br>Symbol | Parameter Description                                          | Test Conditions                                                                           | Min  | Max         | Unit |

|---------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|-------------|------|

| Twisted Pa          | ir Ports (Continued)                                           | ·                                                                                         |      |             |      |

| V <sub>TSQ+</sub>   | RXD Positive Squelch Threshold (peak)                          | Sinusoid<br>5 MHz <f<10 mhz<="" td=""><td>300</td><td>520</td><td>mV</td></f<10>          | 300  | 520         | mV   |

| V <sub>TSQ</sub>    | RXD Negative Squelch Threshold (peak)                          | Sinusoid<br>5 MHz <f<10 mhz<="" td=""><td>-520</td><td>-300</td><td>mV</td></f<10>        | -520 | -300        | mV   |

| V <sub>THS+</sub>   | RXD Post-Squelch Positive<br>Threshold (peak)                  | Sinusoid<br>5 MHz <f<10 mhz<="" td=""><td>150</td><td>293</td><td>mV</td></f<10>          | 150  | 293         | mV   |

| V <sub>THS</sub> -  | RXD Post-Squelch Negative<br>Threshold (peak)                  | Sinusoid<br>5 MHz <f<10 mhz<="" td=""><td>-293</td><td><b>–150</b></td><td>mV</td></f<10> | -293 | <b>–150</b> | mV   |

| V <sub>LTSQ+</sub>  | RXD Positive Squelch Threshold (peak) - Extended Distance Mode | Sinusoid<br>5 MHz <f<10 mhz<="" td=""><td>180</td><td>365</td><td>mV</td></f<10>          | 180  | 365         | mV   |

| $V_{LTSQ-}$         | RXD Negative Squelch Threshold (peak) - Extended Distance Mode | Sinusoid<br>5 MHz <f<10 mhz<="" td=""><td>-365</td><td>-180</td><td>mV</td></f<10>        | -365 | -180        | mV   |

| V <sub>LTHS+</sub>  | RXD Post-Squelch Positive Threshold - Extended Distance Mode   | Sinusoid<br>5 MHz <f<10 mhz<="" td=""><td>90</td><td>175</td><td>mV</td></f<10>           | 90   | 175         | mV   |

| V <sub>LTHS</sub> _ | RXD Post-Squelch Negative Threshold - Extended Distance Mode   | Sinusoid<br>5 MHz <f<10 mhz<="" td=""><td>-175</td><td>-90</td><td>mV</td></f<10>         | -175 | -90         | mV   |

| V <sub>RXDTH</sub>  | RXD Switching Threshold                                        | (Note 1)                                                                                  | -60  | 60          | mV   |

|                     | ply Current                                                    |                                                                                           | •    |             |      |

| I <sub>DD</sub>     | Power Supply Current (Idle) (Note 2)                           | CLK = 20 MHz<br>V <sub>DD</sub> = +5.25V                                                  | _    | 100         | mA   |

|                     | Power Supply Current (Transmitting)                            | CLK = 20 MHz<br>V <sub>DD</sub> = +5.25V                                                  | _    | 350         | mA   |

#### Notes:

- 1. Parameter not tested.

- 2. LED current not included. Maximum current rating on LED drivers is 12 mA.

## **SWITCHING CHARACTERISTICS**

| Parameter<br>Symbol  | Parameter Description                                                 | Test Conditions                                | Min    | Max    | Unit |

|----------------------|-----------------------------------------------------------------------|------------------------------------------------|--------|--------|------|

| Clock and            | Reset Timing                                                          |                                                |        | •      |      |

| t <sub>CLK</sub>     | CLK Clock Period                                                      |                                                | 49.995 | 50.005 | ns   |

| t <sub>CLKH</sub>    | CLK Clock High                                                        |                                                | 20     | 30     | ns   |

| t <sub>CLKL</sub>    | CLK Clock Low                                                         |                                                | 20     | 30     | ns   |

| t <sub>CLKR</sub>    | CLK Rise Time                                                         |                                                | _      | 10     | ns   |

| t <sub>CLKF</sub>    | CLK Fall Time                                                         |                                                | _      | 10     | ns   |

| t <sub>PRST</sub>    | Reset Pulse Width after Power On                                      |                                                | 150    | -      | μs   |

| t <sub>RST</sub>     | Reset Pulse Width                                                     |                                                | 4      | -      | μs   |

| t <sub>RSTSET</sub>  | Reset HIGH Setup Time with respect to CLK                             |                                                | 15     | -      | ns   |

| t <sub>RSTHLD</sub>  | Reset LOW Hold Time                                                   |                                                | 0      | -      | ns   |

| t <sub>XRS</sub>     | AMODE, SELI <sub>0</sub> , and SI_D Setup Time to Rising Edge of RST  |                                                | 0      | -      | ns   |

| t <sub>XRH</sub>     | AMODE, SELI <sub>0</sub> , and SI_D Hold Time from Rising Edge of RST |                                                | 400    | -      | ns   |

| AUI Port Ti          | ming                                                                  | 1                                              |        |        |      |

| t <sub>DOTD</sub>    | CLK Rising Edge to DO Toggle                                          |                                                | _      | 30     | ns   |

| t <sub>DOTR</sub>    | DO+, DO- Rise Time (10% to 90%)                                       |                                                | _      | 7.0    | ns   |

| t <sub>DOTF</sub>    | DO+, DO- Fall Time (90% to 10%)                                       |                                                | _      | 7.0    | ns   |

| t <sub>DORM</sub>    | DO+, DO- Rise and Fall Time Mismatch                                  |                                                | _      | 1.0    | ns   |

| t <sub>DOETD</sub>   | DO± End of Transmission                                               |                                                | 275    | 375    | ns   |

| t <sub>PWODI</sub>   | DI Pulse Width Accept/Reject Threshold                                | V <sub>IN</sub>  > V <sub>ASQ</sub>   (Note 2) | 15     | 45     | ns   |

| t <sub>PWKDI</sub>   | DI Pulse Width Not to Turn-off Internal<br>Carrier Sense              | V <sub>IN</sub>  > V <sub>ASQ</sub>   (Note 3) | 136    | 200    | ns   |

| t <sub>PWOCI</sub>   | CI Pulse Width Accept/Reject Threshold                                | V <sub>IN</sub>  > V <sub>ASQ</sub>   (Note 4) | 10     | 26     | ns   |

| t <sub>PWKCI</sub>   | CI Pulse Width Not to Turn-off Threshold                              | V <sub>IN</sub>  > V <sub>ASQ</sub>   (Note 5) | 75     | 160    | ns   |

| t <sub>CITR</sub>    | CI Rise Time (In Reverse Mode)                                        |                                                | _      | 7.0    | ns   |

| t <sub>CITF</sub>    | CI Fall Time (In Reverse Mode)                                        |                                                | -      | 7.0    | ns   |

| t <sub>CIRM</sub>    | CI+, CI– Rise and Fall Time Mismatch (AUI in Reverse Mode)            |                                                | _      | 1.0    | ns   |

| Expansion            | Bus Timing                                                            | _                                              |        |        |      |

| t <sub>CLKHRL</sub>  | CLK HIGH to SELO Driven LOW                                           | C <sub>L</sub> = 50 pF                         | 15     | 30     | ns   |

| t <sub>CLKHRH</sub>  | CLK HIGH to SELO Driven HIGH                                          | C <sub>L</sub> = 50 pF                         | 15     | 30     | ns   |

| t <sub>CLKHDR</sub>  | CLK HIGH to DAT/JAM Driven                                            | C <sub>L</sub> = 100 pF                        | 14     | 30     | ns   |

| t <sub>CLKHDZ</sub>  | CLK HIGH to DAT/JAM Not Driven                                        | C <sub>L</sub> = 100 pF                        | 14     | 30     | ns   |

| t <sub>DJSET</sub>   | DAT/JAM Setup Time to CLK                                             |                                                | 10     | _      | ns   |

| t <sub>DJHOLD</sub>  | DAT/JAM Hold Time from CLK                                            |                                                | 9      | -      | ns   |

| t <sub>CASET</sub>   | COL/ACK Setup Time to CLK                                             |                                                | 10     | -      | ns   |

| t <sub>CAHLD</sub>   | COL/ACK Hold Time from CLK                                            |                                                | 9      | -      | ns   |

| t <sub>SCLKHLD</sub> | SI, SCLK Hold Time                                                    |                                                | 50     | _      | ns   |

### **SWITCHING CHARACTERISTICS (continued)**

| Parameter<br>Symbol | Parameter Description                       | Test Conditions                                | Min | Max | Unit |  |  |

|---------------------|---------------------------------------------|------------------------------------------------|-----|-----|------|--|--|

| Twisted Pa          | Twisted Pair Port Timing                    |                                                |     |     |      |  |  |

| t <sub>TXTD</sub>   | CLK Rising Edge to TXD± Transition Delay    |                                                | -   | 50  | ns   |  |  |

| t <sub>TETD</sub>   | Transmit End of Transmission                |                                                | 250 | 375 | ns   |  |  |

| t <sub>PWKRD</sub>  | RXD Pulse Width Maintain/Turn-off Threshold | V <sub>IN</sub>  > V <sub>THS</sub>   (Note 6) | 136 | 200 | ns   |  |  |

| t <sub>PERLP</sub>  | Idle Signal Period                          |                                                | 8   | 24  | ms   |  |  |

| t <sub>PWLP</sub>   | Idle Link Test Pulse Width                  |                                                | 75  | 120 | ns   |  |  |

| Control Por         | Control Port Timing                         |                                                |     |     |      |  |  |

| t <sub>SCLK</sub>   | SCLK Clock Period                           |                                                | 100 | _   | ns   |  |  |

| t <sub>SCLKH</sub>  | SCLK Clock HIGH                             |                                                | 30  | -   | ns   |  |  |

| t <sub>SCLKL</sub>  | SCLK Clock LOW                              |                                                | 30  | -   | ns   |  |  |

| t <sub>SCLKR</sub>  | SCLK Clock Rise Time                        |                                                | _   | 10  | ns   |  |  |

| t <sub>SCLKF</sub>  | SCLK Clock Fall Time                        |                                                | _   | 10  | ns   |  |  |

| t <sub>SISET</sub>  | SI Input Setup Time to SCLK Rising Edge     |                                                | 10  | -   | ns   |  |  |

| t <sub>SIHLD</sub>  | SI Input Hold Time from SCLK Rising Edge    |                                                | 10  | _   | ns   |  |  |

| t <sub>SODLY</sub>  | SO Output Delay from SCLK Rising Edge       | C <sub>L</sub> = 100 pF                        | -   | 40  | ns   |  |  |

#### Notes:

- 1. Parameter not tested.

- 2. DI pulses narrower than  $t_{PWODI}$  (min) will be rejected; pulses wider than  $t_{PWODI}$  (max) will turn internal DI carrier sense on.

- 3. DI pulses narrower than t<sub>PWKDI</sub> (min) will maintain internal DI carrier on; pulses wider than t<sub>PWKDI</sub> (max) will turn internal DI carrier sense off.

- 4. CI pulses narrower than t<sub>PWOCI</sub> (min) will be rejected; pulses wider than t<sub>PWOCI</sub> (max) will turn internal CI carrier sense on.

- 5. CI pulses narrower than t<sub>PWKCI</sub> (min) will maintain internal CI carrier on; pulses wider than t<sub>PWKCI</sub> (max) will turn internal CI carrier sense off.

- 6. RXD pulses narrower than t<sub>PWKRD</sub> (min) will maintain internal RXD carrier sense on; a pulse wider than t<sub>PWKRD</sub> (max) will turn RXD carrier sense off.