## Quad High Speed Amplifier

AD8026

#### **FEATURES**

Voltage Feedback, Rail-to-Rail Output

Rated Settling Time to Within 0.5 V of Supply Rail

Quad High Speed Amplifier

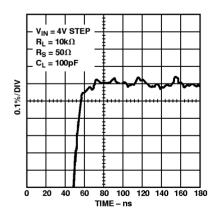

Settling Time to 0.1% of 55 ns (4 V Swing, C<sub>L</sub> = 100 pF)

Slew Rate 135 V/μs (4 V Swing)

-3 dB Bandwidth 60 MHz

Fixed Gain Resistors for High DC Accuracy

Low Voltage Offset 0.5 mV RTO Typical

Gain Error Less than 0.05%

Low Supply Current 3.4 mA

Nominal +12 V Supply

14-Lead SOIC Package

APPLICATIONS LCD Source Drivers CD DVD CDR

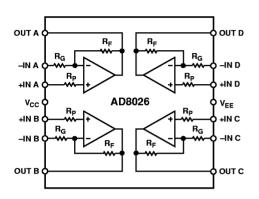

#### FUNCTIONAL BLOCK DIAGRAM

#### PRODUCT DESCRIPTION

The AD8026 is a complete low cost, closed loop, voltage feedback, quad amplifier. Precision trimmed resistors set a fixed  $R_{\rm F}/R_{\rm G}$  ratio of 5/3 to a typical gain accuracy of 0.02%. Manufactured on ADI's proprietary XFCB high speed bipolar process, which enables the output drivers to settle to within 0.1% within 55 ns into a 100 pF load (4 V swing) and drive output voltages to rated settling time to within 0.5 V from the rail. The typical 3 dB bandwidth is 60 MHz, at G=+2.67. The AD8026 is laser trimmed to produce both exceptional offset and gain performance.

The low settling time, high slew rate, low offset and rail-to-rail output voltage drive capability makes the AD8026 ideal for driving LCD displays.

The AD8026 is available in a 14-lead SOIC package.

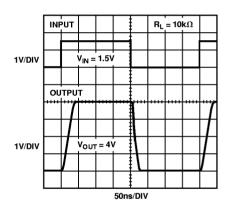

Figure 1. 4 V Step Response

#

| Parameter                                                    | Conditions                                                            | Min | Тур       | Max  | Units                     |

|--------------------------------------------------------------|-----------------------------------------------------------------------|-----|-----------|------|---------------------------|

| DYNAMIC PERFORMANCE  -3 dB Small Signal Bandwidth            | $V_{IN} = 50 \text{ mV rms}$                                          |     |           |      |                           |

| Bandwidth for 0.1 dB Flatness                                | $R_{L} = 1 \text{ k}\Omega$ $V_{IN} = 50 \text{ mV rms}$              | 20  | 60        |      | MHz                       |

| Danawam for our ab Thaness                                   | $R_{\rm L} = 1 \text{ k}\Omega$                                       |     | 12        |      | MHz                       |

| Slew Rate                                                    | $V_O = 4 \text{ V Step}$                                              |     | 135       |      | V/µs                      |

| Full Power Response                                          | $V_0 = 2 \text{ V p-p}$                                               |     | 10        |      | MHz                       |

| Settling Time to 0.1%                                        | $V_O = 4 \text{ V Step, } C_L = 100 \text{ pF,}$<br>$R_S = 50 \Omega$ |     | 55        |      | ns                        |

| NOISE/DISTORTION PERFORMANCE                                 |                                                                       |     |           |      |                           |

| Total Harmonic Distortion                                    | $f_C = 5 \text{ MHz}, V_O = 2 \text{ V p-p},$                         |     |           |      |                           |

| Waltana Najar (DTO)                                          | $R_{L} = 1 \text{ k}\Omega$ $f = 10 \text{ kHz}$                      |     | -60<br>67 |      | dBc<br>nV/√ <del>Hz</del> |

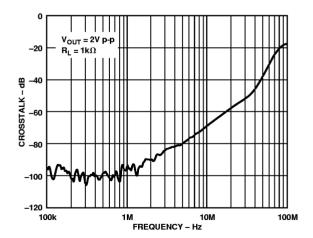

| Voltage Noise (RTO) <sup>1</sup> Crosstalk, Output to Output | f = 10  kHz<br>$f = 5 \text{ MHz}, V_O = 2 \text{ V p-p},$            |     | 07        |      | nv/vnz                    |

| Crossian, Suiput to Suiput                                   | $R_{\rm L} = 1 \text{ k}\Omega$                                       |     | -80       |      | dB                        |

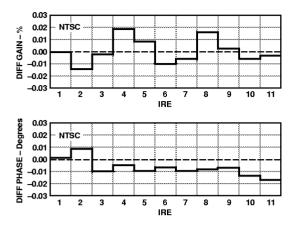

| Differential Gain Error                                      | $NTSC R_L = 1 k\Omega$                                                |     | 0.02      |      | %                         |

| Differential Phase Error                                     | NTSC $R_L = 1 \text{ k}\Omega$                                        |     | 0.02      |      | Degrees                   |

| DC PERFORMANCE                                               |                                                                       |     |           |      |                           |

| RTO Offset Voltage <sup>2</sup>                              | $V_{IN} = 0 V$                                                        |     | 0.5       | 5.5  | mV                        |

| DTO OT A DAG                                                 | $T_{ m MIN}$ to $T_{ m MAX}$                                          |     | 10        | 6    | mV                        |

| RTO Offset Drift<br>+Input Bias Current                      |                                                                       |     | 10<br>0.6 | 1.6  | μV/°C<br>μA               |

| Closed-Loop Gain Error <sup>3</sup>                          | $R_L = 10 \text{ k}\Omega, -2.67 < V_O < +2.67$                       |     | -0.02     | 0.05 | μ1<br>%                   |

| Trees Trees Trees                                            | T <sub>MIN</sub> to T <sub>MAX</sub>                                  |     |           | 0.05 | %                         |

| Gain Matching                                                | Channel-to-Channel, $R_L$ = 10 k $\Omega$                             |     |           | 0.03 | %                         |

| INPUT CHARACTERISTICS                                        |                                                                       |     |           |      |                           |

| +Input Resistance                                            |                                                                       |     | 170       |      | kΩ                        |

| +Input Capacitance                                           |                                                                       |     | 2.5       |      | pF                        |

| OUTPUT CHARACTERISTICS                                       |                                                                       |     |           |      |                           |

| Output Voltage Swing                                         | $R_L = 10 \text{ k}\Omega, V_{CC} - V_{OH}, V_{EE} + V_{OL}$          |     | 0.2       | 0.25 | V .                       |

| Short Circuit Output Current                                 |                                                                       |     | 175       |      | mA                        |

| POWER SUPPLY                                                 |                                                                       |     |           |      |                           |

| Operating Range <sup>4</sup>                                 |                                                                       |     | 2.0       | 13   | V                         |

| Quiescent Current/Amp<br>Power Supply Rejection Ratio (RTO)  | $+V_S = 5.5 \text{ V to } 6.5 \text{ V}, -V_S = -6 \text{ V}$         | 48  | 3.2<br>60 | 3.4  | mA/Amp<br>dB              |

| Tower Supply Rejection Ratio (RTO)                           | $-V_S = -5.5 \text{ V to } -6.5 \text{ V}, -V_S = -6 \text{ V}$       | 48  | 65        |      | dB                        |

| OPERATING TEMPERATURE RANGE                                  |                                                                       | 0   |           | +70  | °C                        |

#### NOTES

-2- REV. 0

<sup>&</sup>lt;sup>1</sup>Includes gain resistor thermal noise.

<sup>&</sup>lt;sup>2</sup>RTO offset includes effects of input voltage offset, input current, and input offset current.

<sup>&</sup>lt;sup>3</sup>Measured in the inverting mode.

<sup>&</sup>lt;sup>4</sup>Observe Absolute Maximum Ratings.

Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS1

Supply Voltage Var-Van

| Supply voltage ACC-AEE                             |

|----------------------------------------------------|

| Internal Power Dissipation                         |

| Small Outline Package (R)                          |

| +Input Voltage $V_{CC}$ - $V_{IN}$ + < 12 V        |

| –Input Voltage $\langle V_{EE} + 12 V \rangle$     |

|                                                    |

| Output Short Circuit Duration                      |

| Observe Power Derating Curves                      |

| Storage Temperature Range65°C to +125°C            |

| Operating Temperature Range (A Grade) 0°C to +70°C |

| Lead Temperature Range (Soldering 10 sec) +300°C   |

|                                                    |

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

NOTES

14-Lead SOIC Package:  $\theta_{JA} = 120$  °C/W, where  $P_D = (T_I - T_A)/\theta_{IA}$ .

#### **ORDERING GUIDE**

| Model          | Temperature<br>Range | Package<br>Description | Package<br>Option |

|----------------|----------------------|------------------------|-------------------|

| AD8026AR       | 0°C to +70°C         | 14-Lead Plastic SOIC   | SO-14             |

| AD8026AR-REEL  | 0°C to +70°C         | REEL SOIC              | SO-14             |

| AD8026AR-REEL7 | 0°C to +70°C         | REEL 7 SOIC            | SO-14             |

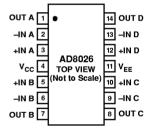

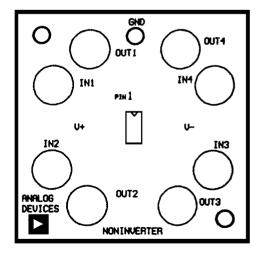

#### PIN CONFIGURATION

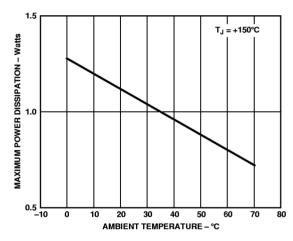

#### MAXIMUM POWER DISSIPATION

14 0 V

The maximum power that can be safely dissipated by the AD8026 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic encapsulated devices is determined by the glass transition temperature of the plastic, approximately +150°C. Exceeding this limit temporarily may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of +175°C for an extended period can result in device failure.

While the AD8026 is internally short circuit protected, this may not be sufficient to guarantee that the maximum junction temperature (+150°C) is not exceeded under all conditions. To ensure proper operation, it is necessary to observe the maximum power derating curves.

Figure 2. Maximum Power Dissipation vs. Temperature

#### CAUTION-

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8026 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0 -3-

<sup>&</sup>lt;sup>2</sup>Specification is for device in free air:

## **AD8026—Typical Performance Characteristics**

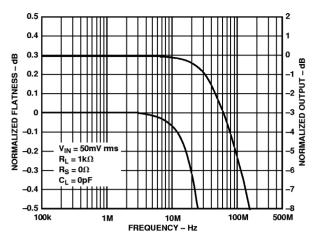

Figure 3. Small Signal Bandwidth and 0.1 dB Flatness

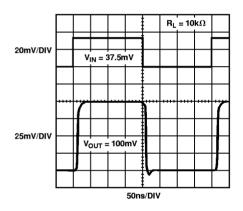

Figure 4. 100 mV Step Response

Figure 5. Short-Term Settling Time

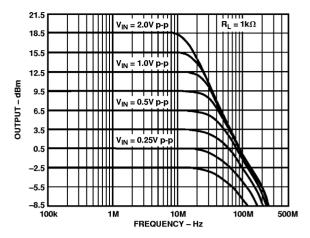

Figure 6. Large Signal Bandwidth

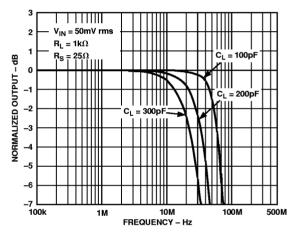

Figure 7. Cap Load vs. Frequency

Figure 8. Crosstalk (Output-to-Output) vs. Frequency

-4- REV. 0

## AD8026

Figure 9. Differential Gain and Differential Phase

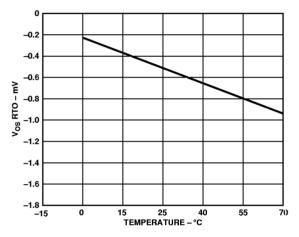

Figure 10. Vos RTO vs. Temperature

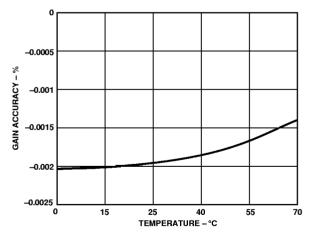

Figure 11. Gain Accuracy vs. Temperature

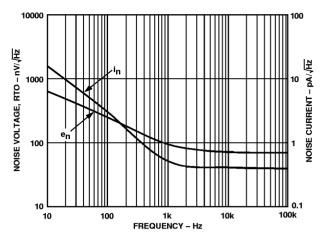

Figure 12. Noise (RTO) vs. Frequency

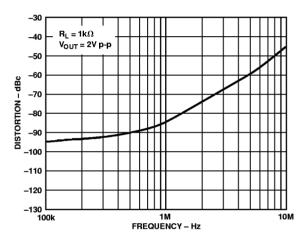

Figure 13. Total Harmonic Distortion

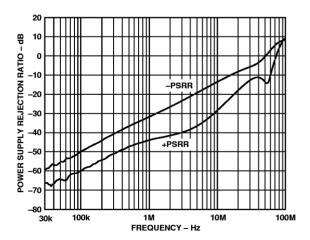

Figure 14. PSRR vs. Frequency

REV. 0 –5–

### AD8026

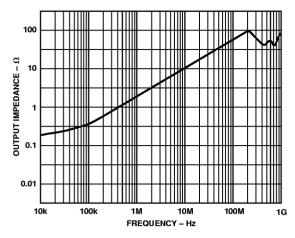

Figure 15. Output Impedance vs. Frequency

Figure 16. Input Impedance vs. Frequency

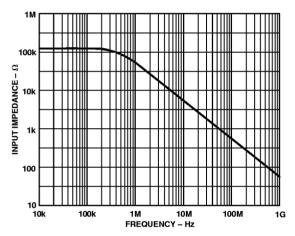

Figure 17. Bandwidth and Flatness vs. Series Resistance into 100 pF

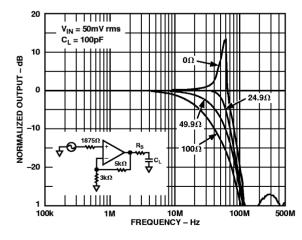

#### THEORY OF OPERATION

The AD8026, a quad voltage feedback amplifier with rail-to-rail output swing, is internally configured for a gain of either -5/3 or +8/3. The gain-setting resistors are laser trimmed for precise control of their ratio. In addition, the amplifier's frequency response has been adjusted to compensate for the parasitic capacitances associated with the gain resistors and with the amplifier's inverting input. The result is an amplifier with very tight control of closed-loop gain and settling time.

The amplifier's input stage will operate with voltages from about -0.2 V below the negative supply voltage to within about 1 V of the positive supply. Exceeding these values will not cause phase reversal at the output; however, the input ESD protection devices will begin to conduct if the input voltages exceed the supply rails by greater than 0.5 V. The gain resistors that connect to Pins 2, 6, 9, and 13 are protected from ESD in such a way that the voltages applied to these pins may exceed the negative supply by as much as -7 V.

The rail-to-rail output range of the AD8026 is provided by a complementary common-emitter output stage. The chosen circuit topology allows the outputs to source and sink 50 mA of output current and, with the use of an external series resistor, to achieve rapid settling time while driving capacitive loads within 0.5 V of the supply rails.

#### **Output Referred Offset Voltage**

The output referred offset voltage for a voltage feedback amplifier can be estimated with the following equation:

$$V_{OOS} = V_{IOS} \times \left(1 + R_F/R_G\right) + I_{OS} \times \left(R_F || R_G\right) + I_B \times \left(R_P - \left(R_F || R_G\right)\right)$$

where

$V_{OOS}$  = output referred offset voltage,

$V_{IOS}$  = input referred offset voltage,

$I_{OS}$  = difference of the two input currents,

$I_B$  = average of the two input currents,

$R_P$  = total resistance in series with positive input,

$R_F = 5 \text{ k}\Omega$ ,  $R_G = 3 \text{ k}\Omega$  for this part.

This equation leads to the well known conclusion that, for a voltage feedback amplifier to maintain minimum output offset voltage, the value of  $R_{P}$  should be selected to match the parallel combination of  $R_{F}$  and  $R_{G}.$  It should be noted that the AD8026 was designed for an assumed source impedance, of  $500\,\Omega$  driving the +Input. Therefore, the value of  $R_{P}$  included on the chip is  $500\,\Omega$  less than the ideal value for minimum output offset. Additional resistance may be added externally, in series with the +Input, if the part is to be driven by a lower impedance source.

#### **APPLICATIONS**

The AD8026 is designed with on-chip resistors for each op amp to provide accurate fixed gain and low output-referenced offset voltages. This can result in significant cost and board-space savings for systems that can take advantage of the AD8026 specifications.

The part is actually trimmed in three steps. First, the supply current of the part is trimmed. Then the gain is accurately trimmed to specification. This trim adjusts the values of either the gain or feedback resistor for a ratio of 5 to 3. The final trim is for the offset voltage. For this trim, the –Input is connected to ground and the +Input is connected to ground via  $500\,\Omega$ , while internal offset resistors are trimmed.

-6- REV. 0

In a system application, the part is designed assuming that each –Input will be driven from a low impedance source, while each +Input will be driven by a current-output DAC with a 500  $\Omega$  termination resistor. Thus, to first order, each on-chip series input resistor to each +Input is 500  $\Omega$  less than the parallel combination of the gain-setting resistors. The offset-inducing effect of the bias currents is minimized by this scheme.

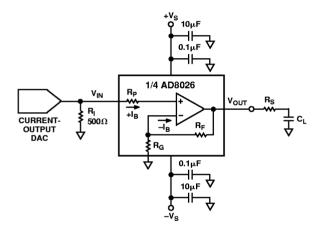

Figure 18 shows how to drive the AD8026 with a fixed positive gain of 8/3 from a current output DAC. The gain and offset errors are minimized by using a 500  $\Omega$  resistor ( $R_{\rm I}$ ) to convert the DAC output current into a voltage. The gain resistor ( $R_{\rm G}$ ) should be directly connected to ground, or driven from a low output impedance source to ensure minimum offset and maximum gain accuracy.

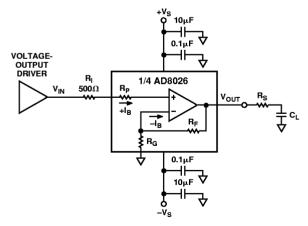

If the +Input of any of the op amps is driven from a voltage source, the low offset voltage of the AD8026 can be maintained by adding a series resistance of 500  $\Omega$  between the source and the +Input to the AD8026. This is illustrated in Figure 19. If the –Input is to be driven, such as when creating an offset voltage, then a low source impedance should be provided in order to maintain both gain and offset accuracy.

Figure 18. Low Offset and High Gain Accuracy Circuit for Driving the AD8026 from a Current Output DAC

Figure 19. Low Offset and High Gain Accuracy Circuit for Driving the AD8026 from a Voltage Source

#### QUAD AMPLIFIER CHARACTERIZATION BOARD

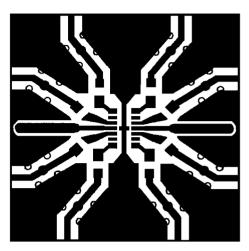

Figure 20. Component Side

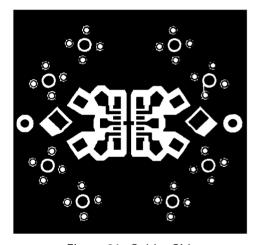

Figure 21. Solder Side

Figure 22. Silkscreen

REV. 0 -7-

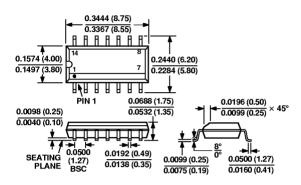

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 14-Lead SOIC (SO-14)