## PART NUMBER

### 54193BEA-ROCV

#### Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

#### Quality Overview

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

#### Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

*The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.*

# 54/74193

## 54LS/74LS193

### UP/DOWN BINARY COUNTER (With Separate Up/down Clocks)

**DESCRIPTION** — The '193 is an up/down modulo-16 binary counter. Separate Count Up and Count Down Clocks are used and in either counting mode the circuits operate synchronously. The outputs change state synchronously with the LOW-to-HIGH transitions on the clock inputs. Separate Terminal Count Up and Terminal Count Down outputs are provided which are used as the clocks for subsequent stages without extra logic, thus simplifying multistage counter designs. Individual preset inputs allow the circuits to be used as programmable counters. Both the Parallel Load (PL) and the Master Reset (MR) inputs asynchronously override the clocks. For functional description and detail specifications please refer to the '192 data sheet.

#### ORDERING CODE: See Section 9

| PKGS            | PIN OUT | COMMERCIAL GRADE                                                      | MILITARY GRADE                                                            | PKG TYPE |

|-----------------|---------|-----------------------------------------------------------------------|---------------------------------------------------------------------------|----------|

|                 |         | V <sub>CC</sub> = +5.0 V $\pm 5\%$ ,<br>T <sub>A</sub> = 0°C to +70°C | V <sub>CC</sub> = +5.0 V $\pm 10\%$ ,<br>T <sub>A</sub> = -55°C to +125°C |          |

| Plastic DIP (P) | A       | 74193PC, 74LS193PC                                                    |                                                                           | 9B       |

| Ceramic DIP (D) | A       | 74193DC, 74LS193DC                                                    | 54193DM, 54LS193DM                                                        | 6B       |

| Flatpak (F)     | A       | 74193FC, 74LS193FC                                                    | 54193FM, 54LS193FM                                                        | 4L       |

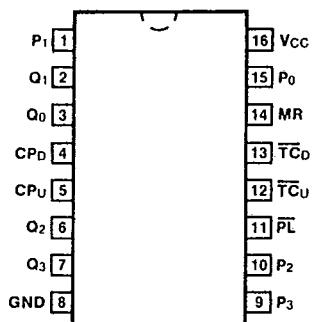

#### CONNECTION DIAGRAM PINOUT A

4

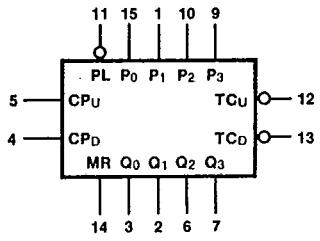

#### LOGIC SYMBOL

V<sub>CC</sub> = Pin 16

GND = Pin 8

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES | DESCRIPTION                                         | 54/74 (U.L.)<br>HIGH/LOW | 54/74LS (U.L.)<br>HIGH/LOW |

|-----------|-----------------------------------------------------|--------------------------|----------------------------|

| CPU       | Count Up Clock Input<br>(Active Rising Edge)        | 1.0/1.0                  | 0.5/0.25                   |

| CPD       | Count Down Clock Input<br>(Active Rising Edge)      | 1.0/1.0                  | 0.5/0.25                   |

| MR        | Asynchronous Master Reset Input<br>(Active HIGH)    | 1.0/1.0                  | 0.5/0.25                   |

| PL        | Asynchronous Parallel Load Input<br>(Active LOW)    | 1.0/1.0                  | 0.5/0.25                   |

| P0 — P3   | Parallel Data Inputs                                | 1.0/1.0                  | 0.5/0.25                   |

| Q0 — Q3   | Flip-flop Outputs                                   | 20/10                    | 10/5.0<br>(2.5)            |

| TCD       | Terminal Count Down (Borrow) Output<br>(Active LOW) | 20/10                    | 10/5.0<br>(2.5)            |

| TCU       | Terminal Count Up (Carry) Output<br>(Active LOW)    | 20/10                    | 10/5.0<br>(2.5)            |

193

T-45-23-09

## MODE SELECT TABLE

| MR | PL | CP <u>U</u> | CP <u>D</u> | MODE           |

|----|----|-------------|-------------|----------------|

| H  | X  | X           | X           | Reset (Asyn.)  |

| L  | L  | X           | X           | Preset (Asyn.) |

| L  | H  | H           | H           | No Change      |

| L  | H  | —           | H           | Count Up       |

| L  | H  | H           | —           | Count Down     |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

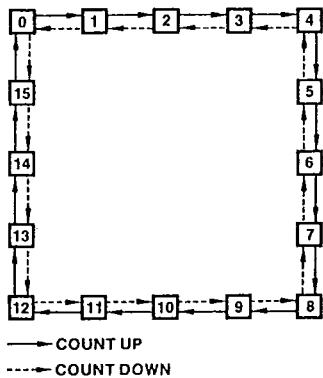

## STATE DIAGRAM

LOGIC EQUATIONS

FOR TERMINAL COUNT

$$\overline{T}_{CU} = Q_0 \cdot Q_1 \cdot Q_2 \cdot Q_3 \cdot \overline{CP_U}$$

$$\overline{T}_{CD} = \overline{Q}_0 \cdot \overline{Q}_1 \cdot \overline{Q}_2 \cdot \overline{Q}_3 \cdot \overline{CP_D}$$

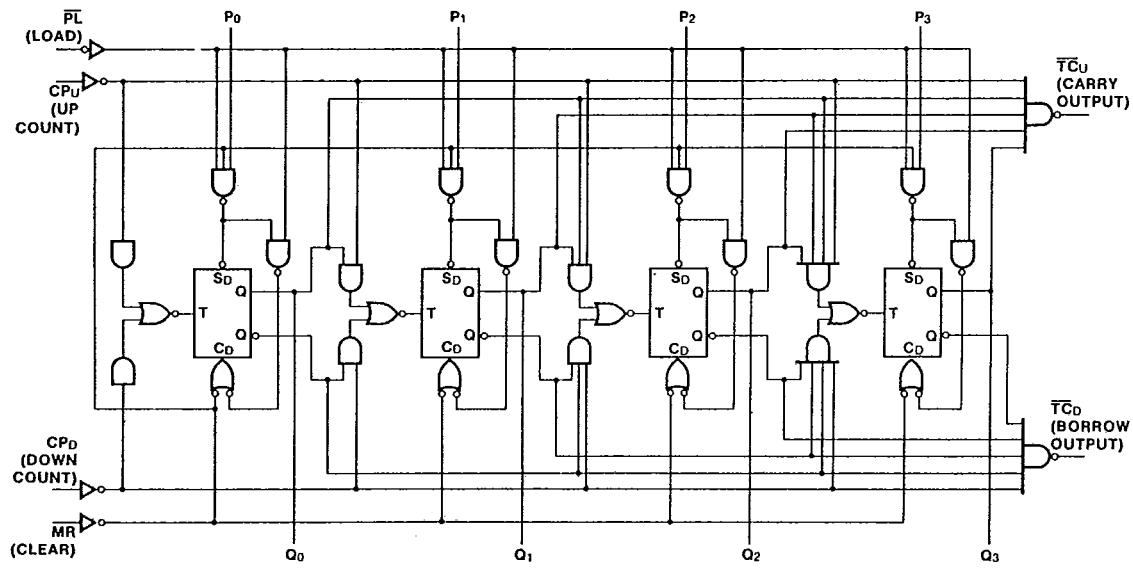

## LOGIC DIAGRAM