## PART NUMBER 54HC76JB-ROCV

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

Qualified Suppliers List of Distributors (QSLD)

Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

## 54HC76

## Dual J-K Flip-Flops with Clear and Preset

These devices contain two independent J-K negative-edge-triggered flip-flops. A low level at the Preset or Clear input sets or resets the outputs regardless of the levels of the other inputs. When Preset and Clear are inactive (high), data at the J and K inputs meeting the setup time requirements are transferred to the outputs on the negative-going edge of the clock pulse. Clock triggering occurs at a voltage level and is not directly related to the rise time of the clock pulse. Following the hold time interval, data at the J and K inputs may be changed without affecting the levels at the outputs. These versatile flip-flops can also perform as toggle flip-flops by tying J and K high.

## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer (OCM).

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- · Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

- Package Options Include Plastic "Small Outline" Packages, Standard Plastic and Ceramic 300-mil DIPs

- Dependable Texas Instruments Quality and Reliability

#### description

These devices contain two independent J-K negative-edge-triggered flip-flops. A low level at the Preset or Clear input sets or resets the outputs regardless of the levels of the other inputs. When Preset and Clear are inactive (high), data at the J and K inputs meeting the setup time requirements are transferred to the outputs on the negative-going edge of the clock pulse. Clock triggering occurs at a voltage level and is not directly related to the rise time of the clock pulse. Following the hold time interval, data at the J and K inputs may be changed without affecting the levels at the outputs. These versatile flip-flops can also perform as toggle flip-flops by tying J and K high.

#### **FUNCTION TABLE** (EACH FLIP-FLOP)

|     |     | INPUT | S |   | OUTI   | PUTS           |

|-----|-----|-------|---|---|--------|----------------|

| PRE | CLR | CLK   | J | K | Q      | ā              |

| L   | н   | Х     | Х | Х | Н      | ٦              |

| н   | Ł   | X     | Х | х | L      | н              |

| l L | L   | X     | Х | Х | H‡     | нŧ             |

| н   | н   | ı     | L | L | σo     | ₫٥             |

| H   | Н   | 1     | Н | L | Н      | Ĺ              |

| н   | Н   | 1     | L | н | L      | H              |

| н   | н   | 4     | н | н | TOGGLE |                |

| Н   | Н   | н     | X | х | αo     | ₫ <sub>0</sub> |

<sup>&</sup>lt;sup>‡</sup>This configuration is nonstable; that is, it will not persist when either Preset or Clear returns to its inactive (high) level.

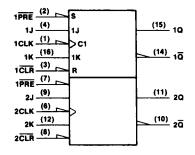

#### SN54HC76 . . . J PACKAGE SN74HC76 . . . D OR N PACKAGE (TOP VIEW)

1CLK [1] U 16] 1K 1PRE []2 15 1 1 Q 1CLR 3 14 10 1J **□**4 13 GND Vcc ☐5 12 T 2K 2CLK 6 11 20 2PRE 10 20

2CLR 8

For functionally and electrically identical parts in chip carrier packages, see SN54HC112.

9 🗍 2J

#### logic symbol†

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for D, J, and N packages.

**HCMOS Devices**

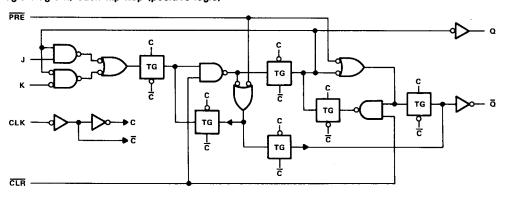

#### logic diagram, each flip-flop (positive logic)

#### absolute maximum ratings over operating free-air temperature range<sup>†</sup>

| Supply voltage, VCC                                                                            |

|------------------------------------------------------------------------------------------------|

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0 or V <sub>I</sub> > V <sub>CC</sub> ) |

| Output clamp current, IOK (VO < 0 or VO > VCC ± 20 mA                                          |

| Continuous output current, Io (Vo = 0 to Vcc)                                                  |

| Continuous current through VCC or GND pins                                                     |

| Lead temperature 1,6 mm (1/16 in) from case for 60 s: J package                                |

| Lead temperature 1,6 mm (1/16 in) from case for 10 s: D or N package                           |

| Storage temperature range65°C to 150°C                                                         |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

| •                                         | 1.                      | SN54HC76 |     |      | SN74HC76 |     |      |      |

|-------------------------------------------|-------------------------|----------|-----|------|----------|-----|------|------|

|                                           |                         | MIN      | NOM | MAX  | MIN      | NOM | MAX  | UNIT |

| V <sub>CC</sub> Supply voltage            |                         | 2        | 5   | 6    | 2        | 5   | 6    | V    |

|                                           | V <sub>CC</sub> = 2 V   | 1.5      | •   |      | 1.5      |     |      |      |

| VIH High-level input voltage              | V <sub>CC</sub> = 4.5 V | 3.15     |     |      | 3.15     |     |      | V    |

|                                           | V <sub>CC</sub> = 6 V   | 4.2      |     |      | 4.2      |     |      |      |

|                                           | V <sub>CC</sub> = 2 V   | 0        |     | 0.3  | 0        |     | 0.3  |      |

| V <sub>IL</sub> Low-level input voltage   | V <sub>CC</sub> = 4.5 V | 0        |     | 0.9  | 0        |     | 0.9  | V    |

|                                           | V <sub>CC</sub> = 6 V   | 0        |     | 1.2  | 0        |     | 1.2  |      |

| V <sub>I</sub> Input voltage              | -                       | 0        |     | Vcc  | 0        |     | Vcc  | ٧    |

| VO Output voltage                         |                         | 0        |     | Vcc  | 0        |     | Vcc  | ٧    |

|                                           | V <sub>CC</sub> = 2 V   | 0        |     | 1000 | 0        |     | 1000 |      |

| tt Input transition (rise and fall) times | V <sub>CC</sub> = 4.5 V | 0        |     | 500  | 0        |     | 500  | ns   |

|                                           | V <sub>CC</sub> = 6 V   | 0        |     | 400  | 0        |     | 400  |      |

| TA Operating free-air temperature         | •                       | - 55     |     | 125  | -40      |     | 85   | °C   |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| 24244555        | TEST COMPITIONS                                   | vcc      | TA = 25°C |       |       | SN54HC76 |        | SN74HC76 |        | UNIT |

|-----------------|---------------------------------------------------|----------|-----------|-------|-------|----------|--------|----------|--------|------|

| PARAMETER       | TEST CONDITIONS                                   |          | MIN       | TYP   | MAX   | MIN      | MAX    | MIN      | MAX    | ONT  |

|                 |                                                   | 2 V      | 1.9       | 1.998 |       | 1.9      |        | 1.9      |        |      |

| ∨он             | $V_I = V_{IH}$ or $V_{IL}$ , $I_{OH} = -20 \mu A$ | 4.5 V    | 4.4       | 4.499 |       | 4.4      |        | 4.4      |        |      |

|                 |                                                   | 6 V      | 5.9       | 5.999 |       | 5.9      |        | 5.9      |        | V    |

|                 | VI = VIH or VIL, IOH = -4 mA                      | 4.5 V    | 3.98      | 4.30  |       | 3.7      |        | 3.84     |        |      |

|                 | VI = VIH or VIL, IOH = -5.2 mA                    | 6 V      | 5.48      | 5.80  |       | 5.2      |        | 5.34     |        |      |

|                 | $V_I = V_{IH}$ or $V_{IL}$ , $I_{OL} = 20 \mu A$  | 2 V      |           | 0.002 | 0.1   |          | 0.1    |          | 0.1    |      |

|                 |                                                   | 4.5 V    |           | 0.001 | 0.1   |          | 0.1    |          | 0.1    |      |

| VOL             |                                                   | 6 V      |           | 0.001 | 0.1   |          | 0.1    |          | 0.1    | V    |

|                 | VI = VIH or VIL, IOL = 4 mA                       | 4.5 V    |           | 0.17  | 0.26  |          | 0.4    |          | 0.33   |      |

|                 | VI = VIH or VIL, IOL = 5.2 mA                     | 6 V      |           | 0.15  | 0.26  |          | 0.4    |          | 0.33   |      |

| l <sub>1</sub>  | V <sub>I</sub> = V <sub>CC</sub> or 0             | 6 V      |           | ±0.1  | ± 100 | -        | ± 1000 | -        | ± 1000 | nΑ   |

| <sup>1</sup> CC | $V_1 = V_{CC} \text{ or } 0, I_0 = 0$             | 6 V      |           |       | 4     |          | 80     |          | 40     | μΑ   |

| Ci              |                                                   | 2 to 6 V |           | 3     | 10    |          | 10     |          | 10     | рF   |

#### timing requirements over recommended operating free-air temperature range (unless otherwise noted)

|                 |                        |                        |       | T <sub>A</sub> = | 25°C | SN54HC76 |     | SN74HC76 |     | UNIT |

|-----------------|------------------------|------------------------|-------|------------------|------|----------|-----|----------|-----|------|

|                 |                        |                        | VCC   | MIN              | MAX  | MIN      | MAX | MIN      | MAX | ONL  |

|                 |                        |                        | 2 V   | 0                | 6    | 0        | 4.2 | 0        | 5   |      |

| fclock          | Clock frequency        | ncy                    |       | 0                | 31   | 0        | 21  | 0        | 25  | MHz  |

|                 |                        |                        | 6 V   | 0                | 36   | 0        | 25  | 0        | 29  |      |

| t <sub>w</sub>  |                        |                        | 2 V   | 100              |      | 150      |     | 125      |     |      |

|                 | Pulse duration         | PRE or CLR low         | 4.5 V | 20               |      | 30       |     | 25       |     | ns   |

|                 |                        |                        | 6 V   | 17               |      | 25       |     | 21       |     |      |

|                 |                        | CLK high or low        | 2 V   | 80               |      | 120      |     | 100      |     |      |

|                 |                        |                        | 4.5 V | 16               |      | 24       |     | 20       |     |      |

|                 |                        |                        | 6 V   | 14               |      | 20       |     | 17       |     |      |

|                 |                        | Data                   | 2 V   | 150              |      | 225      |     | 190      |     |      |

|                 |                        |                        | 4.5 V | 30               |      | 45       |     | 38       |     |      |

|                 | 0                      |                        | 6 V   | 25               |      | 38       |     | 32       |     |      |

| t <sub>su</sub> | Setup time before CLK1 | PRE or CLR<br>inactive | 2 V   | 100              |      | 150      |     | 125      |     | ns   |

|                 |                        |                        | 4.5 V | 20               |      | 30       |     | 25       |     |      |

|                 |                        |                        | 6 V   | 17               |      | 25       |     | 21       |     |      |

|                 |                        |                        | 2 V   | 0                |      | 0        |     | 0        |     |      |

| th              | Hold time, after CLK1  |                        | 4.5 V | 0                |      | 0        |     | 0        |     | ns   |

|                 |                        | 6 V                    | 0     |                  | 0    |          | 0   |          |     |      |

$C_{pd}$

switching characteristics over recommended operating free-air temperature range (unless otherwise noted), C<sub>L</sub> = 50 pF (see Note 1)

| PARAMETER        | FROM       | FROM TO (OUTPUT)             | V     | TA = 25°C |     |     | SN54HC76 |     | SN74HC76 |     |      |

|------------------|------------|------------------------------|-------|-----------|-----|-----|----------|-----|----------|-----|------|

| TAILAINETER      | (INPUT)    |                              | VCC   | MIN       | TYP | MAX | MIN      | MAX | MIN      | MAX | UNIT |

|                  |            |                              | 2 V   | 6         | 9   |     | 4.2      |     | 5        |     |      |

| f <sub>max</sub> |            |                              | 4.5 V | 31        | 41  |     | 21       |     | 25       |     | MHz  |

|                  |            |                              | 6 V   | 36        | 50  |     | 25       |     | 29       |     |      |

|                  | PRE or CLR | Q or $\overline{\Delta}$     | 2 V   |           | 65  | 155 |          | 250 |          | 190 |      |

| <sup>t</sup> pd  |            |                              | 4.5 V |           | 16  | 31  |          | 47  |          | 39  | ns   |

|                  |            |                              | 6 V   |           | 15  | 26  |          | 40  |          | 33  |      |

|                  | 110.0      |                              | 2 V   |           | 70  | 145 |          | 220 |          | 180 |      |

| tpd              | CLK        | Q or Q                       | 4.5 V |           | 19  | 29  |          | 44  |          | 36  | ns   |

|                  |            |                              | 6 V   | 1         | 16  | 25  |          | 37  |          | 31  |      |

| tt               |            |                              | 2 V   |           | 38  | 75  |          | 110 |          | 95  |      |

|                  |            | Q or $\overline{\mathbf{Q}}$ | 4.5 V |           | 8   | 15  |          | 22  |          | 19  | ns   |

|                  |            |                              | 6 V   |           | 6   | 13  |          | 19  |          | 16  |      |

No load,  $T_A = 25$  °C

36 pF typ

NOTE 1: Load circuit and voltage waveforms are shown in Section 1.

Power dissipation capacitance per flip-flop