# Linear Voltage Regulator, Multiple-Output, System Power Supply IC, for Automotive Infotainment System

#### Overview

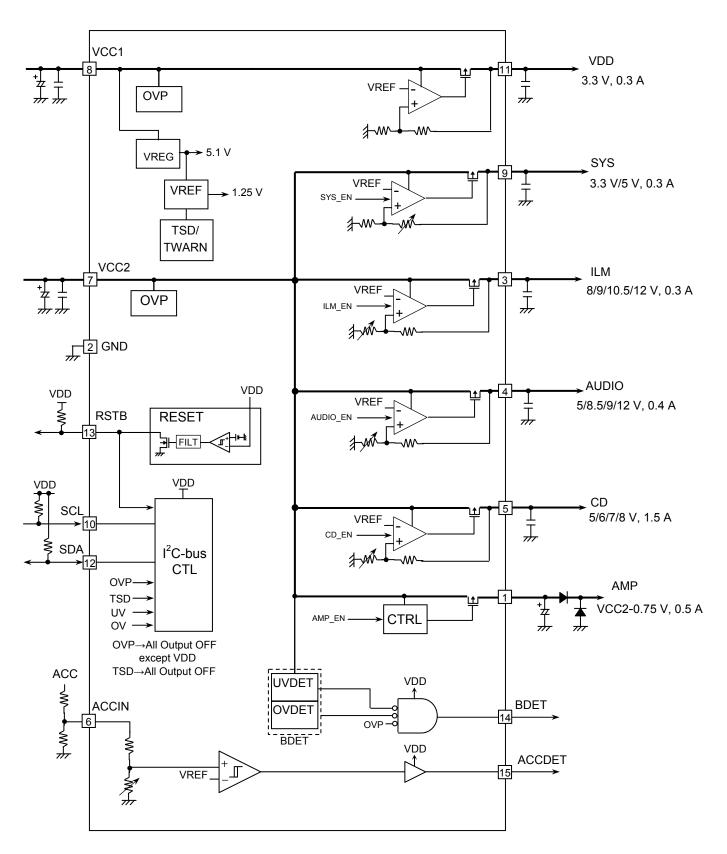

The LV56851UV is a multiple output linear voltage regulator IC, which allows reduction of quiescent current. The LV56851UV is specifically designed to address automotive infotainment systems power supply requirements.

The LV56851UV integrates 5 linear regulator outputs, 1 high side power switch, I2C-bus communication, ACC detection, battery voltage detection, over-current limiter, overvoltage protection and thermal shut down.

#### **Features**

• Low consumption current: 60µA (typ, VDD output is in operation)

• 5 regulator outputs

VDD for microcontroller: 3.3 V,Iomax: 300 mA

For system: 3.3/5 V, Iomax: 300 mA For audio: 5/8.5/9/12 V, Iomax: 400 mA For illumination: 8/9/10.5/12 V, Iomax: 300 mA

For CD: 5/6/7/8 V, Iomax: 1500 mA

• 1 high side switch

AMP: Imax: 500 mA, voltage difference between input and output: 0.75 V

• ACC detection circuit

Detection Voltage 2.7/3.2/3.6/4.2 V

Battery voltage detection (BDET): VCC2 Low voltage detection(UVDET): 6.5/7.5(hys=0.5 V or 1.5 V)/8 V

Over voltage detection(OVDET): detection voltage 18 V

• I2C-bus communication interface

Each output except VDD is independently enabled/disabled. SYS/ILM/CD/AUDIO/ACC/UV voltage setting.

Read back supported: Output voltage setting, Output over-current, Detections(ACC/UV/OVDET/OVP/TWARN)

RESET

Detection Voltage 2.8 V(typ, 0.85\*VDD), N-MOS Open-Drain output

Supply input

VCC1: For internal reference voltage, control circuitry, VDD output. VCC2: For AUDIO/ILM/CD/AMP/SYS

• Over-current protection

Overvoltage protection(OVP): VCC1,VCC2 Typ 21 V (All outputs except VDD are turned off)

• Thermal shutdown: Typ 175°C, Thermal Warning: Typ 140°C

• Package: HZIP15

AEC-Q100 (Grade 3) Qualified and PPAP capable

# **Typical Applications**

• Automotive infotainment

ON Semiconductor® www.onsemi.com

HZIP15

#### GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code Y = Year M = Month DDD = Additional Traceability Data

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " •", may or may not be present.

#### ORDERING INFORMATION

Ordering Code: LV56851UV-XH

Package HZIP15 (Pb-Free / Halogen Free)

Shipping (Qty / packing) 720 / Tube

<sup>\*</sup> I<sup>2</sup>C Bus is a trademark of Philips Corporation.

### **BLOCK DIAGRAM**

### PIN EQUIVALENT CIRCUITS

| Pin # | Pin name | Function                  | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|----------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | АМР      | AMP output<br>VCC2-0.75 V | 7 VCC2  The state of the state |

| 2     | GND      | GND                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3     | ILM      | ILM output<br>8 V~12 V    | 7 VCC2 VCC2 VCC2 W A GND GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4     | AUDIO    | AUDIO output<br>5 V~12 V  | 7 VCC2  4 VCC2  (4 (2) (2) (3) (3) (4) (4) (4) (4) (4) (4) (4) (4) (4) (4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5     | CD       | CD output<br>5 V~8 V      | 7 VCC2  (3) (3) (3) (3) (3) (3) (3) (3) (3) (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Continued on next page

Continued from preceding page

| Pin # | Pin name               | Function                         | Equivalent circuit                                                 |

|-------|------------------------|----------------------------------|--------------------------------------------------------------------|

| 6     | ACCIN                  | ACC detection input              | © 38,738,40<br>GND SND                                             |

| 7     | VCC2                   | Supply terminal                  | VCC2 VCC1  (7) (8)                                                 |

| 8     | VCC1 Supply terminal 2 |                                  | ② GND                                                              |

| 9     | SYS                    | SYS output<br>3.3 V/5 V          | 7<br>Q<br>Q<br>Q<br>Q<br>Q<br>Q<br>Q<br>Q<br>Q<br>Q<br>Q<br>Q<br>Q |

| 10    | SCL                    | I <sup>2</sup> C-bus clock input | 8 VCC1 VDD VDD (SND)                                               |

Continued on next page

Continued from preceding page

| Pin # | Pin name | Function                        | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|----------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11    | VDD      | VDD output<br>3.3 V             | (3) VCC1 (3) (4) (4) (4) (4) (4) (4) (4) (4) (4) (4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12    | SDA      | I <sup>2</sup> C-bus data input | VDD  100Ω 1kΩ  12  GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 13    | RSTB     | RESET Open-drain output         | 11 VDD  100Ω 1kΩ  3 W GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 14    | BDET     | BDET output                     | 1100Ω VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15    | ACCDET   | ACCDET output                   | (14) 15) The second of the sec |

MAXIMUM RATINGS / Ta = 25°C (Note 1)

| Parameter                     | Symbol              | Conditions                                                                                        | Ratings          | Unit |

|-------------------------------|---------------------|---------------------------------------------------------------------------------------------------|------------------|------|

| Supply voltage                | Vcc max             | VCC1,VCC2                                                                                         | 36               | V    |

| Input voltage                 | Vio max             | SDA,SCL,ACCDET,BDET,RSTB,SYS,VDD<br>ILM,AUDIO,CD<br>ACCIN, AMP                                    | 7<br>14<br>36    | V    |

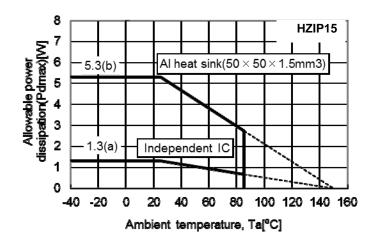

| Allowable power dissipation   | Pd max<br>Ta ≤ 25°C | -Independent IC -AI heatsink (50 * 50 * 1.5 mm <sup>3</sup> ) is used -Size of heatsink: infinite | 1.3<br>5.3<br>26 | W    |

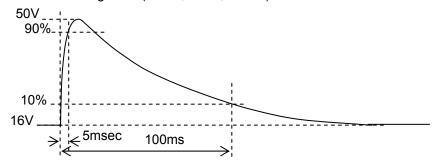

| Peak supply voltage           | Vcc peak            | VCC1/VCC2/ACCIN  • See the test waveform below                                                    | 50               | V    |

| Operating ambient temperature | Topr                |                                                                                                   | -40 to +85       | °C   |

| Storage temperature           | Tstg                |                                                                                                   | -55 to +150      | °C   |

| Junction temperature          | Tjmax               |                                                                                                   | +150             | °C   |

<sup>1.</sup> Stresses exceeding those listed in the Absolute Maximum Rating table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

Waveform of surge test (VCC1,VCC2,ACCIN)

· Allowable power dissipation derating curve

(a) Independent IC

(b)Aluminum heat-sink (50×50×1.5 mm3)

Heat-sink tightening condition

tightening torque: 39 N•cm,

with silicone grease

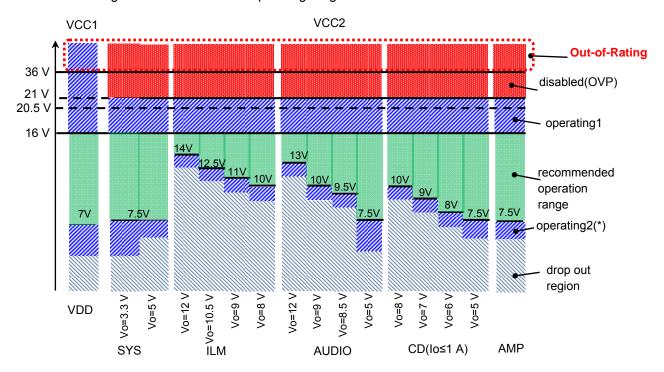

# **RECOMMENDED OPERATING RANGES** at Ta = 25°C (Note 2)

### ■VCC1

| Parameter                 | Symbol | Conditions | Ratings | Unit |

|---------------------------|--------|------------|---------|------|

| Operating supply voltage1 | VCCop1 | VDD output | 7 to 16 | V    |

#### ■VCC2

| Parameter                 | Symbol | Conditions              | Ratings    | Unit |  |

|---------------------------|--------|-------------------------|------------|------|--|

| Operating aupply voltage? | VCCon2 | ILM(10.5 V) output      | 12.5 to 16 | V    |  |

| Operating supply voltage2 | VCCop2 | ILM(8 V) output         | 10 to 16   | V    |  |

| Operating supply voltage3 | VCCop3 | AUDIO(8.5 V) output     | 9.5 to 16  | ٧    |  |

| 0                         | VCCop4 | CD(8V) output(Io=1.5 A) | 10.5 to 16 |      |  |

| Operating supply voltage4 |        | CD(8V) output(lo≤ 1 A)  | 10 to 16   | V    |  |

| Operating supply voltage5 | VCCop5 | AMP output              | 7.5 to 16  | V    |  |

| Operating supply voltage6 | VCCop6 | SYS output              | 7.5 to 16  | V    |  |

<sup>2.</sup> Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

• "Maximum Rating" and "Recommended operating range"

(\*) Each lower limit value is determined by "Output voltage"-"Dropout voltage".

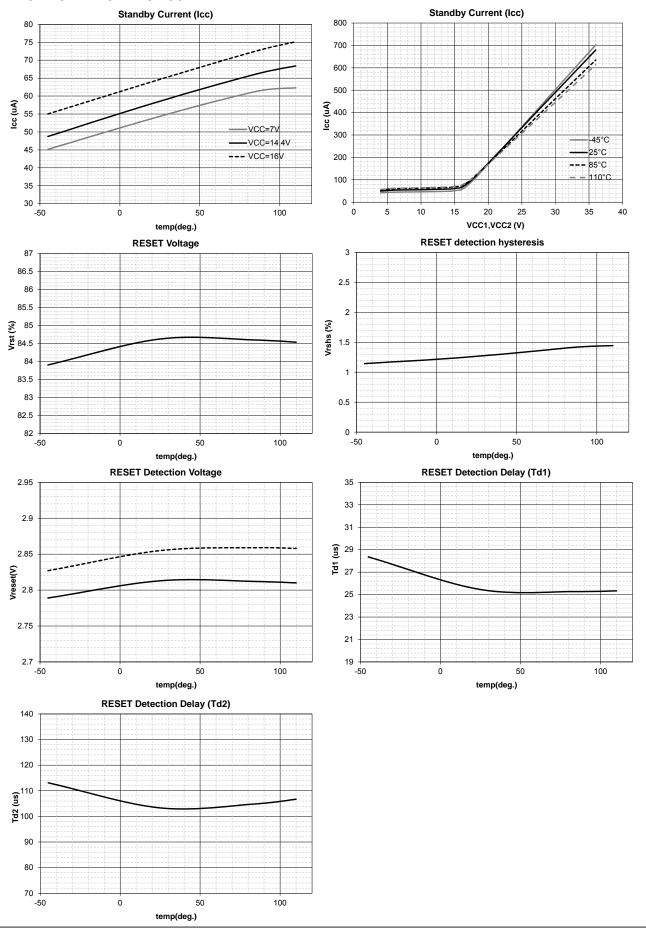

**ELECTRICAL CHARACTERISTICS** at Ta = 25°C(Note 4), VCC1=VCC2=14.4 V unless otherwise noted. (Note 3)

| Parameter                 | Symbol              | Conditions                                                                                        | Min  | Тур  | Max   | Unit     |

|---------------------------|---------------------|---------------------------------------------------------------------------------------------------|------|------|-------|----------|

| Quiescent current         | Icc                 | VDD w/out load, ACCIN=0V                                                                          |      | 60   | 100   |          |

| Quiescent current         | icc                 | I <sup>2</sup> C register Gr0/Gr1/Gr2=00h                                                         |      | 00   | 100   | μA       |

| VDD output (3.3 V)        |                     |                                                                                                   | 1    |      |       |          |

| Output voltage            | Vo1                 | lo1=200 mA                                                                                        | 3.13 | 3.3  | 3.47  | V        |

| Output current            | lo1                 | Vo1≥ 3.1 V                                                                                        | 300  |      |       | mA       |

| Line regulation           | ∆Vo <sub>LN</sub> 1 | 7.5 V <vcc1<16 io1="200" ma<="" td="" v,=""><td></td><td>30</td><td>90</td><td>mV</td></vcc1<16>  |      | 30   | 90    | mV       |

| Load regulation           | $\Delta Vo_{LD}1$   | 1 mA <lo1<200 ma<="" td=""><td></td><td>70</td><td>150</td><td>mV</td></lo1<200>                  |      | 70   | 150   | mV       |

| Dropout voltage           | V <sub>DROP</sub> 1 | lo1=200 mA                                                                                        |      | 0.5  | 1.0   | V        |

| Ripple rejection (Note 5) | R <sub>REJ</sub> 1  | f=120 Hz, VCC1=0.5 Vpp<br>lo1=200 mA                                                              | 40   | 50   |       | dB       |

| RESET                     |                     |                                                                                                   |      |      |       |          |

| Docot voltage             | Vrst0               | VDD falling                                                                                       | 2.7  | 2.8  | 2.94  | V        |

| Reset voltage             | Vrst                | As a ratio of Vo1, VDD falling                                                                    |      | 85   |       | %        |

| Hysteresis voltage        | Vrshs               | As a ratio of Vo1                                                                                 |      | 1.6  |       | %        |

| Detection Delay1          | Td1                 | H to L, VDD=Vrst+0.4 V to Vrst-0.4 V                                                              |      | 25   |       | µsec     |

| Detection Delay2          | Td2                 | L to H, VDD=Vrst-0.4 V to Vrst+0.4 V                                                              |      | 100  |       | µsec     |

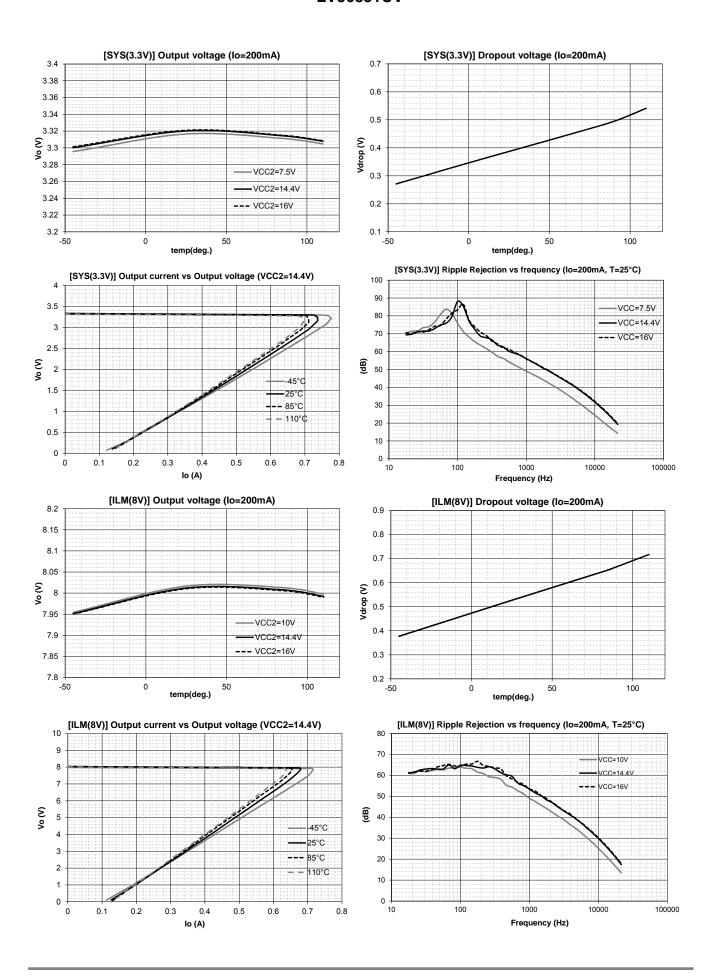

| SYS output (3.3 V/5 V);   | SYS_EN=             | 1                                                                                                 |      |      |       |          |

| Output voltage 1          | Vo21                | lo2=200 mA, SYS_V=0                                                                               | 3.13 | 3.3  | 3.47  | ٧        |

| Output voltage 2          | Vo22                | lo2=200 mA, SYS_V=1                                                                               | 4.75 | 5.0  | 5.25  | V        |

| Output current            | lo2                 | Vo21≥3.1 V, Vo22≥4.7 V                                                                            | 300  |      |       | mA       |

| Line regulation           | ΔVo <sub>LN</sub> 2 | 7.5 V <vcc2<16 lo2="200" ma<="" td="" v,=""><td></td><td>30</td><td>90</td><td>mV</td></vcc2<16>  |      | 30   | 90    | mV       |

| Load regulation           | $\Delta Vo_{LD}2$   | 1 mA <lo2<200 ma<="" td=""><td></td><td>70</td><td>150</td><td>mV</td></lo2<200>                  |      | 70   | 150   | mV       |

| Dropout voltage           | V <sub>DROP</sub> 2 | lo2=200 mA                                                                                        |      | 0.4  | 0.8   | <b>V</b> |

| Ripple rejection (Note 5) | R <sub>REJ</sub> 2  | f=120 Hz, VCC2=0.5 Vpp<br>lo2=200 mA                                                              | 40   | 50   |       | dB       |

| ILM output (8-12 V); ILM  | EN=1                |                                                                                                   |      |      |       |          |

| Output voltage 1          | Vo31                | lo3=200 mA, ILM_V[1:0]=00                                                                         | 7.6  | 8.0  | 8.4   | V        |

| Output voltage 2          | Vo32                | lo3=200 mA, ILM_V[1:0]=01                                                                         | 8.55 | 9.0  | 9.45  | V        |

| Output voltage 3          | Vo33                | Io3=200 mA, ILM_V[1:0]=10                                                                         | 9.97 | 10.5 | 11.03 | V        |

| Output voltage 4          | Vo34                | lo3=200 mA, ILM_V[1:0]=11                                                                         | 11.4 | 12   | 12.6  | V        |

| Output current            | lo3                 |                                                                                                   | 300  |      |       | mA       |

| Line regulation           | ΔVo <sub>LN</sub> 3 | Vo+2 V <vcc2<16 io3="200" ma<="" td="" v,=""><td></td><td>30</td><td>90</td><td>mV</td></vcc2<16> |      | 30   | 90    | mV       |

| Load regulation           | ΔVo <sub>LD</sub> 3 | 1 mA <lo3<200 ma<="" td=""><td></td><td>70</td><td>150</td><td>mV</td></lo3<200>                  |      | 70   | 150   | mV       |

| Dropout voltage           | V <sub>DROP</sub> 3 | Io3=200 mA                                                                                        |      | 0.6  | 1.05  | V        |

| Ripple rejection (Note 5) | R <sub>REJ</sub> 3  | f=120 Hz ,lo3=200 mA                                                                              | 40   | 50   |       | dB       |

Continued on next page.

| Continued from preceding page |                      | 1                                                                                               |          |                                                  |      | 1    |

|-------------------------------|----------------------|-------------------------------------------------------------------------------------------------|----------|--------------------------------------------------|------|------|

| Parameter                     | Symbol               | Conditions                                                                                      | Min      | Тур                                              | Max  | Unit |

| CD output (5-8 V); CD         | _EN=1                | 1                                                                                               |          | <del>                                     </del> |      | 1    |

| Output voltage 1              | Vo41                 | lo4=1000 mA, CD_V[1:0]=00                                                                       | 4.75     | 5.0                                              | 5.25 | V    |

| Output voltage 2              | Vo42                 | lo4=1000 mA, CD_V[1:0]=01                                                                       | 5.7      | 6.0                                              | 6.3  | V    |

| Output voltage 3              | Vo43                 | Io4=1000 mA, CD_V[1:0]=10                                                                       | 6.65     | 7.0                                              | 7.35 | V    |

| Output voltage 4              | Vo44                 | Io4=1000 mA, CD_V[1:0]=11                                                                       | 7.6      | 8.0                                              | 8.4  | V    |

| Output current                | lo4                  | Vo41≥4.7 V, V44≥7.6 V                                                                           | 1500     |                                                  |      | mA   |

| Line regulation               | $\Delta Vo_{LN}4$    | Vo+2 V <vcc2<16 ma<="" td="" v,io4="1000"><td></td><td>50</td><td>100</td><td>mV</td></vcc2<16> |          | 50                                               | 100  | mV   |

| Load regulation               | $\Delta Vo_{LD}4$    | 10 mA <lo4<1000 ma<="" td=""><td></td><td>100</td><td>200</td><td>mV</td></lo4<1000>            |          | 100                                              | 200  | mV   |

| Dropout voltage 1             | V <sub>DROP</sub> 4  | Io4=1000 mA                                                                                     |          | 0.9                                              | 1.5  | V    |

| Dropout voltage 2             | V <sub>DROP</sub> 4' | Io4=500 mA                                                                                      |          | 0.45                                             | 0.75 | V    |

| Ripple rejection (Note 5)     | R <sub>REJ</sub> 4   | f=120 Hz ,lo4=1000 mA                                                                           | 40       | 50                                               |      | dB   |

| AUDIO output (5-12 V)         | ); AUDIO_I           | EN=1                                                                                            |          |                                                  |      |      |

| Output voltage 1              | Vo51                 | lo5=200 mA, AUD_V[1:0]=00                                                                       | 4.75     | 5.0                                              | 5.25 | V    |

| Output voltage 2              | Vo52                 | lo5=200 mA, AUD_V[1:0]=01                                                                       | 8.13     | 8.5                                              | 8.87 | V    |

| Output voltage 3              | Vo53                 | lo5=200 mA, AUD_V[1:0]=10                                                                       | 8.55     | 9.0                                              | 9.45 | V    |

| Output voltage 4              | Vo54                 | Io5=200 mA, AUD_V[1:0]=11                                                                       | 11.4     | 12                                               | 12.6 | V    |

| Output current                | lo5                  |                                                                                                 | 400      |                                                  |      | mA   |

| Line regulation               | $\Delta Vo_{LN}5$    | Vo+1 V <vcc2<16 ma<="" td="" v,io5="200"><td></td><td>30</td><td>90</td><td>mV</td></vcc2<16>   |          | 30                                               | 90   | mV   |

| Load regulation               | $\Delta Vo_{LD}5$    | 1 mA <lo5<200 ma<="" td=""><td></td><td>70</td><td>150</td><td>mV</td></lo5<200>                |          | 70                                               | 150  | mV   |

| Dropout voltage               | V <sub>DROP</sub> 5  | Io5=200 mA                                                                                      |          | 0.25                                             | 0.45 | V    |

| Ripple rejection              | R <sub>REJ</sub> 5   | f=120 Hz, Io5=200 mA                                                                            | 40       | 50                                               |      | dB   |

| (Note 5)                      | IXKEJO               | 1-120112, 103-200111A                                                                           | 40       | 30                                               |      | ub   |

| AMP HS-SW; AMP_EN             | l=1                  |                                                                                                 |          | 1 1                                              |      | T    |

| Output voltage                | Vo6                  | Io6=500 mA                                                                                      | Vcc2-1.5 | Vcc2-0.75                                        |      | V    |

| Output current                | lo6                  | Vo6≥VCC2-1.5 V                                                                                  | 500      |                                                  |      | mA   |

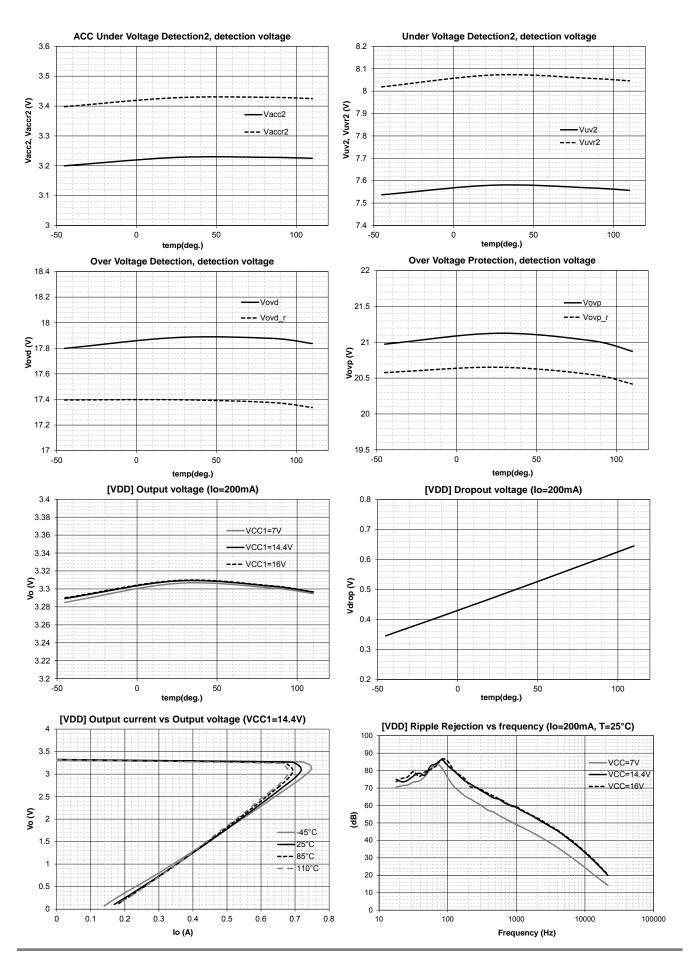

| ACC detection                 | T                    |                                                                                                 |          | <del> </del>                                     |      | 1    |

| Detection voltage 1           | Vacc1                | ACC_V[1:0]=00, ACCIN falling                                                                    | 2.62     | 2.7                                              | 2.78 | V    |

| Detection voltage 2           | Vacc2                | ACC_V[1:0]=01, ACCIN falling                                                                    | 3.1      | 3.2                                              | 3.3  | V    |

| Detection voltage 3           | Vacc3                | ACC_V[1:0]=10, ACCIN falling                                                                    | 3.49     | 3.6                                              | 3.71 | V    |

| Detection voltage 4           | Vacc4                | ACC_V[1:0]=11, ACCIN falling                                                                    | 4.07     | 4.2                                              | 4.33 | V    |

| Release voltage 1             | Vaccr1               | ACC_V[1:0]=00, ACCIN rising                                                                     | 2.81     | 2.9                                              | 2.99 | V    |

| Release voltage 2             | Vaccr2               | ACC_V[1:0]=01, ACCIN rising                                                                     | 3.3      | 3.4                                              | 3.5  | V    |

| Release voltage 3             | Vaccr3               | ACC_V[1:0]=10, ACCIN rising                                                                     | 3.68     | 3.8                                              | 3.92 | V    |

| Release voltage 4             | Vaccr4               | ACC_V[1:0]=11, ACCIN rising                                                                     | 4.26     | 4.4                                              | 4.54 | V    |

| Threshold hysteresis          | Vachs                |                                                                                                 |          | 0.2                                              |      | V    |

Continued on next page.

Continued from preceding page

| Continued from preceding page     |          |                                   |          |          |         |      |

|-----------------------------------|----------|-----------------------------------|----------|----------|---------|------|

| Parameter                         | Symbol   | Conditions                        | Min      | Тур      | Max     | Unit |

| Under-Voltage detection           | n(UVDET) |                                   | <u> </u> | <u> </u> |         |      |

| detection voltage 1               | Vuv1     | VCC2 falling, UVD_V[1:0]=00       | 6.3      | 6.5      | 6.7     | V    |

| detection voltage 2               | Vuv2     | VCC2 falling, UVD_V[1:0]=01       | 7.27     | 7.5      | 7.73    | V    |

| detection voltage 3               | Vuv3     | VCC2 falling, UVD_V[1:0]=10       | 7.27     | 7.5      | 7.73    | V    |

| detection voltage 4               | Vuv4     | VCC2 falling, UVD_V[1:0]=11       | 7.76     | 8.0      | 8.24    | V    |

| release voltage 1                 | Vuvr1    | VCC2 rising, UVD_V[1:0]=00        | 6.79     | 7.0      | 7.21    | V    |

| release voltage 2                 | Vuvr2    | VCC2 rising, UVD_V[1:0]=01        | 7.76     | 8.0      | 8.24    | V    |

| release voltage 3                 | Vuvr3    | VCC2 rising, UVD_V[1:0]=10        | 8.73     | 9.0      | 9.27    | V    |

| release voltage 4                 | Vuvr4    | VCC2 rising, UVD_V[1:0]=11        | 8.24     | 8.5      | 8.76    | V    |

| detection hysteresis 1            | Vuvhs1   | UVD_V[1:0]=00                     |          | 0.5      |         | V    |

| detection hysteresis 2            | Vuvhs2   | UVD_V[1:0]=01                     |          | 0.5      |         | V    |

| detection hysteresis 3            | Vuvhs3   | UVD_V[1:0]=10                     |          | 1.5      |         | V    |

| detection hysteresis 4            | Vuvhs4   | UVD_V[1:0]=11                     |          | 0.5      |         | V    |

| Over-Voltage detection            | (OVDET)  |                                   | 1        | 1        | 1       |      |

| detection voltage                 | Vovd     | VCC2 rising                       | 17       | 18       | 19      | V    |

| detection hysteresis              | Vodhys   |                                   |          | 0.5      |         | V    |

| Over-Voltage protectio            | n(OVP)   |                                   |          | _        |         |      |

| detection voltage                 | Vovp     | VCC1/VCC2 rising, output disabled |          | 21       |         | V    |

| detection hysteresis              | Vovhys   |                                   |          | 0.5      |         | V    |

| CMOS Output(ACCDE                 | r, BDET) |                                   |          |          |         |      |

| "H" voltage                       | VflgH    | Isource=1 mA                      |          | VDD-0.3  | VDD     | V    |

| "L" voltage                       | VflgL    | Isink=1 mA                        |          | 0.3      | 0.4     | V    |

| RSTB:                             | _        |                                   |          | _        |         |      |

| Input "L" voltage                 | Vilrs    | Internal circuit reset            | 0        |          | 0.4     | V    |

| Input "H" voltage                 | Vihrs    | Internal circuit reset released   | 2.8      | VDD      | VDD+0.3 | V    |

| "L" voltage                       | VrsbL    | Isink=1 mA                        |          | 0.3      | 0.4     | V    |

| I <sup>2</sup> C-bus I/F; SCL,SDA |          |                                   |          |          |         |      |

| Input "L" voltage                 | Vils     |                                   | 0        |          | 0.4     | V    |

| Input "H" voltage                 | Vihs     |                                   | 2.8      | VDD      | VDD+0.3 | V    |

| SDA "L" voltage                   | Vols     | Isink=1 mA, ACK or data read      |          | 0.3      | 0.4     | V    |

<sup>3.</sup> Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

4. All the specification is defined based on the tests performed under the conditions where Tj and Ta(=25°C) are almost equal. These tests were performed with pulse load to minimize the increase of junction temperature (Tj).

5. Guaranteed by design

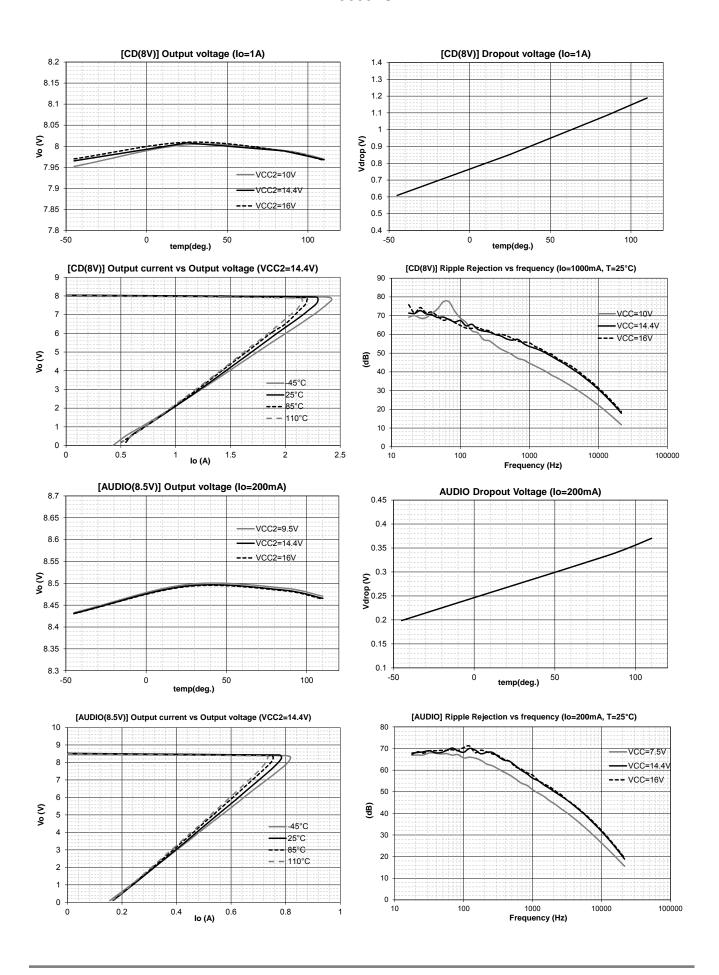

# **TYPICAL CHARACTERISTICS**

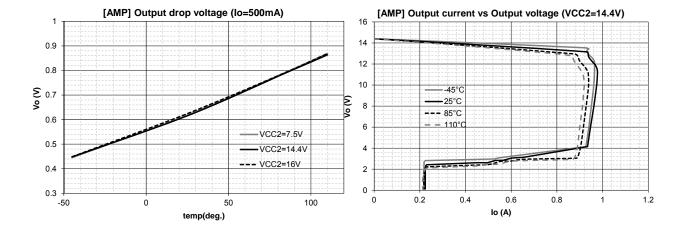

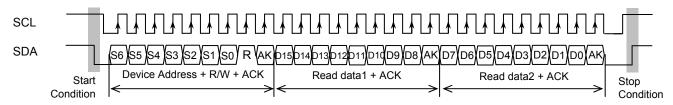

I<sup>2</sup>C-bus Interface timing

| <u> </u>                         |         |     |     |     |      |

|----------------------------------|---------|-----|-----|-----|------|

| Parameter                        | Symbol  | min | typ | max | unit |

| SCL clock frequency              | fSCL    | 0   |     | 400 | kHz  |

| START condition hold time        | tHD;STA | 0.6 |     |     | us   |

| SCL "L" pulse-width              | tLOW    | 1.3 |     |     | us   |

| SCL "H" pulse-width              | tHIGH   | 0.6 |     |     | us   |

| DATA hold time                   | tHD;DAT | 0   |     |     | us   |

| DATA setup time                  | tSU;DAT | 0.1 |     |     | us   |

| SDA/SCL rise time                | tr      |     |     | 0.3 | us   |

| SDA/SCL fall time                | tf      |     |     | 0.3 | us   |

| STOP condition setup time        | tSU;STO | 0.6 |     |     | us   |

| Bus free time                    | tBUF    | 1.3 |     |     | us   |

| between STOP and START condition |         |     |     |     |      |

| Bus line load capacitance        | Cb      |     |     | 400 | pF   |

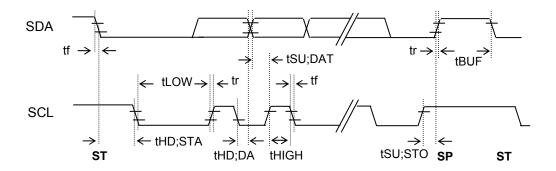

# I<sup>2</sup>C-bus interface format (MSB first)

This part is I<sup>2</sup>C controlled power supply, using 2 wires of SCL,SDA.

The communication protocol comprises start-condition, device-address, sub-address, data and stop-condition.

Every 8 bits are followed by ACK bit, and the receiver device pulls down SDA line during ACK period.

D14

D15

D13

This part doesn't accept sub-address auto increment format. (Single data byte write per a communication.) The protocol in Read-mode comprises start-condition, device-address, data1, data2 and stop-condition.

(Note)The I<sup>2</sup>C-bus communication may be unstable when VDD voltage is not stable or out of specification range, since I<sup>2</sup>C-BUS circuitry is supplied by VDD.

### Write mode

#### Read mode

#### · Device address

|   | S6 | S5 | S4 | S3 | S2 | S1 | S0 | R/W |

|---|----|----|----|----|----|----|----|-----|

| ĺ | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1/0 |

### Register map

#### Write

|      | D7     | D6     | D5       | D4     | D3     | D2     | D1     | D0   | init     |

|------|--------|--------|----------|--------|--------|--------|--------|------|----------|

| PM   | ILM_EN | CD_EN  | AUDIO_EN | SYS_EN | AMP_EN | 0      | 0      | 0    | 00000000 |

| VCTL | ILM_V1 | ILM_V0 | CD_V1    | CD_V0  | AUD_V1 | AUD_V0 | SYS_V  | 0    | 00000000 |

| DET  | ACC_V1 | ACC_V0 | UVD_V1   | UVD_V0 | BDETMD | 0      | (Reser | ved) | 00000000 |

# Read

| VCTL | ILM_V1 | ILM_V0 | CD_V1 | CD_V0 | AUD_V1 | AUD_V0 | SYS_V | 0  | 00000000 |

|------|--------|--------|-------|-------|--------|--------|-------|----|----------|

|      |        |        |       |       |        |        |       |    |          |

|      | D7     | D6     | D5    | D4    | D3     | D2     | D1    | D0 | init     |

| FLG  | ACCUV  | UV     | OV    | OVP   | TWARN  | ОС     | 0     | 0  | 00000000 |

|      |        |        |       |       |        |        |       |    |          |

D11

D10

D9

D8

init

D12

# Write Register explanation

| ADR | bit | Name     | init | Description                      |

|-----|-----|----------|------|----------------------------------|

| 00h | 7   | ILM_EN   | 0    | ILM output enable 1: ON 0: OFF   |

|     | 6   | CD_EN    | 0    | CD output enable 1: ON 0: OFF    |

|     | 5   | AUDIO_EN | 0    | AUDIO output enable 1: ON 0: OFF |

|     | 4   | SYS_EN   | 0    | SYS output enable 1: ON 0: OFF   |

|     | 3   | AMP_EN   | 0    | AMP output enable 1: ON 0: OFF   |

|     | 2   |          | 0    |                                  |

|     | 1   |          | 0    |                                  |

|     | 0   |          | 0    |                                  |

| ADR | bit   | Name       | init | Description                                                |

|-----|-------|------------|------|------------------------------------------------------------|

| 01h | [7:6] | ILM_V[1:0] | 00   | ILM output voltage(*) 11: 12 V 10: 10.5 V 01: 9 V 00: 8 V  |

|     | [5:4] | CD_V[1:0]  | 00   | CD output voltage(*) 11: 8 V 10: 7 V 01: 6 V 00: 5 V       |

|     | [3:2] | AUD_V[1:0] | 00   | AUDIO output voltage(*) 11: 12 V 10: 9 V 01: 8.5 V 00: 5 V |

|     | 1     | SYS_V      | 0    | SYS output voltage(*) 1: 5 V 0: 3.3 V                      |

|     | 0     |            | 0    |                                                            |

<sup>(\*) &</sup>quot;Output voltage setting" is only valid when corresponding output is set disabled(xxx\_EN=0). It is ignored when the output is set enabled(xxx\_EN=1).

| ADR | bit   | Name       | init | Description                                                   |

|-----|-------|------------|------|---------------------------------------------------------------|

| 02h | [7:6] | ACC_V[1:0] | 00   | ACC detection voltage 11: 4.2 V 10: 3.6 V 01: 3.2 V 00: 2.7 V |

|     | [5:4] | UVD_V[1:0] | 00   | UVDET detection voltage                                       |

|     |       |            |      | 11: 8 V 10: 7.5 V(9 V) 01: 7.5 V(8 V) 00: 6.5 V               |

|     | 3     | BDETMD     | 0    | BDET output mode 1: BDET/TWARN 0: BDET only                   |

|     | 2     |            | 0    |                                                               |

|     | [1:0] | (Reserved) | 00   | (For TEST) Must be set to "00" for normal use.                |

# Read Register explanation

| ADR | bit     | Name       | init | Description                                                  |

|-----|---------|------------|------|--------------------------------------------------------------|

|     | [15:14] | ILM_V[1:0] | 00   | ILM output voltage 11: 12 V 10: 10.5 V 01: 9 V 00: 8 V       |

|     | [13:12] | CD_V[1:0]  | 00   | CD output voltage 11: 8 V 10: 7 V 01: 6 V 00: 5 V            |

|     | [11:10] | AUD_V[1:0] | 00   | AUDIO output voltage 11: 12 V 10: 9 V 01: 8.5 V 00: 5 V      |

|     | 9       | SYS_V      | 0    | SYS output voltage 1: 5 V 0: 3.3 V                           |

|     | 8       |            | 0    |                                                              |

|     | 7       | ACCUV      | 0    | ACC detection 1: Under voltage 0: Nornmal                    |

|     | 6       | UV         | 0    | Under voltage detection 1: Under voltage 0: Normal           |

|     | 5       | OV         | 0    | Over voltage detection 1: Over Voltage 0: Normal             |

|     | 4       | OVP        | 0    | Over voltage protection 1: Over Voltage Protection 0: Normal |

|     | 3       | TWARN      | 0    | Thermal Warning 1: High temperature 0: Normal                |

|     | 2       | ОС         | 0    | Output Over Current 1: Over current 0: Normal                |

|     | 1       |            | 0    |                                                              |

|     | 0       |            | 0    |                                                              |

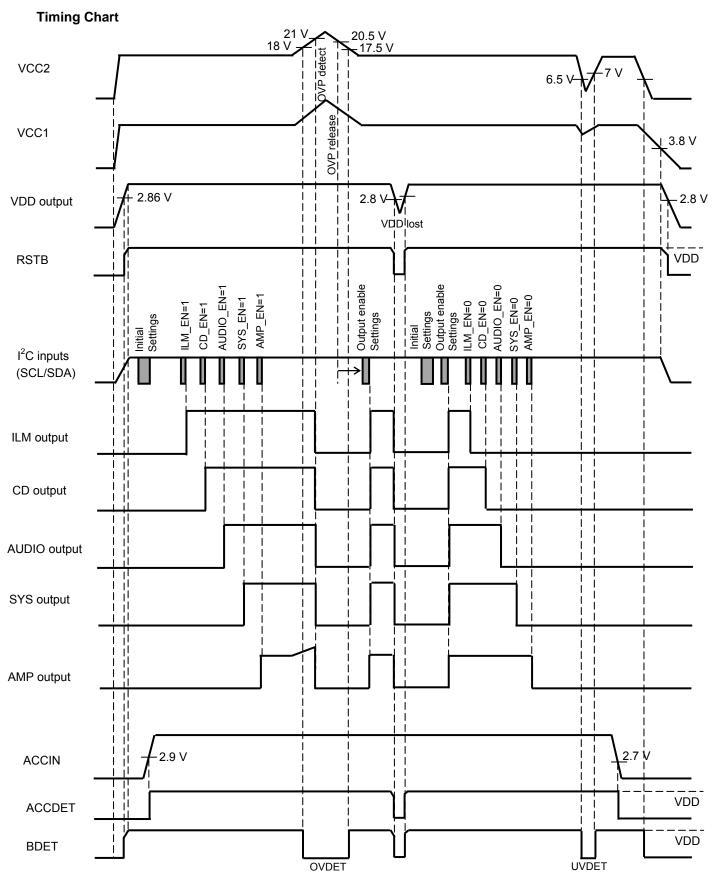

#### **FUNCTIONAL DESCRIPTION**

#### [Standby mode]

When VCC1 is applied, internal control circuitry is automatically reset and goes into Stand-by mode.

In Stand-by mode, following functions are active.

VDD(3.3 V) output

I<sup>2</sup>C-bus communication

Over voltage

protection(OVP)/UVDET/OVDET/ACC

detection/BDET output

Thermal shutdown(TSD)

### [VCC1/VCC2]

VCC1 input is necessary for any operation of this device since VCC1 supplies VDD and common circuitry such as reference voltage, internal control circuitry.

VCC2 is the supply for AUDIO/ILM/CD/AMP/SYS outputs.

LV56851UV can tolerate up to 50 V peak surge voltage on VCC1/2 or ACCIN, but for more safety design, adding power clamp such as power zener diode on battery connected line is recommended in order to absorb applied surge.

LV56851UV has no protection against battery reverse connection. If a negative voltage input is possible, adding Schottky diode between VCC and GND is recommended to protect the device from the negative voltage.

#### [Controls]

The functions of LV56851UV can be controlled via  $I^2C$ -bus. See "I2C bus interface format" term for details.

# [Linear Regulators]

### VDD output

When VCC1 is applied, VDD output is active regardless of control states.

### SYS/CD/AUDIO/ILM output

These outputs are individually enabled or disabled via I<sup>2</sup>C-bus.

The voltage of each output can be selected via I<sup>2</sup>C-bus. These commands must be set prior to enabling corresponding output. If you intend to change the voltage setting for these outputs, be sure to do it after the output is set disabled. In order to avoid unintended output voltage change, each "output voltage setting" is valid only when corresponding output is set disabled(xxx\_EN=0). The "output voltage setting" is ignored when the output is set enabled(xxx\_EN=1).

Output voltage setting can be referred by reading via I<sup>2</sup>C-bus(VCTL register). It is strongly recommended to read and check VCTL register value just before setting enable the output in order to avoid unintended output voltage change even in case if communication error were to happen and incorrect voltage setting were written to the device.

Each regulator output limits output current if the output gets over-loaded condition. The limit current decreases as the output voltage gets lower, in order to reduce the stress applied to the device.

All regulators in LV56851UV are low dropout outputs, because the output stage of all regulators is P-channel LDMOS.

When you select output capacitors for linear regulators, you should consider three main characteristics: startup delay, transient response and loop stability. The capacitor values and type should be based on cost, availability, size and temperature constraints. Tantalum, Aluminum electrolytic, Film, or Ceramic capacitors are all acceptable solutions. However, attention must be paid to ESR constraints. The aluminum electrolytic capacitor is the least expensive solution, but if the circuit operates at low temperatures (-25 to -40°C), both the value and ESR of the capacitor will vary considerably. The capacitor manufacturer's datasheet usually provides this information.

#### [High-side switch]

AMP is a high-side power switch connected to VCC2. The output is enabled or disabled via I<sup>2</sup>C-bus.

The high-side switch limits output current if the output gets over-loaded condition. The limit current becomes lower value, if the output voltage gets lower than 2.5

V(typ) in order to reduce the stress applied to the device.

If the output is connected to inductive load or loads which have different ground potential, protection diodes (D1,D2) are necessary to protect the device from negative voltage.

# [Current Limiting]

When the each output becomes in over loaded condition, the device limits the output current.

All outputs are also protected against short circuit to GND by fold back current limiter.

If one of each output except VDD is in over-current condition, OC bit of FLG register is set 1, which can be read via I<sup>2</sup>C-bus.

### [Detections]

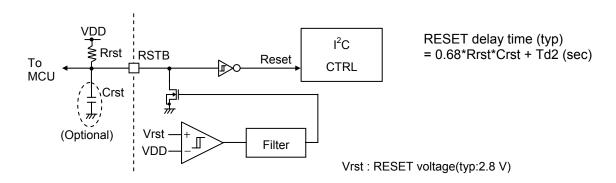

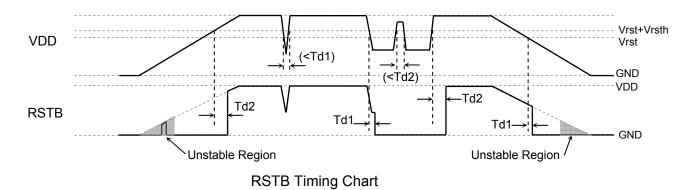

#### RESET circuit

When the VDD voltage drops below the reset threshold (typ:2.8 V, 85% of Vo1:3.3 V) for more than Detection delay period(Td1), RSTB is pulled low. During RSTB=Low, internal control circuitry is reset and all the registers of I<sup>2</sup>C-bus are initialized.

When the VDD voltage rises higher than the threshold (typ:2.86 V, 86.6% of Vo1:3.3 V), RSTB becomes open state and reaches high level by external resistor Rrst, internal reset is released after the delay period(Td2).

Add an optional capacitor between RSTB to GND in order to obtain longer reset time (>Td2). The approximate delay time can be calculated by the expression below.

RESET circuit block diagram

### Under voltage detection (UVDET)

If the VCC2 voltage gets lower than set value (UVD\_V[1:0]), Under-Voltage is detected and the UV bit of FLG register is set 1, which can be read via I<sup>2</sup>C-bus. BDET pin keeps "Low" during UVDET condition. Each output status keeps the same condition even if UV is detected.

### Over voltage detection (OVDET)

If the VCC2 voltage exceeds 18V(typ), Over-Voltage is detected and the OV bit of FLG register is set 1, which can be read via I<sup>2</sup>C-bus. BDET pin keeps "Low" during OVDET condition. Each output status keeps the same condition even if OV is detected.

### ACC Under voltage detection

If the ACCIN voltage gets lower than set value (ACC\_V[1:0]), the ACCUV bit of FLG register is set 1, which can be read via I<sup>2</sup>C-bus. ACCDET pin keeps "Low" during ACCUV is detected.

Each output status keeps the same condition even if ACCUV is detected.

# Over voltage protection (OVP)

If the voltage of VCC1 or VCC2 exceeds 21 V(typ), OVP is detected and the OVP bit of FLG register is set 1, which can be read via I<sup>2</sup>C-bus. And all the outputs except VDD are automatically turned off. When the voltage of VCC1 and VCC2 get lower than 20.5 V(typ), OVP detection is released. But output voltages are not automatically restored, because once OVP is detected, PM register of I<sup>2</sup>C-bus is reset.

BDET pin keeps "Low" during OVP condition.

#### Thermal Shutdown

To protect the device from overheating, a thermal shutdown circuitry is included. If the junction temperature exceeds approximately 175°C(typ), all outputs are turned off regardless of control state. After the junction temperature drops below 145°C(typ), VDD output is automatically restored and I<sup>2</sup>C-bus control becomes available.

The thermal shutdown circuit does not guarantee the protection of the final product because it operates out of maximum rating (exceeding Tjmax=150°C).

#### Thermal Warning

To inform over-temperature of the die, when the junction temperature exceeds approximately 140°C(typ), the TWARN bit of FLG register is set 1, which can be read via I<sup>2</sup>C-bus. After the junction temperature drops below 130°C(typ), TWARN is released and TWARN bit is reset.

Each output status keeps the same condition even if TWARN is detected.

If you set BDETMD bit=1 of DET register, BDET pin becomes "Low" when TWARN is detected.

#### **BDET** output

BDET output depends on BDETMD bit setting of DET register as shown on the table below.

When each of the listed condition is satisfied, BDET is pulled "Low".

| Conditions for | or BDET=Low              | BDETM       | D        |

|----------------|--------------------------|-------------|----------|

|                | Conditions               | 0 (default) | 1        |

| UV             | VCC2 < UVDET Threshold   | ✓           | <b>✓</b> |

| OV             | VCC2 > OVDET Threshold   | <b>√</b>    | <b>√</b> |

| TWARN          | $Ti > 140^{\circ}C(tvp)$ | ignored     | ✓        |

Note: The above values are obtained when typ. All the voltage setting are default values

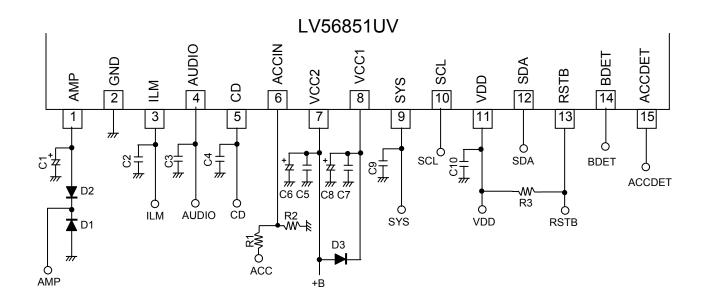

# **APPLICATION CIRCUIT EXAMPLE**

# Peripheral parts

| Part name       | Description                            | Recommended value       | Note               |

|-----------------|----------------------------------------|-------------------------|--------------------|

| C1              | Capacitor for AMP output stabilization | greater than 2.2 μF     |                    |

| C2,C3,C4,C9,C10 | output stabilization capacitor         | greater than10 μF(*)    |                    |

| C6,C8           | Power supply bypass capacitor          | C6: greater than 100 μF | Make sure to       |

|                 |                                        | C8: greater than 47 μF  | implement close to |

| C5,C7           | Capacitor for oscillation protector    | greater than 0.22 μF    | VCC and GND.       |

| D1,D2           | Internal device protection diode       | ON Semiconductor        |                    |

|                 |                                        | SB1003M3                |                    |

| D3              | Reverse current protection diode       | ON Semiconductor        |                    |

|                 |                                        | SB1003M3                |                    |

| R1,R2           | ACC divider resistors                  |                         | R1>R2              |

| R3              | Pull-up resistor                       | 100 kΩ                  |                    |

<sup>(\*)</sup> Make sure that output capacitors are greater than 10  $\mu$ F and meets the condition of ESR=0.001 to 10  $\Omega$ , in which voltage/temperature dependence and their tolerances are taken into consideration. Moreover, in case of electrolytic capacitor, high-frequency characteristics should be sufficiently good.

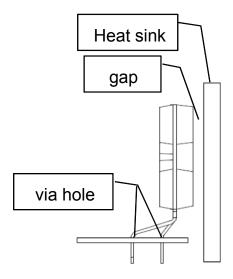

#### **HZIP15 Heat sink attachment**

Heat sinks are used to lower the semiconductor device junction temperature by leading the head generated by the device to the outer environment and dissipating the heat.

- a. Unless otherwise specified, for power ICs with tabs and power ICs with attached heat sinks, solder must not be applied to the heat sink or tabs.

- b. Heat sink attachment

Binding-head machine-screw

Countersunk head machine screw

- Use flat-head screws to attach heat sinks.

- Use also washer to protect the package.

- Use tightening torques in the ranges 39-59 Ncm(4-6 kgcm).

- If tapping screws are used, do not use screws with a diameter larger than the holes in the semiconductor device itself.

- Do not make gap, dust, or other contaminants to get between the semiconductor device and the tab or heat sink.

- Take care to the position of via hole.

- Do not allow dirt, dust, or other contaminants to get between the semiconductor device and the tab or heat sink.

- Verify that there are no press burrs or screw-hole burrs on the heat sink.

- Warping in heat sinks and printed circuit boards must be no more than 0.05 mm between screw holes, for either concave or convex warping.

- Twisting must be limited to under 0.05 mm.

- Heat sink and semiconductor device should be mounted in parallel.

Take care of electric or compressed air screw driver

• The speed of these torque wrenches must not exceed 700 rpm, and should typically be about 400 rpm.

- c. Silicone grease

- Spread the silicone grease evenly when mounting heat sinks.

- Sanyo recommends YG-6260 (Momentive Performance Materials Japan LLC)

#### d. Mount

- First mount the heat sink on the semiconductor device, and then mount that assembly on the printed circuit board.

- In case of attaching a heat sink after mounting a semiconductor device into the printed circuit board, be sure not to apply mechanical stress to the semiconductor device and the external pins when tightening up a heat sink with the screw.

- e. When mounting the semiconductor device to the heat sink using jigs, etc.,

- Take care not to allow the device to ride onto the jig or positioning dowel.

- Design the jig so that no unreasonable mechanical stress is applied to the semiconductor device.

### f. Heat sink screw holes

Be sure that chamfering and shear drop of heat sinks must not be larger than the diameter of screw head used.

- When using nuts, do not make the heat sink hole diameters larger than the diameter of the head of the screws used. A hole diameter about 15 % larger than the diameter of the screw is recommended.

- When tap screws are used, be sure that the diameter of the holes in the heat sink are not too small. A diameter about 15 % smaller than the diameter of the screw is recommended.

- g. There is a method to mount the semiconductor device to the heat sink by using a spring band. But this method is not recommended because of possible displacement due to fluctuation of the spring force with time or vibration.

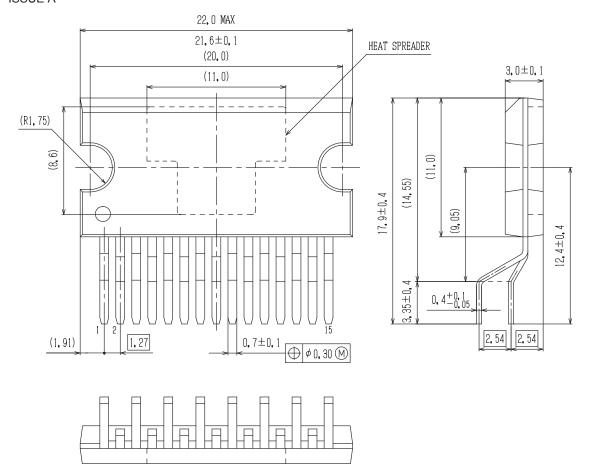

# **Package Dimensions**

unit: mm

**HZIP15** CASE 945AB ISSUE A

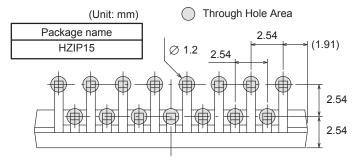

# **SOLDERING FOOTPRINT\***

NOTE: The measurements are not to guarantee but for reference only.

<sup>\*</sup>For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent re