# TTL 256 x 4-Bit Random Access Memory

The 93422 Series are 1024-bit Read/Write RAMs, organized 256 words by 4 bits, designed for high performance main memory and control storage applications.

They have full decoding on-chip, separate data input and data output lines, an active low-output enable, write enable, and two chip selects, one active high, one active low. These memories are fully compatible with standard TTL logic families. A three-state output is provided to drive bus-organized systems and/or highly capacitive loads.

- Three-State Outputs

- Non-Inverting Data Outputs

- Power Dissipation 0.26 mW/Bit Typical

- Standard 22-Pin, 400 Mil Wide Package

- Power Dissipation Decreases with Increasing Temperature

- Organized 256 Words x 4 Bits

- Two Chip Select Lines for Memory Expansion

- Address Access Time: 93422 60 ns Max

93L422A 55 ns Max

93L422 75 ns Max

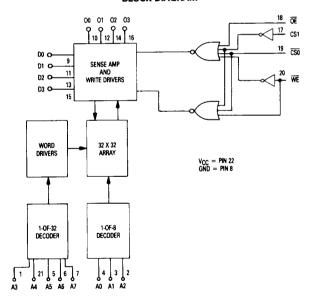

#### **BLOCK DIAGRAM**

# Military 93422 93L422.A

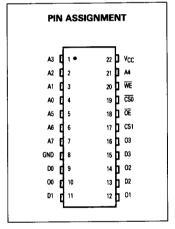

| PIN NAMES |                |  |  |  |  |

|-----------|----------------|--|--|--|--|

| CS0, CS1  | . Chip Selects |  |  |  |  |

| A0-A7     | Address Inputs |  |  |  |  |

| ŌĒ        |                |  |  |  |  |

| WE        | . Write Enable |  |  |  |  |

| D0-D3     |                |  |  |  |  |

| 00-03     | . Data Outputs |  |  |  |  |

#### **FUNCTIONAL DESCRIPTION**

The 93422 Series are fully decoded 1024-bit random access memories organized 256 words by 4 bits. Word selections are achieved by means of an 8-bit address, A0-A7.

The Chip Select (CS0 and CS1) inputs provide for memory array expansion. For large memories, the fast chip select time permits the decoding of chip select from the address without increasing address access time.

The read and write operations are controlled by the state of the active low Write Enable (WE, Pin 20). With WE and CS0 held low and the CS1 held high, the data at  $D_{\Pi}$  is written into the addressed location. To read, WE and CS1 are held high and CS0 is held low. Data in the specified location is presented at the output (00–02) and is non-inverted.

The three-state outputs provide drive capability for higher speeds with capacitive load systems. The third state (high impedance) allows bus-organized systems where multiple outputs are connected to a common bus.

During writing, the output is held in a high-impedance state.

## **GUARANTEED OPERATING RANGES**

|                                              | Suppl | Ambient |       |                         |  |

|----------------------------------------------|-------|---------|-------|-------------------------|--|

| Part Number                                  | Min   | Nom     | Max   | Temp. (T <sub>A</sub> ) |  |

| 93422/BWAJC<br>93L422/BWAJC<br>93L422A/BWAJC | 4.5 V | 5.0 V   | 5.5 V | −55°C to<br>+125°C      |  |

### **ABSOLUTE MAXIMUM RATINGS\***

| Input Current (dc)                                                           | - 12 mA to +5.0 mA |

|------------------------------------------------------------------------------|--------------------|

| Output Current (dc) (Output Low)                                             | + 20 mA            |

| Voltage Applied to Outputs<br>(Output High)                                  | -0.5 V to +5.5 V   |

| Input Voltage (dc)                                                           | -0.5 V to +5.5 V   |

| V <sub>CC</sub> Pin Potential to Ground Pin                                  | -0.5 V to +7.0 V   |

| Operating Junction Temperature, T <sub>J</sub><br>Ceramic Package (W Suffix) | <165℃              |

| Storage Temperature<br>Ceramic Package (W Suffix)                            | -65°C to +150°C    |

<sup>\*</sup>Device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.

#### **TRUTH TABLE**

|    |     | Inputs |    |       |        |                 |

|----|-----|--------|----|-------|--------|-----------------|

| ŌĒ | CS0 | CS1    | WE | D0-D3 | O0-O3  | Mode            |

| Х  | Н   | х      | Х  | х     | High Z | Not Selected    |

| X  | X   | L      | Х  | Х     | High Z | Not Selected    |

| X  | L   | Н      | L  | L     | High Z | Write "0"       |

| Х  | L   | н      | L  | н     | High Z | Write "1"       |

| Н  | Х   | Х      | X  | х     | High Z | Output Disabled |

| L  | L   | Н      | Н  | X     | 00-03  | Read            |

H = High Voltage Level

## DC OPERATING CONDITIONS AND CHARACTERISTICS

(Full operating voltage and temperature range)

|                          | Limits                                 |          |                |            |                        |                                                                                                     |                        |      |        |

|--------------------------|----------------------------------------|----------|----------------|------------|------------------------|-----------------------------------------------------------------------------------------------------|------------------------|------|--------|

| Symbol                   | Characteristic                         |          | Characteristic |            | Min                    | Max                                                                                                 | Units                  | Cond | itions |

| VOL                      | Output Low Voltage                     |          | _              | 0.45       | Vdc                    | V <sub>CC</sub> = Min, I <sub>OL</sub> = 8.0                                                        | mA                     |      |        |

| VIH                      | Input High Voltage                     |          | 2.1            | _          | Vdc                    | Guaranteed Input High Voltage for All Inpu                                                          |                        |      |        |

| VIL                      | Input Low Voltage                      |          |                | 0.8        | Vdc                    | Guaranteed Input Low                                                                                | Voltage for All Inputs |      |        |

| IIL                      | Input Low Current                      |          | 0.01           | - 300      | μAdc                   | V <sub>CC</sub> = Max, V <sub>in</sub> = 0.45 V                                                     |                        |      |        |

| ļш                       | Input High Current                     |          | _              | 40         | μAdc                   | V <sub>CC</sub> = Max, V <sub>in</sub> = 5.5 V                                                      |                        |      |        |

| l <sub>off</sub>         | Output Current (High Z)                |          | _              | 50<br>- 50 | μAdc                   | V <sub>CC</sub> = Max, V <sub>out</sub> = 2.4 V<br>V <sub>CC</sub> = Max, V <sub>out</sub> = 0.45 V |                        |      |        |

| los                      | Output Current Short Circuit to Ground |          | - 10           | 70         | mAdc                   | V <sub>CC</sub> = Max (Note 1)                                                                      |                        |      |        |

| Voн                      | Output High Voltage                    |          | 2.4            | _          | Vdc                    | V <sub>CC</sub> = Min, I <sub>OH</sub> = -5.2 mA                                                    |                        |      |        |

| VIK                      | Input Diode Clamp Volta                | ge       | _              | - 1.5      | Vdc                    | V <sub>CC</sub> = Max, I <sub>in</sub> = -10 mA                                                     |                        |      |        |

|                          |                                        | 93422    | _              | 130        | mAdc                   | T <sub>A</sub> = +125°C                                                                             |                        |      |        |

|                          |                                        |          |                | 155        | mAdc                   | T <sub>A</sub> = +25°C                                                                              |                        |      |        |

| ICC Power Supply Current |                                        | <b>—</b> | 170            | mAdc       | T <sub>A</sub> = -55°C | Vcc = 5.5 V,                                                                                        |                        |      |        |

| lcc                      | Tower Supply Current                   | 93L422A  | _              | 70         | mAdc                   | T <sub>A</sub> = +125°C                                                                             | All Inputs Grounded    |      |        |

|                          | 93L422                                 |          | _              | 80         | mAdc                   | T <sub>A</sub> = +25°C                                                                              | 1                      |      |        |

|                          |                                        |          | _              | 90         | mAdc                   | T <sub>A</sub> = -55°C                                                                              | 1                      |      |        |

L = Low Voltage Level

X = Don't Care (High or Low)

# AC OPERATING CONDITIONS AND CHARACTERISTICS

(Full operating voltage and temperature range)

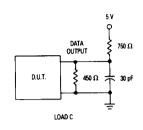

# AC TEST LOAD AND WAVEFORMS

## LOADING CONDITIONS

ù.

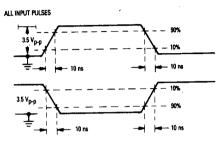

#### INPUT PULSES

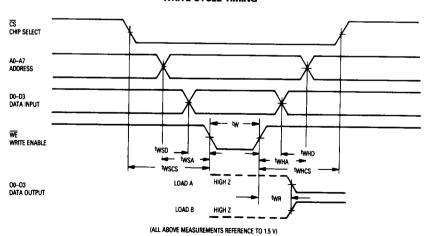

|            | Characteristic                         | 93422/   | 93422/BWAJC |       | 93L422/BWAJC |     | 93L422A/BWAJC |      |

|------------|----------------------------------------|----------|-------------|-------|--------------|-----|---------------|------|

| Symbol     | (Notes 1, 2, 3, 4, 5)                  | Min      | Max         | Min   | Max          | Min | Max           | Unit |

| READ MODE  | DELAY TIMES                            |          |             |       |              |     |               | ns   |

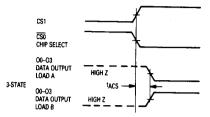

| tACS       | Chip Select Time                       | <b>—</b> | 45          |       | 45           | -   | 40            |      |

| TZRCS      | Chip Select to High Z                  | -        | 45          | 1 - 1 | 45           | -   | 40            |      |

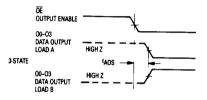

| tAOS       | Output Enable Time                     | I —      | 45          |       | 45           | _   | 40            |      |

| ¹ZROS      | Output Enable to High Z                | l –      | 45          |       | 45           | _   | 40            |      |

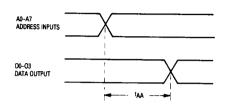

| tAA        | Address Access Time                    |          | 60          |       | 75           |     | 55            |      |

| WRITE MODE | DELAY TIMES                            |          |             |       |              | ľ   |               | ns   |

| tzws       | Write Disable to High Z                | l –      | 45          | -     | 45           | l – | 45            |      |

| twr        | Write Recovery Time                    |          | 50          |       | 50           |     | 45            |      |

|            | INPUT TIMING REQUIREMENTS              |          |             |       |              | 1   |               | ns   |

| ₩          | Write Pulse Width (to guarantee write) | 30       | _           | 30    | _            | 40  | _             |      |

| *WSD       | Data Setup Time Prior<br>to Write      | 5.0      | _           | 5.0   | _            | 5.0 | -             |      |

| tWHD       | Data Hold Time After Write             | 5.0      | _           | 5.0   |              | 5.0 | _             |      |

| tWSA       | Address Setup Time (at tw = Min)       | 10       | _           | 10    | _            | 10  | -             |      |

| tWHA       | Address Hold Time                      | 10       | -           | 10    |              | 5.0 | -             |      |

| twscs      | Chip Select Setup Time                 | 5.0      |             | 5.0   | _            | 5.0 | -             |      |

| twics      | Chip Select Hold Time                  | 5.0      |             | 5.0   | <u> </u>     | 5.0 |               | L    |

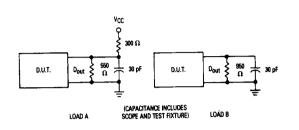

# NOTES:

IOTES:

1. Output short circuit conditions must not exceed 1.0 second duration.

2. The maximum address access time is guaranteed to be the worst-case bit in the memory.

3. Load A used to measure transitions between logic levels and from High Z state to logic Low state.

Load B used to measure transitions between High Z state to logic High state.

Load C used to measure transitions from either logic High or Low state to High Z state.

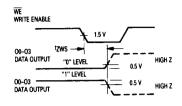

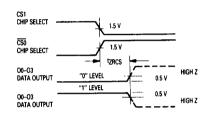

4. All time measurements are referenced to + 1.5 Vdc except transitions into the High Z state where outputs are referenced to a delta of 0.5 Vdc from the logic level using load C.

from the logic level using Load C.

5. See test circuit and waveforms.

# 8

## **READ OPERATION TIMING DIAGRAM**

(All Time Measurements Referenced to 1.5 V)

#### PROPAGATION DELAY FROM CHIP SELECT

# PROPAGATION DELAY FROM ADDRESS INPUTS

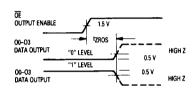

# PROPAGATION DELAY FROM OUTPUT ENABLE

## WRITE CYCLE TIMING

## MOTOROLA MEMORY DATA

## WRITE ENABLE TO HIGH Z DELAY

## PROPAGATION DELAY FROM CHIP SELECT TO HIGH Z

## PROPAGATION DELAY FROM OUTPUT ENABLE TO HIGH Z

(ALL IZXXX PARAMETERS ARE MEASURED AT A DELTA OF 0.5 V FROM THE LOGIC LEVEL AND USING LOAD C.)

|          | θ <sub>JA</sub> (Jui<br>Amb | nction to<br>lient) |                                     |

|----------|-----------------------------|---------------------|-------------------------------------|

| Package  | Blown*                      | Still               | $\theta_{ m JC}$ (Junction to Case) |

| W Suffix | 50°C/W                      | 75°C/W              | 15°C/W                              |

<sup>\*500</sup> linear ft. per minute blown air.

8