### 1. DESCRIPTION

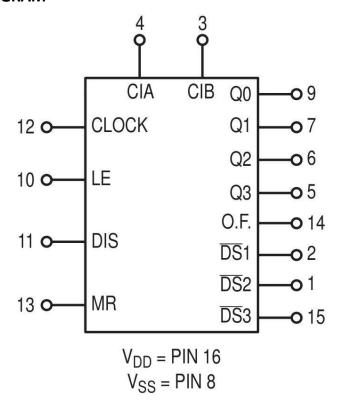

The XD14553 3-digit BCD counter consists of 3 negative edge triggered BCD counters that are cascaded synchronously. A quad latch at the output of each counter permits storage of any given count. The information is then time division multiplexed, providing one BCD number or digit at a time. Digit select outputs provide display control. All outputs are TTL compatible.

An on–chip oscillator provides the low–frequency scanning clock which drives the multiplexer output selector.

This device is used in instrumentation counters, clock displays, digital panel meters, and as a building block for general logic applications.

## 2. FEATURES

- TTL Compatible Outputs

- On–Chip Oscillator

- Cascadable

- Clock Disable Input

- Pulse Shaping Permits Very Slow Rise Times on Input Clock

- Output Latches

- Master Reset

# 3. MAXIMUM RATINGS (Voltages Referenced to V<sub>SS</sub>) (Note 1.)

| Symbol                             | Parameter                                       | Value                         | Unit |

|------------------------------------|-------------------------------------------------|-------------------------------|------|

| V <sub>DD</sub>                    | DC Supply Voltage Range                         | -0.5 to +18.0                 | V    |

| V <sub>in</sub> , V <sub>out</sub> | Input or Output Voltage Range (DC or Transient) | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| I <sub>in</sub>                    | Input Current<br>(DC or Transient) per Pin      | ±10                           | mA   |

| l <sub>out</sub>                   | Output Current<br>(DC or Transient) per Pin     | +20                           | mA   |

| PD                                 | Power Dissipation,<br>per Package (Note 2.)     | 500                           | mW   |

| TA                                 | Ambient Temperature Range                       | -40to +85                     | °C   |

| T <sub>stg</sub>                   | Storage Temperature Range                       | -65 to +150                   | °C   |

| TL                                 | Lead Temperature (8–Second Soldering)           | 260                           | °C   |

<sup>1.</sup> Maximum Ratings are those values beyond which damage to the device may occur.

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range  $V_{SS} \le (V_{in} \text{ or } V_{out}) \le V_{DD}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either V<sub>SS</sub> or V<sub>DD</sub>). Unused outputs must be left open.

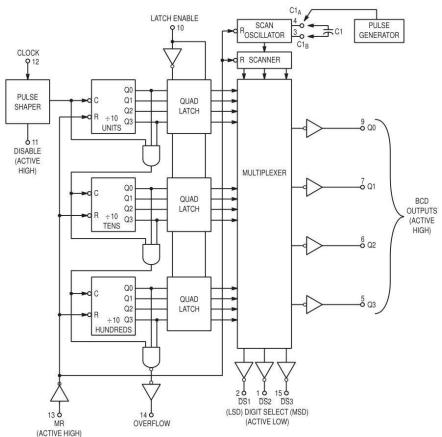

# 4. BLOCK DIAGRAM

TRUTH TABLE

|              | IKUIHI | ADLL          |   |                       |

|--------------|--------|---------------|---|-----------------------|

|              |        |               |   |                       |

| Master Reset | Clock  | Clock Disable |   | Outputs               |

| 0            |        | 0             | 0 | No Change             |

| 0            |        | 0             | 0 | Advance               |

| 0            | X      | 1             | X | No Change             |

| 0            | 1      |               | 0 | Advance               |

| 0            | 1      | $\sim$        | 0 | No Change             |

| 0            | 0      | Х             | X | No Change             |

| 0            | X      | Х             |   | Latched               |

| 0            | X      | Х             | 1 | Latched               |

| 1            | X      | Х             | 0 | Q0 = Q1 = Q2 = Q3 = 0 |

X = Don't Care

## 5. ELECTRICAL CHARACTERISTICS(Voltages Referenced to Vss)

| Characteristic                                                                | Symbol          | V <sub>DD</sub> | -40℃   |      | 25 ℃     |                                                   |      | 85°C     |          |      |

|-------------------------------------------------------------------------------|-----------------|-----------------|--------|------|----------|---------------------------------------------------|------|----------|----------|------|

|                                                                               |                 | Vdc             | Min    | Max  | Min      | Тур (3.)                                          | Max  | Min      | Max      | Unit |

| Output Voltage "0"                                                            | V <sub>OL</sub> | 5.0             | _      | 0.05 | _        | 0                                                 | 0.05 | _        | 0.05     | Vdc  |

| Level $V_{in} = V_{DD}$ or 0                                                  |                 | 10              | _      | 0.05 | –        | 0                                                 | 0.05 | –        | 0.05     |      |

|                                                                               |                 | 15              | _      | 0.05 | _        | 0                                                 | 0.05 | _        | 0.0<br>5 |      |

| "1" Level                                                                     | V <sub>OH</sub> | 5.0             | 4.95   | _    | 4.95     | 5.0                                               | _    | 4.95     | _        | Vdc  |

| $V_{in} = 0 \text{ or } V_{DD}$                                               | V ∪H            | 10              | 9.95   | _    | 9.95     | 10                                                | _    | 9.95     | _        | ""   |

|                                                                               |                 | 15              | 14.95  | _    | 14.95    | 15                                                | _    | 14.95    | _        |      |

| Input Voltage "0"                                                             | V <sub>IL</sub> |                 |        |      |          |                                                   |      |          |          | Vdc  |

| Level ( $V_0 = 4.5 \text{ or } 0.5 \text{ Vdc}$ )                             |                 | 5.0             | _      | 1.5  | –        | 2.25                                              | 1.5  | _        | 1.5      |      |

| $(V_0 = 9.0 \text{ or } 1.0 \text{ Vdc})$                                     |                 | 10              | _      | 3.0  | –        | 4.50                                              | 3.0  | –        | 3.0      |      |

| (Vo = 13.5 or 1.5 Vdc)                                                        |                 | 15              | _      | 4.0  | _        | 6.75                                              | 4.0  | _        | 4.0      |      |

| "1" Level                                                                     | V <sub>IH</sub> |                 |        |      |          |                                                   |      |          |          | Vdc  |

| (Vo = 0.5  or  4.5  Vdc)                                                      |                 | 5.0             | 3.5    | _    | 3.5      | 2.75                                              | _    | 3.5      | _        |      |

| $(V_0 = 1.0 \text{ or } 9.0 \text{ Vdc})$                                     |                 | 10              | 7.0    | _    | 7.0      | 5.50                                              | _    | 7.0      | _        |      |

| $(V_0 = 1.5 \text{ or } 13.5 \text{ Vdc})$                                    |                 | 15              | 11     | _    | 11       | 8.25                                              | _    | 11       | _        |      |

| Output Drive Current                                                          | I <sub>OH</sub> |                 |        |      |          |                                                   |      |          |          | mAdc |

| (V <sub>OH</sub> = 4.6 Vdc) Source                                            |                 | 5.0             | - 0.25 | _    | - 0.2    | - 0.36                                            | _    | 0.14     | _        |      |

| (V <sub>OH</sub> = 9.5 Vdc) Pin 3                                             |                 | 10              | - 0.62 | _    | - 0.5    | - 0.9                                             | _    | 0.35     | _        |      |

| (V <sub>OH</sub> = 13.5 Vdc)                                                  |                 | 15              | -1.8   | _    | - 1.5    | - 3.5                                             | –    | 1.1      | _        |      |

| (VoH = 4.6 Vdc) Source —                                                      |                 | 5.0             | - 0.64 | _    | - 0.51   | - 0.88                                            | _    | -0.36    | _        | mAdc |

| $(V_{OH} = 9.5 \text{ Vdc})Other$                                             |                 | 10              | -1.6   | _    | -1.3     | - 2.25                                            | _    | - 0.9    | _        |      |

| (VoH = 13.5 Vdc) Outputs                                                      |                 | 15              | -4.2   | _    | -3.4     | - 8.8                                             | _    | - 2.4    | _        |      |

| (V <sub>OL</sub> = 0.4 Vdc) Sink —                                            | I <sub>OL</sub> | 5.0             | 0.5    | _    | 0.4      | 0.88                                              | _    | 0.28     | _        | mAdc |

| (VoL = 0.5 Vdc) Pin 3                                                         |                 | 10              | 1.1    | _    | 0.9      | 2.25                                              | _    | 0.65     | _        |      |

| $(V_{OL} = 1.5 \text{ Vdc})$                                                  |                 | 15              | 1.8    | _    | 1.5      | 8.8                                               | _    | 1.20     | _        |      |

| $(V_{OL} = 0.4 \text{ Vdc})$ Sink — Other                                     |                 | 5.0             | 3.0    | _    | 2.5      | 4.0                                               | _    | 1.6      | _        | mAdc |

| (V <sub>OL</sub> = 0.5 Vdc) Outputs                                           |                 | 10              | 6.0    | _    | 5.0      | 8.0                                               | _    | 3.5      | _        |      |

| (Vol = 1.5 Vdc)                                                               |                 | 15              | 18     | _    | 15       | 20                                                | _    | 10       | _        |      |

| Input Current                                                                 | I <sub>in</sub> | 15              | _      | ±0.1 | _        | ±<br>0.00001                                      | ±0.1 | _        | ±<br>1.0 | μAdc |

| Input                                                                         | C <sub>in</sub> | _               | _      | _    | _        | 5.0                                               | 7.5  | _        | _        | pF   |

| Capacitance                                                                   |                 |                 |        |      |          |                                                   |      |          |          |      |

| (V <sub>in</sub> = 0)                                                         |                 |                 |        |      |          |                                                   |      |          |          |      |

| Quiescent                                                                     | I <sub>DD</sub> | 5.0             | _      | 5.0  | –        | 0.010                                             | 5.0  | –        | 150      | μAdc |

| Current                                                                       |                 | 10              | _      | 10   | -        | 0.020                                             | 10   | -        | 300      |      |

| (Per                                                                          |                 | 15              | _      | 20   | _        | 0.030                                             | 20   | -        | 600      |      |

| Package)                                                                      |                 |                 |        |      |          |                                                   |      |          |          |      |

| MR = V <sub>DD</sub>                                                          |                 | F 0             |        |      | <u> </u> | . (O 2E A /I-I                                    | L-/  | <u> </u> | <u> </u> |      |

| Total Supply Current <sup>(4.)</sup> <sup>(5.)</sup> (Dynamic plus Quiescent, | lτ              | 5.0<br>10       |        |      | f +      | : (0.35 µA/kl<br>IDD   IT = (0.8<br>/kHz) f + IDD | 35   |          |          | μAdc |

| Per Package)                                                                  |                 | 15              |        |      |          | ; (1.50 μA/k                                      |      | )        |          |      |

| $(C_L = 50 \text{ pF on all outputs, all})$                                   |                 | 10              |        |      | • •      | / bu //                                           | _,   |          |          |      |

| buffers switching)                                                            |                 |                 |        |      |          |                                                   |      |          |          |      |

<sup>3.</sup> Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

$$I_T(C_L) = I_T(50 \text{ pF}) + (C_L - 50) \text{ Vfk}$$

where: IT is in  $\mu$ A (per package), CL in pF, V = (VDD – VSS) in volts, f in kHz is input frequency, and k = 0.004.

<sup>4.</sup> The formulas given are for the typical characteristics only at 25 C.

<sup>5.</sup> To calculate total supply current at loads other than 50 pF:

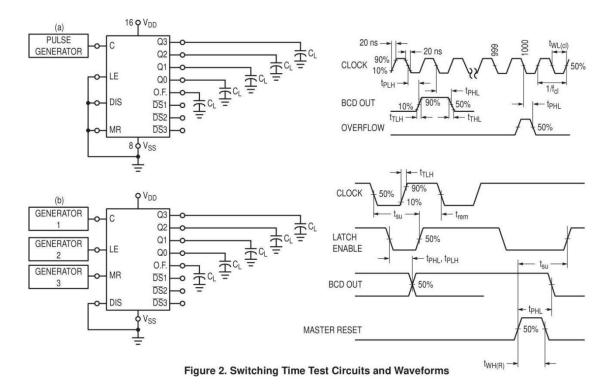

# 6. SWITCHING CHARACTERISTICS (6.) (CL = 50 pF, TA = 25 C)

| Characteristic                                                                                                                                | Figure | Symbol                                 | V <sub>DD</sub> | Min                | Тур (7.)              | Max                 | Unit    |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------|-----------------|--------------------|-----------------------|---------------------|---------|

| Output Rise and Fall Time  ttlh, tthl = (1.5 ns/pF) CL + 25 ns  ttlh, tthl = (0.75 ns/pF) CL + 12.5 ns  ttlh, tthl = (0.55 ns/pF) CL + 9.5 ns | 2a     | t <sub>TLH</sub> ,<br>t <sub>THL</sub> | 5.0<br>10<br>15 | _<br>_<br>_<br>_   | 100<br>50<br>40       | 200<br>100<br>80    | ns      |

| Clock to BCD Out                                                                                                                              | 2a     | t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | 5.0<br>10<br>15 | _<br>_<br>_        | 900<br>500<br>200     | 1800<br>1000<br>400 | ns      |

| Clock to Overflow                                                                                                                             | 2a     | t <sub>PHL</sub>                       | 5.0<br>10<br>15 | _<br>_<br>_        | 600<br>400<br>200     | 1200<br>800<br>400  | ns      |

| Reset to BCD Out                                                                                                                              | 2b     | t <sub>PHL</sub>                       | 5.0<br>10<br>15 | -<br>-<br>-        | 900<br>500<br>300     | 1800<br>1000<br>600 | ns      |

| Clock to Latch Enable Setup Time<br>Master Reset to Latch Enable Setup Time                                                                   | 2b     | t <sub>su</sub>                        | 5.0<br>10<br>15 | 600<br>400<br>200  | 300<br>200<br>100     | _<br>_<br>_         | ns      |

| Removal Time<br>Latch Enable to Clock                                                                                                         | 2b     | t <sub>rem</sub>                       | 5.0<br>10<br>15 | -80<br>-10<br>0    | - 200<br>- 70<br>- 50 | _<br>_<br>_         | ns      |

| Clock Pulse Width                                                                                                                             | 2a     | t <sub>WH(cl)</sub>                    | 5.0<br>10<br>15 | 550<br>200<br>150  | 275<br>100<br>75      | _<br>_<br>_         | ns      |

| Reset Pulse Width                                                                                                                             | 2b     | t <sub>WH(R)</sub>                     | 5.0<br>10<br>15 | 1200<br>600<br>450 | 600<br>300<br>225     | _<br>_<br>_         | ns      |

| Reset Removal Time                                                                                                                            | _      | t <sub>rem</sub>                       | 5.0<br>10<br>15 | -80<br>0<br>20     | - 180<br>- 50<br>- 30 | _<br>_<br>_         | ns      |

| Input Clock Frequency                                                                                                                         | 2a     | f <sub>cl</sub>                        | 5.0<br>10<br>15 | _<br>_<br>_        | 1.5<br>5.0<br>7.0     | 0.9<br>2.5<br>3.5   | MH<br>z |

| Input Clock Rise Time                                                                                                                         | 2b     | t <sub>тьн</sub>                       | 5.0<br>10       | No Limit           |                       | ns                  |         |

| Disable, MR, Latch Enable                                                                                                                     | _      | t <sub>TLH</sub> ,                     | 15<br>5.0       | _                  | _                     | 15                  | μѕ      |

| Rise and Fall Times                                                                                                                           |        | t <sub>THL</sub>                       | 10<br>15        | _<br>_             | _<br>_                | 5.0<br>4.0          | ·       |

| Scan Oscillator<br>Frequency (C1<br>measured in μF)                                                                                           | 1      | f <sub>osc</sub>                       | 5.0<br>10       | _<br>_             | 1.5/C1<br>4.2/C1      | _<br>_              | Hz      |

|                                                                                                                                               |        |                                        | 15              | _                  | 7.0/C1                | _                   |         |

<sup>6.</sup> The formulas given are for the typical characteristics only at 25 C.

<sup>7.</sup> Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

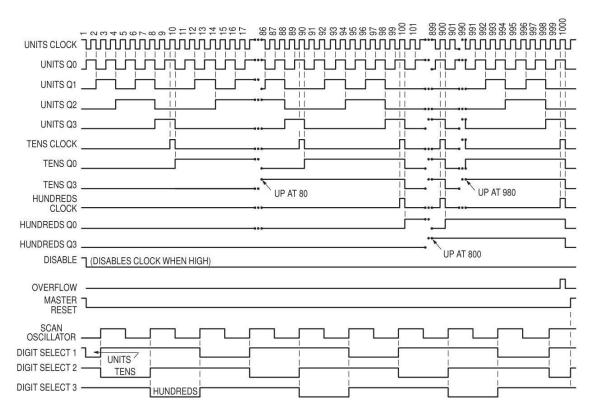

Figure 1. 3-Digit Counter Timing Diagram (Reference Figure 3)

#### **OPERATING CHARACTERISTICS**

The XD14553 three–digit counter, shown in Figure 3, consists of three negative edge–triggered BCD counters which are cascaded in a synchronous fashion. A quad latch at the output of each of the three BCD counters permits storage of any given count. The three sets of BCD outputs (active high), after going through the latches, are time division multiplexed, providing one BCD number or digit at a time. Digit select outputs (active low) are provided for display control. All outputs are TTL compatible.

An on–chip oscillator provides the low frequency scanning clock which drives the multiplexer output selector. The frequency of the oscillator can be controlled externally by a capacitor between pins 3 and 4, or it can be overridden and driven with an external clock at pin 4. Multiple devices can be cascaded using the overflow output, which provides one pulse for every 1000 counts.

The Master Reset input, when taken high, initializes the three BCD counters and the multiplexer scanning circuit. While Master Reset is high the digit scanner is set to digit one; but all three digit select outputs are disabled to prolong display life, and the scan oscillator is inhibited. The Disable input, when high, prevents the input clock from reaching the counters, while still retaining the last count. A pulse shaping circuit at the clock input permits the counters to continue operating on input pulses with very slow rise times. Information present in the counters when the latch input goes high, will be stored in the latches and will be retained while the latch input is high, independent of other inputs. Information can be recovered from the latches after the counters have been reset if Latch Enable remains high during the entire reset cycle.

Figure 3. Expanded Block Diagram

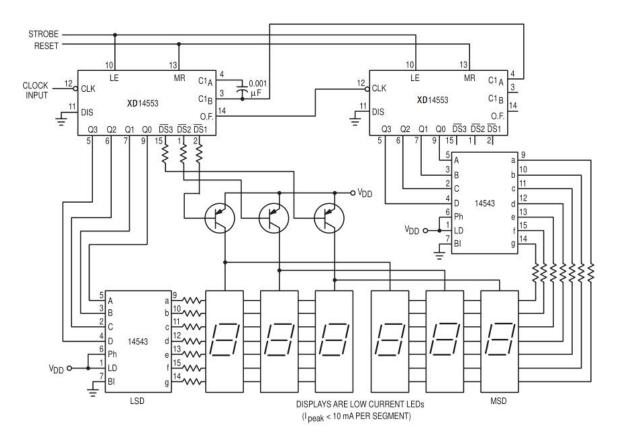

Figure 4. Six-Digit Display

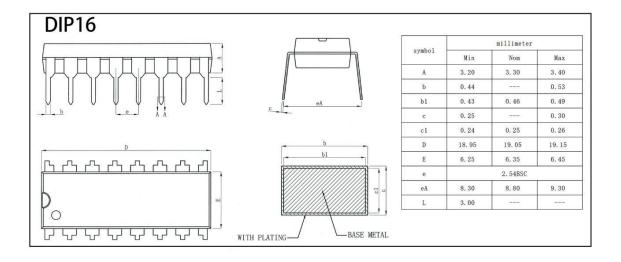

## 7. ORDERING INFORMATION

## **Ordering Information**

| Part    | Device  | Package | Body size    | Temperature | MSL  | Transport | Package  |

|---------|---------|---------|--------------|-------------|------|-----------|----------|

| Number  | Marking | Type    | (mm)         | (°C)        |      | Media     | Quantity |

| XD14553 | XD14553 | DIP16   | 19.05 * 6.35 | - 40 to 85  | MSL3 | Tube 25   | 1000     |

## 8. DIMENSIONAL DRAWINGS