# **AM29818A**

# Pipeline Register with SSR Diagnostics

The AM29818A is a high-speed, general-purpose pipeline register with an on-board shadow register for performing Serial Shadow Register (SSR) Diagnostics and/or Writable Control Store loading.

The D-to-Y path provides an 8-bit parallel data path pipeline register for normal system operation. The shadow register can load parallel data to or from the pipeline register and can output data through the D input port (as in WCS loading).

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- · Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# Am29818A

# Advanced Micro Devices

# Pipeline Register with SSR™ Diagnostics

# DISTINCTIVE CHARACTERISTICS

- High-speed noninverting 8-bit parallel register for any data path or pipelining application

- WCS (Writable Control Store) pipeline register

- Load WCS from serial register

- Read WCS via serial scan

- Alternate sourced as SN54/74S818

- High-speed 8-bit "shadow register" with serial shift mode for Serial Shadow Register (SSR) Diagnostics

- Controllability: serial scan in new machine state

- Observability: serial scan out diagnostics routine results

- Speed comparable with that of 'AS374 register

#### GENERAL DESCRIPTION

The Am29818A is a high-speed, general-purpose pipeline register with an on-board shadow register for performing Serial Shadow Register (SSR) Diagnostics and/or Writable Control Store loading.

The D-to-Y path provides an 8-bit parallel data path pipeline register for normal system operation. The shadow register can load parallel data to or from the pipeline register and can output data through the D input port (as in WCS loading).

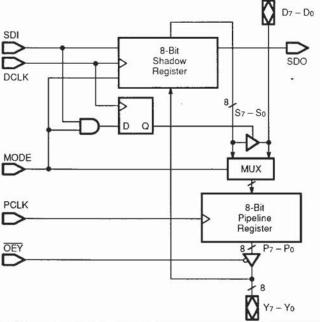

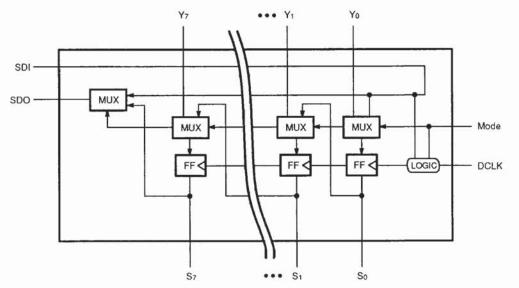

The 8-bit shadow register has multiplexer inputs that select parallel inputs from the Y-port or adjacent bits in the shadow register to operate as a shift register. In the se-

rial shift mode, SDI is shifted into the '0' location of the Shadow register and the contents of '7' location appear at the SDO output. This register can then participate in a serial loop throughout the system where normal data, address, status and control registers are replaced with Am29818A Diagnostic Pipeline Registers. The loop can be used to scan in a complete test routine starting point (data, address, etc.). Then after a specified number of clock cycles, the data clocked out can be compared to the expected results. WCS loading can be accomplished using the same technique. An instruction word can be serially shifted into the shadow register and written into the WCS RAM by enabling the D output.

### **BLOCK DIAGRAM**

08611-001A

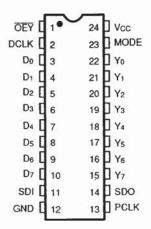

# CONNECTION DIAGRAM Top View

08611-002A

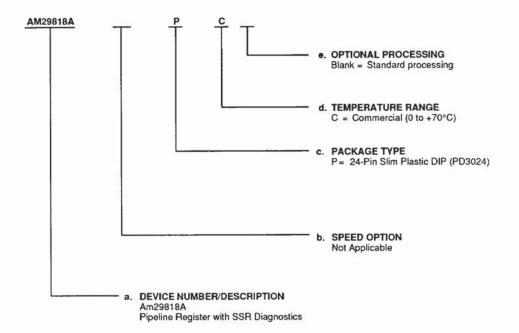

# ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

a. Device Number

- a. Device Number

b. Speed Option (If applicable)

c. Package Type

d. Temperature Range

e. Optional Processing

| Valid Combinations |    |  |  |  |  |

|--------------------|----|--|--|--|--|

| AM29818A           | PC |  |  |  |  |

# **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

### PIN DESCRIPTION

Do - D7

#### Parallel Data Inputs (Input/Output)

Parallel data input to the pipeline register or parallel data output from the shadow register (see Function Table for control modes).

#### DCLK

# Diagnostics Clock (Input)

Diagnostics/WCS clock for loading shadow register (serial or parallel modes – see Function Table).

#### MODE

#### Mode Control (Input)

Control input for pipeline register multiplexer and shadow register control (see Function Table).

#### OEY

### Y-Port Output Enable (Input: Active LOW)

Active LOW output enable for Y-port.

#### **PCLK**

#### Pipeline Register Clock (Input)

Pipeline register clock input loads D-port or shadow register contents on LOW-to-HIGH transition.

#### eni

### Serial Data Input (Input)

Input to shadow register (see Function Table).

#### SDO

#### Serial Data Output (Output)

Output from shadow register.

#### Yo - Y7

# Parallel Data Outputs (Input/Output)

Data outputs from the pipeline register and parallel inputs to the shadow register.

# **FUNCTIONAL DESCRIPTION**

Data transfers into the shadow register occur on the LOW-to-HIGH transition of DCLK. MODE and SDI determines what data source will be loaded. The pipeline register is loaded on the LOW-to-HIGH transition of PCLK. MODE selects whether the data source is the data input or the shadow register output. Because of the

independence of the clock inputs data can be shifted in the shadow register via DCLK and loaded into the pipeline register from the data input via PCLK simultaneously. As long as no setup or hold times are violated, this simultaneous operation is legal.

#### **FUNCTION TABLE**

| Inputs |      |      | Outputs |                |                                                  |                                 |                                                                          |  |  |

|--------|------|------|---------|----------------|--------------------------------------------------|---------------------------------|--------------------------------------------------------------------------|--|--|

| SDI    | MODE | DCLK | PCLK    | SDO            | Shadow<br>Register                               | Pipeline<br>Register            | Operation                                                                |  |  |

| Х      | L    | 1    | х       | S <sub>7</sub> | $S_i \leftarrow S_{i-1}$<br>$S_0 \leftarrow SDI$ | NA                              | Serial Shift; D <sub>7</sub> – D <sub>0</sub> Disabled                   |  |  |

| Х      | L    | Х    | 1       | S <sub>7</sub> | NA                                               | Pi ← Di                         | Normal Load Pipeline Register                                            |  |  |

| L      | Н    | 1    | Х       | SDI            | S <sub>i</sub> ← Y <sub>i</sub>                  | NA                              | Load Shadow Register from Y; D <sub>7</sub> – D <sub>0</sub><br>Disabled |  |  |

| Х      | Н    | X    | 1       | SDI            | NA                                               | P <sub>i</sub> ← S <sub>i</sub> | Load Pipeline Register from Shadow Reg.                                  |  |  |

| Н      | Н    | 1    | Х       | SDI            | Hold*                                            | NA                              | Hold Shadow Register; D7 - Do Enabled*                                   |  |  |

<sup>\*</sup>Although not shown, Hold is implemented by gating DCLK internally.

#### **Table Definitions**

#### Inputs

H = HIGH

L = LOW

X = Don't Care

1 = LOW-to-HIGH Transition

### Outputs

S7 - S0 = Shadow Register outputs

P7 -P0 = Pipeline Register outputs

D7 -D0 = Data I/O port

$Y_7 - Y_0 = Y I/O port$

NA = Not applicable, output is not a function

of the specified input combinations.

# SHADOW REGISTER

08611-005A

### An Introduction to Serial Shadow Register (SSR) Diagnostics

#### Diagnostics

A diagnostics capability provides the necessary functionality as well as a systematic method for detecting and pin-pointing hardware-related failures in a system. This capability must be able to both observe intermediate test points and control intermediate signals address, data, control and status - to exercise all portions of the system under test. These two capabilities - observability and controllability - provide the ability to establish a desired set of input conditions and state register values, sample the necessary outputs, and determine whether the system is functioning correctly.

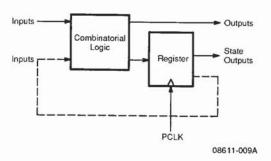

#### **Testing Combinatorial and Sequential Networks**

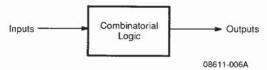

The problem of testing a combinational logic network is well understood (Figure 1). Sets of input signals (test vectors) are applied to the network and the network outputs are compared to the set of computed outputs (result vectors). In some cases sets of test vectors and result vectors can be generated in a computer-aided environment, minimizing engineering effort. Additionally, fault coverage analysis can be automated to provide a measure of how efficient a set of test vectors is at pinpointing hardware failures. For example, a popular measure of fault coverage computes the percentage of stuck-at-ones (nodes with outputs always HIGH) and stuck-at-zeros (nodes with outputs always LOW) a given set at test vectors will discover.

Figure 1. Combinatorial Logic Network

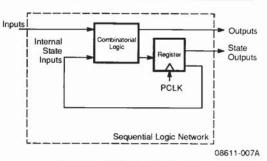

A sequential network (Figure 2) is much more difficult to test systematically. The outputs of a sequential network depend not only on the present inputs but also on the internal state of the network. Initializing the internal state register to the value necessary to test a given set of inputs is difficult at best, and not easily automated. Additionally, observing the internal state of a sequential network can be very difficult and time consuming if the state information is not directly available. For example, consider the problem of determining the value of an internal 16-bit counter if only a carry-out signal is available. The counter must be clocked until it reaches the carry-out state and the starting value computed. Up to 65,535 clock cycles may be necessary! An easier method must exist. Serial Shadow Register diagnostics provides this method

Figure 2. Sequential Network

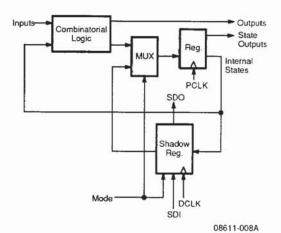

#### Serial Shadow Register Diagnostics

Serial Shadow Register diagnostics provides sufficient observability and controllability to turn any sequential network into a combinatorial network. This is accomplished by providing the means to both initialize (control) and sample (observe) the state elements of a sequential network. Figure 3 shows the method by which serial shadow register diagnostics accomplishes these two functions.

Figure 3. SSR Diagnostics Diagram

Serial Shadow Register diagnostics utilizes an extra multiplexer on the input of each state register and a duplicate or shadow of each state flip/flop in an additional register. The shadow register can be loaded serially via the serial data input (thus the name Serial Shadow Register diagnostics) for controllability. Once the desired state information is loaded into the serial register it can be transferred into the internal state register by selecting the multiplexer and clocking the state register with PCLK. This allows any internal state to be set to a desired state in a simple, quick, and systematic manner.

Internal state information can be sampled by loading the serial register from the state register outputs. This state information can then be shifted out via the serial data output to provide observability. Notice that the serial data inputs and outputs can be cascaded to make long chains of state information available on a minimum number of connections.

In effect, Serial Shadow Register diagnostics breaks the normal feedback path of the sequential network and establishes a logical path with which inputs can be defined and outputs sampled (Figure 4). This means that those techniques which have been developed to test combinatorial networks can be applied to any sequential network in which Serial Shadow Register diagnostics is utilized.

Figure 4. SSR Diagnostics Logical Path

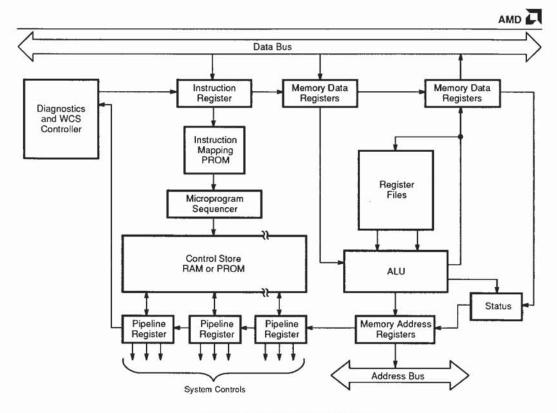

# A Typical Computer Architecture with SSR Diagnostics

When normal pipeline registers are replaced by SSR diagnostics pipeline registers system debug and diagnostics are easily implemented. State information which was inaccessible is now both observable and controllable. Figure 5 shows a typical computer system using the Am29818A.

Serial paths have been added to all the important state registers (macro instruction, data, status, address, and micro instruction registers). This extra path will make it easier to diagnose system failures by breaking the feedback paths and turning sequential state machines into combinatorial logic blocks. For example, the status outputs of the ALU may be checked by loading the micro instruction register with the necessary micro instruction. The desired ALU function is then executed and the status outputs captured in the status register. The status bits can then be serially shifted out and checked for validity.

A single diagnostic loop was shown in Figure 5 for simplicity, but several loops can be employed in more complicated systems to reduce scan time. Additionally, the Am29818As can be used to sample intermediate test points not associated with normal state information. These additional test points can further ease diagnostics, testability and debug.

SSR Diagnostics/WCS Pipeline Registers Replace Normal Registers with Diagnostics Loop

08611-010A

Figure 5. Typical System Configuration

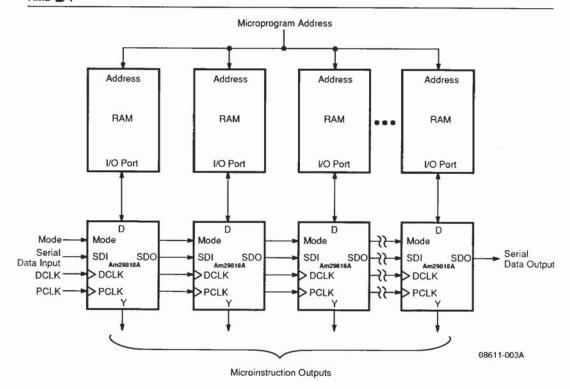

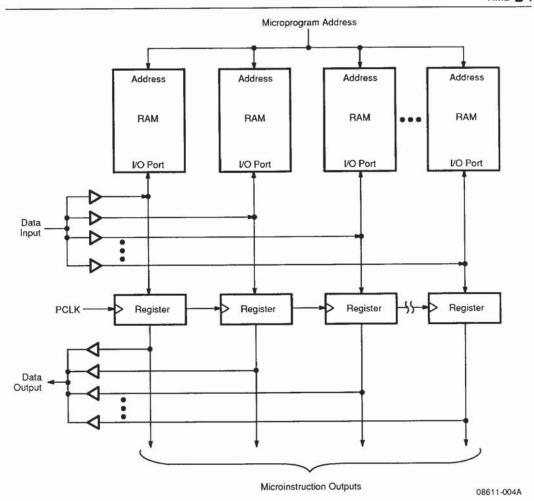

# Use of the Am29818A Pipeline Register in Writable Control Store (WCS) Designs

The Am29818A SSR diagnostics/WCS Pipeline Register was designed specifically to support writable control store designs. In the past, designers of WCS based systems needed to use an excessive amount of support circuitry to implement a WCS. As shown in Figure 7, additional input and output buffers are necessary to provide paths from the parallel input data bus to the memory, and from the instruction register to the output data bus. The input port is necessary to write data to the control store, initializing the micromemory. The output port provides the access to the instruction register, indirectly allowing the RAM to be read. Additionally, access to the instruction register is useful during system debugging and system diagnostics.

The Am29818A supports all of the above operations (and more) without any support circuitry. Figure 6 shows

a typical WCS design with the Am29818A. Access to memory is now possible over the serial diagnostics port. The instruction register contents may be read by serially shifting the information out on the diagnostics port. Additionally, the instruction register may be written from the serial port via the shadow register. This simplifies system debug and diagnostics operations considerably.

# Conclusion

Serial Shadow Register diagnostics provides the observability and controllability necessary to take any sequential network and turn it into a combinatorial network. This provides a method for pin-pointing digital system hardware failures in a systematic and well-understood fashion.

Figure 6. Am29818A-Based WCS Application

Figure 7. WCS Application without Am29818As

# **ABSOLUTE MAXIMUM RATINGS**

Storage Temperature -65°C to +150°C Ambient Temperature with Power Applied -55°C to +125°C Supply Voltage to Ground Potential Continuous -0.5 V to +7.0 V DC Voltage Applied to Outputs for High Output State -0.5 V to +5.5 V

DC Input Voltage -1.5 V to +6.0 V DC Output Current, into Outputs 100 mA DC Input Current

-30 mA to +5.0 mA

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality

at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

Commercial (C) Devices

Temperature (TA) 0°C to +70°C Supply Voltage (Vcc) +4.5 V to +5.5 V

Operating ranges define those limits between which the funtionality of the device is guaranteed.

# DC CHARACTERISTICS over operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description | Test Condition                                 | s                                     | Min.                    | Max. | Unit  |     |

|---------------------|-----------------------|------------------------------------------------|---------------------------------------|-------------------------|------|-------|-----|

| Voн                 | Output HIGH Voltage   | Vcc = 4.5 V                                    | Y0 - Y7                               | Iон = -6 mA             | 2.4  |       | ٧   |

|                     | 357                   | VIN = VIH OF VIL                               | D <sub>0</sub> - D <sub>7</sub> , SDO | Iон = -1 mA             | 2.4  |       | ٧   |

| VoL                 | Output LOW Voltage    | Vcc = 4.5 V                                    | Y0 - Y7                               | lo <sub>L</sub> = 24 mA |      | 0.5   | ٧   |

|                     |                       | VIN = VIH OF VIL                               | D <sub>0</sub> – D <sub>7</sub> , SDO | IoL = 8 mA              |      | 0.5   | V   |

| VIH                 | Input HIGH Voltage    | Guaranteed Inp<br>inputs (Note 1)              | 2.0                                   |                         | V    |       |     |

| VIL                 | Input LOW Voltage     | Guaranteed Inp<br>inputs (Note 1)              |                                       | 0.8                     | V    |       |     |

| Vı                  | Input Clamp Voltage   | Vcc = 4.5 V, lin                               |                                       | -1.2                    | ٧    |       |     |

| lıL                 | Input LOW Current     | Vcc = 5.5 V, V <sub>IN</sub> = 0.5 V           |                                       |                         |      | -0.25 | mA  |

| fін                 | Input HIGH Current    | Vcc = 5.5 V, V <sub>IN</sub> = 2.4 V           |                                       |                         |      | 50    | μА  |

| lı                  | Input HIGH Current    | Vcc = 5.5 V, VIN 5.5 V                         |                                       |                         |      | 100   | μА  |

| loz                 | Off-State Current     | Vcc = 5.5 V Vo = 0.5 V Vo = 2.4 V              |                                       |                         | -250 | μА    |     |

|                     | (High-Impedance)      |                                                |                                       |                         |      | 100   | μА  |

| Isc                 | Output Short-Circuit  | Vcc = 5.5 V Y <sub>0</sub> - Y <sub>7</sub>    |                                       | -30                     | -100 | mA    |     |

|                     | Current               | (Note 2) D <sub>0</sub> – D <sub>7</sub> , SDO |                                       |                         | -15  |       | -50 |

| loff                | Bus Leakage           | Vcc = 0 V, Vout = 2.9 V                        |                                       |                         |      | 100   | μА  |

| Icc                 | Power Supply Current  | Vcc = 5.5 V                                    | Outputs Hi-Z                          |                         | 145  | mA    |     |

#### Notes:

<sup>1.</sup> Input thresholds are tested during DC parameter testing, and may be tested in combination with other DC parameters.

<sup>2.</sup> Not more than one output shorted at a time. Duration of the short-circuit test should not exceed one second.

# SWITCHING CHARACTERISTICS over operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description            | Test Conditions*       | Min. | Max. | Unit |

|---------------------|----------------------------------|------------------------|------|------|------|

| tplh<br>&<br>tphl   | PCLK → Yx                        |                        |      | 9    | ns   |

|                     | MODE → SDO                       | C <sub>L</sub> = 50 pF |      | 16   | ns   |

|                     | SDI → SDO                        |                        |      | 15   | пѕ   |

|                     | DCLK → SDO                       |                        |      | 25   | ns   |

|                     | D <sub>X</sub> → PCLK            |                        | 4    |      | ns   |

|                     | MODE → PCLK                      |                        | 15   |      | ns   |

| ts                  | Yx → DCLK                        |                        | 5    |      | ns   |

|                     | MODE → DCLK                      |                        | 12   |      | ns   |

|                     | SDI → DCLK                       |                        | 10   |      | ns   |

|                     | DCLK → PCLK                      |                        | 15   |      | ns   |

|                     | PCLK → DCLK                      |                        | 40   |      | ns   |

| tн                  | $D_X \rightarrow PCLK$           |                        | 2    |      | ns   |

|                     | MODE → PCLK                      |                        | 0    |      | ns   |

|                     | Yx → DCLK                        |                        | 5    |      | ns   |

|                     | MODE → DCLK                      |                        | 2    |      | ns   |

|                     | SDI → DCLK                       |                        | 0    |      | ns   |

| tız                 | $\overline{OEY} \rightarrow Y_X$ | 1                      |      | 15   | ns   |

|                     | DCLK → D <sub>X</sub>            |                        |      | 45   | ns   |

| tHZ                 | $\overline{OEY} \rightarrow Y_X$ |                        |      | 25   | ns   |

|                     | DCLK → D <sub>X</sub>            |                        |      | 80   | ns   |

| tzL                 | <del>OEY</del> → Y <sub>X</sub>  |                        |      | 15   | ns   |

|                     | DCLK → D <sub>X</sub>            |                        |      | 25   | ns   |

| tzн                 | <del>OEY</del> → Y <sub>X</sub>  |                        |      | 15   | ns   |

|                     | DCLK → D <sub>X</sub>            | 1                      |      | 25   | ns   |

| tew                 | PCLK (HIGH and LOW)              |                        | 10   |      | ns   |

|                     | DCLK (HIGH and LOW)              | 1                      | 15   |      | ns   |

<sup>\*</sup>See Test Circuit and Waveforms (Chapter 2).

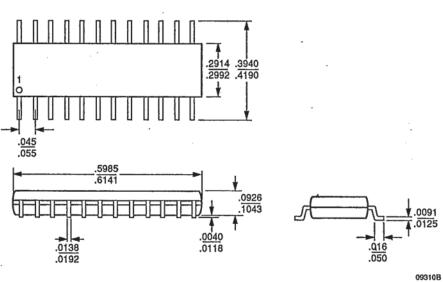

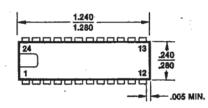

# PD3024

# CD3024

\*For reference only.

1954 6 - 03

112

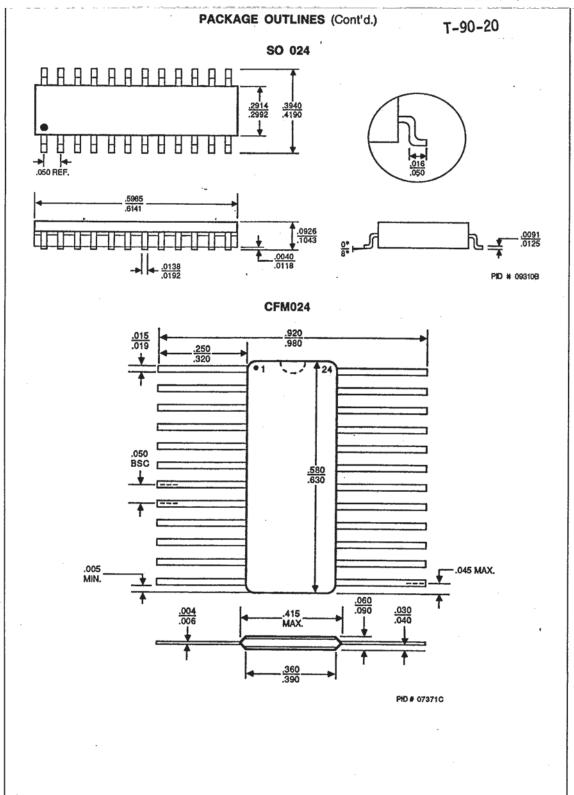

# PACKAGE OUTLINES (Cont'd.)

T-90-20

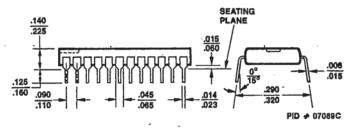

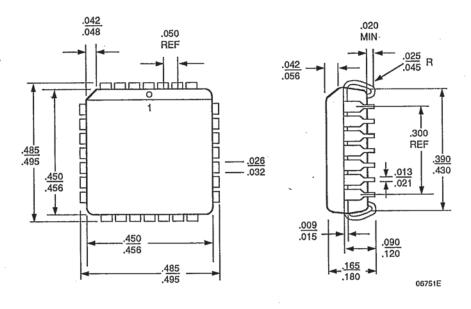

PL 028

PID # 06751E

**CL 028**

PHD # 06595D

Advanced Micro Devices reserves the right to make changes in its product without notice in order to improve design or performance characteristics. The performance characteristics listed in this document are guaranteed by specific tests, correlated testing, guard banding, design and other practices common to the industry. For specific testing details, contact your local AMD sales representative. The company assumes no responsibility for the use of any circuits described herein.

ADVANCED MICRO DEVICES 901 Thompson Pl., P.O. Box 3453, Sunnyvale, CA 94088, USA TEL: (408) 732-2400 • TWX: 910-339-9280 • TELEX: 34-6306 • TOLL FREE: (800) 538-8450

© 1988 Advanced Micro Devices, Inc. Printed in U.S.A. AIS-WCP-20M-01/88-0

**Bus Interface Products**

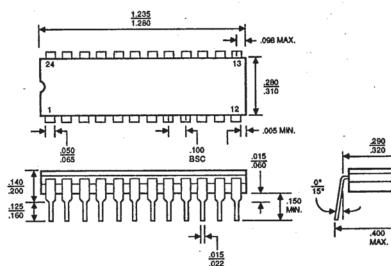

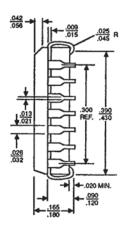

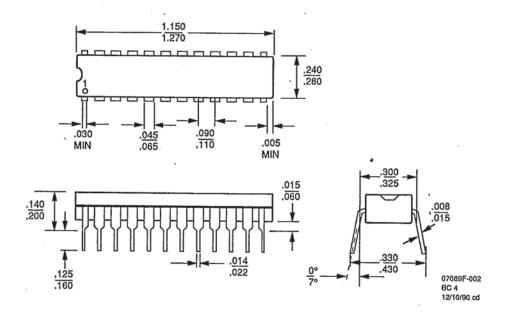

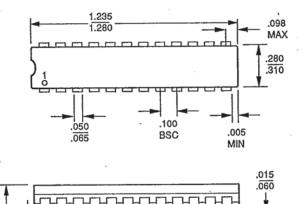

PD3024 24-Pin 300-mil Plastic SKINNYDIP

Note:

For reference only. All dimensions measured in inches. BSC is an ANSI standard for Basic Space Centering.

T-90-20

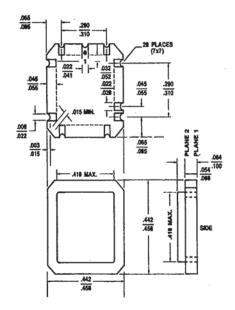

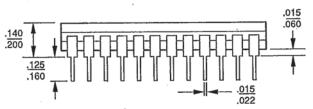

# CD3024 24-Pin 300-mil Ceramic SKINNYDIP

06850C

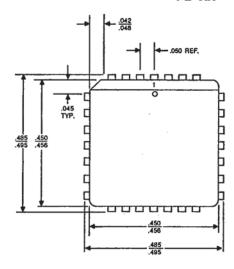

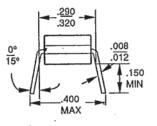

PL 028 28-Pin Plastic Leaded Chip Carrier

**Bus Interface Products**

T-90-20

SO 024 24-Pin Plastic Small Outline Package