# PM5320

# **ARROW 155**

# ASSP Telecom Standard Product Data Sheet

Released

Issue No. 3: December 2005

| Issue<br>No. | Issue<br>Date    | Details of Change                                                                                                                                                                |

|--------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3            | December<br>2005 | Updated ordering information including RoHS-compliant device details.                                                                                                            |

| 2            | July 2004        | Section 6                                                                                                                                                                        |

|              |                  | Pin numbers added to connector description.                                                                                                                                      |

|              |                  | Section 7                                                                                                                                                                        |

|              |                  | Description of overhead byte access corrected for both transmit and receive STS-1E section and line blocks. Section and line DCC are not accessible from the PDH overhead ports. |

|              |                  | JTAG description removed and reference to JTAG App Note included instead.                                                                                                        |

|              |                  | Section 9                                                                                                                                                                        |

|              |                  | Power numbers added from Characterization Report.                                                                                                                                |

|              |                  | Section 13.8                                                                                                                                                                     |

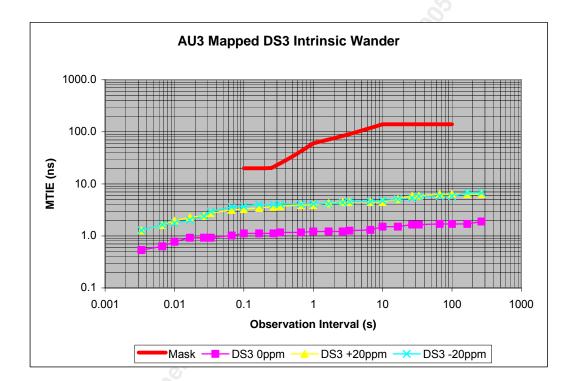

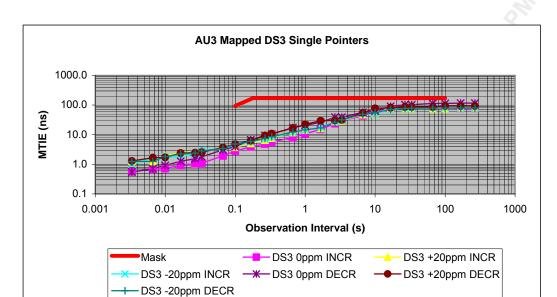

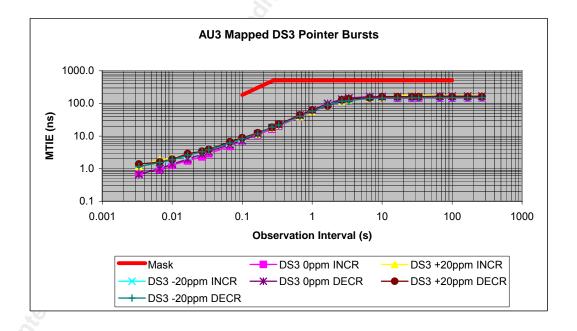

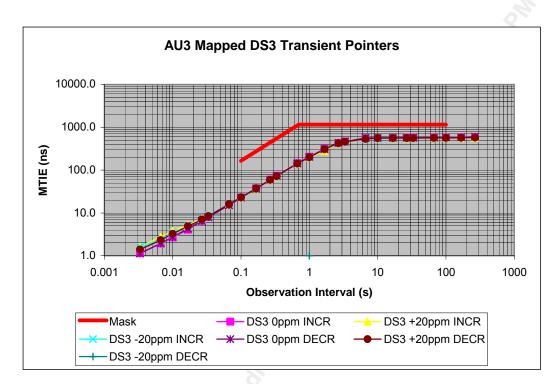

|              |                  | Jitter numbers added. MTIE graphs included.                                                                                                                                      |

| 1            | May 2003         | Document created                                                                                                                                                                 |

## **Table of Contents**

| lat | ole of Co | ontents  |                                       | 3  |

|-----|-----------|----------|---------------------------------------|----|

| Lis | t of Figu | ıres     |                                       | 8  |

| Lis | t of Tab  | les      |                                       | 11 |

| 1   | Refere    | ences    |                                       | 13 |

|     | 1.1       |          | al                                    |    |

|     | 1.2       | Protoco  | lo                                    | 13 |

|     | 1.3       |          | aneous                                |    |

| 2   |           |          |                                       |    |

| 3   |           |          |                                       |    |

| 4   |           |          |                                       |    |

| 5   | Overvi    |          |                                       |    |

|     | 5.1       |          | Diagram                               |    |

|     | 5.2       | Interfac | ces                                   |    |

|     |           | 5.2.1    | Serial Line Side                      |    |

|     |           | 5.2.2    | SONET/SDH Overhead                    |    |

|     |           | 5.2.3    | Ring Control Port                     |    |

|     |           | 5.2.4    | DS3/E3/STS-1E Overhead                | 27 |

|     |           | 5.2.5    | DS3/E3/STS-1E Serial                  |    |

|     |           | 5.2.6    | Parallel TelecomBus                   | 28 |

|     |           | 5.2.7    | Microprocessor                        |    |

|     |           | 5.2.8    | JTAG                                  |    |

|     | 5.3       | Modes    | of Operation                          |    |

|     |           | 5.3.1    | OC-3 Mode                             | 29 |

|     |           | 5.3.2    | DS3/E3/STS-1E Mapper Mode             |    |

|     | 5.4       | Datapa   | ıth                                   |    |

|     |           | 5.4.1    | SONET/SDH Only Mode                   | 30 |

|     |           | 5.4.2    | Receive STSI Datapath Configurations  | 31 |

|     |           | 5.4.3    | Transmit STSI Datapath Configurations |    |

|     |           | 5.4.4    | Loopbacks                             | 32 |

| 6   | Pin De    | •        |                                       |    |

|     | 6.1       |          | I TelecomBus Transmit Interface       |    |

|     | 6.2       | Paralle  | I TelecomBus Receive Interface        | 35 |

|     | 6.3       | Serial L | Line Interface                        | 36 |

|   | 6.4      | Serial [ | DS3/E3/STS-1E Interface                         | 37 |

|---|----------|----------|-------------------------------------------------|----|

|   | 6.5      | DS3/E    | 3/STS-1E Overhead Interface                     | 40 |

|   | 6.6      | SONE     | T/SDH Overhead Interface                        | 43 |

|   | 6.7      | Ring C   | ontrol Port                                     | 49 |

|   | 6.8      | Microp   | rocessor Interface                              | 50 |

|   | 6.9      | JTAG 8   | & Scan Interface                                | 51 |

|   | 6.10     | Power    | and Ground                                      | 51 |

| 7 | Function | onal Des | cription                                        | 53 |

|   | 7.1      | Data a   | nd Clock Recovery Unit (DCRU622)                | 53 |

|   | 7.2      | SONE     | T Frame and Byte Aligner (SFBA)                 | 54 |

|   | 7.3      | Receiv   | re Regenerator and Multiplexer Processor (RRMP) | 54 |

|   | 7.4      | Receiv   | re Trail Trace Processor (RTTP)                 | 57 |

|   | 7.5      | Receiv   | re High Order Path Processor (RHPP)             | 58 |

|   |          | 7.5.1    | Pointer Interpreter                             | 58 |

|   |          | 7.5.2    | Concatenation Pointer Interpreter State Machine | 61 |

|   |          | 7.5.3    | Error Monitoring                                | 63 |

|   | 7.6      | SONE     | T/SDH Bit Error Rate Monitor (SBER)             | 66 |

|   | 7.7      | SONE     | T/SDH Alarm Reporting Controller (SARC)         | 66 |

|   | 7.8      | SONE     | T/SDH Virtual Container Aligner (SVCA)          | 67 |

|   |          | 7.8.1    | TU3 Termination                                 | 67 |

|   |          | 7.8.2    | Elastic Store                                   | 67 |

|   |          | 7.8.3    | Pointer Generator                               | 67 |

|   | 7.9      | SONE     | T Time Slot Interchange (STSI)                  | 70 |

|   | 7.10     | Drop Te  | elecomBus Interface                             | 70 |

|   | 7.11     | Add Te   | elecomBus Interface                             | 70 |

|   | 7.12     | DS3/E    | 3 Desynchronizer (D3E3MD)                       | 70 |

|   |          | 7.12.1   | FIFO                                            | 71 |

|   |          | 7.12.2   | Digital PLL                                     | 71 |

|   |          | 7.12.3   | Transfer Function                               | 71 |

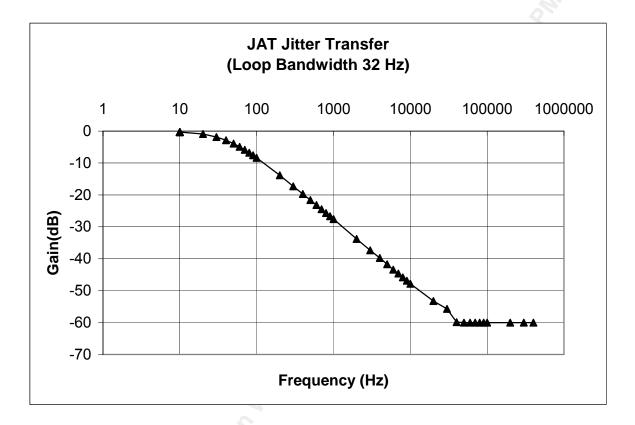

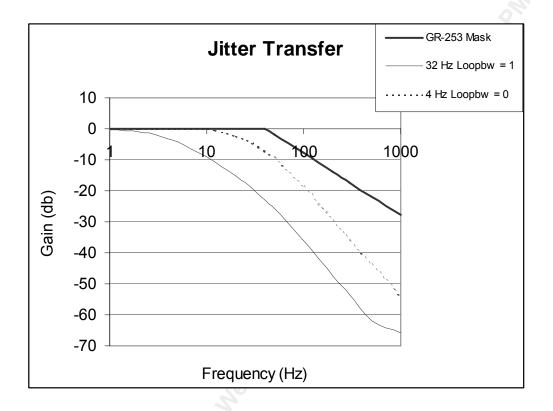

|   | 7.13     | DS3/E    | 3/STS-1E Jitter Attenuator (JAT)                | 72 |

|   |          | 7.13.1   | Digital PLL                                     | 72 |

|   |          | 7.13.2   | FIFO                                            | 72 |

|   |          | 7.13.3   | Transfer Function                               | 72 |

|   | 7.14     | DS3 Fr   | ramer                                           | 73 |

|   | 7.15     | E3 Fra   | mer                                             | 75 |

|      | 7.15.1   | In G.832 E3 Format, the E3-FRMR Extracts:    | 76 |

|------|----------|----------------------------------------------|----|

|      | 7.15.2   | In G.751 E3 Mode, the E3-FRMR Extracts:      | 76 |

| 7.16 | STS-1E   | Receive Section Overhead Processor (RSOP)    | 77 |

|      | 7.16.1   | Framer                                       | 77 |

|      | 7.16.2   | Descramble                                   | 78 |

|      |          | Data Link Extract                            |    |

|      |          | Error Monitor                                |    |

|      | 7.16.5   | Loss of Signal                               | 78 |

|      | 7.16.6   | Loss of Frame                                | 79 |

| 7.17 | STS-1E   | Receive Line Overhead Processor (RLOP)       | 79 |

|      |          | Line RDI Detect                              |    |

|      | 7.17.2   | Line AIS Detect                              | 79 |

|      |          | Data Link Extract Block                      |    |

|      |          | Error Monitor Block                          |    |

| 7.18 | STS-1E   | Bit Error Monitor (RASE)                     | 80 |

|      | 7.18.1   | Bit Error Rate Monitor                       | 80 |

|      | 7.18.2   | Synchronization Status Extraction            | 81 |

| 7.19 | STS-1E   | Receive Path Overhead Processor (RPOP)       | 81 |

|      | 7.19.1   | Pointer Interpreter                          | 81 |

|      | 7.19.2   | SPE Timing                                   | 84 |

|      | 7.19.3   | Error Monitor                                | 84 |

| 7.20 | STS-1E   | SONET/SDH Path Aligner                       | 85 |

| 7.21 | Perform  | nance Monitor Accumulator (PMON)             | 85 |

| 7.22 | Bit-Orie | nted Code Detector (RBOC)                    | 86 |

| 7.23 | Facility | Data Link Receiver (RDLC)                    | 86 |

| 7.24 | Pseudo   | -Random Sequence Generator/Detector (PRGD)   | 87 |

| 7.25 | JAT622   |                                              | 87 |

| 7.26 | Transm   | it Regenerator Multiplexer Processor (TRMP)  | 88 |

| 7.27 | Transm   | it Trail trace Processor (TTTP)              | 92 |

| 7.28 | Transm   | it High Order Path Processor (THPP)          | 92 |

| 7.29 | Transm   | it Add TelecomBus Pointer Interpreter (SHPI) | 94 |

| 7.30 | SONET    | /SDH PRBS Generator and Monitor (PRGM)       | 94 |

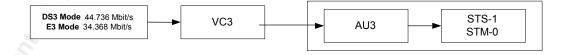

| 7.31 | DS3/E3   | Mapper (D3E3MA)                              | 94 |

|      | 7.31.1   | FIFO                                         | 95 |

|      | 7.31.2   | AIS Generator                                | 95 |

|         | 7.31.3   | Mapper                                       | 95    |

|---------|----------|----------------------------------------------|-------|

|         | 7.31.4   | DPLL                                         | 96    |

|         | 7.31.5   | Transfer Function                            | 96    |

| 7.32    | DS3 Tr   | ansmitter                                    | 97    |

| 7.33    | E3 Tran  | nsmitter                                     | 98    |

|         |          | In G.832 E3 Format, the E3-TRAN:             |       |

|         | 7.33.2   | In G.751 E3 Mode, the E3-TRAN:               | 99    |

| 7.34    | STS-1E   | E Transmit Section Overhead Processor (TSOP) | 99    |

|         |          | Line AIS Insert                              |       |

|         | 7.34.2   | Data Link Insert                             | 99    |

|         | 7.34.3   | BIP-8 Insert                                 | . 100 |

|         | 7.34.4   | Framing and Identity Insert                  | . 100 |

|         | 7.34.5   | Scrambler                                    | . 100 |

| 7.35    | STS-1E   | Transmit Line Overhead Processor (TLOP)      | . 100 |

|         | 7.35.1   | APS Insert                                   | . 100 |

|         | 7.35.2   | Data Link Insert                             | . 100 |

|         | 7.35.3   | Line BIP Calculate                           | . 100 |

|         | 7.35.4   | Line RDI Insert                              | . 101 |

|         | 7.35.5   | Line REI Insert                              | . 101 |

| 7.36    | STS-1E   | Transmit Path Overhead Processor (TPOP)      | . 101 |

|         | 7.36.1   | Pointer Generator                            | . 101 |

|         | 7.36.2   | BIP-8 Calculate                              | . 102 |

|         | 7.36.3   | Path REI Calculate                           | . 102 |

| 7.37    | Bit Orie | ented Code Generator (XBOC)                  | . 102 |

| 7.38    | Trail Tr | ace Buffer (TTB)                             | . 102 |

| 7.39    | Facility | Data Link Transmitter (TDPR)                 | . 103 |

| 7.40    | JTAG T   | est Access Port                              | . 104 |

| 7.41    | Micropi  | rocessor Interface                           | . 104 |

| Functio | nal Timi | ng                                           | . 105 |

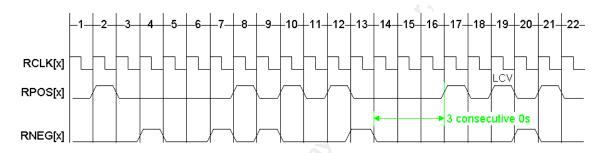

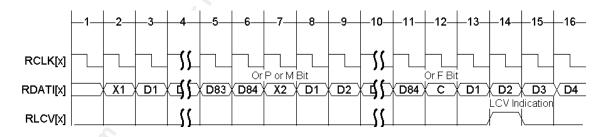

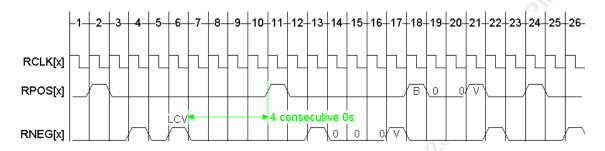

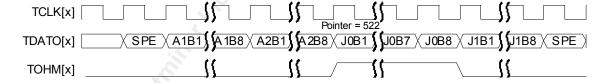

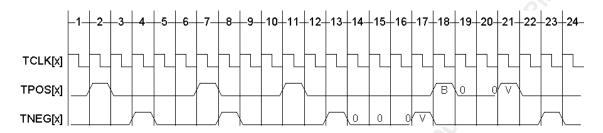

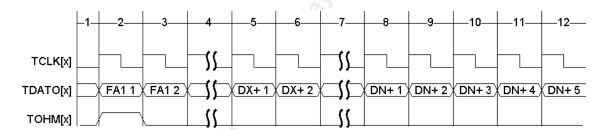

| 8.1     | Receive  | e PDH Serial Formats                         | . 105 |

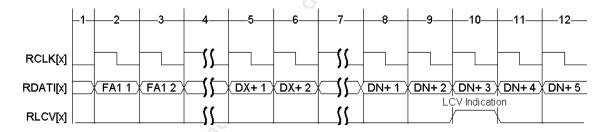

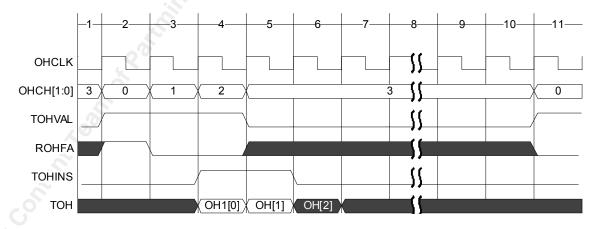

| 8.2     | Receive  | e PDH Overhead Extraction                    | . 107 |

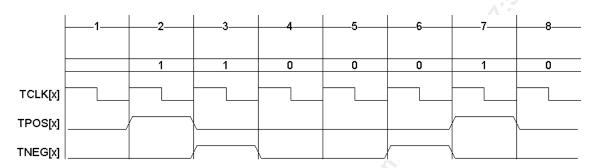

| 8.3     | Transm   | nit PDH Serial Formats                       | . 110 |

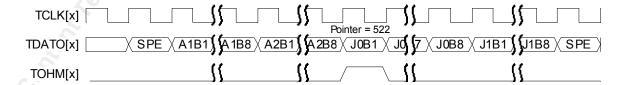

| 8.4     | Transm   | nit PDH Overhead Insertion                   | . 112 |

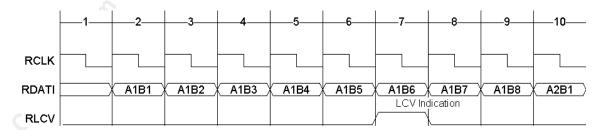

| 8.5     | Add Te   | lecomBus                                     | . 114 |

| 8.6     | Drop Te  | elecomBus                                    | . 115 |

8

|    | 8.7     | Receive SONET Transport Overhead               | . 117 |

|----|---------|------------------------------------------------|-------|

|    | 8.8     | Receive SONET Section and Line DCC             | . 118 |

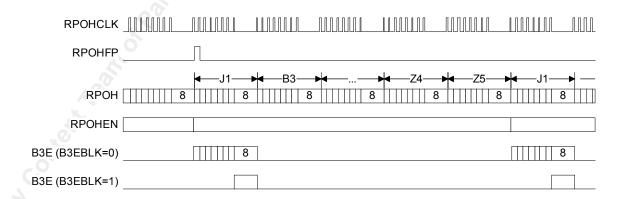

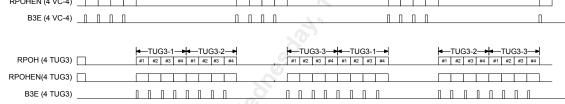

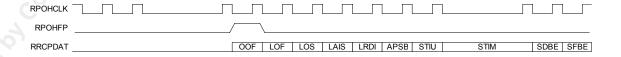

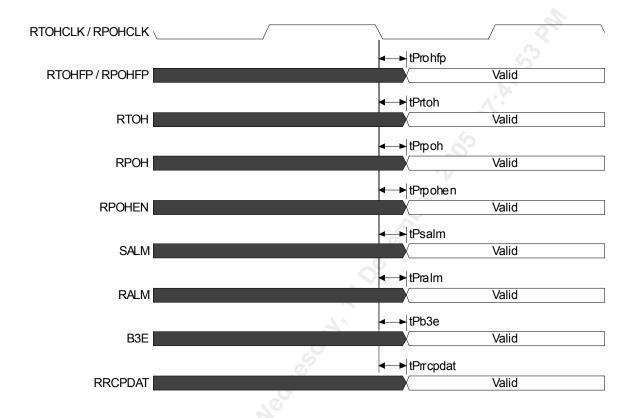

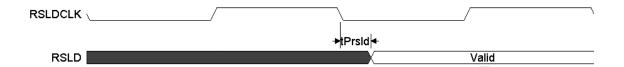

|    | 8.9     | Receive SONET Path Overhead Port               | . 119 |

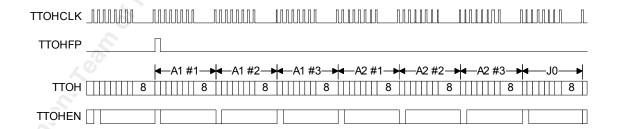

|    | 8.10    | Transmit SONET Transport Overhead              | . 120 |

|    | 8.11    | Transmit SONET Section and Line DCC            | . 121 |

|    | 8.12    | Transmit SONET Path Overhead                   |       |

|    | 8.13    | Receive Ring Control Port                      | . 123 |

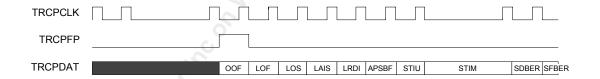

|    | 8.14    | Transmit Ring Control Port                     | . 125 |

| 9  | Power.  |                                                | . 126 |

|    | 9.1     | Normal Operating Conditions                    | . 126 |

|    | 9.2     | Power Consumption                              | . 126 |

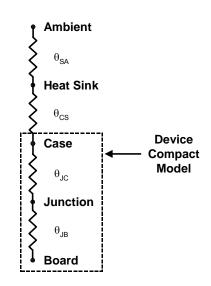

| 10 | Therma  | al Information                                 | . 128 |

|    | 10.1    | Package and Thermals                           |       |

|    |         | e Specification                                |       |

| 12 | DC Cha  | aracteristics                                  | . 131 |

| 13 | AC Tim  | ing Characteristics                            | . 133 |

|    | 13.1    | General                                        | . 133 |

|    | 13.2    | Microprocessor Interface                       | . 133 |

|    | 13.3    | PECL Line Interface Timing                     | . 135 |

|    | 13.4    | PDH Reference Clock Timing                     | . 135 |

|    | 13.5    | TelecomBus Interface Timing                    | . 136 |

|    | 13.6    | SONET/SDH Overhead Interface Timing            | . 139 |

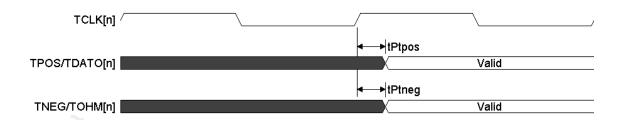

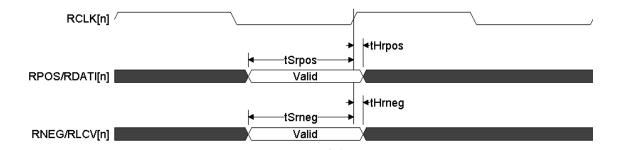

|    | 13.7    | PDH Interface Timing                           | . 142 |

|    | 13.8    | DS3/E3 Serial Interface Timing Characteristics | . 144 |

|    | 13.9    | PDH Overhead Interface Timing                  | . 154 |

|    | 13.10   | JTAG 155                                       |       |

| 14 | Orderin | g Information                                  | . 156 |

# **List of Figures**

| Figure 1  | Four port OC-3 to OC-12 Aggregator                 | 21    |

|-----------|----------------------------------------------------|-------|

| Figure 2  | OC-12/STM-4 Terminal Mux                           | 22    |

|           | OC-3/STM-1 Terminal Mux Example #1                 |       |

| Figure 4  | OC-3/STM-1 Terminal Mux Example #2                 | 23    |

| Figure 5  | CPE ADM – No Equipment Protection                  | 24    |

| Figure 6  | CPE ADM – Fully Redundant                          | 25    |

| -         | Block Diagram                                      |       |

| Figure 8  | STSI Datapaths                                     | 30    |

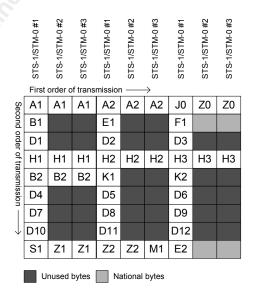

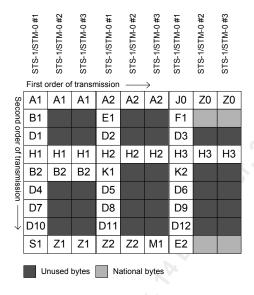

| Figure 9  | STS-3 (STM-1) on RTOH                              | 56    |

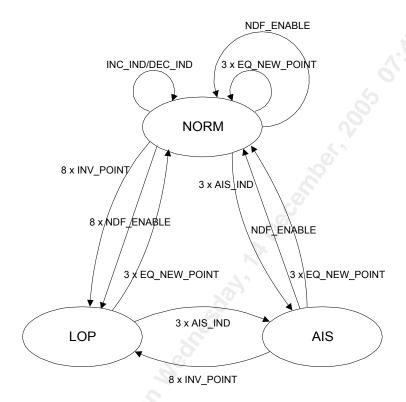

| Figure 10 | Pointer Interpretation State Diagram               | 59    |

| Figure 11 | Concatenation Pointer Interpretation State Diagram | 62    |

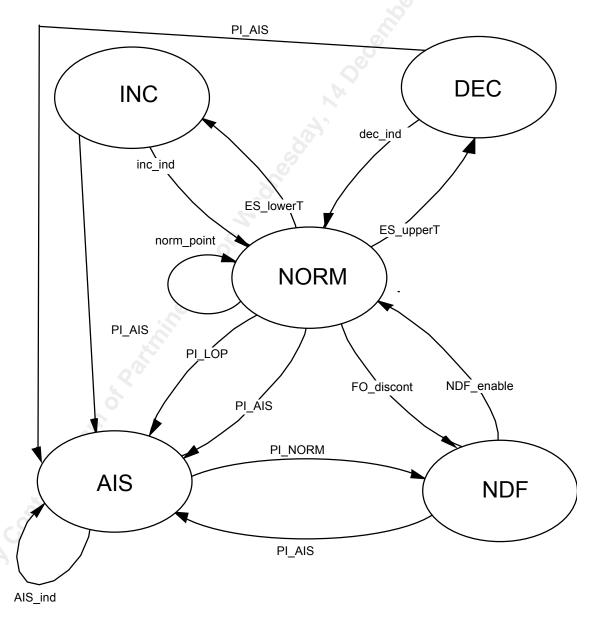

| Figure 12 | Pointer Generation State Diagram                   | 68    |

| Figure 13 | Typical JAT Jitter Transfer Function               | 73    |

| Figure 14 | Pointer Interpretation State Diagram               | 82    |

|           | STS-3 (STM-1) On TTOH                              |       |

| Figure 16 | Mapping Structure                                  | 95    |

| Figure 17 | Typical D3E3MA Jitter Transfer                     | 97    |

| Figure 18 | Receive Bipolar DS3 Stream                         | . 105 |

| Figure 19 | Receive Unipolar DS3 Stream                        | . 105 |

| Figure 20 | Receive Bipolar E3 Stream                          | . 106 |

| Figure 21 | Receive Unipolar E3 Stream                         | . 106 |

| Figure 22 | Receive Unipolar STS-1E Stream                     | . 106 |

| Figure 23 | Receive Overhead Extraction Structure              | . 107 |

| Figure 24 | Transmit Bipolar DS3 Stream                        | . 110 |

| Figure 25 | Transmit Unipolar DS3 Stream                       | . 110 |

| Figure 26 | Transmit Bipolar E3 Stream                         | . 111 |

| Figure 27 | Transmit Unipolar E3 Stream                        | . 111 |

| Figure 28 | Transmit Unipolar STS-1E Stream                    | . 111 |

| Figure 29 | Overhead Insertion                                 | . 112 |

| Figure 30 | Add Parallel TelecomBus Timing                     | . 115 |

| Figure 31 | Drop TelecomBus (J1SQUELCH = 0)                    | . 116 |

| Figure 32 | Drop TelecomBus (J1SQUELCH = 1)                    | . 117 |

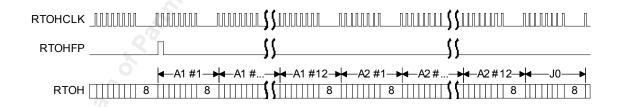

| Figure 33 | RTOH Output Timing (OC-12 Mode)                    | . 117 |

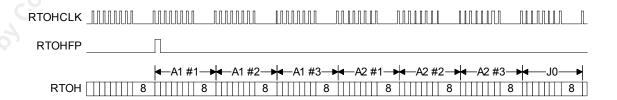

| Figure 34 | RTOH Output Timing (OC-3 Mode)                                    | 117 |

|-----------|-------------------------------------------------------------------|-----|

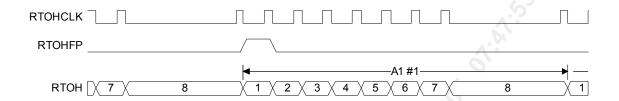

| Figure 35 | RTOH and RTOHFP Output Timing                                     | 118 |

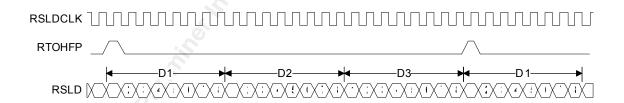

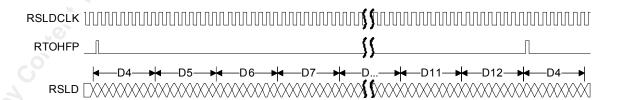

|           | RTOHFP and RSLD output timing (RSLDSEL = 0)                       |     |

| Figure 37 | RTOHFP and RSLD Output Timing (RSLDSEL = 1)                       | 118 |

| Figure 38 | RPOH Output Timing                                                | 119 |

| Figure 39 | RPOH STS-1/STM-0 Time Slots Output Timing                         | 120 |

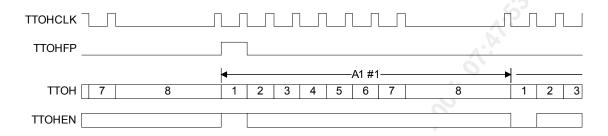

| Figure 40 | TTOH and TTOHEN Input Timing                                      | 120 |

| Figure 41 | TTOH and TTOHFP Input Timing                                      | 121 |

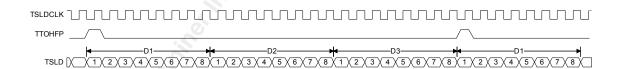

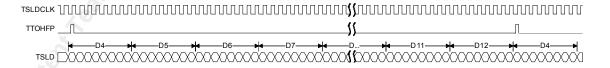

| Figure 42 | TTOHFP and TSLD Output Timing (TSLDSEL = 0)                       | 121 |

| Figure 43 | TTOHFP and TSLD Output Timing (TSLDSEL = 1)                       | 121 |

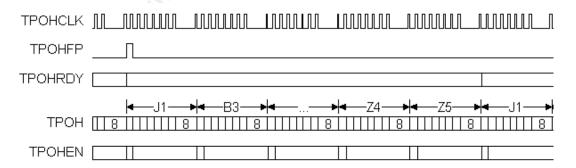

| Figure 44 | TPOH Input Timing                                                 | 122 |

| Figure 45 | TPOH STS-1/STM-0 Time Slots Input Timing                          | 123 |

| -         | RRCP Output Timing                                                |     |

|           | TRCP Input Timing                                                 |     |

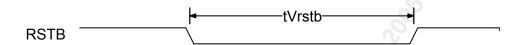

| Figure 48 | RSTB Timing                                                       | 133 |

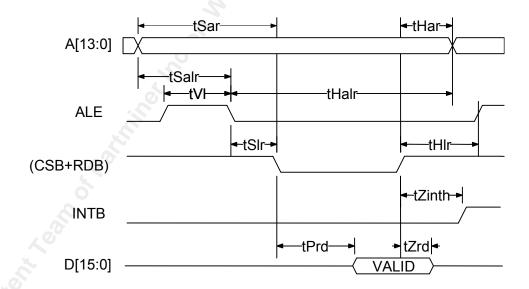

| Figure 49 | Microprocessor Interface Read Timing                              | 133 |

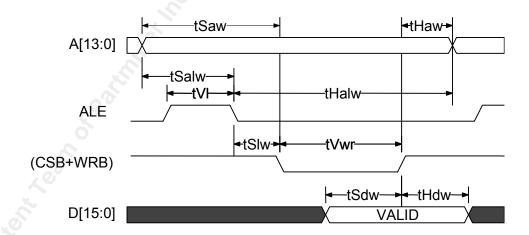

| Figure 50 | Microprocessor Interface Write Timing                             | 134 |

| Figure 51 | Drop TelecomBus Interface Timing                                  | 136 |

| Figure 52 | Add TelecomBus Interface Timing                                   | 137 |

| Figure 53 | Transmit SONET/SDH Overhead Interface Timing                      | 139 |

| Figure 54 | Transmit SONET/SDH Overhead Interface Timing                      | 140 |

| Figure 55 | Transmit Ring Control Input Timing Diagram                        | 140 |

| Figure 56 | Receive SONET/SDH Overhead RTOH/RPOH Interface Timing             | 140 |

| Figure 57 | Receive SONET/SDH Overhead RSLDCLK Interface Timing               | 142 |

| Figure 58 | Transmit PDH Interface Timing                                     | 142 |

| Figure 59 | Receive PDH Interface Timing                                      | 143 |

| Figure 60 | DS3 Mapping Wander MTIE                                           | 145 |

| Figure 61 | DS3 Pointer Wander MTIE (Single Pointer Adjustment)               | 146 |

| Figure 62 | DS3 Pointer Wander MTIE (Burst of 3 Pointer Adjustments)          | 146 |

|           | DS3 Pointer Wander MTIE (Phase Transient Pointer Adjustment       | 147 |

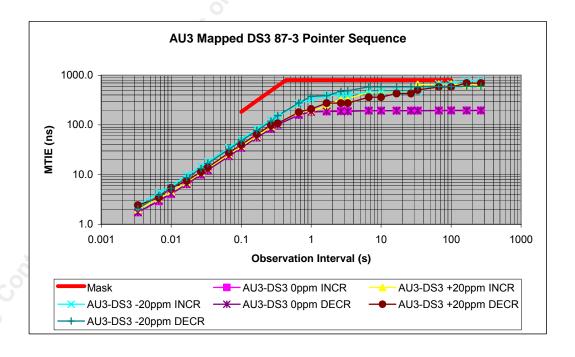

| Figure 64 | DS3 Pointer Wander MTIE (87-3 Pointer Sequence)                   | 147 |

| Figure 65 | DS3 Pointer Wander MTIE (Periodic Pointer Adjustments)            | 148 |

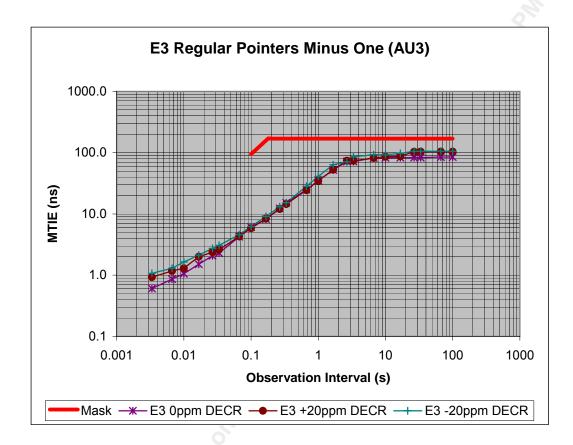

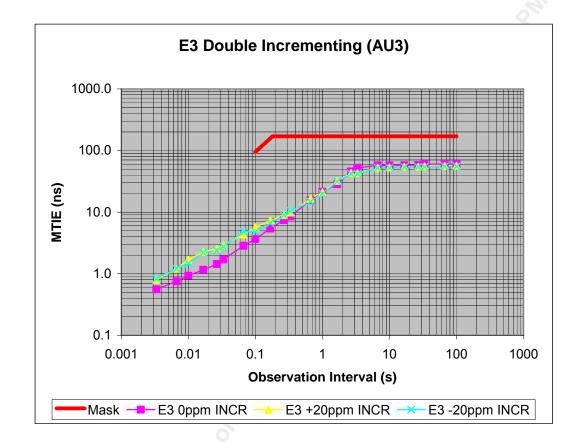

| Figure 66 | E3 Mapping Wander MTIE                                            | 149 |

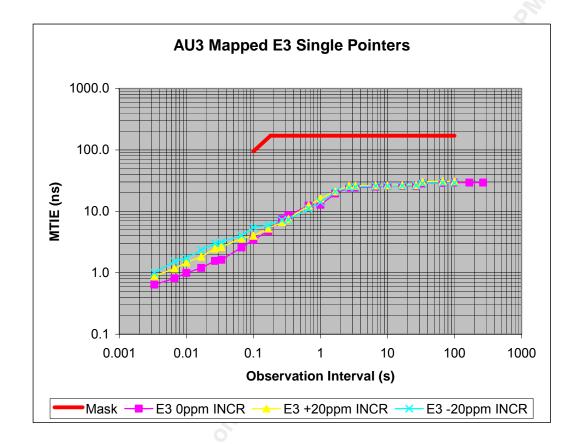

| Figure 67 | E3 Pointer Wander MTIE (Single Pointers of opposite polarity)     | 150 |

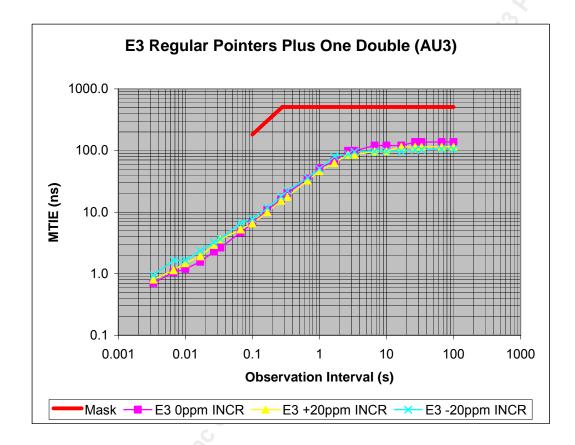

| Figure 68 | E3 Pointer Wander MTIE (Regular Pointers plus one double pointer) | 151 |

## ARROW 155 ASSP Telecom Standard Product Data Sheet Released

| Figure 69 | E3 Pointer Wander MTIE (Regular Pointers with one missing     |     |

|-----------|---------------------------------------------------------------|-----|

| pointe    | r)                                                            | 152 |

| Figure 70 | E3 Pointer Wander MTIE (Double pointers of opposite polarity) | 153 |

| Figure 71 | PDH Overhead Insertion & Extraction Interface Timing          | 154 |

## **List of Tables**

| Table 1  | Definitions                                           | 18    |

|----------|-------------------------------------------------------|-------|

| Table 2  | Pin Type Definition                                   | 33    |

|          | RRMP Framing Algorithms                               |       |

| Table 4  | PLM-P, UNEQ-P and PDI-P Defects Declaration           | 64    |

| Table 5  | Expected PDI Defect Based on PDI and PDI Range Values | 65    |

| Table 6  | Pointer Interpreter Event (Indications) Description   | 82    |

| Table 7  | Pointer Interpreter Transition Description            | 83    |

| Table 8  | Maximum Line REI Errors per Transmit Frame            | 88    |

| Table 9  | TOH Insertion Priority                                | 89    |

| Table 10 | Z0/National Growth Bytes Definition for Row #1        | 91    |

| Table 11 | Path overhead byte source priority                    |       |

| Table 12 | DS3 Receive Overhead Bits                             | . 107 |

| Table 13 | G.751 E3 Receive Overhead Bits                        | . 108 |

| Table 14 | G.832 E3 Receive Overhead Bits                        | . 108 |

| Table 15 | STS-1E Receive Overhead Bits                          | . 109 |

| Table 16 | DS3 Transmit Overhead Bits                            | . 113 |

| Table 17 | G.751 E3 Transmit Overhead Bits                       | . 113 |

| Table 18 | G.832 E3 Transmit Overhead Bits                       | . 113 |

| Table 19 | STS-1E Transmit Overhead Bits                         | . 114 |

| Table 20 | Ring Control Port Bit Definition                      | . 124 |

| Table 21 | Normal Operating Voltages for 0.18 um CMOS            | . 126 |

| Table 22 | Power Requirements                                    | . 126 |

| Table 23 | Conditions for Power Requirements                     | . 127 |

| Table 24 | Package and Thermal Information                       | . 128 |

| Table 25 | Device Compact Model <sup>3</sup>                     | . 128 |

| Table 26 | Heat Sink Requirements                                | . 128 |

| Table 27 | DC Characteristics for Pins                           | . 131 |

| Table 28 | DC Characteristics                                    | . 131 |

| Table 29 | RSTB Timing (Figure 70)                               | . 133 |

| Table 30 | Microprocessor Interface Read Access (Figure 49)      | 133   |

| Table 31 | Microprocessor Interface Write Access (Figure 50)     | 134   |

| Table 32 | PECL Line Interface Timing                            | . 135 |

| Table 33 | PDH Reference Clock Timing                            | . 135 |

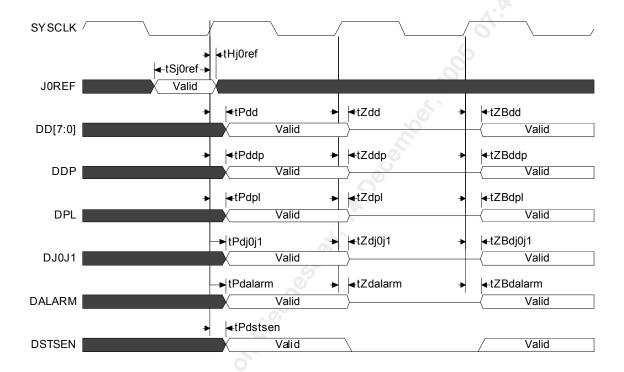

| Table 34 | Drop TelecomBus Interface (Figure 51)                       | 136 |

|----------|-------------------------------------------------------------|-----|

| Table 35 | Add TelecomBus Interface (Figure 52)                        | 138 |

| Table 36 | Transmit SONET/SDH Overhead TTOH/TPOH Interface (Figure 53) | 139 |

| Table 37 | Transmit SONET/SDH Overhead TSLDCLK Interface (Figure 54)   | 140 |

| Table 38 | Transmit Ring Control Input Timing                          | 140 |

| Table 39 | Receive SONET/SDH Overhead RTOH/RPOH Interface (Figure 55)  | 141 |

| Table 40 | Receive SONET/SDH Overhead RSLDCLK Interface (Figure 57)    | 142 |

| Table 41 | Transmit PDH Interface (Figure 58)                          | 142 |

| Table 42 | Receive PDH Interface (Figure 59)                           | 143 |

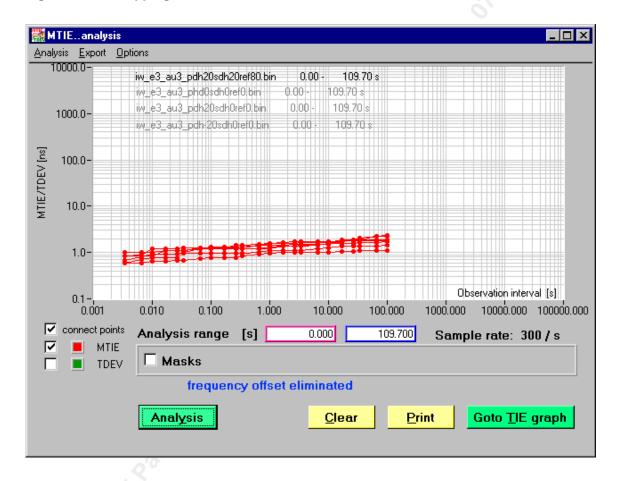

| Table 43 | DS3 Serial Interface Timing Characteristics                 | 144 |

| Table 44 | E3 Serial Interface Timing Characteristics                  | 148 |

| Table 45 | PDH Overhead Insertion & Extraction Interface (Figure 71)   | 154 |

| Table 46 | JTAG Port Interface                                         | 155 |

| Table 47 | Ordering Information                                        | 156 |

## 1 References

#### 1.1 Thermal

- 1. Electronic Industries Association. *Methodology for the Thermal Measurement of Component Packages (Single Semiconductor Device): EIA/JESD51*. December 1995.

- 2. Electronic Industries Alliance 1999. *Integrated Circuit Thermal Test Method Environmental Conditions Junction-to-Board: JESD51-8*. October 1999.

- 3. Telcordia Technologies. *Network Equipment-Building System (NEBS) Requirements: Physical Protection: Telcordia Technologies Generic Requirements GR-63-CORE.* Issue 1. October 1995.

- 4. SEMI (Semiconductor Equipment and Materials International). SEMI G30-88 Test Method for Junction-to-Case Thermal Resistance Measurements of Ceramic Packages. 1988.

#### 1.2 Protocol

- 1. ANSI, Digital Hierarchy Synchronous DS3 Format Specifications, T1.103-1993.

- 2. ANSI, Synchronous Optical Network (SONET) Basic Description including Multiplex Structure, Rates, and Formats, T1.105-1995.

- 3. ANSI, *Synchronous Optical Network (SONET) Payload Mappings*, T1.105.02, October 27, 1995.

- 4. ANSI, Digital Hierarchy Formats Specifications, T1.107-1995.

- 5. ANSI, Digital Hierarchy Supplement to Formats Specifications (DS3 Format Applications), T1.107a-1990.

- 6. ANSI, Digital Hierarchy Layer 1 In-Service Digital Transmission Performance Monitoring, T1.231-1997.

- 7. ANSI, Customer Installation—to-Network DS3 Metallic Interface Specification, T1.404-1994.

- 8. AT&T, Requirements For Interfacing Digital Terminal Equipment To Services Employing The Extended Superframe Format, TR 54016, September 1989.

- 9. AT&T, Accunet T1.5 Service Description and Interface Specification, TR 62411, December 1990.

- 10. Bell Communications Research, *Asynchronous Digital Multiplexes Requirements and Objectives*, TR-TSY-000009, Issue 1, May 1986.

- 11. Bell Communications Research, *Alarm Indication Signal Requirements and Objectives*, TA-TSY-000191, Issue 1, May 1986.

- 12. Bell Communications Research, *Wideband and Broadband Digital Cross-Connect Systems Generic Criteria*, TR-NWT-000233, Issue 3, November 1993.

- 13. Bell Communications Research, *Digital Interface Between The SLC®96 Digital Loop Carrier System And A Local Digital Switch*, TR-TSY-000008, Issue 2, August 1987.

- 14. Bell Communications Research, *Integrated Digital Loop Carrier Generic Requirements, Objectives, and Interface*, TR-TSY-000303, Issue 2, December 1992.

- 15. Bell Communications Research, *Transport Systems Generic Requirements (TSGR): Common Requirement*, TR-TSY-000499, Issue 5, December 1993.

- Bell Communications Research OTGR: Network Maintenance Transport Surveillance -Generic Digital Transmission Surveillance, TR-TSY-000820, Section 5.1, Issue 1, June 1990

- 17. ETSI, Generic Functional Requirements for Synchronous Digital Hierarchy (SDH) Equipment, ETS 300 417-1-1, January 1996.

- 18. ETSI, ISDN Primary Rate User-Network Interface Specification and Test Principles, ETS 300 011, 1992.

- 19. IEEE. 1149.1b-1994 IEEE Standard Test Access Port and Boundary-Scan Architecture. Sept 22, 1994

- 20. ITU-T, *Physical/Electrical Characteristics of Hierarchical Digital Interfaces*, Recommendation G.703, 1991.

- 21. ITU-T, Synchronous Frame Structures Used at Primary Hierarchical Levels, Recommendation G.704, July 1995.

- 22. ITU-T, Frame Alignment and CRC Procedures Relating to G704 Frame Structures, Recommendation G706, 1991.

- 23. ITU-T, *Network Node Interface For The Synchronous Digital Hierarchy*, Recommendation G.707, 1996.

- 24. ITU-T, Second Order Digital Multiplex Equipment Operating at 6312 kbit/s and Multiplexing Three Tributaries at 2048 kbit/s, Recommendation G.747, 1988.

- 25. ITU-T, Loss of Signal (LOS) and Alarm Indication Signal (AIS) Defect Detection and Clearance Criteria, Recommendation G.775, November 1994.

- 26. ITU-T, Structure of Recommendations on Equipment for the Synchronous Design Hierarchy (SDH), Recommendation G781, January 1994.

- 27. ITU-T, Characteristics of Synchronous Digital Hierarchy (SDH) Equipment Functional Blocks, Recommendation G.783, October 2000.

- 28. ITU-T, Characteristics of Synchronous Digital Hierarchy (SDH) Equipment Functional Blocks, Recommendation G.783 Amendment 1, June 2002.

- 29. ITU-T, *The Control of Jitter and Wander within Digital Networks which are Based on the 2048 kbit/s Hierarchy*, Recommendation G.823, March 1994.

- 30. ITU-T, Error Performance Measuring Equipment Operating at the Primary Rate and Above, Recommendation O.151, October 1992.

- 31. ITU-T, *ISDN User-Network Interface Data Link Layer Specification*, Recommendation Q.921, March 1993.

- 32. International Organization for Standardization, *High-Level Data Link Control procedures Frame Structure*, ISO 3309:1984.

- 33. Telcordia Technologies, *Synchronous Optical Network (SONET) Transport Systems: Common Generic Criteria*, GR-253-CORE, Issue 3, September 2000.

- 34. Telcordia Technologies, *SONET Add-Drop Multiplexer (SONET ADM) Generic Criteria*, GR-496-CORE, Issue 1, December 1998.

- 35. Telcordia Technologies. *Network Equipment-Building System (NEBS) Requirements: Physical Protection:* GR-63-CORE, Issue 1. October 1995.

- 36. TTC, Frame Structures on Primary and Secondary Hierarchical Digital Interfaces, Standard JT-G704, 1995.

- 37. TTC, Frame Synchronization and CRC Procedure, Standard JT-G706.

- 38. Nippon Telegraph and Telephone Corporation, *Technical Reference for High-Speed Digital Leased Circuit Services*, Third Edition, 1990.

### 1.3 Miscellaneous

- 1. PMC-Sierra, Inc., *Enhanced-LVDS (ELVDS) Electrical Specification*, PMC-2001507, Issue 1, 2002.

- 2. PMC-Sierra, Inc., *Extended SONET/SDH Serial Interface (ESSI) Specification*, PMC-2010653, Issue 1, 2001.

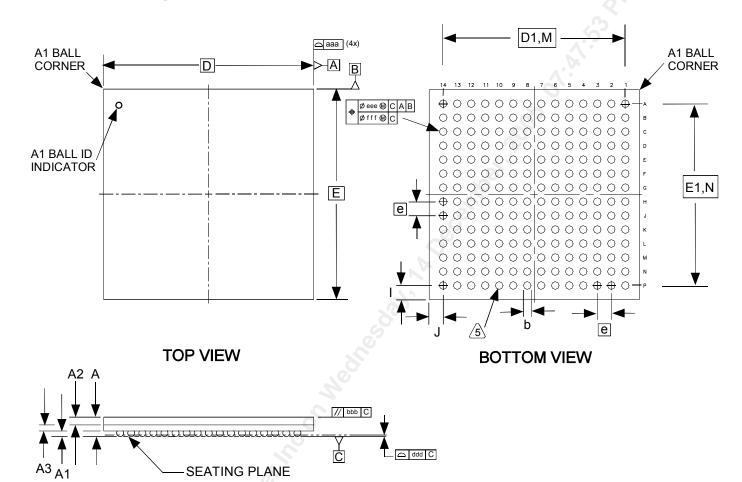

- 3. PMC-Sierra, Inc., ARROW 155 Ball Map File, PMC-2031854

- 4. PMC-Sierra, Inc., ARROW 155 ASSP Telecom Standard Product Data Sheet Register Description, PMC-2031892, Issue 1, 2004

- 5. PMC-Sierra, Inc., ARROW 155 Short Form Data Sheet, PMC-2030735

- 6. PMC-Sierra, Inc., *PM5319/PM5320 ARROW 622/155 Hardware Design Guide*, PMC-2030859, Issue 2, 2004

- 7. PMC-Sierra, Inc., PM5319/PM5320 ARROW 622/155 Operation and Configuration Guide, PMC-2030860, Issue 2, 2004

## 2 Patents

The technology discussed in this document is protected by the following patents:

- Canada 2,159,763

- Canada 2,161,921

- Canada 2,245,760

- USA 6,052,073

- USA 5,606,563

- USA 5,640,398

- USA 6,703,950

- USA 6,744,787

## 3 Definitions

**Table 1 Definitions**

| Term    | Definition                                        |

|---------|---------------------------------------------------|

| AIS     | Alarm Indication Signal                           |

| BER     | Bit Error Rate                                    |

| BIP     | Byte Interleaved Parity                           |

| COFA    | Change of Frame Alignment                         |

| CRC     | Cyclic Redundancy Check                           |

| CSU     | Clock Synthesis Unit                              |

| D3E3MA  | DS3 / E3 TO STS-1/STM-0 Mapper / Synchronizer     |

| D3E3MD  | STS-1/STM-0 TO E3 / DS3 Demapper / Desynchronizer |

| DCC     | Data Communication Channel                        |

| DLL     | Digital Delay Locked Loop                         |

| DS3     | Digital Signal Level 3                            |

| E3 FRMR | ITU-T G.832 E3, G.751 E3 Framer                   |

| E3 TRAN | CCITT G.832 E3, G.751 E3 Transmitter              |

| ERDI    | Enhanced Remote Defect Indication                 |

| ESD     | Electrostatic Discharge                           |

| EXZS    | Excess Zeros                                      |

| FAS     | Framing Alignment Signal                          |

| F-bit   | Framing Bit                                       |

| FCS     | Frame Check Sequence                              |

| FEAC    | Far End Alarm Control                             |

| FEBE    | Far End Block Error                               |

| FERF    | Far End Receive Failure                           |

| FERR    | Framing Bit Error                                 |

| FIFO    | First-In First-Out                                |

| HDLC    | High-level Data Link Layer                        |

| ITU     | International Telecommunications Union            |

| JAT     | Digital Jitter Attenuator                         |

| JTAG    | Joint Test Action Group                           |

| LAIS    | Line AIS also referred to as AIS-L                |

| LCV     | Line Code Violation                               |

| LOF     | Loss of Frame                                     |

| LOH     | Line Overhead                                     |

| LOP     | Loss of Pointer                                   |

| LOS     | Loss of Signal                                    |

| LOT     | Loss of Transition                                |

| LRDI    | Line RDI also referred to as RDI-L                |

| Term    | Definition                                                      |  |  |  |  |  |  |  |

|---------|-----------------------------------------------------------------|--|--|--|--|--|--|--|

| NC      | No Connect, indicates an unused pin                             |  |  |  |  |  |  |  |

| NDF     | New Data Flag                                                   |  |  |  |  |  |  |  |

| NRZ     | Non Return to Zero                                              |  |  |  |  |  |  |  |

| ODL     | Optical Data Link                                               |  |  |  |  |  |  |  |

| OOF     | Out of Frame                                                    |  |  |  |  |  |  |  |

| PERR    | Parity Error                                                    |  |  |  |  |  |  |  |

| PHY     | Physical Layer                                                  |  |  |  |  |  |  |  |

| PLL     | Phase-Locked Loop                                               |  |  |  |  |  |  |  |

| PMDL    | Path Maintenance Data Link                                      |  |  |  |  |  |  |  |

| PMON    | E3/T3 Performance Monitor                                       |  |  |  |  |  |  |  |

| PRGD    | Pseudo Random Sequence Generator/ Detector                      |  |  |  |  |  |  |  |

| PRGM    | Pseudo Random Sequence Generator/Monitor                        |  |  |  |  |  |  |  |

| PSL     | Path Signal Label                                               |  |  |  |  |  |  |  |

| PSLM    | Path Signal Label Mismatch                                      |  |  |  |  |  |  |  |

| RAI     | Receive Alarm Indication                                        |  |  |  |  |  |  |  |

| RBOC    | Bit Oriented Code Detector                                      |  |  |  |  |  |  |  |

| RDI     | Remote Defect Indication                                        |  |  |  |  |  |  |  |

| RDLC    | Data Link Receiver                                              |  |  |  |  |  |  |  |

| RED     | Receive Error Detection                                         |  |  |  |  |  |  |  |

| RHPP    | Receive High Order Path Processor                               |  |  |  |  |  |  |  |

| RRMP    | Receive Regenerator and Multiplexer Section Processor           |  |  |  |  |  |  |  |

| RTTP    | Receive Trail Trace Processor                                   |  |  |  |  |  |  |  |

| SARC    | SONET/SDH Alarm Reporting Controller                            |  |  |  |  |  |  |  |

| SBER    | SONET/SDH Bit Error Monitoring                                  |  |  |  |  |  |  |  |

| SD      | Signal Degrade (alarm)                                          |  |  |  |  |  |  |  |

| SDH     | Synchronous Digital Hierarchy                                   |  |  |  |  |  |  |  |

| SF      | Signal Fail                                                     |  |  |  |  |  |  |  |

| SMDS    | Switched Multi-Megabit Data Service                             |  |  |  |  |  |  |  |

| SOH     | Section Overhead                                                |  |  |  |  |  |  |  |

| SONET   | Synchronous Optical Network                                     |  |  |  |  |  |  |  |

| SPE     | Synchronous Payload Envelope                                    |  |  |  |  |  |  |  |

| SPTB    | SONET/SDH Path Trace Buffer                                     |  |  |  |  |  |  |  |

| STSI    | SONET/SDH Timeslot Interchange                                  |  |  |  |  |  |  |  |

| SVCA    | SONET/SDH Virtual Container Aligner                             |  |  |  |  |  |  |  |

| T3 FRMR | T3 (DS3) Framer                                                 |  |  |  |  |  |  |  |

| T3 TRAN | T3 (DS3) Transmitter                                            |  |  |  |  |  |  |  |

| TAP     | Test Access Port                                                |  |  |  |  |  |  |  |

| TDPR    | Transmit Data Link Controller with Performance Report Interface |  |  |  |  |  |  |  |

| THPP    | Transmit High Order Path Processor                              |  |  |  |  |  |  |  |

| TIM     | Trace Identifier Mismatch                                       |  |  |  |  |  |  |  |

| Term | Definition                                     |

|------|------------------------------------------------|

| TIU  | Trace Identifier Unstable                      |

| TOH  | Transport Overhead                             |

| TRMP | Transmit Regenerator and Multiplexer Processor |

| TTTP | Transmit Trail Trace Processor                 |

| UI   | Unit Interval                                  |

| WAN  | Wide Area Network                              |

| XBOC | Bit-Oriented Code Transmitter                  |

| XOR  | Exclusive OR logic operator                    |

## 4 Applications

This section describes some of the possible ways that the device can be used in a system application.

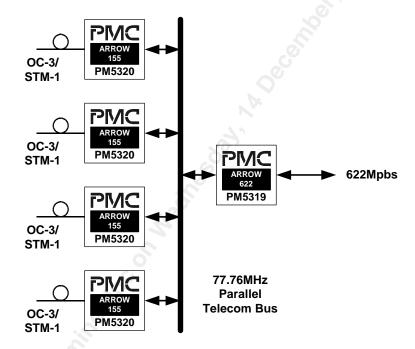

Figure 1 shows the ARROW 155 and the ARROW 622 on a 4x OC-3/STM-1 line card. The 4 ARROW 155 devices interface with the SONET/SDH streams, while the ARROW 622 aggregates these streams into a 622Mbps backplane.

Figure 1 Four port OC-3 to OC-12 Aggregator

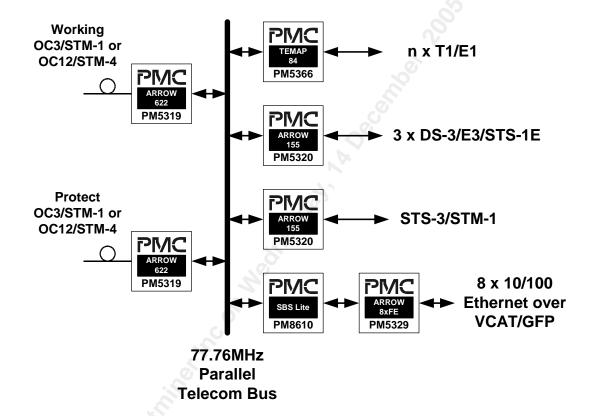

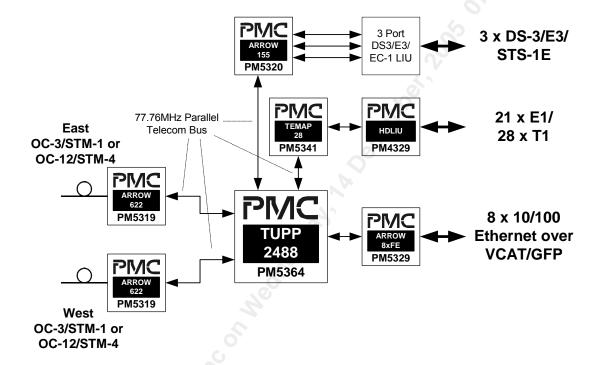

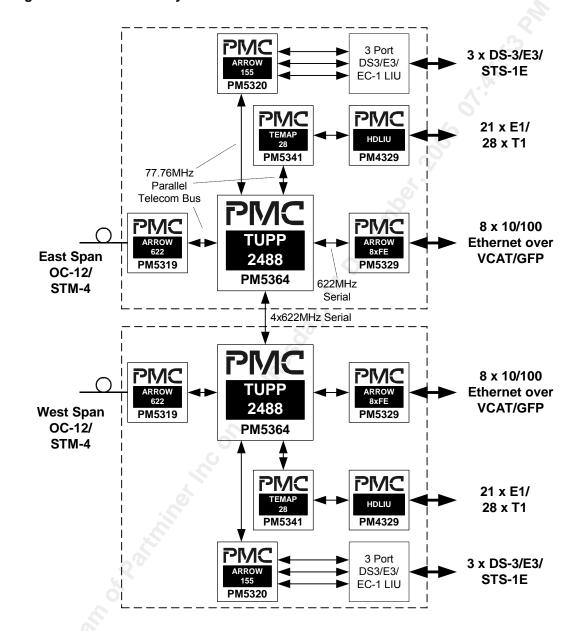

Figure 2 shows an OC-12/STM-4 terminal multiplexer example. The ARROW 622 devices provide the working and protect link to the network. The ARROW 155 can be used to manipulate an OC-3/STM-1 stream or to map/demap up to 3 PDH (DS3/E3/STS-1E) streams. The TEMAP 84 is used to map/demap DS1/E1 streams. The SBS-ARROW 8xFE combination maps Ethernet channels into SONET/SDH payload.

Figure 2 OC-12/STM-4 Terminal Mux

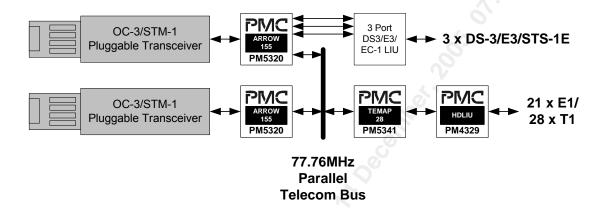

Figure 3 and Figure 4 are both examples of OC-3/STM-1 terminal mutiplexers. They illustrate the different PMC-Sierra device combination that allow the insertion/extraction of PDH streams from SONET/SDH.

Figure 3 OC-3/STM-1 Terminal Mux Example #1

Figure 4 OC-3/STM-1 Terminal Mux Example #2

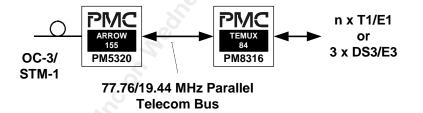

Figure 5 shows the ARROW 622 as part of a small ADM architecture. The ARROW 622 interfaces to the SONET/SDH network, while the ARROW 155 provides access to the PDH streams mapped into SONET/SDH. Figure 6 illustrates a similar application with added equipment protection.

Figure 5 CPE ADM - No Equipment Protection

Figure 6 CPE ADM – Fully Redundant

## 5 Overview

The ARROW 155 device is a single port OC-3 (STM-1) Framer. The ARROW 155 terminates Section, Line, and Path overhead at both the STS-n (AU-4) level and the TU-3 level. On the line side, it incorporates a multi-rate SERDES, allowing it to mate directly to an optics module or connect across a backplane. The system side interface is an 8-bit multi-drop Parallel TelecomBus, allowing multiple devices to share a single bus. The ARROW 155 maps/de-maps up to three channels of DS3/E3 or STS-1E with bi-directional traffic monitoring. The traffic may be multiplexed either into the line or system side interfaces or any combination thereof.

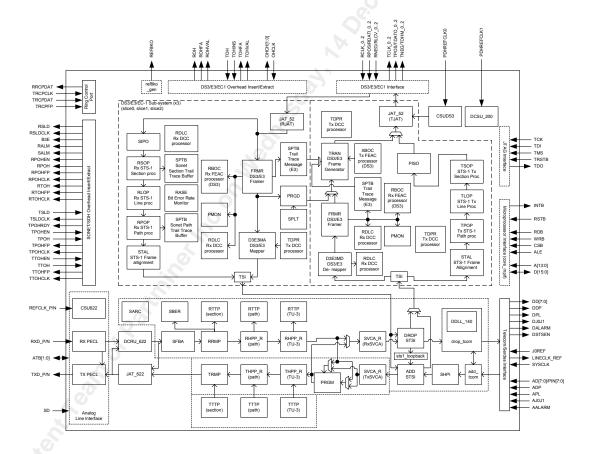

## 5.1 Block Diagram

Figure 7 Block Diagram

#### 5.2 Interfaces

The ARROW 155 has eight distinct interfaces: Serial Line Side, SONET/SDH Overhead, Ring Control Port, DS3/E3/STS-1E Overhead, DS3/E3/STS-1E Serial, Microprocessor Interface, Parallel TelecomBus, and JTAG.

#### 5.2.1 Serial Line Side

The serial line side consists of an AC-coupled PECL transmit pair (TXD\_P, TXD\_N), a PECL receive pair (RXD\_P, RXD\_N), and a PECL reference clock input (REFCLK\_P, REFCLK\_N). The transmit and receive pair operate at 155 Mbit/s. The reference clock input operates at 77.76 MHz or 155.52 MHz.

#### 5.2.2 SONET/SDH Overhead

The ARROW 155 provides full access to all overhead bytes on the STS-3 (STM-1) SONET/SDH datapath. The SONET/SDH overhead port is implemented as four separate interfaces. The receive transport overhead bytes are available on RTOH, RTOHCLK, and RTOHFP signals from the Transport Overhead Processor (RRMP). This interface runs at a nominal 5.184 MHz. The section and line DCC bytes also appear on dedicated pins RSLD and RSLDCLK. The receive path overhead bytes are available on RPOH, RPOHEN, RPOHFP, and RPOHCLK signals from the RHPP blocks. B3E, along with a variety of other alarm signals, are available on RALM and SALM signals from the SARC. This interface runs at a nominal 20.736 MHz.

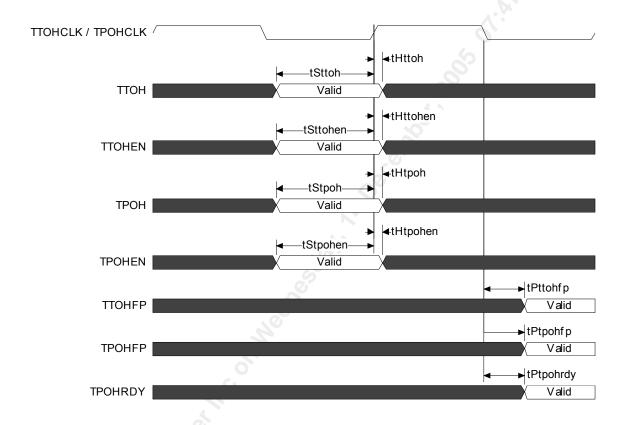

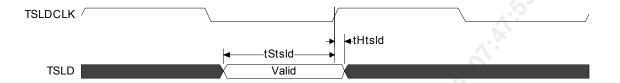

The transmit transport overhead is inserted using TTOH, TTOHEN, TTOHFP, and TTOHCLK. This interface runs at a nominal 5.184 MHz. Section and Line DCC bytes may be inserted using the dedicated pins TSLD and TSLDCLK. The transmit path overhead interface consists of the TPOH, TPOHRDY, TPOHEN, TPOHFP, and TPOHCLK signals to/from the THPP blocks. This interface runs at a nominal 20.736 MHz.

#### **5.2.3** Ring Control Port

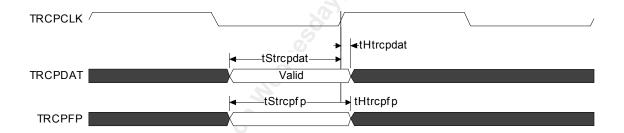

The ring control port allows a mate ARROW 155, or FPGA to perform real time insertion and extraction of alarms and status. The Ring Control Port consists of the RRCPDAT, TRCPDAT, TRCPCLK, and TRCPFP signals that connect to the SARC block. RPOHCLK and RPOHFP are used to indicate timing and frame alignment for the RRCPDAT signal. The functional timing section (Sections 8.13 and 8.14) provides further detail on this interface.

#### 5.2.4 DS3/E3/STS-1E Overhead

The ARROW 155 provides access to the overhead of up to three DS3, E3, or STS-1E signals. The DS3/E3/STS-1E overhead port consists of the ROH, ROHFA, ROHVAL, TOH, TOHINS, TOHFA, TOHVAL, OHCH[1:0], and OHCLK pins. The DS3/E3/STS-1E overhead port is clocked by the OHCLK pin, and provides each channel's overhead in a timeslot multiplexed bit serial stream. The channel on the bus at each time is indicated by the OHCH[1:0] pins. Cycles where OHCH[1:0] = '11', are invalid and should be ignored.

#### 5.2.5 DS3/E3/STS-1E Serial

The DS3/E3/STS-1E Serial interface is jitter attenuated in both the transmit and receive directions. Depending on the mode of operation, the transmit interface consists of either TCLK, TPOS, and TNEG for each channel or TCLK, TDATO, and TOHM for each channel (total of 9 pins). Depending on the mode of operation, the receive interface consists of either RCLK, RPOS, and RNEG for each channel or RCLK, RDATI, and RLCV for each channel (total of 9 pins). These signals may connect directly to an LIU without additional jitter attenuation. The DS3/E3 desynchronizer exceeds all jitter and wander specifications, and requires only a DS3 or E3 line rate clock. The PDHREFCLK[1:0] inputs are provided for this purpose.

#### 5.2.6 Parallel TelecomBus

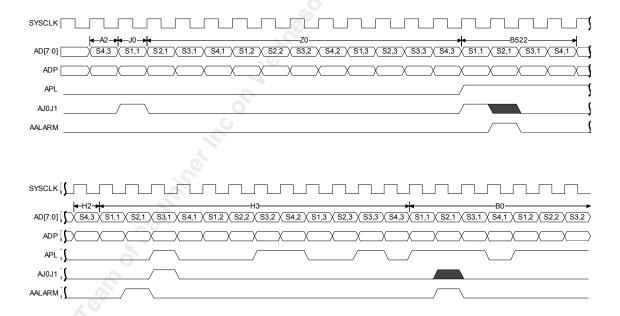

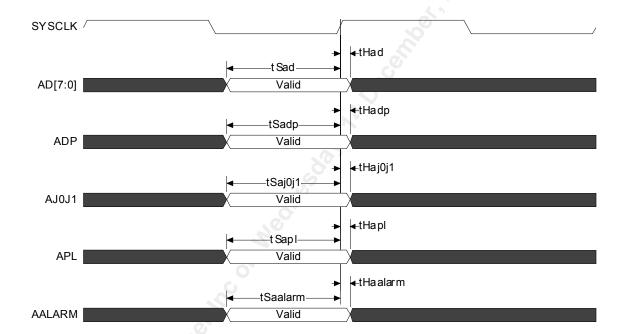

The Parallel TelecomBus (P-TCB) interface implements the main system side interface and is clocked relative to a single input clock (SYSCLK). On the Add side (chip data in), it consists of an 8-bit databus (AD[7:0]), a data parity signal (ADP), a payload marker (APL), a frame marker signal (AJ0J1), and an alarm forcing signal (AALARM).

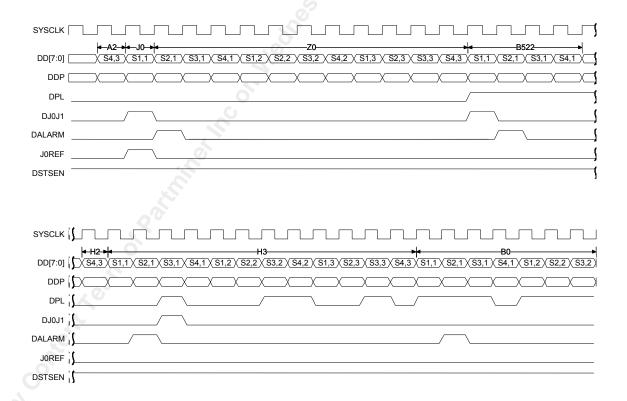

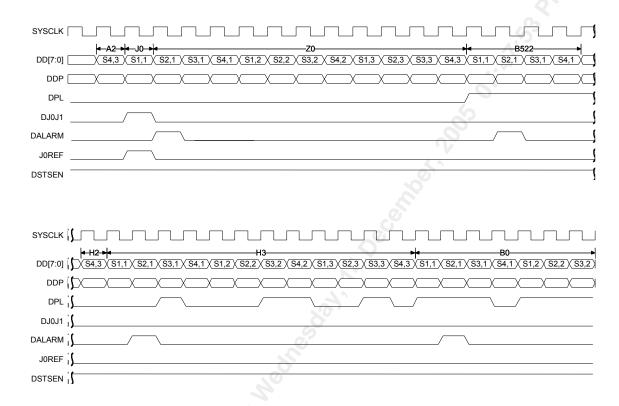

On the Drop side (chip data out), it consists of an 8-bit databus (DD[7:0]), a data parity signal (DDP), a payload marker (DPL), a frame marker (DJ0J1), an alarm signal (DALARM), a frame pulse reference input (J0REF), and a timeslot tristate enable (DSTSEN).

An output clock reference signal (LINECLK\_REF) provides a 77.76 MHz clock that is locked to either the recovered line side clock, or the generated line side clock. The system designer may chose to use LINECLK\_REF as the source for SYSCLK to eliminate pointer movements in either the Add or Drop direction.

Where H1& H2 are valid, the SHPI block may be used rather than explicit framing, payload, and alarm signals. If the SHPI is enabled, the ADP, APL, and AALARM inputs may be grounded. If the J1SQUELCH bit is set, the AJ0J1 signal (which normally pulses high to mark the J0 and J1 bytes) is re-defined as to only carry a single frame pulse per frame. The location of that frame pulse in the frame is user programmable in the FPINDLY[13:0] bits. The ADP input may be ignored if the APE bit is not set. Note that the SHPI is enabled by default. To disable it, set the PT PATH[x] bits in register 0x1A06.

If the J1SQUELCH bit is set, the DJ0J1 signal is modified similar to the AJ0J1 signal to create a user selectable frame pulse, which is programmed with the FPOUTDLAY[13:0] bits.

Note that although the ARROW 155 operates at 155.52 Mbit/s, the TelecomBus interface operates at 77.76 MHz. This is to provide hardware compatibility with the PM5319 ARROW 622 device and to allow multiple ARROW 155 devices to timeslot-multiplex their traffic into a 622.08 Mbit/s fabric switch or DS0 termination device. While the TelecomBus always operates at 77.76 MHz, it is compatible with 19.44 MHz systems.

#### 5.2.7 Microprocessor

The generic microprocessor interface provides configuration and control of the ARROW 155. It consists of a 16-bit bidirectional data bus (D[15:0]), an address bus (A[13:0]), an address latch enable (ALE) for supporting multiplexed address and data bus applications, and active low read strobe (RDB), write strobe (WRB), and chip select (CSB). The device is reset by the active low RSTB pin. Alarms and events in the device can interrupt the controller via the active low open drain (INTB) interrupt pin.

#### 5.2.8 JTAG

The standard JTAG interface consists of the TCK, TDI, TMS, TRSTB, and TDO signals.

### 5.3 Modes of Operation

The ARROW 155 device has several modes of operation that can be software configured. Descriptions of the main modes follow.

#### 5.3.1 OC-3 Mode

In this mode, all rate programmable blocks (RRMP, TRMP, JAT\_622, DCRU and STS3 <-> STS12 converters) are configured for STS-3 operation, and these blocks run at the reduced clock frequency of 19.44 MHz. DS3/E3/STS-1E channels are switched into the datapath by programming the appropriate timeslots of the respective SONET/SDH Timeslot Interchange (STSI) but the valid timeslots of the STSI toward the SONET/SDH line side are restricted to only one STS-3 worth of timeslots. (The DROP STSI incoming timeslots 2 to 4 are duplicates of 1, 6 to 8 are duplicates of 5 and 10 to 12 are duplicates of 9 on the STSI inputs DIN1,2 and 4 for UNEQ-P. The ADD STSI outgoing timeslots 2 to 4, 6 to 8 and 10 to 12 on output ports 1 & 4 are discarded. All DROP STSI outgoing and all ADD STSI incoming timeslots are valid.)

#### 5.3.2 DS3/E3/STS-1E Mapper Mode

The SONET/SDH interface in the ARROW 155 may be turned off, allowing the device to operate strictly as a mapper for DS3, E3, and STS-1E signals. The DS3/E3/STS-1E channels must talk through the P-TCB interface. A dedicated Bypass mode is provided in the STSI's to support this mode with minimal configuration. For normal operation, the user need not provide clock to the line side in this mode. However, to use the PRBS block, a line side clock and use of the STSI block are required.

### 5.4 Datapath

Section 5.1 has already given a brief overview of the main SONET/SDH framer datapath. There are, however, a number of possibilities in the configuration of the STSI blocks, which can best be understood by Figure 8. The receive DIN timeslots 1, 5, and 9 contain valid data, and the other input timeslots are invalid. Similarly, transmit DOUT timeslots 1, 5, and 9 must contain the valid timeslots, and the other timeslots will be discarded.

PDH transmitter PDH receiver SLICE (source and destination) DROP din4 dout4 BUS **RX LINE** din3 dout3 (dest) **RSTSI** SVCA dout2 din2 (source) din1 dout1 (bypass) STS-1 VDD Loopback

**TSTSI**

(bypass) stsia\_bypass

dout4

dout3

dout2

dout1

Figure 8 STSI Datapaths

### 5.4.1 SONET/SDH Only Mode

TX LINE

**SVCA**

(dest)

If only the SONET/SDH framer is required, and no traffic from the DS3/E3/STS-1E subsystem will appear on the TelecomBus or on the serial line interface, then the user only needs to configure the DIN1 and DOUT1 ports of the Transmit and Receive STSI. If no timeslot interchange is required, this can easily be accomplished by writing a '1' to the STSID\_BYPASS and STSIA\_BYPASS bits. If timeslot interchange is required, the user will have to configure the DOUT1 port of both STSIs.

din4

din3

din2

din1

ADD

BUS/

SHPI

(source)

#### 5.4.2 Receive STSI Datapath Configurations

The DOUT2 port of the Receive STSI can be used as the source for Transmit PDH (DS3/E3/STS-1E) traffic if RXD\_P/N is the exclusive source of Transmit PDH traffic. This datapath input is selected by writing '1' to TX\_SLICE\_DROP\_ADDB. When STSID\_BYPASS is '1', all timeslots that appear on the TelecomBus are copied to the Transmit slice. The TSI of each slice can then select the appropriate timeslot for that PDH slice. When the Receive STSI is not in bypass, the DOUT2 port will have to be configured to output the required timeslots.

The DOUT3 port of the Receive STSI is provided for the DS3/E3/STS-1E mapping mode, where the Receive PDH slice is the exclusive source of Drop TelecomBus traffic. This mode is selected by writing '1' to the DROP BUS SEL bit.

The DOUT4 port of the Receive STSI provides a per-timeslot loopback capability, and is also used to enable the most general datapath configuration. If the datapath configuration requires that the transmit PDH traffic can come from either the PECL interface or from the TelecomBus, or if the receive PDH traffic can go out either the TelecomBus or the PECL interface, then DOUT4 must be configured to select those timeslots from the Receive SONET/SDH line that are destined for the Transmit PDH, and those timeslots from the Receive PDH that are destined for the Transmit SONET line. If a per-timeslot line loopback is required DOUT4 must be configured to select the timeslots that need to loop-back.

The DIN4 port of the Receive STSI serves a special function to support UNEQ-P insertion on the Drop bus. When the STSID\_UNEQ\_DIS bit is '0', DIN4 contains a copy of the timeslots on DIN1, but with the SPE forced to all 00. If a path is unused in the Drop TelecomBus, then a similar timeslot or timeslots from DIN4 should be switched onto the DOUT1/DOUT3 output as an UNEQ-P path.

#### 5.4.3 Transmit STSI Datapath Configurations

The DIN2 port of the Transmit STSI is sourced from the Receive PDH slice. This data path source is best when the receive PDH traffic is destined exclusively for the PECL interface. Note that there is no bypass output on DOUT2, so any PDH timeslots will have to be explicitly mapped to either DOUT1 or DOUT4.

The DOUT3 port of the Transmit STSI feeds the Transmit PDH slice when the TX\_SLICE\_DROP\_ADDB bit is '0'. This datapath setting supports the general case of PDH transmit traffic sourced from both the PECL and the Add bus, as well as the 3xETEC datapath of sourcing the Transmit PDH traffic exclusively from the Add bus. This port does support an automatic bypass, but the bypass is not recommended if Transmit SONET or PDH data is also coming from the STS-1 Loop-back. Note that if PDH transmit traffic is sourced from both the STS-1 Loopback and the Add bus, the J0 alignment of the Add bus and the Drop bus must be such that the STSLB J0I interrupt does not assert.

The DIN4 port completes the STS-1 loop-back described above. These timeslots will have to be mapped into the DOUT1 or DOUT3 ports for their respective destinations. The DOUT4 port provides a bypass path for a full datpath line loopback at the STSIs.

### 5.4.4 Loopbacks

The loopbacks in this device are described in the *PMC-2030860 PM5319/PM5320 ARROW 622/155 Operation and Configuration Guide*.

## 6 Pin Description

The following sections describe each ball. Unless stated, all control signals are active high logic. Ball assignments may be found in the ARROW 155 Ball Map File, PMC-2031854. This file is provided in .xls format to simplify schematic symbol generation.

**Table 2 Pin Type Definition**

| Туре      | Definition                                     |

|-----------|------------------------------------------------|

| Input     | Input                                          |

| Output    | Pin is always driven                           |

| Tri-State | Pin is either driven, or held in Hi-Z          |

| BiDi      | Bidirectional                                  |

| OD        | Open drain. Either driven low or held in Hi-Z. |

### 6.1 Parallel TelecomBus Transmit Interface

All pins are 3.3 V LVTTL compatible logic levels.

| Pin Name                    | Reset<br>State | Туре       | Pin<br>No.           | Function                                                                                                                                                                                                                                                       |

|-----------------------------|----------------|------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSCLK                      | Hi-Z           | Input      | N2                   | Parallel TelecomBus Add Clock                                                                                                                                                                                                                                  |

|                             |                |            | 11/2                 | SYSCLK is a 77.76 MHz clock. AD[7:0], ADP, APL, AJ0J1, AALARM, and J0REF are sampled on the rising edge of SYSCLK. DD[7:0], DDP, DPL, DJ0J1, DALARM, and DSTSEN are updated on the rising edge of SYSCLK.                                                      |

|                             |                | <i>C</i> . |                      | SYSCLK should be free of glitches when RSTB is high.                                                                                                                                                                                                           |

| AD[7]                       | Hi-Z           | Input      | L2                   | Parallel TelecomBus Add Bus                                                                                                                                                                                                                                    |

| AD[6]<br>  AD[5]<br>  AD[4] |                |            | L4<br>K1<br>K3<br>K4 | The AD[7:0] input bus sources the transmit SONET/SDH frames.                                                                                                                                                                                                   |

| AD[3]                       |                |            |                      | AD[7:0] is sampled on the rising edge of SYSCLK.                                                                                                                                                                                                               |

| AD[2]<br>AD[1]<br>AD[0]     | 00/10          |            | J1<br>J2<br>J3       |                                                                                                                                                                                                                                                                |

| ADP                         | Hi-Z           | Input      | МЗ                   | Parallel TelecomBus Add Data Parity                                                                                                                                                                                                                            |

| Land                        |                |            |                      | ADP reports the parity of the corresponding Add data bus (AD[7:0]). ADP reports even parity by default, however it may be configured for odd parity and to report parity over Add data bus and the control signals (APL and AJ0J1) via microprocessor control. |

|                             |                |            |                      | If a parity signal is not available, ADP may be tied low if the APE bit in register 0x1809 is set low.                                                                                                                                                         |

| 0                           |                |            |                      | ADP is sampled on the rising edge of SYSCLK.                                                                                                                                                                                                                   |

| Pin Name    | Reset<br>State | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------------|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APL         | Hi-Z           | Input  | L1         | Parallel TelecomBus Add Payload marker                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                |        |            | APL distinguishes between transport overhead bytes and synchronous payload/high order virtual container bytes in the corresponding Add data bus (AD[7:0]).                                                                                                                                                                                                                                                                          |

|             |                |        |            | APL is set high to mark each payload / HO-VC byte on AD[7:0] and set low to mark each transport overhead byte on AD[7:0].                                                                                                                                                                                                                                                                                                           |

|             |                |        |            | APL may be tied low if the SHPI is enabled for all timeslots. APL must be tied low if the frame pulse is moved to any position other than J0.                                                                                                                                                                                                                                                                                       |

|             |                |        |            | APL is sampled on the rising edge of SYSCLK.                                                                                                                                                                                                                                                                                                                                                                                        |

| AJ0J1       | Hi-Z           | Input  | M2         | Parallel TelecomBus Add J0/J1 marker                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                |        |            | AJ0J1 pulses high when AD[7:0] carries the J0 and all J1 bytes. It is low otherwise. J0 position must be indicated, but J1 bytes may be internally decoded provided that valid H1/H2 pointers are present.                                                                                                                                                                                                                          |

|             |                |        |            | By default the J0 frame pulse is indicated, but the ARROW 155 may be configured to accept a frame pulse on any byte of the SONET/SDH frame. If the frame pulse is moved from the J0 position, the APL input must also be tied low.                                                                                                                                                                                                  |

|             |                |        |            | AJ0J1 is sampled on the rising edge of SYSCLK.                                                                                                                                                                                                                                                                                                                                                                                      |

| AALARM      | Hi-Z           | Input  | M1         | Parallel TelecomBus Add Alarm marker                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                |        | 27         | AALARM identifies STS/STM streams on the corresponding Add data bus (AD[7:0]) that are in alarm state. Definition of the alarm condition depends on the amount of SONET/SDI processing performed by the ARROW 155.                                                                                                                                                                                                                  |

|             |                | 9110   |            | AALARM is set high when the stream on AD[7:0] is in alarm state (for instance, PAIS) and is set low when the stream is out of alarm state.                                                                                                                                                                                                                                                                                          |

|             |                |        |            | AALARM may be tied low if the SHPI is enabled for all timeslots. Note that AALARM high will result in transmit path AIS regardless of SHPI settings, as AALARM is internally ORed with the SHPI output.                                                                                                                                                                                                                             |

|             | Q              |        |            | In a concatenated data configuration (STS-3c) only the first STS-1 is defined.                                                                                                                                                                                                                                                                                                                                                      |

| 2           |                |        |            | AALARM is sampled on the rising edge of SYSCLK.                                                                                                                                                                                                                                                                                                                                                                                     |

| LINECLK_REF | Low            | Output | N1         | Line Clock Reference                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                |        |            | LINECLK_REF is an output clock aligned with either the recovered receive data clock (LINECLK_REF_SEL = 0) or the transmit clock (LINECLK_REF_SEL = 1). Internal receive pointer adjustments can be avoided by using LINECLK_REF as the source for SYSCLK when the LINECLK_REF_SEL bit is '0'. Internal Transmit pointer adjustments can be avoided by using LINECLK_REF as the source of SYSCLK when the LINECLK_REF_SEL bit is '1' |

|             |                |        |            | If LINECLK_REF is not required, it may be powered down by writing a '1' to the LINECLK_PWRDN bit.                                                                                                                                                                                                                                                                                                                                   |

## 6.2 Parallel TelecomBus Receive Interface

All pins are 3.3V LVTTL compatible logic levels, unless stated otherwise.

| Pin Name                                                    | Reset<br>State | Туре                  | Pin<br>No.                             | Function                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------|----------------|-----------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DD[7] H                                                     | Hi-Z           | Tri-state             | F1                                     | Parallel TelecomBus Drop bus                                                                                                                                                                                                                                             |

| DD[6]<br>DD[5]<br>DD[4]<br>DD[3]<br>DD[2]<br>DD[1]<br>DD[0] |                | Output                | F2<br>F3<br>E1<br>F4<br>E3<br>E4<br>D1 | The DD[7:0] output bus delivers the received SONET/SDH data. DD[7:0] defaults to tri-state on reset, and can be configured to drive tri-state on a timeslot by timeslot basis. DD[7:0] is updated on the rising edge of SYSCLK.                                          |

| DDP                                                         | Hi-Z           | Tri-state             | G3                                     | Parallel TelecomBus Drop Data Parity                                                                                                                                                                                                                                     |

|                                                             |                | Output                |                                        | DDP reports the parity of the corresponding outgoing data bus (DD[7:0]). DDP reports even parity by default, however it may be configured for odd parity and to report parity over outgoing data bus and the control signals (DPL and DJ0J1) via microprocessor control. |

|                                                             |                |                       |                                        | DDP is updated on the rising edge of SYSCLK.                                                                                                                                                                                                                             |

| DPL                                                         | Hi-Z           | Tri-state             | G4                                     | Parallel TelecomBus Drop Payload marker                                                                                                                                                                                                                                  |

|                                                             |                | Output                | 4                                      | DPL distinguishes between transport overhead bytes and synchronous payload/high order virtual container bytes in the corresponding Drop data bus (DD[7:0]).                                                                                                              |

|                                                             |                |                       |                                        | DPL is set high to mark each payload / HO-VC byte on DD[7:0] and set low to mark each transport overhead byte on DD[7:0].                                                                                                                                                |

|                                                             |                |                       |                                        | DPL is updated on the rising edge of SYSCLK.                                                                                                                                                                                                                             |

| DJ0J1                                                       | Hi-Z           | Z Tri-state<br>Output | G2                                     | Parallel TelecomBus Drop J0/J1 marker                                                                                                                                                                                                                                    |

|                                                             |                |                       |                                        | DJ0J1 pulses high when DD[7:0] carries the J0 (DPL low) and all J1 bytes (DPL high). It is low otherwise.                                                                                                                                                                |

| 0                                                           | QUIS           |                       |                                        | The ARROW 155 may be configured to squelch all J1 pulses by setting the J1SQUELCH bit. By default, the J0 frame pulse is indicated, however the ARROW 155 may be configured to indicate any SONET/SDH byte as the frame pulse.                                           |

|                                                             | Ö              |                       |                                        | DJ0J1 may be tri-stated along with the rest of the Drop bus by the DJ0J1ENB bit.                                                                                                                                                                                         |

|                                                             |                |                       |                                        | DJ0J1 is updated on the rising edge of SYSCLK.                                                                                                                                                                                                                           |

| DALARM                                                      | Hi-Z           | Tri-state             | G1                                     | Parallel TelecomBus Drop Alarm marker                                                                                                                                                                                                                                    |

| DALARM                                                      |                | Output                |                                        | DALARM identifies STS/STM streams on the corresponding Drop data bus (DD[7:0]) that are in alarm state. Definition of the alarm condition depends on the amount of SONET/SDH processing performed by the ARROW 155.                                                      |