### MABC-001000-DP000L

Rev. V3

#### **Features**

- Robust GaN Protection at Any Power Up/Power Down Sequence

- Fixed Gate Bias Voltage with Pulsed Drain Bias Voltage. Add-On Module Allows for Gate Pulsing

- Open Drain Output Current of ≤ 200 mA for External MOSFET Switch Drive

- Internal Thermistor or External Temperature Sensor Voltage for Gate Bias Sum

- 30 dB Typical EMI/RFI Rejection at All I/O Ports

- 6.60 x 22.48 mm<sup>2</sup> Package with 1 mm Pitch SMT Leads

- Target ≤ 500 ns Total Switch Transition Time

- Gate Bias Output Current ≤ 50 mA for Heavy RF Compression

- RoHS\* Compliant and 260°C Reflow Compatible

### **Description**

The MABC-001000-DP000L is a bias controller that provides proper gate voltage and pulsed drain voltage biasing for a device under test (DUT). Applicable DUT's would be depletion-mode GaN (Gallium Nitride) or GaAs (Gallium Arsenide) power amplifiers or HEMT devices.

The module also provides bias sequencing so that pulsed drain voltage cannot be applied to a DUT unless the negative gate bias voltage is present.

The applications section of this datasheet will show how the module can be implemented for the following two applications:

- Application Option 1: Fixed negative gate biasing with pulsed drain biasing.

- Application Option 2: Pulsed negative gate biasing with pulsed drain biasing.

Both of these applications will recommend the external circuitry and p-Channel Power MOSFET.

The MABC-001000-DP000L module can also be installed onto an MABC-001000-PB1PPR evaluation board for evaluation, test, and characterization purposes.

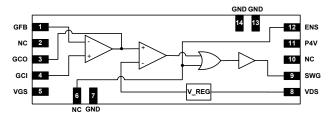

#### **Functional Schematic**

### Pin Configuration<sup>1</sup>

| Pin# | Label | Function                              |  |  |

|------|-------|---------------------------------------|--|--|

| 1    | GFB   | Gate Voltage (-) Feedback             |  |  |

| 2    | NC    | No Connect                            |  |  |

| 3    | GCO   | Gate Voltage (-) Control Output       |  |  |

| 4    | GCI   | Gate Voltage (-) Control Input        |  |  |

| 5    | VGS   | Gate (-) Supply Voltage               |  |  |

| 6    | NC    | No Connect                            |  |  |

| 7    | GND   | Ground                                |  |  |

| 8    | VDS   | Drain (+) Supply Voltage              |  |  |

| 9    | SWG   | Driver Output to MOS Switch Gate      |  |  |

| 10   | NC    | No Connect                            |  |  |

| 11   | P4V   | Auxiliary +4.3 V <sub>DC</sub> Output |  |  |

| 12   | ENS   | MOS Switch Enable TTL                 |  |  |

| 13   | GND   | Ground                                |  |  |

| 14   | GND   | Ground                                |  |  |

Unused package pins must be left open and not connected to ground.

### Ordering Information<sup>2</sup>

| Part Number        | Packaging   |

|--------------------|-------------|

| MABC-001000-DP000L | Tray        |

| MABC-001000-DP00TL | Tape & Reel |

<sup>2.</sup> Reference Application Note M513 for reel size information.

<sup>\*</sup> Restrictions on Hazardous Substances, compliant to current RoHS EU directive.

### MABC-001000-DP000L

Rev. V3

### **Electrical Characteristics:** T<sub>A</sub> = 25°C

| Symbol           | Parameter                                               | Conditions                               | Min | Тур                 | Max | Unit |

|------------------|---------------------------------------------------------|------------------------------------------|-----|---------------------|-----|------|

| V <sub>DS</sub>  | Supply Voltage, Positive                                |                                          | 10  | 50                  | 70  | V    |

| I <sub>DS</sub>  | Supply Current, Positive                                |                                          | -   | 14                  | -   | mA   |

| $V_{GS}$         | Supply Voltage, Negative                                |                                          | -8  | -6                  | 0   | V    |

| I <sub>GS</sub>  | Supply Current, Negative                                |                                          | -   | -3                  | -   | mA   |

| V <sub>ENL</sub> | ENS Input Voltage, Low                                  |                                          | 0   | 0                   | 0.3 | V    |

| V <sub>ENH</sub> | ENS Input Voltage, High                                 |                                          | 2   | 3.3                 | 4.3 | V    |

| I <sub>ENS</sub> | ENS Input Current                                       |                                          | -   | 40                  | -   | uA   |

| V <sub>GTH</sub> | Input, Gate Feedback Threshold to V <sub>GS</sub>       |                                          | -   | 2.7                 | -   | V    |

| $V_{DTH}$        | Input, Drain Feedback Threshold                         |                                          | -   | 65% V <sub>DS</sub> | -   | V    |

| $V_{GC}$         | Output Voltage, Pulsed/Fixed Gate                       |                                          | -8  | -3.5                | 0   | V    |

| $V_{GCR}$        | Output Voltage, Pulsed/Fixed Gate Ripple (Peak-to-peak) |                                          | -   | 50                  | -   | mV   |

| I <sub>GC</sub>  | Output Gate Current, Peak                               |                                          | -   | 50                  | -   | mA   |

| R <sub>OFF</sub> | Output Drive, Open Drain, OFF State                     |                                          | -   | 4M                  | -   | Ω    |

| R <sub>ON</sub>  | Output Drive, Open Drain, ON State                      | $V_{DS} = 50 \text{ V}$<br>Temp. = +85°C | -   | 1.2                 | -   | Ω    |

| I <sub>ON</sub>  | Output Drive, Current, ON State                         | ]                                        | -   | 100                 | 200 | mA   |

### **Absolute Maximum Ratings**

| Parameter                           | Min.   | Max.    |

|-------------------------------------|--------|---------|

| Supply (+) Voltage, V <sub>DS</sub> | 0 V    | +60 V   |

| Supply (-) Voltage, V <sub>GS</sub> | -10 V  | 0 V     |

| Logic Voltage, ENS, GSE             | -0.3 V | +4.5    |

| Analog (-) Voltage, GCI, GFB        | -10 V  | 0 V     |

| Switch Driver Voltage, SWG          | 0 V    | +75 V   |

| Switch Driver Sink Current, SWG     | -      | -200 mA |

| Lead Soldering Temp (10 s)          | -      | +260°C  |

| Operating Temperature               | -40°C  | +85°C   |

| Storage Temperature                 | -65°C  | +150°C  |

### **Recommended Operating Conditions**

| Parameter                           | Typical          |

|-------------------------------------|------------------|

| Supply (+) Voltage, V <sub>DS</sub> | +12 V to +55 V   |

| Supply (-) Voltage, V <sub>GS</sub> | -8 V to -2 V     |

| Logic Voltage, ENS                  | 0 V to +4.3 V    |

| Analog (-) Voltage, GCI, GFB        | -8 V to -2 V     |

| Switch Driver Sink Current, SWG     | -1 mA to -200 mA |

| Operating Temperature               | -40°C to +85°C   |

### MABC-001000-DP000L

Rev. V3

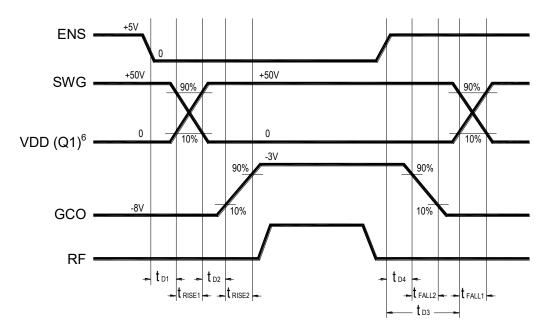

### Timing Characteristics: $T_A = 25$ °C

| Symbol             | Parameter                                       | Conditions                                                                                           | Min | Тур | Max | Unit |

|--------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>D1</sub>    | Open Drain ON Propagation Delay <sup>3</sup>    | 5 700 0                                                                                              | -   | 100 | -   | ns   |

| t <sub>D3</sub>    | Open Drain OFF Propagation Delay <sup>3</sup>   | $R_{PULL-UP} = 700 \Omega$<br>$V_{DS} = 50 V$<br>$I_{R} = 71 \text{ mA avg.}$<br>Switch Disconnected | -   | 70  | -   | ns   |

| t <sub>RISE1</sub> | Open Drain Rise Time <sup>4</sup>               |                                                                                                      | -   | 115 | -   | ns   |

| t <sub>FALL1</sub> | Open Drain Fall Time <sup>4</sup>               |                                                                                                      | -   | 60  | -   | ns   |

| t <sub>D1</sub>    | MOS Switch ON Propagation Delay <sup>3,5</sup>  | $V_{DS} = 50 \text{ V}$ $MOS C_{ISS} = 2780 \text{ pF}$ $R_{DS,ON} = 60 \text{ m}\Omega$             | -   | 300 | -   | ns   |

| t <sub>D3</sub>    | MOS Switch OFF Propagation Delay <sup>3,5</sup> |                                                                                                      | -   | 1.8 | -   | μs   |

| t <sub>RISE1</sub> | MOS Switch Rise Time <sup>4,5</sup>             |                                                                                                      | -   | 400 | -   | ns   |

| t <sub>FALL1</sub> | MOS Switch Fall Time <sup>4,5</sup>             |                                                                                                      | -   | 80  | -   | μs   |

| t <sub>D2</sub>    | Gate Bias ON Propagation Delay <sup>3,5</sup>   |                                                                                                      | -   | 100 | -   | ns   |

| t <sub>D4</sub>    | Gate Bias OFF Propagation Delay <sup>3,5</sup>  |                                                                                                      | -   | 200 | -   | ns   |

| t <sub>RISE2</sub> | Gate Bias Rise Time <sup>4,5</sup>              |                                                                                                      | -   | 500 | -   | ns   |

| t <sub>FALL2</sub> | Gate Bias Fall Time <sup>4,5</sup>              |                                                                                                      | -   | 400 | -   | ns   |

- 3. Propagation delay is measured from 90% of the TTL signal to 10% of the signal of interest.4. Rise and fall times are measured between 10% and 90% of the steady state signal.

- 5. Parameter was measured with MABC-001000-PB1PPR sample board. MAGX-L21214-650L00 was used as the DUT.

### **Timing Diagrams**

6. Q1 refers to an external p-Channel HEXFET that pulses the drain of the DUT. See Applications Section for more information.

MABC-001000-DP000L

Rev. V3

### **Applications Section**

#### **Functional Description**

The MABC-001000-DP000L GaN Bias Controller/ Sequencer Module circuitry provides proper sequencing and generation of the gate voltage and pulsed drain voltage for a device under test (DUT). Reference the Product View and Pin Configuration table on page 1. The basic functions of the circuits within the module are described as follows:

- Overhead Voltages for the Circuits within the MABC-001000-DP000L Module

- Pin 8 (VDS) is the Drain (+) Supply Voltage that provides the input voltage to a low dropout linear regulator (VREG). This supplies the positive voltage for the circuits within the module. It also provides the Auxiliary +4.3 V Output to Pin 11 (P4V).

- Pin 5 (VGS) is the Gate (-) Supply Voltage that is also used to supply the negative voltage for the circuits within the module.

- Negative Gate Voltage for the Device Under Test (DUT)

- A voltage follower op-amp circuit provides a low impedance output to Pin 3 (GCO) Gate Voltage (-) Control Output. Pin 3 (GCO) output is applied to the gate terminal of a DUT as shown in Figure 1 on page 5.

- The reference voltage for the voltage follower is provided by the Pin 4 (GCI) Gate Voltage (-) Analog Input. This input reference voltage is developed by an external potentiometer/ resistive divider circuit as shown in Figure 1 on page 6. It is recommended to use the -8 V to -3 V voltage that is also applied to Pin 5 (VGS).

- Reference: The external potentiometer is adjusted to set the gate voltage Pin 3 (GCO) to the DUT. Alternative voltage inputs such as a temperature compensation circuit or a Digital-to-Analog (DAC) converter could also be supplied to Pin 4 (GCI).

- Pin 9 (SWG) MOS Switch Driver Output

- An N-Channel MOSFET develops the pulsed signal (SWG) to drive the resistive divider network for the gate of an external p-Channel HEXFET as shown in Figure 1 on page 5. The input signal for the internal MOSFET is provided by the output from the sequencing circuits.

- Sequencing Circuits

- A voltage comparator circuit senses if the negative gate voltage is present as an input on Pin 1 (GFB) - Gate Voltage (-) Feedback.

- A logic circuit provides the switched input enable signal for the N-Channel MOSFET. The following 3 signals must be at correct levels to generate the enable logic signal:

- Pin 12 (ENS) MOS Switch Enable TTL

- Negative gate voltage (GFB) is present

- The internal positive voltage output is present from V REG

MABC-001000-DP000L

Rev. V3

### **Applications Section**

### **Module Layout Guidelines**

Reference the Product View, Pin Configuration Table on page 1, and the Recommended Landing Pattern on page 7.

The following recommendations should be followed when the MABC-001000-DP000L module is used to bias a high-power RF device or amplifier. The input and output locations were determined so that the layout and signal routing could be optimized when interfacing with a high-power amplifier assembly.

- The negative gate voltage input and outputs are located on the left side of the module and should be located as close as possible to the gate bias pads on the high-power amplifier assembly.

- The positive pulsed voltages are located on the right side of the module and should be located as close as possible to the external MOSFET switch. The MOSFET switch drain should be located as close as possible to the drain bias pads on the high-power amplifier assembly. The charge storage capacitors should be located as close as possible to the MOSFET switch source terminal pads.

- The module ground pads are located at Pins 7, 13, and 14.

- Route all signal lines and ground returns to be as short as possible and implement a ground plane on the back of the printed wiring board (PWB) if that option is available to the designer. Following these layout criteria will minimize circuit parasitics that degrade the performance of the pulsed signal.

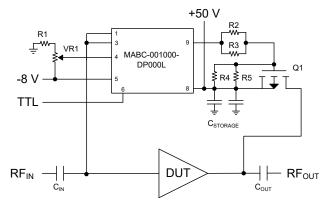

### Application Option 1: Fixed Negative Gate Biasing with Pulsed Drain Biasing

Figure 1 shows a block diagram of the MABC-001000-DP000L module with the recommended external components to support this application option. See Table 1 for component recommendations and values.

Figure 1. Fixed Gate/Pulsed Drain Biasing

| Part  | Value               | MFG       | MFG P/N            |

|-------|---------------------|-----------|--------------------|

| R1    | 2.7 kΩ              | Panasonic | ERJ-2GEJ272X       |

| R2,R3 | 1.02 kΩ             | Vishay    | CRCW25121K02FKEGHP |

| R4,R5 | 402 Ω               | Vishay    | CRCW2512402RFKEG   |

| VR1   | 10 kΩ               | Bourns    | 3224W-1-103E       |

| Q1    | P-Channel<br>MOSFET | IR        | IRF5210SPBF        |

Table 1. Recommended Parts List for Fixed Gate/Pulsed Drain Biasing

MABC-001000-DP000L

Rev. V3

### **Applications Section**

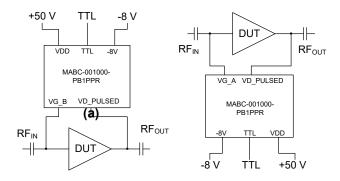

# Application Option 2: Pulsed Negative Gate Biasing with Pulsed Drain Biasing

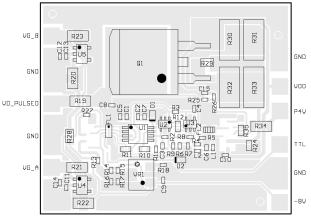

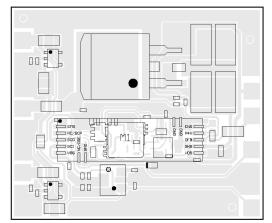

A block diagram showing a typical application of the MABC-001000-PB1PPR sample board is shown in Figure 2 below. Figures 3 and 4 show layouts of the MABC-001000-PB1PPR sample board with/without the MABC-001000-DP000L module installed.

The additional external circuitry on the MABC-001000-PB1PPR sample board provides the added capability of pulsed gate biasing. A full schematic, layout, and bill of materials are available upon request. A schematic, assembly layout, and Bill of Materials of the MABC-001000-DP000L evaluation board are available upon request.

Figure 2. Pulsed Gate/Pulsed Drain Biasing: (a) North Biasing; (b) South Biasing

Figure 3. Populated MABC-001000-PB1PPR Evaluation Board

Figure 4. MABC-001000-PB1PPR with MABC-001000-DP000L Mounted

MABC-001000-DP000L

Rev. V3

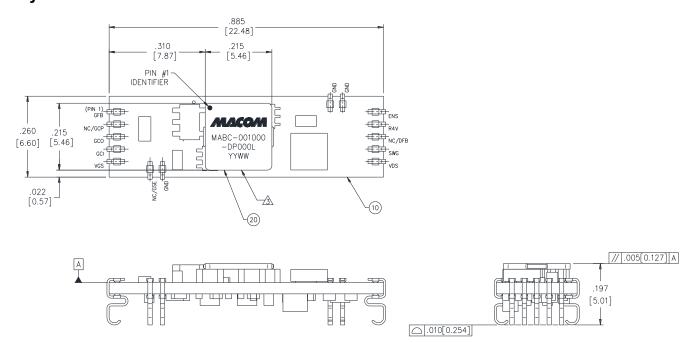

### Physical Dimensions<sup>6,7,8</sup>

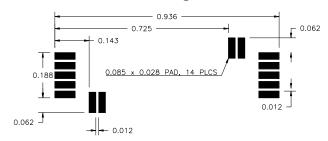

### Recommended Landing Pattern<sup>6</sup>

- 7. All dimensions are in inches.

- Reference Application Note M538 for lead-free solder reflow recommendations.

- 9. Plating is 100% Sn over BeCu.

### **Handling Procedures**

Please observe the following precautions to avoid damage:

### Static Sensitivity

This module is sensitive to electrostatic discharge (ESD) and can be damaged by static electricity. Proper ESD control techniques should be used when handling these HBM class 1B devices.

MABC-001000-DP000L

Rev. V

### MACOM Technology Solutions Inc. ("MACOM"). All rights reserved.

These materials are provided in connection with MACOM's products as a service to its customers and may be used for informational purposes only. Except as provided in its Terms and Conditions of Sale or any separate agreement, MACOM assumes no liability or responsibility whatsoever, including for (i) errors or omissions in these materials; (ii) failure to update these materials; or (iii) conflicts or incompatibilities arising from future changes to specifications and product descriptions, which MACOM may make at any time, without notice. These materials grant no license, express or implied, to any intellectual property rights.

THESE MATERIALS ARE PROVIDED "AS IS" WITH NO WARRANTY OR LIABILITY, EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MACOM PRODUCTS INCLUDING FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHT, ACCURACY OR COMPLETENESS, OR SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES WHICH MAY RESULT FROM USE OF THESE MATERIALS.

MACOM products are not intended for use in medical, lifesaving or life sustaining applications. MACOM customers using or selling MACOM products for use in such applications do so at their own risk and agree to fully indemnify MACOM for any damages resulting from such improper use or sale.