# Datasheet

# ZDB5101 Z-Wave Development Board

| Document No.: | DSH12571                                                                                   |

|---------------|--------------------------------------------------------------------------------------------|

| Version:      | 4                                                                                          |

| Description:  | This datasheet is for the ZM5101 Z Wave SiP Module based ZDB5101 Z-Wave Development Board. |

| Written By:   | MHANSEN;EBUSKGAARD;BBR                                                                     |

| Date:         | 2018-03-08                                                                                 |

| Reviewed By:  | OPP;BBR;EBUSKGAARD                                                                         |

| Restrictions: | None                                                                                       |

## Approved by:

Date CET Initials Name Justification

2018-03-08 09:50:12 NTJ Niels Thybo Johansen

This document is the property of Silicon Labs. The data contained herein, in whole or in part, may not be duplicated, used or disclosed outside the recipient for any purpose. This restriction does not limit the recipient's right to use information contained in the data if it is obtained from another source without restriction.

|          | REVISION RECORD |            |                                      |                                                                                                                                                          |  |  |

|----------|-----------------|------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Doc. Rev | Date            | Ву         | Pages affected                       | Brief description of changes                                                                                                                             |  |  |

| 3        | 20170517        | MHansen    | Table 5                              | Specified if measurements are radiated or conducted                                                                                                      |  |  |

| 1D       | 20140506        | slarsen    | Figure 3.1,<br>Table 4,<br>p.1, p.10 | Removed all references to matching network component as no matching is done on the board. Removed references to EU/US/HK BOM splits. BOMs are identical. |  |  |

| 1C       | 20131122        | MVithanage | Figure 4.1                           | Removed caption                                                                                                                                          |  |  |

| 1B       | 20131119        | MVithanage | Figure 3.1,<br>§All,<br>Table 4      | Removed 2.4GHz antenna Changed API to variant/library Changed OTP to Flash                                                                               |  |  |

| 1A       | 20131118        | MVithanage | §All                                 | Updated ZM4125 datasheet                                                                                                                                 |  |  |

| 2        | 20180308        | BBR        | All                                  | Added Silicon Labs template                                                                                                                              |  |  |

# **Table of Contents**

ABBREVIATIONS......1

| 2 I                                                                                    | NTRODUCTION                                                                                                              | .1     |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------|

| 2.1                                                                                    | Purpose                                                                                                                  |        |

| 2.2                                                                                    | Audience and prerequisites                                                                                               |        |

| 3 2                                                                                    | ZDB5101 Z-WAVE DEVELOPMENT BOARD                                                                                         | .2     |

| 3.1                                                                                    | Application Connector Specification                                                                                      | 2      |

| 3.2                                                                                    | SPI Interfaces and NVM                                                                                                   |        |

| 3.3                                                                                    | EMC Noise Reduction                                                                                                      |        |

| 3.4<br>3.5                                                                             | ZM5101 MCU SpecificationRF Specification for ZDB5101 with SAW                                                            |        |

| 3.6                                                                                    | Electrical Specification                                                                                                 |        |

| 3.6                                                                                    | ·                                                                                                                        |        |

| 3.6                                                                                    | 5.2 DC Characteristics                                                                                                   | .6     |

| 3.7                                                                                    | Module Outline                                                                                                           | .7     |

| 3.8<br>3.9                                                                             | Z-Wave Module Component Placement                                                                                        |        |

|                                                                                        | REFERENCES                                                                                                               |        |

| - ·                                                                                    |                                                                                                                          |        |

|                                                                                        |                                                                                                                          |        |

|                                                                                        | Table of Figures                                                                                                         |        |

|                                                                                        | e 3.1: ZDB5101 Z-Wave Development Board                                                                                  |        |

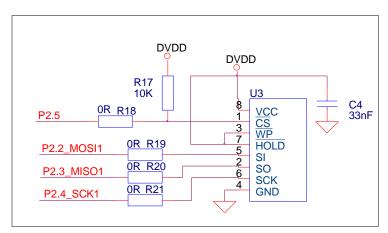

| Figur                                                                                  | e 3.1: ZDB5101 Z-Wave Development Boarde 3.2: External NVM                                                               | 4      |

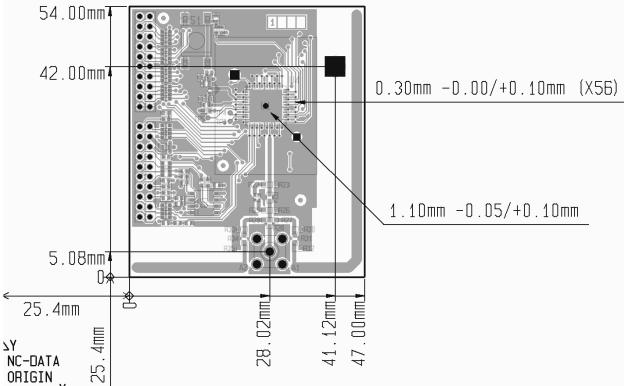

| Figur<br>Figur                                                                         | e 3.1: ZDB5101 Z-Wave Development Boarde 3.2: External NVMe 3.3: ZDB5101 Z-Wave Development Board PCB outline (Top View) | 7      |

| Figur<br>Figur                                                                         | e 3.1: ZDB5101 Z-Wave Development Boarde 3.2: External NVM                                                               | 7      |

| Figur<br>Figur                                                                         | e 3.1: ZDB5101 Z-Wave Development Boarde 3.2: External NVMe 3.3: ZDB5101 Z-Wave Development Board PCB outline (Top View) | 7      |

| Figur<br>Figur                                                                         | e 3.1: ZDB5101 Z-Wave Development Boarde 3.2: External NVMe 3.3: ZDB5101 Z-Wave Development Board PCB outline (Top View) | 7      |

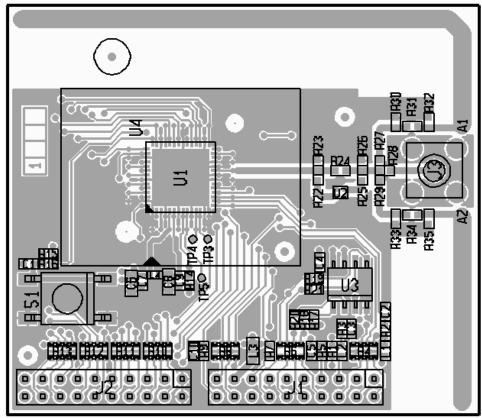

| Figur<br>Figur<br>Figur                                                                | e 3.1: ZDB5101 Z-Wave Development Boarde 3.2: External NVM                                                               | 4 7 8  |

| Figur<br>Figur<br>Figur<br>Table<br>Table                                              | e 3.1: ZDB5101 Z-Wave Development Board                                                                                  | 2 3    |

| Figur<br>Figur<br>Figur<br>Table<br>Table<br>Table                                     | e 3.1: ZDB5101 Z-Wave Development Board                                                                                  | 2 3 4  |

| Figur<br>Figur<br>Figur<br>Table<br>Table<br>Table                                     | e 3.1: ZDB5101 Z-Wave Development Board                                                                                  | 2345   |

| Figur<br>Figur<br>Figur<br>Table<br>Table<br>Table<br>Table<br>Table<br>Table          | e 3.1: ZDB5101 Z-Wave Development Board                                                                                  | 23456  |

| Figur<br>Figur<br>Figur<br>Table<br>Table<br>Table<br>Table<br>Table<br>Table<br>Table | e 3.1: ZDB5101 Z-Wave Development Board                                                                                  | 234566 |

# 1 ABBREVIATIONS

| Abbreviation | Explanation                                         |

|--------------|-----------------------------------------------------|

| D            | Differential                                        |

| EEPROM       | Electrically Erasable Programmable Read-Only Memory |

| HW           | Hardware                                            |

| 1            | Input                                               |

| NM           | Not Mounted                                         |

| NVM          | Non-Volatile Memory                                 |

| 0            | Output                                              |

| PCB          | Printed Circuit Board                               |

| SiP          | System-in-Package                                   |

| SMA          | Sub-Miniature A                                     |

| SW           | Software                                            |

| ZDB          | Z-Wave Development Board                            |

| ZDP          | Z-Wave Development Platform                         |

# 2 INTRODUCTION

### 2.1 Purpose

The purpose of this datasheet is to describe the ZDB5101 Z-Wave Development Board. The ZDB5101 Z-Wave Development Board contains the highly integrated ZM5101 Z-Wave SiP Module, NVM, HW interface protection circuitry, PCB antennas and a SMA connector for whip antenna mounting.

#### 2.2 Audience and prerequisites

The audience is customers who want to use or evaluate the ZM5101 Z-Wave SiP Module or find inspiration for implementing the ZM5101 on a 4-layer application PCB.

### 3 ZDB5101 Z-WAVE DEVELOPMENT BOARD

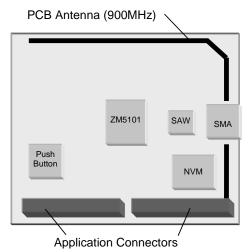

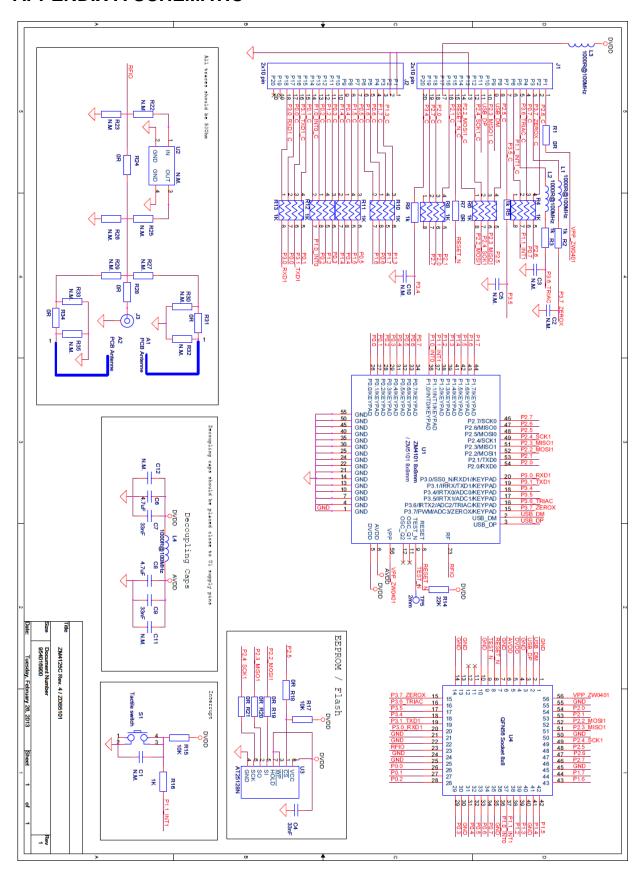

The ZDB5101 Z-Wave Development Board contains the ZM5101 Z-Wave SiP Module, NVM, HW Interface protection circuitry, PCB antennas and a SMA connector for whip antenna mounting. The key components on ZDB5101 are shown in Figure 3.1.

Figure 3.1: ZDB5101 Z-Wave Development Board

### 3.1 Application Connector Specification

The Application Connectors, J1, J2, on ZDB5101 Z-Wave Development Board are 2x10 2mm pitch pin rows. The signal availability on the application connectors are shown in Table 1.

Table 1: ZDB5101 Application Connector Pin List

|        | ZDB5101 / ZM4125-S           |        | ZDB5101 / ZM4125-S    |

|--------|------------------------------|--------|-----------------------|

| J1 no. | Pin Name                     | J2 no. | Pin Name              |

| 1      | VPP                          | 1      | Ground                |

| 2      | P2.6-MISO0                   | 2      | Ground                |

| 3      | P3.7-PWM-ADC3-ZEROX-KEYPAD   | 3      | P1.3-Keypad           |

| 4      | P0.7-KEYPAD                  | 4      | P1.7-Keypad           |

| 5      | P3.6-IRTX2-ADC2-TRIAC-KEYPAD | 5      | P0.6-Keyoad           |

| 6      | P1.1-INT1-KEYPAD             | 6      | P1.6-Keypad           |

| 7      | P3.5-IRTX1-ADC1-KEYPAD       | 7      | P0.5-Keypad           |

| 8      | P2.5-MOSI0                   | 8      | P1.5-Keypad           |

| 9      | USB_DM                       | 9      | P0.4-Keypad           |

| 10     | P2.3-MISO1                   | 10     | P1.4-Keypad           |

| 11     | USB_DP                       | 11     | P0.3-Keyoad           |

| 12     | P2.4-SCK1                    | 12     | P1.2-Keypad           |

| 13     | GND                          | 13     | P0.2-Keypad           |

| 14     | P2.2-MOSI1                   | 14     | P1.0-INT0-Keypad      |

| 15     | RESET_N                      | 15     |                       |

| 16     | P2.1-TXD0                    | 16     | P3.1-IRRX-TXD1-Keypad |

| 17     | VCC                          | 17     | P0.0-Keypad           |

| 18     | P2.0-RXD0                    | 18     | P3.0                  |

| 19     | P2.7-SCK0                    | 19     | NC                    |

| 20     | P3.4-IRTX0-ADC0-KEYPAD       | 20     | NC                    |

Table 2 gives an overview of the communication interfaces, signaling pins, and some ZM5101 HW features available on the application connectors. All GPIOs from ZM5101 are available on application

connectors J1, J2. For a complete list of signals and functionalities available, refer to the ZM5101 Z-Wave SiP Module Datasheet [1].

Table 2: ZDB5101 Z-Wave Development Board Application Connector Layout

| ## ADC[3:0]  ADC[3:0]  ADC[3:0]  J1: 3  J1: 5  J1: 5  J1: 7  ADC2: input  ADC2: input  ADC3: input  ADC4: input/ligher reference  ADC0: input/higher reference  GND  J1: 13  J2: 1, 2  INT1  INT0  J2: 14  INT0  J2: 14  INT0  Appendix A for IO pin number  P[0.0-0.0], Refer to Appendix A for IO pin number  P[3.0-3-1]  P[3.4-3.7]  MISO1  J1: 10  MOSI1  J1: 10  I/O  Master only SPI - Master-In-Slave-Out, and prog interface.  Work as a keypad matrix.  INT0  J1: 15  I Reset: Active low reset. The ZM5101 Z-Wave SIP Module has an integrated Power-On-Reset and Brown-out detection circuitry.  RXD0  J1: 18  I UART Receive Data: Supports up to 230.4kbaud.  SCK1  TRIAC  J1: 16  O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX  J1: 1  Power  J2: 10  Master or slave SPI. Master-In-Slave-Out SPI interface.  OTERIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module has an integrated Power-On-Reset and Brown-out detection circuitry.  RXD0  J1: 16  O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX  J1: 1  Power  J2: 10  Master only SPI - SPI Clock, and SPI clock for prog interface.  VPP  J1: 1  Power  OTERIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module that can control a triac on the Application Module like light dimmer modules etc.  TXD0  J1: 16  O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX  J1: 3  I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP  J1: 1  Power  OTERIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module that can control a triac on the Application Module like light dimmer modules etc.  ACCO TRIAC Control SPI SIP Clock and SPI clock for prog interface.  WPM  J1: 1  Power  J1: 1  Power  J2: 10  Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSIO  J1: 19  I/O  Master or s |                    | Table 2: ZDB5101 Z-Wave Development Board Application Connector Layout |       |                                                                |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------------------------------------|-------|----------------------------------------------------------------|--|--|--|

| ADC[3:0]  Analog-to-Digital Converter input. The ADC is 12/8 bit and can use +3.3V, an internal or an external voltage as reference.  ADC3: input ADC2: input ADC1: input/lower reference ADC3: input ADC1: input/lower reference ADC3: input ADC3: input ADC3: input ADC4: input/lower reference ADC5: input/lower reference GND J1: 13 J2: 1, 2  INT1 J1: 6 INT0 J2: 14  INT1 INT0 J2: 14  INT1 INT1 INT1 INT1 INT1 INT1 INT1 INT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Name               | Pin#                                                                   | I/O   | Description                                                    |  |  |  |

| Hand the state of  | +3.3V              | J1: 17                                                                 | Power |                                                                |  |  |  |

| J1: 3 J1: 5 J1: 7 ADC3: input ADC2: input ADC3: input ADC3: input/lower reference ADC0: input/higher reference ADC0: input/higher reference ADC0: input/higher reference ADC0: input/higher reference  GND J1: 13 J2: 1, 2 INT1 J1: 6 I/O Interrupt: The signals are level triggered. When in power down mode, the ZDB5101 Z-Wave Development Board's MCU can be woken by asserting the interrupt signal. P[0.0-0.0], Appendix A for IO pin number P[3.0-3.1] P[3.0-3.1] P[3.4-3.7] MISO1 J1: 10 I/O Master only SPI - Master-In-Slave-Out, and prog interface.  MOSI1 J1: 14 I/O Master only SPI - Master Out Slave In, and prog interface. PWM J1: 3 I Reset: Active low reset. The ZM5101 Z-Wave SiP Module has an integrated Power-On-Reset and Brown-out detection circuitry.  RXD0 J1: 18 I UART Receive Data: Supports up to 230.4kbaud.  Master Only SPI - SPI Clock, and SPI clock for prog interface.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MISO0 J1: 19 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  Mosio J1: 19 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  Mosio J1: 19 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  Mosio J1: 19 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  Mosio J1: 19 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  Mosio J2: 18 I UART Receive Data: Supports up to 230.4kbaud.                                                                                                                                                                                                                                                                                                                                                                                                         | ADC[3:0]           |                                                                        | I     |                                                                |  |  |  |

| J1: 5   J1: 7   ADC2: input   ADC1: input/lower reference   ADC3: input/lower reference   ADC3   |                    |                                                                        |       | l · · ·                                                        |  |  |  |

| GND J1: 13 J2: 1, 2  INT1 J1: 6 INT0 J2: 14  INT0 J2: 14  INT1 J1: 6 INT0 J2: 14  INT0 J2: 14  INT1 J1: 6 INT0 J2: 14  INT0 J2: 15  INT0 J2: 16  INT0 J2: 18  INT |                    |                                                                        |       | ·                                                              |  |  |  |

| GND J1: 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                                                                        |       | ·                                                              |  |  |  |

| GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |                                                                        |       | · ·                                                            |  |  |  |

| INT1 J1: 6 I/O Interrupt: The signals are level triggered. When in power down mode, the ZDB5101 Z-Wave Development Board's MCU can be woken by asserting the interrupt signal.  P[0.0-0.0], P[1.0-1.7] Appendix A for I/O pin number P[3.0-3.1] P[3.4-3.7]  MISO1¹ J1: 10 I/O Master only SPI - Master-In-Slave-Out, and prog interface.  MOSI1¹ J1: 14 I/O Master only SPI - Master Out Slave In, and prog interface.  PWM J1: 3 I Puse Width Modulator Output: Used for frequency variation applications.  RESET_N J1: 15 I Reset: Active low reset. The ZM5101 Z-Wave SiP Module has an integrated Power-On-Reset and Brown-out detection circuitry.  RXD0 J1: 18 I UART Receive Data: Supports up to 230.4kbaud.  SCK1¹ J1: 12 I/O Master only SPI - SPI Clock, and SPI clock for prog interface.  TRIAC J1: 5 O TRIAC Control: A triac control a triac on the Application Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  MOSI0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2712               |                                                                        |       | , ,                                                            |  |  |  |

| INT1 INT0 J1: 6 J2: 14 I/O Interrupt: The signals are level triggered. When in power down mode, the ZDB5101 Z-Wave Development Board's MCU can be woken by asserting the interrupt signal.  P[0.0-0.0], Refer to Appendix A for IO pin number P[3.4-3.7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | GND                |                                                                        | Power | Ground signal                                                  |  |  |  |

| INTO J2: 14 mode, the ZDB5101 Z-Wave Development Board's MCU can be woken by asserting the interrupt signal.  P[0.0-0.0], Refer to P[1.0-1.7] Appendix A for IO pin number P[3.4-3.7] P[3.4-3.7] P[3.4-3.7] MISO1 J1: 10 I/O Master only SPI - Master-In-Slave-Out, and prog interface.  MOSI1 J1: 14 I/O Master only SPI - Master Out Slave In, and prog interface.  PWM J1: 3 I Pulse Width Modulator Output: Used for frequency variation applications.  RESET_N J1: 15 I Reset: Active low reset. The ZM5101 Z-Wave SiP Module has an integrated Power-On-Reset and Brown-out detection circuitry.  RXD0 J1: 18 I UART Receive Data: Supports up to 230.4kbaud.  SCK1 J1: 12 I/O Master only SPI - SPI Clock, and SPI clock for prog interface.  TRIAC J1: 5 O TRIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. Master Out Slave In SPI interface.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | INIT4              |                                                                        | 1/0   | Interrupt: The signals are level triggered. When in newer down |  |  |  |

| Refer to Appendix A for IO pin number P[0.0-0.0], P[1.0-1.7] P[3.0-3.1] P[3.4-3.7] P[3.4 |                    |                                                                        | 1/0   |                                                                |  |  |  |

| P[0.0-0.0], P[1.0-1.7] Appendix A for IO pin number P[3.0-3.1] P[3.0-3.7] P[3 | 11110              | JZ. 14                                                                 |       | ·                                                              |  |  |  |

| P[1.0-1.7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P[0 0-0 0]         | Refer to                                                               | I/O   | · · · ·                                                        |  |  |  |

| P[2.0-2.7], P[3.0-3.1] P[3.4-3.7]  MISO1 J1: 10 I/O Master only SPI - Master-In-Slave-Out, and prog interface.  MOSI1 J1: 14 I/O Master only SPI - Master Out Slave In, and prog interface.  PWM J1: 3 I Pulse Width Modulator Output: Used for frequency variation applications.  RESET_N J1: 15 I Reset: Active low reset. The ZM5101 Z-Wave SiP Module has an integrated Power-On-Reset and Brown-out detection circuitry.  RXD0 J1: 18 I UART Receive Data: Supports up to 230.4kbaud.  SCK1 J1: 12 I/O Master only SPI - SPI Clock, and SPI clock for prog interface.  TRIAC J1: 5 O TRIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    | Appendix A                                                             | ., 0  |                                                                |  |  |  |

| P[3.4-3.7] P[3.4-3.7] P[3.4-3.7] MISO1 <sup>1</sup> J1: 10 I/O Master only SPI - Master-In-Slave-Out, and prog interface.  MOSI1 <sup>1</sup> J1: 14 I/O Master only SPI - Master Out Slave In, and prog interface.  PWM J1: 3 I Pulse Width Modulator Output: Used for frequency variation applications.  RESET_N J1: 15 I Reset: Active low reset. The ZM5101 Z-Wave SiP Module has an integrated Power-On-Reset and Brown-out detection circuitry.  RXD0 J1: 18 I UART Receive Data: Supports up to 230.4kbaud.  SCK1 <sup>1</sup> J1: 12 I/O Master only SPI - SPI Clock, and SPI clock for prog interface.  TRIAC J1: 5 O TRIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module that can control a triac on the Application Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |                                                                        |       |                                                                |  |  |  |

| MISO1 J1: 10 I/O Master only SPI - Master-In-Slave-Out, and prog interface.  MOSI1 J1: 14 I/O Master only SPI - Master Out Slave In, and prog interface.  PWM J1: 3 I Pulse Width Modulator Output: Used for frequency variation applications.  RESET_N J1: 15 I Reset: Active low reset. The ZM5101 Z-Wave SiP Module has an integrated Power-On-Reset and Brown-out detection circuitry.  RXD0 J1: 18 I UART Receive Data: Supports up to 230.4kbaud.  SCK1 J1: 12 I/O Master only SPI - SPI Clock, and SPI clock for prog interface.  TRIAC J1: 5 O TRIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module that can control a triac on the Application Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | P[3.0-3.1]         | number                                                                 |       |                                                                |  |  |  |

| MOSI1 <sup>1</sup> J1: 14 I/O Master only SPI - Master Out Slave In, and prog interface.  PWM J1: 3 I Pulse Width Modulator Output: Used for frequency variation applications.  RESET_N J1: 15 I Reset: Active low reset. The ZM5101 Z-Wave SiP Module has an integrated Power-On-Reset and Brown-out detection circuitry.  RXD0 J1: 18 I UART Receive Data: Supports up to 230.4kbaud.  SCK1 <sup>1</sup> J1: 12 I/O Master only SPI - SPI Clock, and SPI clock for prog interface.  TRIAC J1: 5 O TRIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module that can control a triac on the Application Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P[3.4-3.7]         |                                                                        |       |                                                                |  |  |  |

| PWM J1: 3 I Pulse Width Modulator Output: Used for frequency variation applications.  RESET_N J1: 15 I Reset: Active low reset. The ZM5101 Z-Wave SiP Module has an integrated Power-On-Reset and Brown-out detection circuitry.  RXD0 J1: 18 I UART Receive Data: Supports up to 230.4kbaud.  SCK1¹ J1: 12 I/O Master only SPI - SPI Clock, and SPI clock for prog interface.  TRIAC J1: 5 O TRIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module that can control a triac on the Application Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MISO1 <sup>1</sup> | J1: 10                                                                 | I/O   | Master only SPI - Master-In-Slave-Out, and prog interface.     |  |  |  |

| Applications.  RESET_N J1: 15 I Reset: Active low reset. The ZM5101 Z-Wave SiP Module has an integrated Power-On-Reset and Brown-out detection circuitry.  RXD0 J1: 18 I UART Receive Data: Supports up to 230.4kbaud.  SCK1¹ J1: 12 I/O Master only SPI - SPI Clock, and SPI clock for prog interface.  TRIAC J1: 5 O TRIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module that can control a triac on the Application Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MOSI1 <sup>1</sup> | J1: 14                                                                 | 1/0   | Master only SPI - Master Out Slave In, and prog interface.     |  |  |  |

| integrated Power-On-Reset and Brown-out detection circuitry.  RXD0 J1: 18 I UART Receive Data: Supports up to 230.4kbaud.  SCK1¹ J1: 12 I/O Master only SPI - SPI Clock, and SPI clock for prog interface.  TRIAC J1: 5 O TRIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module that can control a triac on the Application Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PWM                | J1: 3                                                                  | I     |                                                                |  |  |  |

| RXD0 J1: 18 I UART Receive Data: Supports up to 230.4kbaud.  SCK1¹ J1: 12 I/O Master only SPI - SPI Clock, and SPI clock for prog interface.  TRIAC J1: 5 O TRIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module that can control a triac on the Application Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RESET_N            | J1: 15                                                                 | I     | Reset: Active low reset. The ZM5101 Z-Wave SiP Module has an   |  |  |  |

| SCK1 J1: 12 I/O Master only SPI - SPI Clock, and SPI clock for prog interface.  TRIAC J1: 5 O TRIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module that can control a triac on the Application Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |                                                                        |       | integrated Power-On-Reset and Brown-out detection circuitry.   |  |  |  |

| TRIAC J1: 5 O TRIAC Control: A triac controller is implemented in the ZM5101 Z-Wave SiP Module that can control a triac on the Application Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    | J1: 18                                                                 | l     | UART Receive Data: Supports up to 230.4kbaud.                  |  |  |  |

| Z-Wave SiP Module that can control a triac on the Application Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SCK1 <sup>1</sup>  | J1: 12                                                                 | I/O   | Master only SPI - SPI Clock, and SPI clock for prog interface. |  |  |  |

| Module like light dimmer modules etc.  TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TRIAC              | J1: 5                                                                  | 0     |                                                                |  |  |  |

| TXD0 J1: 16 O UART Transmit Data: Supports up to 230.4kbaud.  ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |                                                                        |       |                                                                |  |  |  |

| ZEROX J1: 3 I Zero Cross Detection: Used on dimmer modules for detecting 120/240V zero crossing.  VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |                                                                        |       |                                                                |  |  |  |

| VPP J1: 1 Power OTP programmable voltage  TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |                                                                        | 0     | · · · ·                                                        |  |  |  |

| VPPJ1: 1PowerOTP programmable voltageTXD1J2: 16OUART Transmit Data: Supports up to 230.4kbaud.MISO0J1: 2I/OMaster or slave SPI. Master-In-Slave-Out SPI interface.MOSI0J1: 8I/OMaster or slave SPI. Master Out Slave In SPI interface.SCK0J1: 19I/OMaster or slave SPI. SPI ClockRXD1J2: 18IUART Receive Data: Supports up to 230.4kbaud.USB-DMJ1: 9I/OUSB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ZEROX              | J1: 3                                                                  | I     |                                                                |  |  |  |

| TXD1 J2: 16 O UART Transmit Data: Supports up to 230.4kbaud.  MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                                                                        | _     |                                                                |  |  |  |

| MISO0 J1: 2 I/O Master or slave SPI. Master-In-Slave-Out SPI interface.  MOSI0 J1: 8 I/O Master or slave SPI. Master Out Slave In SPI interface.  SCK0 J1: 19 I/O Master or slave SPI. SPI Clock  RXD1 J2: 18 I UART Receive Data: Supports up to 230.4kbaud.  USB-DM J1: 9 I/O USB differential input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |                                                                        |       |                                                                |  |  |  |