# AG32 MCU

# **Reference Manual**

1.2

# contents

| 1 De | evice overview                                                 | 10 |

|------|----------------------------------------------------------------|----|

| 1.1  | Introduction                                                   | 10 |

| 1.1  | 1.1 System Overview                                            |    |

| 1.1  | 1.2 Clock, reset and supply management                         | 10 |

| 1.1  | 1.3 Low-power operation                                        |    |

| 1.1  | 1.4 ADC/DAC/CMP/DMA/Timers/GPIO                                |    |

|      | 1.5 Communication interfaces                                   |    |

| 1.1  | 1.6 Others                                                     | 11 |

| 1.2  | Features and peripheral counts                                 | 12 |

| 1.3  | Chip architecture                                              | 13 |

| 1.4  | Memory Map                                                     | 14 |

| 1.5  | System Control                                                 | 14 |

| 2 Pi | in Definition                                                  | 22 |

| 3 CI | lock                                                           | 29 |

| 3.1  | Clock sources                                                  | 29 |

| 3.2  | HSE clock                                                      | 30 |

| 3.3  | HSI clock                                                      | 31 |

| 3.4  | PLL clock                                                      |    |

| 3.5  | LSE clock                                                      | 32 |

| 3.6  | LSI clock                                                      | 32 |

| 3.7  | System clock (SYSCLK) selection                                | 32 |

| 3.8  | RTC clock                                                      | 32 |

| 3.9  | Watchdog clock                                                 | 33 |

| 4 Re | eset                                                           | 34 |

| 4.1  | System reset                                                   |    |

| 4.2  | Power reset                                                    | 35 |

| 4.3  | Backup domain reset                                            | 35 |

| 5 Pc | ower control                                                   | 36 |

| 5.1  | Power supplies                                                 | 36 |

| 5.2  | Independent ADC and DAC converter supply and reference voltage | 36 |

| 5.3  | Battery backup domain                                          | 37 |

| 5.4  | Voltage regulator                                              | 37 |

| į | 5.5   | Power on reset (POR)/power down reset (PDR) | 37                |

|---|-------|---------------------------------------------|-------------------|

| 5 | 5.6   | Low-power modes                             | 38                |

|   | 5.6.3 |                                             |                   |

|   | 5.6.2 |                                             |                   |

|   | 5.6.3 | 3 Sleep mode                                | 39                |

|   | 5.6.4 |                                             |                   |

|   | 5.6.  |                                             |                   |

|   | 5.6.6 |                                             |                   |

| 6 | Inte  | errupt Controller                           | 43                |

| ( | 5.1   | Local interrupts                            | 43                |

| ( | 5.2   | External interrupts                         | 43                |

| 6 | 5.3   | Overall priority                            | 45                |

| 6 | 5.4   | Interrupt enable                            | 45                |

| 6 | 6.5   | Interrupt registers                         | 45                |

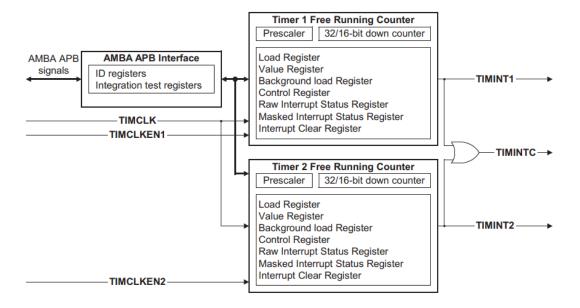

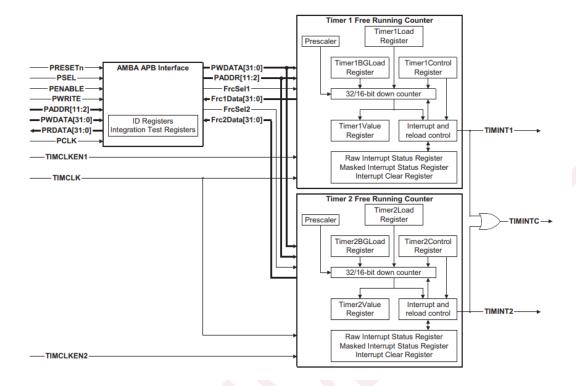

| 7 | Duc   | al Timer(Basic Timers)                      | 47                |

| 7 | 7.1   | Introduction                                | 47                |

| 7 | 7.2   | Functional Overview                         | 48                |

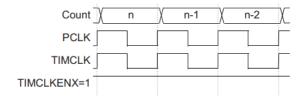

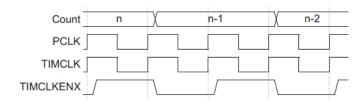

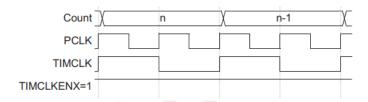

|   | 7.2.  |                                             | <del></del><br>48 |

|   | 7.2.2 |                                             |                   |

| _ |       |                                             |                   |

| 4 | 7.3   | Programmer's Model                          |                   |

|   | 7.3.  | 1 ummary of registers                       | 50                |

| 7 | 7.4   | Register descriptions                       | 57                |

| 8 | Adı   | vanced-control timers                       | 61                |

| 8 | 3.1   | Introduction                                | 61                |

| 8 | 3.2   | Main features                               | 61                |

| 8 | 3.3   | Functional description                      | 63                |

|   | 8.3.  |                                             |                   |

|   | 8.3.  |                                             |                   |

|   | 8.3.3 |                                             |                   |

|   | 8.3.4 |                                             |                   |

|   | 8.3.5 | 5 Capture/compare channels                  | 84                |

|   | 8.3.6 |                                             |                   |

|   | 8.3.  |                                             |                   |

|   | 8.3.8 |                                             |                   |

|   | 8.3.9 |                                             |                   |

|   | 8.3.  |                                             |                   |

|   | 8.3.  |                                             |                   |

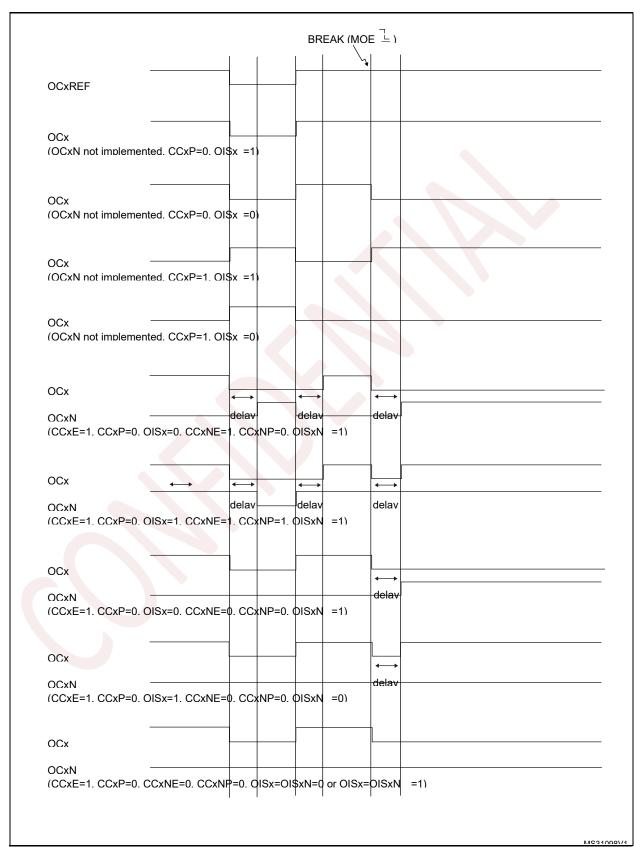

|   | 8.3.  | 12 Using the break function                 | 98                |

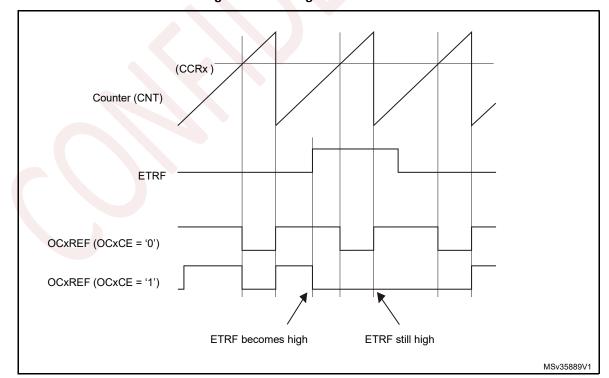

| 8.3.13 | Clearing the OCxREF signal on an external event |     |

|--------|-------------------------------------------------|-----|

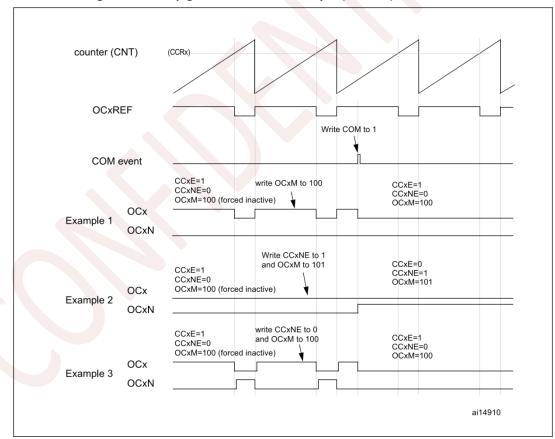

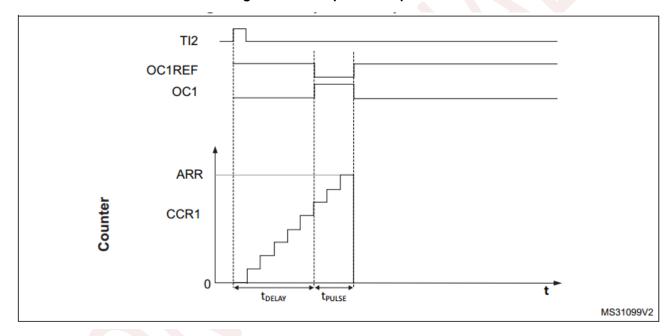

| 8.3.14 |                                                 |     |

| 8.3.15 | •                                               |     |

| 8.3.16 |                                                 |     |

| 8.3.17 |                                                 |     |

| 8.3.18 |                                                 |     |

| 8.3.19 |                                                 |     |

| 8.3.20 | ,                                               |     |

| 8.3.21 | Debug mode                                      | 113 |

| 8.4 r  | egisters                                        | 114 |

| 8.4.1  | control register 1 (CR1)                        | 114 |

| 8.4.2  | control register 2 (CR2)                        | 115 |

| 8.4.3  | slave mode control register (SMCR)              | 117 |

| 8.4.4  | DMA/interrupt enable register (DIER)            | 120 |

| 8.4.5  | status register (SR)                            | 122 |

| 8.4.6  | event generation register (EGR)                 | 124 |

| 8.4.7  | capture/compare mode register 1 (CCMR1)         | 125 |

| 8.4.8  | capture/compare mode register 2 (CCMR2)         | 128 |

| 8.4.9  | capture/compare enable register (CCER)          | 130 |

| 8.4.10 | counter (CNT)                                   | 133 |

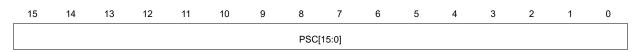

| 8.4.11 | prescaler (PSC)                                 | 133 |

| 8.4.12 | auto-reload register (ARR)                      | 134 |

| 8.4.13 | repetition counter register (RCR)               | 134 |

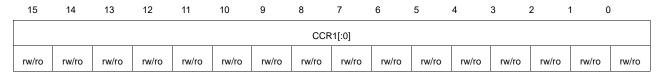

| 8.4.14 | capture/compare register 1 (CCR0)               | 135 |

| 8.4.15 | capture/compare register 2 (CCR1)               | 135 |

| 8.4.16 | capture/compare register 3 (CCR2)               | 136 |

| 8.4.17 | capture/compare register 4 (CCR3)               | 136 |

| 8.4.18 | break and dead-time register (BDTR)             | 137 |

| 8.4.19 | register map                                    | 139 |

| 9 Watc | hdogs                                           | 142 |

|        |                                                 |     |

| 9.1    | Overview                                        | 142 |

| 9.2 l  | ndependent watchdog (IWDG)                      | 142 |

| 9.2.1  | IWDG main features                              | 142 |

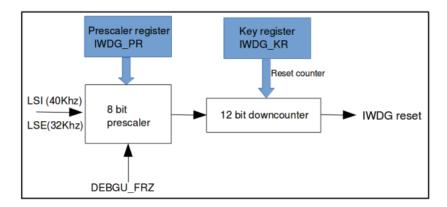

| 9.2.2  | IWDG functional description                     | 142 |

| 9.2.3  | Watchdog clock                                  | 143 |

| 9.2.4  | Debug mode                                      | 143 |

| 9.2.5  | IWDG registers                                  | 144 |

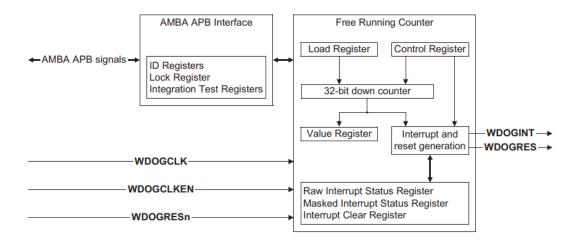

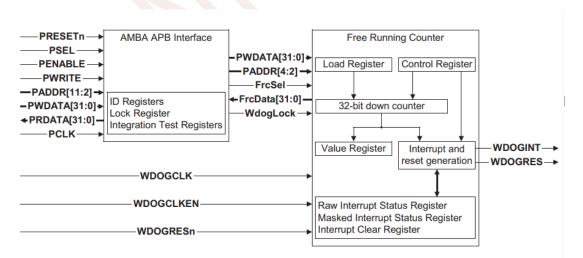

| 9.3 F  | unctional overview                              | 145 |

| 9.3.1  | Features                                        |     |

| 9.3.2  | Watchdog module overview                        |     |

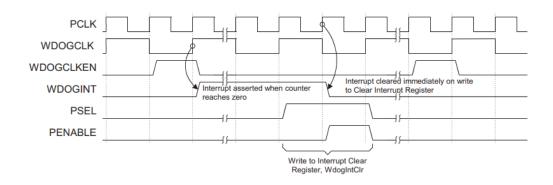

| 9.3.3  | Functional description                          |     |

| 9.3.4  | Operation                                       |     |

|        |                                                 |     |

| 9.3.        | , c                                 |     |

|-------------|-------------------------------------|-----|

| 9.3.        |                                     |     |

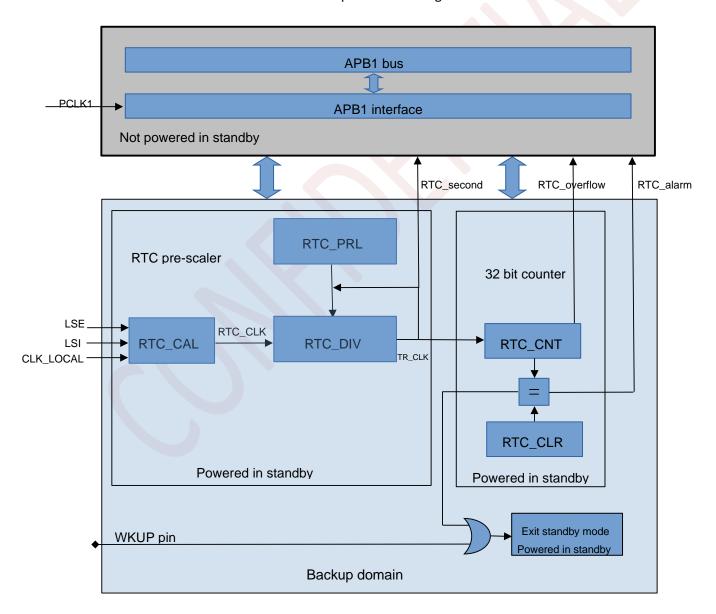

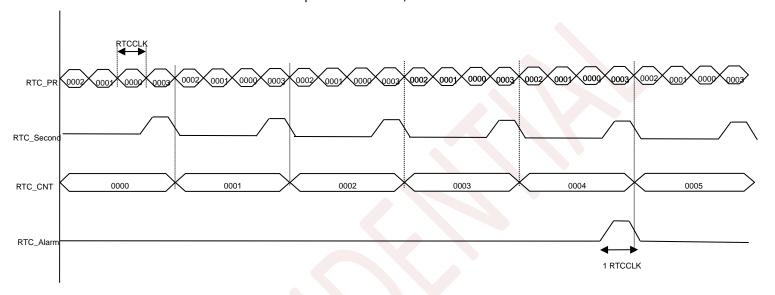

|             | Real-time clock (RTC)               | 153 |

| 10.1        | RTC main features:                  |     |

| 10.2        | RTC functional description          | 154 |

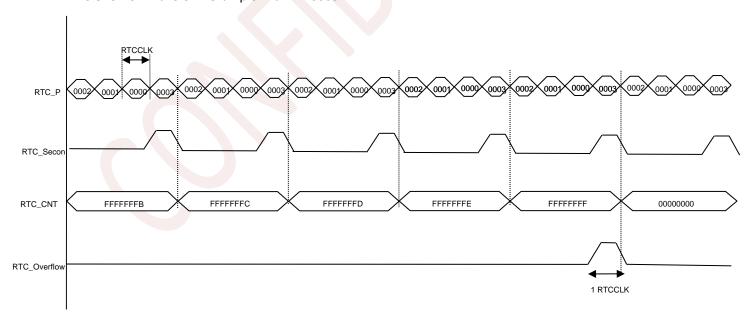

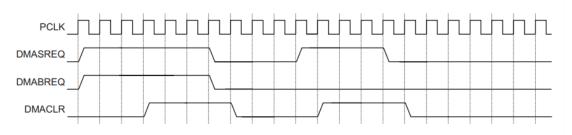

| 11 E        | OMA                                 | 157 |

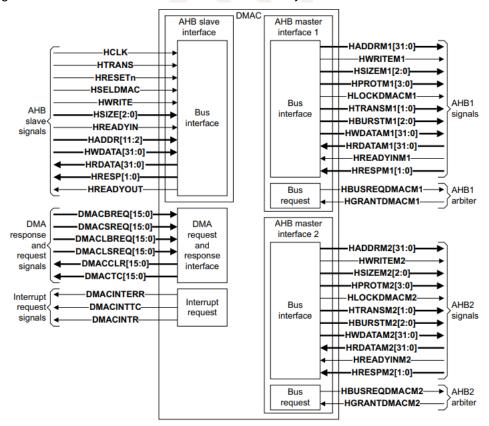

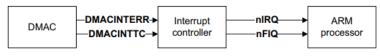

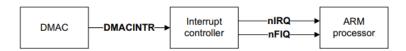

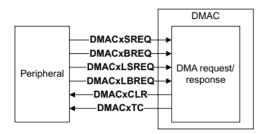

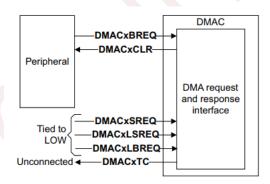

| 11.1        | Overview                            | 157 |

| 11.2        | Functional Overview                 | 158 |

| 11.2        |                                     |     |

| 11.2        | 2.2 System considerations           | 161 |

| 11.2        | 2.3 System connectivity             | 162 |

| 11.2        | 2.4 Software considerations         | 165 |

| 11.3        | Programmer's Model                  | 167 |

| 11.3        |                                     | 167 |

| 11.3        |                                     |     |

| 11.3        | 3.3 Summary of registers            | 169 |

| 11.3        |                                     |     |

| 11.3        | 3.5 Test registers                  | 190 |

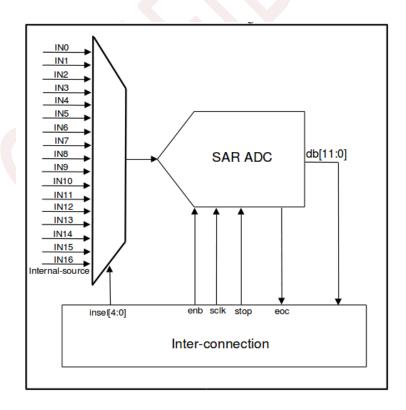

| 12 <i>A</i> | Analog-to-digital converter (ADC)   | 193 |

| 12.1        | Overview                            | 193 |

| 12.2        | Pins and internal signals           | 193 |

| 12.3        | Temperature sensor                  | 194 |

| 12.4        | ADC block pins                      | 194 |

| 12.5        | ADC input signals vs package pins   | 196 |

| 12.6        | ADC characteristics                 | 197 |

| 12.7        | ADC timing diagram                  | 197 |

| 13 E        | Digital-to-analog converter (DAC)   | 199 |

| 13.1        | Overview                            |     |

| 13.2        | DAC block pins                      |     |

| 13.3        | DAC pins                            |     |

| 13.4        | DACs output signals vs package pins | 200 |

| 13.5        | DAC characteristics                 |     |

| 13.6        | DAC output voltage                  | 201 |

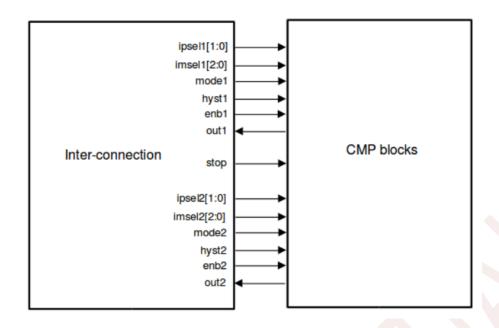

| 14 (        | Comparator (CMP)                    |     |

| 14.1        | Overview                            |     |

|             |                                     |     |

| 14.2 | Characteristic                                     | 202 |

|------|----------------------------------------------------|-----|

| 14.3 | CMP block pins                                     |     |

| 14.4 | CMP input signals vs package pins                  |     |

|      |                                                    |     |

| 14.5 | Comparator characteristics                         |     |

|      | Backup registers (BKP)                             |     |

| 16 C | CRC(Cyclic redundancy check calculation unit )     | 211 |

| 16.1 | Introduction                                       | 211 |

| 16.2 | CRC main features                                  | 211 |

| 16.3 | CRC functional description                         |     |

| 16.3 |                                                    |     |

| 16.3 |                                                    |     |

| 16.3 | 3.3 CRC operation                                  | 212 |

| 16.4 | CRC registers                                      |     |

| 16.4 |                                                    |     |

| 16.4 |                                                    |     |

| 16.4 |                                                    |     |

| 16.4 |                                                    | 215 |

| 16.4 | 4.5 CRC polynomial (CRC_POL)                       | 216 |

| 16.4 | 4.6 CRC register map                               | 216 |

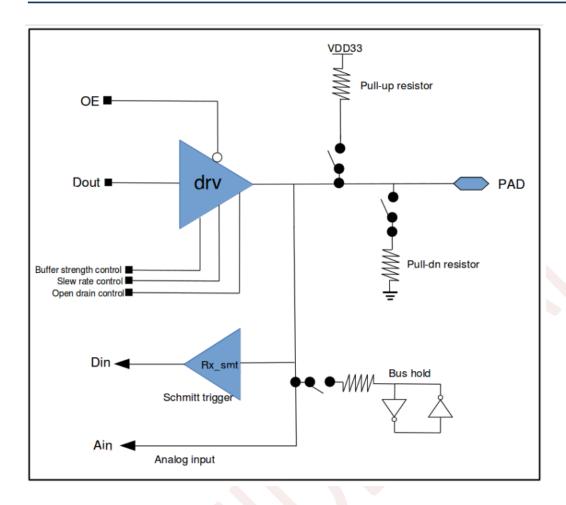

| 17 6 | General-purpose input/outputs (GPIOs)              | 218 |

| 17.1 | Overview                                           | 218 |

| 17.2 | Functional description                             | 218 |

| 17.3 | Register descriptions                              | 220 |

| 17.3 | 3.1 Data register, GPIODATA                        | 220 |

| 17.3 |                                                    |     |

| 17.3 | 3.3 Interrupt sense register, GPIOIS               | 221 |

| 17.3 | 3.4 Interrupt both-edges register, GPIOIBE         | 221 |

| 17.3 | 3.5 Interrupt event register, GPIOIEV              | 221 |

| 17.3 |                                                    |     |

| 17.3 |                                                    |     |

| 17.3 |                                                    |     |

| 17.3 |                                                    |     |

| 17.3 | 3.10 Mode control select register, GPIOAFSEL       | 223 |

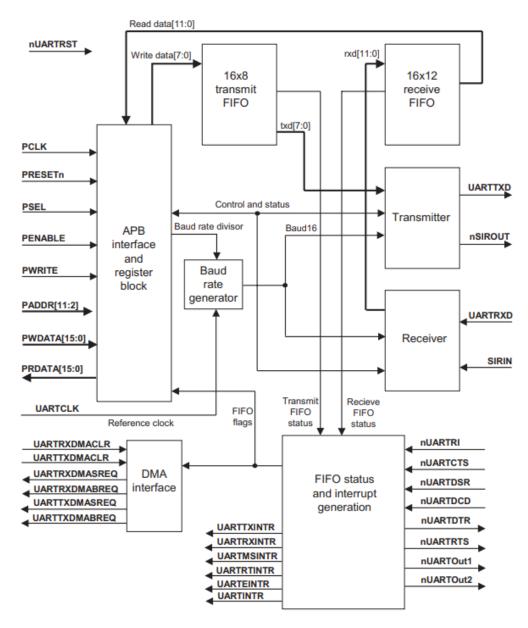

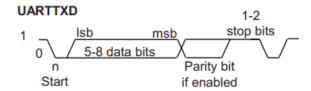

| 18 L | Universal asynchronous receiver transmitter (UART) | 224 |

| 18.1 | UART Introduction                                  | 224 |

| 18.2 | UART functional description                        | 224 |

| 18.3 | Operation                                          |     |

| 18.3 |                                                    |     |

| 18.3  | 3.2 Clock signals          | 227       |

|-------|----------------------------|-----------|

| 18.3  |                            | 227       |

| 18.3  |                            | 230       |

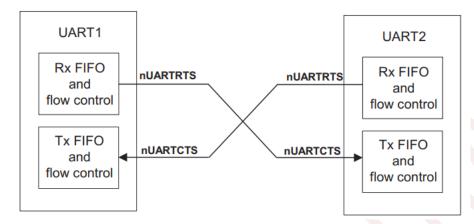

| 18.4  | UART modem operation       | 230       |

| 18.5  | UART hardware flow con     | trol 231  |

| 18.6  |                            | 232       |

| 18.7  |                            | 234       |

| 18.7  |                            | 234       |

| 18.7  |                            | 234       |

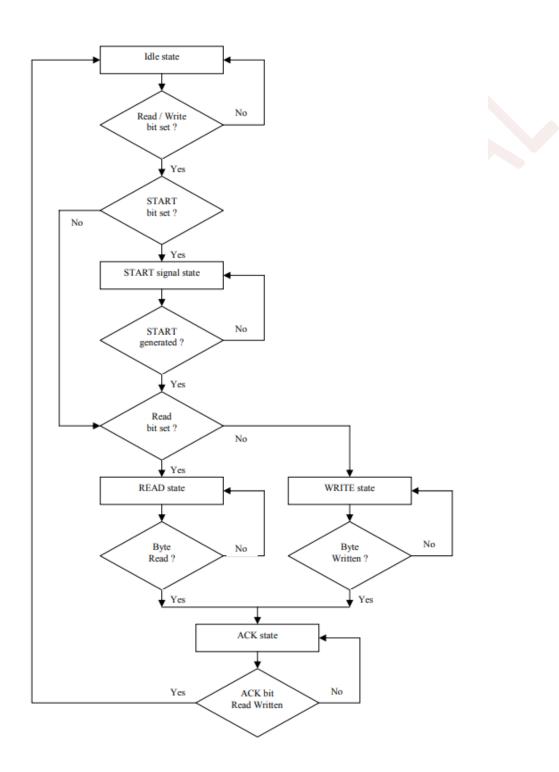

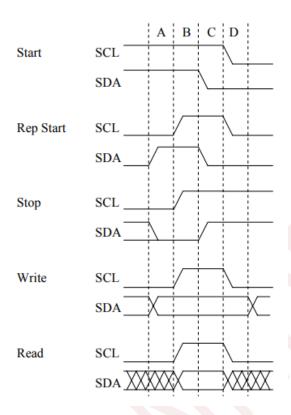

| 19 II |                            | 248       |

| 19.1  | -                          | 248       |

| 19.2  |                            | 248       |

| 19.3  |                            | 250       |

| 19.3  |                            | 250       |

| 19.3  |                            |           |

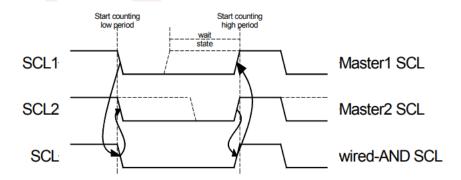

| 19.3  | 2.2 Arbitration Procedure  |           |

|       |                            |           |

|       |                            | 253       |

| 19.4  |                            |           |

| 19.4  | 1.2 Register description   | 253       |

| 20 C  | Controller area network (  | (CAN)256  |

| 20.1  | Overview                   | 256       |

| 20.2  |                            | 257       |

| 20.2  | 2.1 Configuration          | 257       |

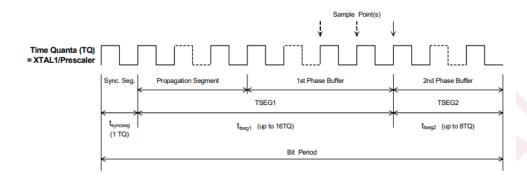

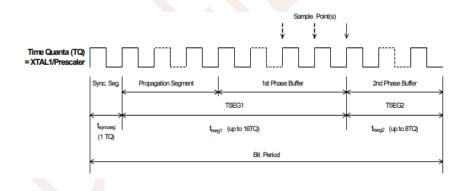

| 20.2  | 2.2 Bus Timing Parameters  |           |

| 20.2  | 2.3 Acceptance Filters     | 258       |

| 20.2  | 2.4 Interrupts             | 259       |

| 20.2  |                            | 259       |

| 20.2  | 2.6 Output Mode            | 259       |

| 20.2  | 2.7 CLKOUT Signal          | 260       |

| 20.2  | 2.8 Example Configuration  | Steps 260 |

| 20.3  | Interrupt Handling         | 260       |

| 20.3  | 3.1 Receive Interrupt      | 261       |

| 20.3  | 3.2 Transmit Interrupt     | 261       |

| 20.3  | 3.3 Error Warning Interrup | t 261     |

| 20.3  | 3.4 Data Overrun Interrupt | 262       |

| 20.3  | 3.5 Wake-up Interrupt      | 262       |

| 20.3  |                            | 262       |

| 20.3  |                            | pt 263    |

| 20.3  |                            | 263       |

| 20.4 | Sleep Mode                                                   | : |

|------|--------------------------------------------------------------|---|

| 20.5 | Register Description                                         | : |

| 20.5 | 1 Acceptance Code Registers (ACR0 – ACR3): ADDRESS 10h – 13h |   |

| 20.5 | 2 Acceptance Mask Registers (AMR0 – AMR3): ADDRESS 14h – 17h |   |

| 20.5 | 3 Arbitration Lost Capture Register (ALC): ADDRESS 0Bh       |   |

| 20.5 | 4 Bus Timing Register 0 (BTR0): ADDRESS 06h                  |   |

| 20.5 | 5 Bus Timing Register 1 (BTR1): ADDRESS 07h                  |   |

| 20.5 | 6 Clcck Divider Register (CDR): ADDRESS 1Fh                  |   |

| 20.5 | 7 Command Register (CMR): ADDRESS 01h                        |   |

| 20.5 | 8 Error Code Capture Register (ECC): ADDRESS OCH             |   |

| 20.5 | 9 Error Warning Limit Register (EWLR): ADDRESS 0Dh           |   |

| 20.5 | 10 Interrupt Register (IR): ADDRESS 03h                      |   |

| 20.5 | 11 Interrupt Enable Register(IER): ADDRESS 04h               |   |

| 20.5 | 12 Mode Register (MOD): ADDRESS 00h                          |   |

| 20.5 | 13 Output Control Register (OCR): ADDRESS 08h                |   |

| 20.5 | 14 Receive Buffer (10h – 1Ch)                                |   |

| 20.5 | 15 Receive Buffer Start Address (RBSA): ADDRESS 1Eh          |   |

| 20.5 | 16 Receive Error Counter Register (RXERR): ADDRESS 0Eh       |   |

| 20.5 | 17 Receive Message Counter (RMC): ADDRESS 1Dh                |   |

| 20.5 | 18 Status Register(SR): ADDRESS 02h                          |   |

| 20.5 | 19 Transmit Buffer (Write: 10h – 1Ch; Read: 60h – 6Ch)       |   |

| 20.5 | 20 Transmit Error Counter Register (TXERR): ADDRESS 0Fh      |   |

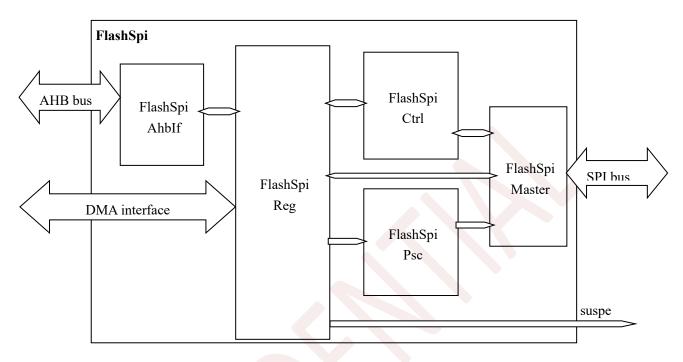

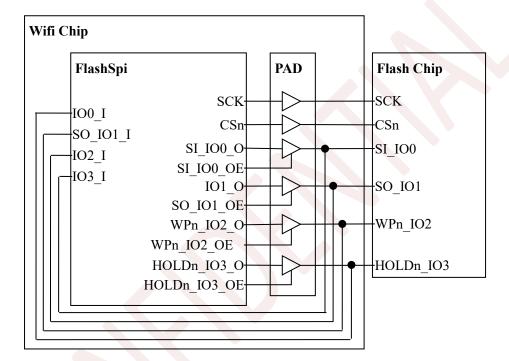

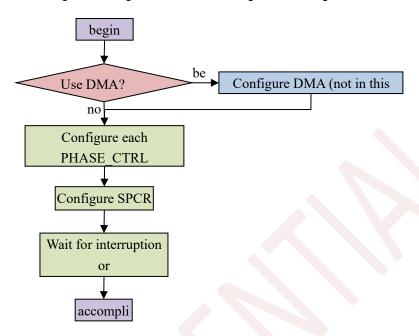

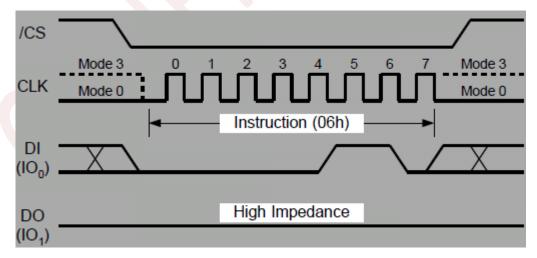

| 1 FI | ash-SPI control                                              | 2 |

| 21.1 | Overview                                                     | : |

| 21.1 | 1 Characteristics of this spi controller                     |   |

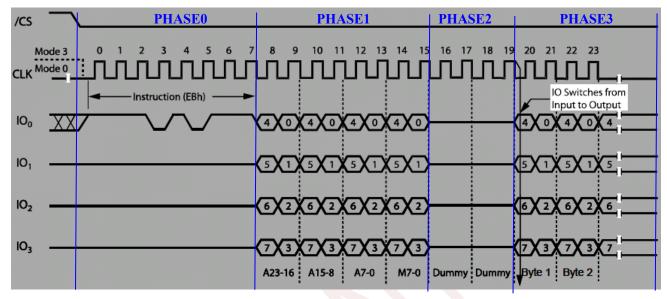

| 21.1 | 2 The concept of PHASE                                       |   |

| 21.1 | 3 Module block diagram                                       |   |

| 21.1 | 4 Top port                                                   |   |

| 21.2 | Instructions for use of the module                           |   |

| 21.2 | 1 System integration method                                  |   |

| 21.2 | 2 register description                                       |   |

| 21.2 | 3 Description of PHASE_ACTION                                |   |

| 21.2 | 1 Software configuration sequence                            |   |

| 2 0  | ther Interfaces                                              |   |

| 22.1 | Universal serial bus full-speed device interface (USBD)      |   |

| 22.2 | Ethernet MAC interface                                       |   |

| 22.3 | Debug mode                                                   |   |

|      | ectrical characteristics                                     |   |

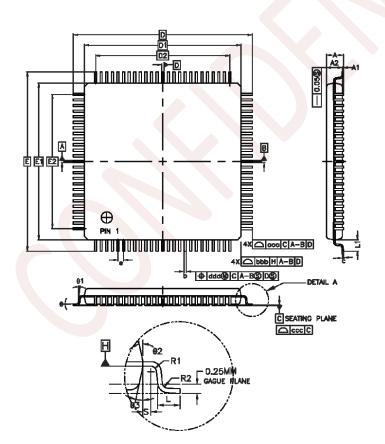

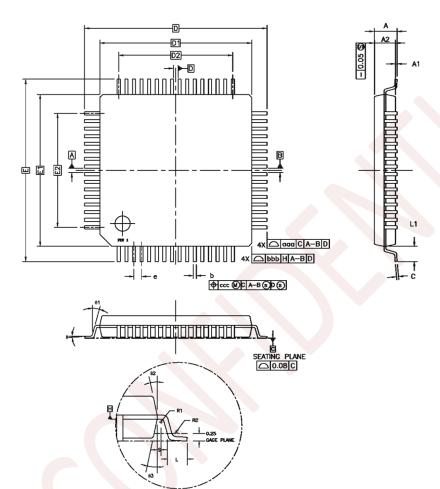

|      | ackage and operation temperature                             |   |

|      |                                                              |   |

| '5 O | rder Information                                             | ; |

26 Revision history \_\_\_\_\_\_312

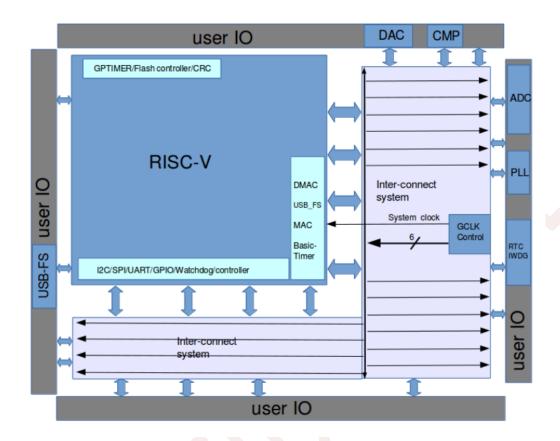

#### 1 Device overview

#### 1.1 Introduction

The AG32 family of 32-bit microcontrollers is designed to offer new degrees of freedom and rich compatible peripherals, and compatible pin and features to MCU users. AG32 product series offers supreme quality, stability, and exceptional pricing value.

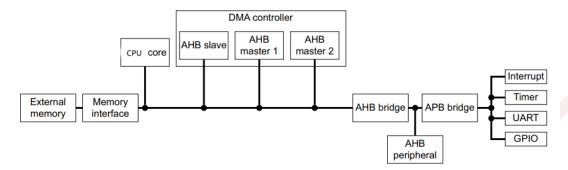

#### 1.1.1 System Overview

- RISC-V core with RV32IMAFC support

- Up to 1 Mbyte of Flash memory

- 128KB SRAM

- 16KB instruction cache

#### 1.1.2 Clock, reset and supply management

- 3.135 V to 3.465 V application supply and I/Os

- POR, PDR

- 4-to-26 MHz crystal oscillator

- Internal 20MHz oscillator

- 32 kHz oscillator for RTC

- Internal 40 kHz oscillator

#### 1.1.3 Low-power operation

- Sleep, Stop and Standby modes

- VBAT supply for RTC

# 1.1.4 ADC/DAC/CMP/DMA/Timers/GPIO

- 3×12-bit, 1.0 MSPS A/D converters: up to 16 channels and 3 MSPS in triple interleaved mode

- 2×10-bit D/A converters

- Two rail-to-rail analog comparators

- General-purpose DMA

- Advanced-control timers

- Up to 78 user I/O ports

#### 1.1.5 Communication interfaces

- I2C interfaces

- UART interfaces

- SPI interfaces

- CAN interfaces

#### **1.1.6** Others

- Debug mode Serial wire debug (SWD) & JTAG interfaces

- USB 2.0 full-speed device/host controller with on-chip PHY

- 10/100 Ethernet MAC with dedicated DMA supports MII/RMII

- RTC: subsecond accuracy

- 128-bit unique ID

# 1.2 Features and peripheral counts

| Peripherals            | ls AG32VF303KCU6 AG32VF303CCT6 AG32 |                  | AG32VF303VCT6   | AG32VH407RCT6     | AG32VF407RGT6 | AG32VF407VGT6 |  |  |  |  |

|------------------------|-------------------------------------|------------------|-----------------|-------------------|---------------|---------------|--|--|--|--|

| Flash memory in Kbytes | sh memory in Kbytes 256K 256K 2     |                  | 256K            | 256K              | 1024K         | 1024K         |  |  |  |  |

| SRAM in Kbytes         |                                     | 128K             |                 |                   |               |               |  |  |  |  |

| PSRAM                  |                                     | /                |                 | 8MB /             |               |               |  |  |  |  |

| Ethernet               |                                     |                  | У               | es                |               |               |  |  |  |  |

| Timers                 |                                     | 2                | x Basic Timer + | 5 x Advanced Time | er            |               |  |  |  |  |

| SPI/I <sup>2</sup> C   |                                     |                  |                 | 2                 |               |               |  |  |  |  |

| UART                   |                                     |                  | ļ               | 5                 |               |               |  |  |  |  |

| USB FS                 |                                     |                  | У               | es                |               |               |  |  |  |  |

| CAN                    |                                     |                  | 1 x C           | AN2.0             |               |               |  |  |  |  |

| 12-bit ADC             | 3                                   | 3                | 3               | 3                 | 3             | 3             |  |  |  |  |

| Number of channels     | 9                                   | 10               | 16              | 11                | 16            | 16            |  |  |  |  |

| 10-bit DAC             |                                     |                  |                 | 2                 |               |               |  |  |  |  |

| Number of channels     |                                     |                  |                 | 2                 |               |               |  |  |  |  |

| rail-to-rail analog    | 2                                   | 2                | 2               | 2                 | 2             | 2             |  |  |  |  |

| comparators            | 2                                   | 2                |                 | 2                 | 2             | 2             |  |  |  |  |

| Maximum CPU frequency  | 248Mhz                              |                  |                 |                   |               |               |  |  |  |  |

| Operating voltage      |                                     | 3.135 to 3.465 V |                 |                   |               |               |  |  |  |  |

| Package                | QFN32                               | LQFP48           | LQFP100         | LQFP64            | LQFP64        | LQFP100       |  |  |  |  |

#### AG32VH407RCT6: AG32 + PSRAM

- MCU + 2K CPLD + 8MB PSRAM

- HyperRAM high-speed interface

- DMA & FIFO R/W reference design

# 1.3 Chip architecture

# 1.4 Memory Map

|                 | Address                   |  |

|-----------------|---------------------------|--|

| ROM             | 0x0001 0000 - 0x0001 1FFF |  |

| System Control  | 0x0300 0000 - 0x0300 0FFF |  |

| PLIC            | 0x0C00 0000 - 0x0C20 FFFF |  |

| SRAM            | 0x2000 0000 - 0x2001 FFFF |  |

| FLASH (XIP)     | 0x8000 0000 - 0x80FF FFFF |  |

| Option bytes    | 0x8100 0000 - 0x8100 003F |  |

| RTC             | 0x4000 0000 - 0x4000 007F |  |

| FLASH control   | 0x4000 1000 - 0x4000 1FFF |  |

| APB Peripherals | 0x4001 0000 - 0x40FF FFFF |  |

| AHB Peripherals | 0x4100 0000 - 0x41FF FFFF |  |

| External AHB    | 0x6000 0000 - 0x7FFF FFFF |  |

# 1.5 System Control

# Device boot mode (BOOT\_MODE)

Address offset: 0x00

| 31 - 2   | 1      | 0    |

|----------|--------|------|

| Reserved | BOOT_N | ИODE |

|          | RO     | RO   |

Bit [1:0]: Device boot mode

The values of BOOT0 and BOOT1 pins are latched on the 4th rising edge of SYSCLK after a reset **Reset control (RST\_CNTL)**

Address offset: 0x04

Bit 31 RSTF\_LPWR: Reset flag by low power

0: No reset detected

- 1: Low power reset detected

- Bit 30 RSTF\_WDOG: Reset flag by watch dog

- 0: No reset detected

- 1: Watch dog reset detected

- Bit 29 RSTF\_IWDG: Reset flag by independent watch dog

- 0: No reset detected

- 1: Independent watch dog reset detected

- Bit 28 RSTF\_SFT: Reset flag by softare

- 0: No reset detected

- 1: Softare reset detected

- Bit 27 RSTF\_POR: Reset flag by power on reset

- 0: No reset detected

- 1: Power on reset detected

- Bit 26 RSTF\_PIN: Reset flag by NRST pin

- 0: No reset detected

- 1: NRST pin reset detected

- Bit 25 RSTF\_EXT: Reset flag by external logic

- 0: No reset detected

- 1: External logic reset detected

- Bit 24 RST\_REMOVE: Reset flag removal

- Write 1 to clear all reset flags

- Bit 1 RST\_EXT\_EN: External logic reset enable

0: Exernal logic reset disabled

1: External logic reset enabled

Bit 0 RST\_SFT: Reset by software

Write 1 to trigger software reset

#### Power control (PWR\_CNTL)

Address offset: 0x08

Bit [1:0] LPWR\_MODE: Low power mode

00: Enter sleep mode with WFI (wait for interrupt) instruction

01: Enter stop mode with WFI instruction

11: Enter standby mode with WFI instruction

#### Clock control (CLK\_CNTL)

Address offset: 0x0C

Bit [15:12] SCLK\_DIV\_HIGH: Flash SPI clock divider high

Flash SPI clock is divided by (SCLK\_DIV\_HIGH + 1) from SYS\_CLK, valid range is

from 0 (divided by 1) to 15 (divided by 16)

Bit [11:8] SCLK\_DIV\_LOW: Flash SPI clock divider low

Must be set to the same value as SCLK\_DIV\_HIGH

Bit 6 PLL\_RDY: PLL ready

0: PLL is not ready

1: PLL is ready

Bit 5 PLL\_ON: PLL on

0: PLL is turned off

1: PLL is turned on

Bit 4 HSE\_RDY: HSE ready

0: HSE is not ready

1: HSE is ready

Bit 3 HSE\_BYP: HSE bypass

0: HSE oscillator is not bypassed

1: HSE oscillator is bypassed

Bit 2 HSE\_ON: HSE on

0: HSE oscillator is turned off

1: HSE oscillator is turned on

## JTAG control (SWJ\_CNTL)

Address offset: 0x14

Bit 4: NJTRST: Configuration for pin NJTRST

0: NJTRST is used as a dedicated pin

1: NJTRST is used as a user pin

Bit 3: JTDO: Configuration for pin JTDO

0: JTDO is used as a dedicated pin

1: JTDO is used as a user pin

Bit 2: JTDI: Configuration for pin JTDI

0: JTDI is used as a dedicated pin

1: JTDI is used as a user pin

Bit 1: JTMS: Configuration for pin JTMS

0: JTMS is used as a dedicated pin

1: JTMS is used as a user pin

Bit 0: JTCK: Configuration for pin JTCK

0: JTCK is used as a dedicated pin

1: JTCK is used as a user pin

#### Debug control (DBG\_CNTL)

Address offset: 0x1C

Bit 4 DBG\_RTC\_STOP: Stop RTC during debug

Bit 3 DBG\_IWDG\_STOP: Stop IWDG during debug

#### Wake up rise triggers (WKP\_RISE\_TRG)

Address offset: 0x20

Bit [7:0] EXT\_INTO-7: Wake up device from stop mode using EXT\_INTO-7, rising edge

triggered

Bit 8 ALARM: Wake up device from stop mode using RTC alaram

#### Wake up fall triggers (WKP\_FALL\_TRG)

Address offset: 0x24

Bit [7:0] EXT\_INTO-7: Wake up device from stop mode using EXT\_INTO-7, falling edge

triggered

Bit 8 ALARM: Wake up device from stop mode using RTC alaram

#### Wake up pending register (WKP PENDING)

Address offset: 0x28

Bits [8:0]: Correspoding bits are set when the selected triggering event occurs

#### PBUS clock divider (PBUS DIVIDER)

Address offset: 0x38

Bits [3:0] PBUS\_DIV: APB clock is divided by (PBUS\_DIV + 1) from SYS\_CLK, valid range

is from 0 (divided by 1) to 15 (divided by 16)

## APB peripheral reset (APB\_RESET)

#### Address offset: 0x40

## Each APB peripheral can be reset with the corresponding bit

0: Reset is deasserted

1: Reset is asserted

Bit [28]: I2C1

Bit [27]: I2C0

Bit [26]: CAN0

Bit [25]: UART4

Bit [24]: UART3

Bit [23]: UART2

Bit [22]: UART1

Bit [21]: UART0

Bit [20]: GPTIMER4

Bit [19]: GPTIMER3

Bit [18]: GPTIMER2

Bit [17]: GPTIMER1

Bit [16]: GPTIMER0

Bit [15]: TIMER1

Bit [14]: TIMERO

Bit [13]: GPIO9

Bit [12]: GPIO8

Bit [11]: GPIO7

Bit [10]: GPIO6

Bit [9]: GPIO5

Bit [8]: GPIO4

Bit [7]: GPIO3

Bit [6]: GPIO2

Bit [5]: GPIO1

Bit [4]: GPIO0

Bit [3]: SPI1

Bit [2]: SPI0

Bit [1]: WATCHDOG0

Bit [0]: FCB0

# AHB peripheral reset (AHB\_RESET)

Address offset: 0x50

Each AHB peripheral can be reset with the corresponding bit

0: Reset is deasserted

1: Reset is asserted

Bit [3]: MAC0

Bit [2]: CRC0

Bit [1]: USB0

Bit [0]: DMAC0

# APB peripheral clock enable (APB\_CLKENABLE)

Address offset: 0x60

Clock must be enabled before any APB peripheral is accessed. Bit asssignment is the same as APB\_RESET register

- 0: Peripheral clock is disabled

- 1: Peripheral clock is enabled

#### AHB peripheral clock enable (AHB\_CLKENABLE)

Address offset: 0x70

Clock must be enabled before any AHB peripheral is accessed. Bit asssignment is the same as AHB\_RESET register

- 0: Peripheral clock is disabled

- 1: Peripheral clock is enabled

#### APB peripheral clock stop during debug (APB\_CLKSTOP)

Address offset: 0x80

Clock can be automatically stopped during debug for the following APB peripherals:

WATCHDOG

TIMER

**GPTIMER**

CAN

Bit asssignment is the same as APB\_RESET register

- 0: Clock is not stopped during debug

- 1: Clock is stopped during debug

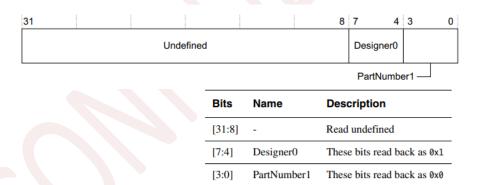

#### Device ID code (DEVICE\_ID)

Address offset: 0x100

Bit [31:0]: Returns the chip device ID: 0x40200001. Read only

# 2 Pin Definition

#### LQFP-100

| Pin | Pin name  | Function                    | Pin | Pin<br>name | Function                |

|-----|-----------|-----------------------------|-----|-------------|-------------------------|

| 1   | PIN_1     | 10                          | 26  | PIN_26      | IO/ADC_IN3/CMP_PA3      |

| 2   | PIN_2     | 10                          | 27  | VSS33       | GND                     |

| 3   | PIN_3     | 10                          | 28  | VDD33       | VDD33                   |

| 4   | PIN_4     | 10                          | 29  | PIN_29      | IO/ADC_IN4/CMP_PA4/DAC0 |

| 5   | PIN_5     | Ю                           | 30  | PIN_30      | IO/ADC_IN5/CMP_PA5/DAC1 |

| 6   | VBAT      | VBAT                        | 31  | PIN_31      | IO/ADC_IN6              |

| 7   | PIN_7     | IO/RTC                      | 32  | PIN_32      | IO/ADC_IN7              |

| 8   | OSC32_IN  | OSC32_IN                    | 33  | PIN_33      | IO/ADC_IN14             |

| 9   | OSC32_OUT | OSC32_OUT                   | 34  | PIN_34      | IO/ADC_IN15             |

| 10  | VSS33     | GND                         | 35  | PIN_35      | IO/ADC_IN8              |

| 11  | VDD33     | VDD33                       | 36  | PIN_36      | IO/ADC_IN9              |

| 12  | OSC_IN    | OSC_IN                      | 37  | PIN_37      | IO/BOOT1                |

| 13  | OSC_OUT   | OSC_OUT                     | 38  | PIN_38      | 10                      |

| 14  | NRST      | NRST                        | 39  | PIN_39      | 10                      |

| 15  | PIN_15    | IO/ADC_IN10                 | 40  | PIN_40      | 10                      |

| 16  | PIN_16    | IO/ADC_IN11                 | 41  | PIN_41      | 10                      |

| 17  | PIN_17    | IO/ADC_IN12                 | 42  | PIN_42      | 10                      |

| 18  | PIN_18    | IO/ADC_IN13                 | 43  | PIN_43      | 10                      |

| 19  | NC        | NC                          | 44  | PIN_44      | 10                      |

| 20  | VSSA      | GNDA                        | 45  | PIN_45      | 10                      |

| 21  | VREFP     | VREFP                       | 46  | PIN_46      | 10                      |

| 22  | VDDA      | VDDA                        | 47  | PIN_47      | 10                      |

| 23  | PIN_23    | IO/WKUP/ADC_INO/C<br>MP_PA0 | 48  | PIN_48      | 10                      |

| 24  | PIN_24    | IO/ADC_IN1/CMP_PA1          | 49  | NC          | NC                      |

| 25  | PIN_25    | IO/ADC_IN2/CMP_PA2          | 50  | VDD33       | VDD33                   |

| Pin | Pin name | Function    | Pin | Pin<br>name | Function  |

|-----|----------|-------------|-----|-------------|-----------|

| 51  | PIN_51   | Ю           | 76  | PIN_76      | 10/ЈТСК   |

| 52  | PIN_52   | Ю           | 77  | PIN_77      | IO/JTDI   |

| 53  | PIN_53   | Ю           | 78  | PIN_78      | 10        |

| 54  | PIN_54   | Ю           | 79  | PIN_79      | 10        |

| 55  | PIN_55   | Ю           | 80  | PIN_80      | 10        |

| 56  | PIN_56   | Ю           | 81  | PIN_81      | 10        |

| 57  | PIN_57   | 10          | 82  | PIN_82      | 10        |

| 58  | PIN_58   | 10          | 83  | PIN_83      | 10        |

| 59  | PIN_59   | 10          | 84  | PIN_84      | 10        |

| 60  | PIN_60   | 10          | 85  | PIN_85      | 10        |

| 61  | PIN_61   | 10          | 86  | PIN_86      | 10        |

| 62  | PIN_62   | 10          | 87  | PIN_87      | 10        |

| 63  | PIN_63   | 10          | 88  | PIN_88      | 10        |

| 64  | PIN_64   | 10          | 89  | PIN_89      | IO/JTDO   |

| 65  | PIN_65   | 10          | 90  | PIN_90      | IO/JNTRST |

| 66  | PIN_66   | 10          | 91  | PIN_91      | 10        |

| 67  | PIN_67   | 10          | 92  | PIN_92      | 10        |

| 68  | PIN_68   | IO/UARTO_TX | 93  | PIN_93      | 10        |

| 69  | PIN_69   | IO/UARTO_RX | 94  | воото       | воото     |

| 70  | PIN_70   | IO/USBDM    | 95  | PIN_95      | 10        |

| 71  | PIN_71   | IO/USBDP    | 96  | PIN_96      | 10        |

| 72  | PIN_72   | IO/JTMS     | 97  | PIN_97      | 10        |

| 73  | NC       | NC          | 98  | PIN_98      | 10        |

| 74  | VSS33    | GND         | 99  | VSS33       | GND       |

| 75  | VDD33    | VDD33       | 100 | VDD33       | VDD33     |

## LQFP-64

| Pin | Pin name  | Function                | Pin | Pin name | Function    |

|-----|-----------|-------------------------|-----|----------|-------------|

| 1   | VBAT      | VBAT                    | 33  | PIN_33   | 10          |

| 2   | PIN_2     | IO/RTC                  | 34  | PIN_34   | 10          |

| 3   | OSC32_IN  | OSC32_IN                | 35  | PIN_35   | 10          |

| 4   | OSC32_OUT | OSC32_OUT               | 36  | PIN_36   | 10          |

| 5   | OSC_IN    | OSC_IN                  | 37  | PIN_37   | 10          |

| 6   | OSC_OUT   | OSC_OUT                 | 38  | PIN_38   | 10          |

| 7   | NRST      | NRST                    | 39  | PIN_39   | 10          |

| 8   | PIN_8     | IO/ADC_IN10             | 40  | PIN_40   | 10          |

| 9   | PIN_9     | IO/ADC_IN11             | 41  | PIN_41   | 10          |

| 10  | PIN_10    | IO/ADC_IN12             | 42  | PIN_42   | IO/UARTO_TX |

| 11  | PIN_11    | IO/ADC_IN13             | 43  | PIN_43   | IO/UARTO_RX |

| 12  | VSSA      | GNDA                    | 44  | PIN_44   | IO/USBDM    |

| 13  | VDDA      | VDDA                    | 45  | PIN_45   | IO/USBDP    |

| 14  | PIN_14    | IO/WKUP/ADC_INO/CMP_PA0 | 46  | PIN_46   | IO/JTMS     |

| 15  | PIN_15    | IO/ADC_IN1/CMP_PA1      | 47  | PIN_47   | 10          |

| 16  | PIN_16    | IO/ADC_IN2/CMP_PA2      | 48  | VDD33    | VDD33       |

| 17  | PIN_17    | IO/ADC_IN3/CMP_PA3      | 49  | PIN_49   | IO/JTCK     |

| 18  | VSS33     | GND                     | 50  | PIN_50   | IO/JTDI     |

| 19  | VDD33     | VDD33                   | 51  | PIN_51   | 10          |

| 20  | PIN_20    | IO/ADC_IN4/CMP_PA4/DAC0 | 52  | PIN_52   | 10          |

| 21  | PIN_21    | IO/ADC_IN5/CMP_PA5/DAC1 | 53  | PIN_53   | 10          |

| 22  | PIN_22    | IO/ADC_IN6              | 54  | PIN_54   | 10          |

| 23  | PIN_23    | IO/ADC_IN7              | 55  | PIN_55   | IO/JTDO     |

| 24  | PIN_24    | IO/ADC_IN14             | 56  | PIN_56   | IO/JNTRST   |

| 25  | PIN_25    | IO/ADC_IN15             | 57  | PIN_57   | 10          |

| 26  | PIN_26    | IO/ADC_IN8              | 58  | PIN_58   | 10          |

| 27  | PIN_27    | IO/ADC_IN9              | 59  | PIN_59   | 10          |

| 28  | PIN_28    | IO/BOOT1                | 60  | воото    | воото       |

| 29  | PIN_29    | 10                      | 61  | PIN_61   | 10          |

| 30  | PIN_30    | 10                      | 62  | PIN_62   | 10          |

| 31  | PIN_31    | 10                      | 63  | VSS33    | GND         |

| 32  | VDD33     | VDD33                   | 64  | VDD33    | VDD33       |

# LQFP-48

| Pin | Pin name  | Function                | Pin | Pin name | Function    |

|-----|-----------|-------------------------|-----|----------|-------------|

| 1   | VBAT      | VBAT                    | 25  | PIN_25   | 10          |

| 2   | PIN_2     | IO/RTC                  | 26  | PIN_26   | 10          |

| 3   | OSC32_IN  | OSC32_IN                | 27  | PIN_27   | 10          |

| 4   | OSC32_OUT | OSC32_OUT               | 28  | PIN_28   | 10          |

| 5   | OSC_IN    | OSC_IN                  | 29  | PIN_29   | 10          |

| 6   | OSC_OUT   | OSC_OUT                 | 30  | PIN_30   | IO/UARTO_TX |

| 7   | NRST      | NRST                    | 31  | PIN_31   | IO/UARTO_RX |

| 8   | VSSA      | GNDA                    | 32  | PIN_32   | IO/USBDM    |

| 9   | VDDA      | VDDA                    | 33  | PIN_33   | IO/USBDP    |

| 10  | PIN_10    | IO/WKUP/ADC_INO/CMP_PA0 | 34  | PIN_34   | IO/JTMS     |

| 11  | PIN_11    | IO/ADC_IN1/CMP_PA1      | 35  | PIN_35   | 10          |

| 12  | PIN_12    | IO/ADC_IN2/CMP_PA2      | 36  | VDD33    | VDD33       |

| 13  | PIN_13    | IO/ADC_IN3/CMP_PA3      | 37  | PIN_37   | IO/JTCK     |

| 14  | PIN_14    | IO/ADC_IN4/CMP_PA4/DACO | 38  | PIN_38   | IO/JTDI     |

| 15  | PIN_15    | IO/ADC_IN5/CMP_PA5/DAC1 | 39  | PIN_39   | IO/JTDO     |

| 16  | PIN_16    | IO/ADC_IN6              | 40  | PIN_40   | IO/JNTRST   |

| 17  | PIN_17    | IO/ADC_IN7              | 41  | PIN_41   | Ю           |

| 18  | PIN_18    | IO/ADC_IN8              | 42  | PIN_42   | 10          |

| 19  | PIN_19    | IO/ADC_IN9              | 43  | PIN_43   | 10          |

| 20  | PIN_20    | IO/BOOT1                | 44  | воото    | воото       |

| 21  | PIN_21    | 10                      | 45  | PIN_45   | 10          |

| 22  | PIN_22    | 10                      | 46  | PIN_46   | Ю           |

| 23  | VSS33     | GND                     | 47  | VSS33    | GND         |

| 24  | VDD33     | VDD33                   | 48  | VDD33    | VDD33       |

## QFN-32

| Pin | Pin name | Function                | Pin | Pin name | Function    |

|-----|----------|-------------------------|-----|----------|-------------|

| 1   | PIN_1    | IO/RTC                  | 17  | GND      | GND         |

| 2   | PIN_2    | IO/OSC_IN               | 18  | PIN_18   | 10          |

| 3   | PIN_3    | IO/OSC_OUT              | 19  | PIN_19   | 10          |

| 4   | NRST     | NRST                    | 20  | PIN_20   | IO_UARTO_TX |

| 5   | PIN_5    | IO_ADC_IN12             | 21  | PIN_21   | IO_UARTO_RX |

| 6   | VDDA33   | VDDA33                  | 22  | PIN_22   | IO_USBDM    |

| 7   | PIN_7    | IO_WKUP_ADC_INO_CMP_PA0 | 23  | PIN_23   | IO_USBDP    |

| 8   | PIN_8    | IO_ADC_IN1_CMP_PA1      | 24  | PIN_24   | IO_JTMS     |

| 9   | PIN_9    | IO_ADC_IN2_CMP_PA2      | 25  | PIN_25   | IO_JTCK     |

| 10  | PIN_10   | IO_ADC_IN3_CMP_PA3      | 26  | PIN_26   | IO_JTDI     |

| 11  | PIN_11   | IO_ADC_IN4_CMP_PA4_DAC0 | 27  | PIN_27   | IO_JTDO     |

| 12  | PIN_12   | IO_ADC_IN5_CMP_PA5_DAC1 | 28  | PIN_28   | IO_JNTRST   |

| 13  | PIN_13   | IO_ADC_IN6              | 29  | PIN_29   | 10          |

| 14  | PIN_14   | IO_ADC_IN7              | 30  | воото    | воото       |

| 15  | PIN_15   | IO_BOOT1                | 31  | PIN_31   | 10          |

| 16  | VDD33    | VDD33                   | 32  | VDD33    | VDD33       |

#### **AG32VH407RCT6 & AG32VF407RGT6**

| PIN | AG32VH407RCT6 |                         |           | AG32VF407RGT6           |  |  |  |

|-----|---------------|-------------------------|-----------|-------------------------|--|--|--|

| No. |               |                         |           |                         |  |  |  |

| 1   | VBAT          | VBAT                    | VBAT      | VBAT                    |  |  |  |

| 2   | PIN_2         | IO_RTC                  | PIN_2     | IO_RTC                  |  |  |  |

| 3   | OSC32_IN      | OSC32_IN                | OSC32_IN  | OSC32_IN                |  |  |  |

| 4   | OSC32_OUT     | OSC32_OUT               | OSC32_OUT | OSC32_OUT               |  |  |  |

| 5   | OSC_IN        | OSC_IN                  | OSC_IN    | OSC_IN                  |  |  |  |

| 6   | OSC_OUT       | OSC_OUT                 | OSC_OUT   | OSC_OUT                 |  |  |  |

| 7   | NRST          | NRST                    | NRST      | NRST                    |  |  |  |

| 8   | RWDS          | RWDS                    | PIN_8     | IO_ADC_IN10             |  |  |  |

| 9   | PIN_9         | IO_ADC_IN11             | PIN_9     | IO_ADC_IN11             |  |  |  |

| 10  | PIN_10        | IO_ADC_IN12             | PIN_10    | IO_ADC_IN12             |  |  |  |

| 11  | PIN_11        | IO_ADC_IN13             | PIN_11    | IO_ADC_IN13             |  |  |  |

| 12  | GND           | GND                     | GND       | GND                     |  |  |  |

| 13  | VDD33         | VDD33                   | VDD33     | VDD33                   |  |  |  |

| 14  | PIN_14        | IO_WKUP_ADC_IN0_CMP_PA0 | PIN_14    | IO_WKUP_ADC_IN0_CMP_PA0 |  |  |  |

| 15  | PIN_15        | IO_ADC_IN1_CMP_PA1      | PIN_15    | IO_ADC_IN1_CMP_PA1      |  |  |  |

| 16  | PIN_16        | IO_ADC_IN2_CMP_PA2      | PIN_16    | IO_ADC_IN2_CMP_PA2      |  |  |  |

| 17  | PIN_17        | IO_ADC_IN3_CMP_PA3      | PIN_17    | IO_ADC_IN3_CMP_PA3      |  |  |  |

| 18  | GND           | GND                     | GND       | GND                     |  |  |  |

| 19  | VDD33         | VDD33                   | VDD33     | VDD33                   |  |  |  |

| 20  | PIN_20        | IO_ADC_IN5_CMP_PA5_DAC1 | PIN_20    | IO_ADC_IN4_CMP_PA4_DAC0 |  |  |  |

| 21  | PIN_21        | IO_ADC_IN7              | PIN_21    | IO_ADC_IN5_CMP_PA5_DAC1 |  |  |  |

| 22  | RWDS          | RWDS                    | PIN_22    | IO_ADC_IN6              |  |  |  |

| 23  | PIN_23        | IO_ADC_IN15             | PIN_23    | IO_ADC_IN7              |  |  |  |

| 24  | PIN_24        | IO_ADC_IN9              | PIN_24    | IO_ADC_IN14             |  |  |  |

| 25  | PIN_25        | IO_BOOT1                | PIN_25    | IO_ADC_IN15             |  |  |  |

| 26  | PIN_26        | 10                      | PIN_26    | IO_ADC_IN8              |  |  |  |

| 27  | PIN_27        | 10                      | PIN_27    | IO_ADC_IN9              |  |  |  |

| 28  | PIN_28        | 10                      | PIN_28    | IO_BOOT1                |  |  |  |

| 29  | PIN_29        | IO                      | PIN_29    | 10                      |  |  |  |

| 30  | VDD33         | VDD33                   | PIN_30    | 10                      |  |  |  |

| 31  | GND           | GND                     | PIN_31    | 10                      |  |  |  |

| 32  | VDD33         | VDD33                   | VDD33     | VDD33                   |  |  |  |

| 33  | PIN_33        | IO                      | PIN_33    | Ю                       |  |  |  |

| 34  | PIN_34        | Ю                       | PIN_34    | 10                      |  |  |  |

| 35  | PIN_35        | IO                      | PIN_35    | 10                      |  |  |  |

| 36  | PIN_36        | IO                      | PIN_36    | 10                      |  |  |  |

| 37  | PIN_37        | IO                      | PIN_37    | 10                      |  |  |  |

| 38  | PIN_38        | 10                      | PIN_38    | IO                      |  |  |  |

| 39 | PIN_39 | IO          | PIN_39 | Ю           |

|----|--------|-------------|--------|-------------|

| 40 | PIN_40 | 10          | PIN_40 | 10          |

| 41 | PIN_41 | Ю           | PIN_41 | 10          |

| 42 | PIN_42 | IO_UART0_TX | PIN_42 | IO_UART0_TX |

| 43 | PIN_43 | IO_UART0_RX | PIN_43 | IO_UART0_RX |

| 44 | PIN_44 | IO_USBDM    | PIN_44 | IO_USBDM    |

| 45 | PIN_45 | IO_USBDP    | PIN_45 | IO_USBDP    |

| 46 | PIN_46 | IO_JTMS     | PIN_46 | IO_JTMS     |

| 47 | PIN_47 | IO          | PIN_47 | 10          |

| 48 | VDD33  | VDD33       | VDD33  | VDD33       |

| 49 | PIN_49 | IO_JTCK     | PIN_49 | IO_JTCK     |

| 50 | PIN_50 | IO_JTDI     | PIN_50 | IO_JTDI     |

| 51 | PIN_51 | 10          | PIN_51 | 10          |

| 52 | PIN_52 | Ю           | PIN_52 | 10          |

| 53 | PIN_53 | Ю           | PIN_53 | 10          |

| 54 | PIN_54 | Ю           | PIN_54 | 10          |

| 55 | PIN_55 | IO_JTDO     | PIN_55 | IO_JTDO     |

| 56 | PIN_56 | IO_JNTRST   | PIN_56 | IO_JNTRST   |

| 57 | PIN_57 | 10          | PIN_57 | 10          |

| 58 | PIN_58 | Ю           | PIN_58 | Ю           |

| 59 | PIN_59 | 10          | PIN_59 | 10          |

| 60 | воото  | воото       | воото  | BOOT0       |

| 61 | PIN_61 | 10          | PIN_61 | Ю           |

| 62 | PIN_62 | 10          | PIN_62 | 10          |

| 63 | GND    | GND         | GND    | GND         |

| 64 | VDD33  | VDD33       | VDD33  | VDD33       |

#### Note:

RWDS(PIN\_8 and PIN\_22) needs to be short circuited externally.VDD33 needs to be isolated from other power sources on the PCB using magnetic beads separately.

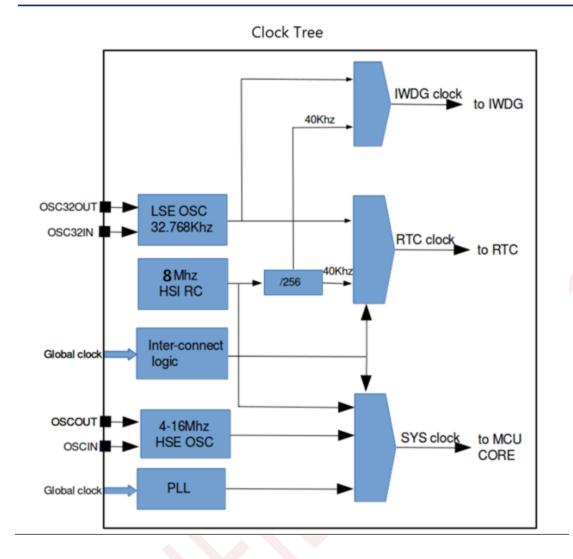

# 3 Clock

#### 3.1 Clock sources

Three different clock sources can be used to drive the system clock (SYSCLK):

- (1) HSI oscillator clock

- (2) HSE oscillator clock

- (3) PLL clock

- (4) Interconnect global clocks(FPGA Core)

The devices have the following two secondary clock sources:

- (1) 40 kHz low speed internal RC (LSI), which drives the independent watchdog and optionally the RTC used for Auto-wakeup from Stop/Standby mode.

- (2) 32.768 kHz low speed external crystal (LSE crystal), which optionally drives the real-time clock (RTCCLK)

Each clock source can be switched on or off independently when it is not used, to optimize power consumption.

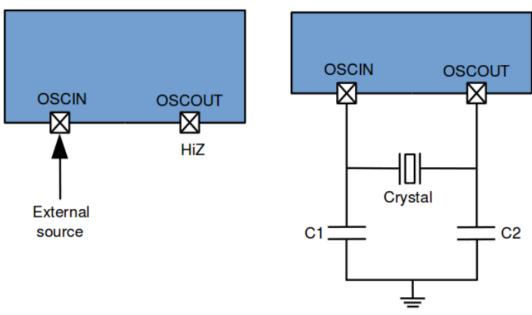

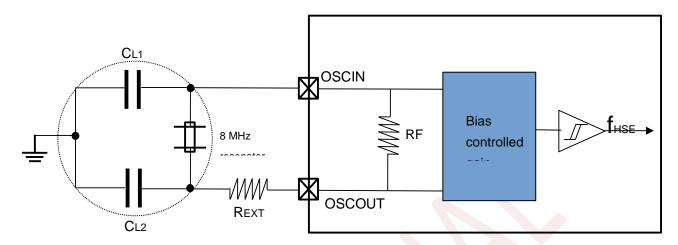

## 3.2 HSE clock

The high speed external clock signal (HSE) can be generated from two possible clock sources:

- (1) HSE external crystal/ceramic resonator

- (2) HSE user external clock

The resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

HSE/ LSE clock sources

#### External source (HSE bypass)

In this mode, an external clock source must be provided. It can have a frequency of up to 100 MHz. You select this mode by setting the HSEBYP and HSEON bits in the Clock control register (RCC\_CR). The external clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC\_IN pin while the OSC\_OUT pin should be left hi-Z.

External crystal/ceramic resonator (HSE crystal)

The 4 to 24 MHz external oscillator has the advantage of producing a very accurate rate on the main clock. The HSERDY flag indicates if the high-speed external oscillator is stable or not. At startup, the clock is not released until this bit is set by hardware. The HSE Crystal can be switched on and off using the HSEON bit.

#### 3.3 HSI clock

The HSI clock signal is generated from an internal Oscillator and can be used directly as a system clock. The HSI internal oscillator has the advantage of providing a clock source at low cost (no external components). It also has a faster startup time than the HSE crystal oscillator.

#### 3.4 PLL clock

The internal PLL can be used to multiply HSE crystal output clock frequency.

If the USB interface is used in the application, the PLL must be programmed to output 48 MHz. This is needed to provide a 48 MHz USBCLK.

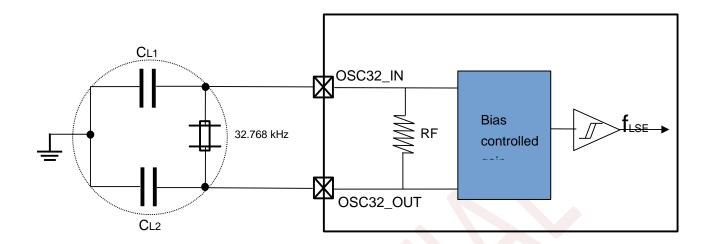

#### 3.5 LSE clock

The LSE crystal is a 32.768 kHz Low Speed External crystal or ceramic resonator. It has the advantage providing a low-power but highly accurate clock source to the real-time clock peripheral (RTC) for clock/calendar or other timing functions.

The LSE crystal is switched on and off using the LSEON bit in Backup domain control register.

The LSERDY flag in the Backup domain control register indicates if the LSE crystal is stable or not. At startup, the LSE crystal output clock signal is not released until this bit is set by hardware.

External source (LSE bypass)

In this mode, an external clock source must be provided. It can have a frequency of up to 1MHz. The external clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC32\_IN pin while the OSC32\_OUT pin should be left Hi-Z.

#### 3.6 LSI clock

The LSI clock is HSI divided by 256. It can be kept running in Stop mode for the independent watchdog (IWDG) and Auto-wakeup unit. The clock frequency is around 40 kHz (between 30 kHz and 60 kHz).

# 3.7 System clock (SYSCLK) selection

After a system reset, the HSI oscillator is selected as system clock. When a clock source is used directly or through the PLL as system clock, it is not possible to stop it. A switch from one clock source to another occurs only if the target clock source is ready (clock stable after startup delay or PLL locked).

A switch from one clock source to another occurs only if the target clock source is ready (clock stable after startup delay or PLL locked).

#### 3.8 RTC clock

The RTCCLK clock source can be either the CLKLOCAL(from fpga core logic), LSE or LSI clocks. This is selected by programming the RTCSEL[1:0] bits in the Backup domain control register (RCC\_BDCR). This selection cannot be modified without resetting the Backup domain.

The LSE clock is in the Backup domain, whereas the HSE and LSI clocks are not. Consequently:

(1) If LSE is selected as RTC clock:

The RTC continues to work even if the VDD supply is switched off, provided the VBAT supply is maintained.

(2) If LSI is selected as Auto-Wakeup unit (AWU) clock:

The AWU state is not guaranteed if the VDD supply is powered off.

(3) If the CLKLOCAL is used as the RTC clock:

The RTC state is not guaranteed if the VDD supply is powered off or if the internal voltage regulator is powered off (removing power from the 1.2 V domain).

The DPB bit (disable backup domain write protection) in the Power controller register must be set to 1.

# 3.9 Watchdog clock

If the Independent watchdog (IWDG) is started by either hardware option or software access,

(1) Under run or stop mode

Select LSE or LSI clock source by setting the IWDG\_STOP\_CLKSEL bit in the Backup domain control register (RCC\_BDCR).

(2) Under Standby mode

HW will select LSE as clock source for IWDG.

#### 4 Reset

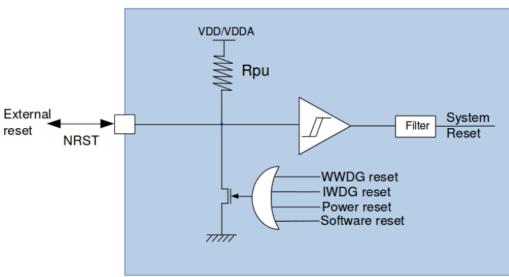

There are three types of reset: system reset, power reset and backup domain reset.

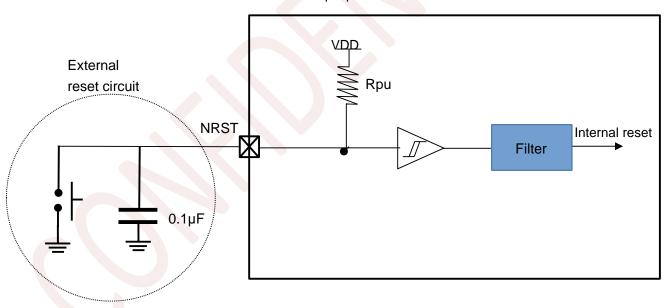

Simplified diagram of the reset circuit

# 4.1 System reset

A system reset is generated when one of the following events occurs:

- (1) A low level on the NRST pin (external reset)

- (2) Window watchdog end of count condition (WWDG reset)

- (3) Independent watchdog end of count condition (IWDG reset)

- (4) A software reset (SW reset)

- (5) Low-power management reset

The reset source can be identified by checking the reset flags in the Control/Status register, RCC\_CSR.

#### **Software reset**

The SYSRESETREQ bit in MCU Application Interrupt and Reset Control Register must be set to force a software reset on the device.

#### Low-power management reset

There are two ways to generate a low-power management reset:

(1) Reset generated when entering Standby mode:

This type of reset is enabled by resetting nRST\_STDBY bit in User Option Bytes. In this case, whenever a Standby mode entry sequence is successfully executed, the device is reset instead of entering Standby mode.

(2) Reset when entering Stop mode:

This type of reset is enabled by resetting nRST\_STOP bit in User Option Bytes. In this case, whenever a Stop mode entry sequence is successfully executed, the device is reset instead of entering Stop mode.

#### 4.2 Power reset

A power reset is generated when one of the following events occurs:

- (1) Power-on/power-down reset (POR/PDR reset)

- (2) When exiting Standby mode

# 4.3 Backup domain reset

The backup domain has two specific resets that affect only the backup domain.

A backup domain reset is generated when one of the following events occurs:

- (1)Software reset.

- (2) VDD33 or VBAT power on, if both supplies have previously been powered off.

#### 5 Power control

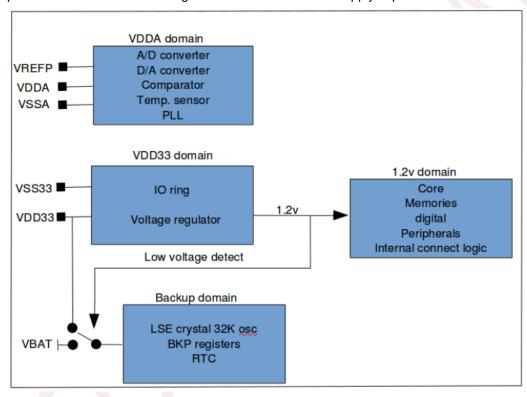

# 5.1 Power supplies

The AG32VF requires a 3.135-to-3.465V operating voltage supply (VDD33). An embedded regulator is used to supply the internal 1.2V digital power. The real-time clock (RTC) and backup registers can be powered from the VBAT voltage when the main VDD33 supply is powered off.

# 5.2 Independent ADC and DAC converter supply and reference voltage

To improve conversion accuracy, the ADC and the DAC have an independent power supply which can be separately filtered and shielded from noise on the PCB.

- (1) The ADC and DAC voltage supply input is available on a separate VDDA pin.

- (2) An isolated supply ground connection is provided on pin VSSA.

To ensure a better accuracy on low-voltage inputs and outputs, the user can connect a separate external reference voltage on VREFP. VREFP is the highest voltage, represented by the full scale

value, for an analog input (ADC) or output (DAC) signal. The voltage on VREFP can range from 3.135V to VDDA.

# 5.3 Battery backup domain

To retain the content of the Backup registers and supply the RTC function when VDD33 is turned off, VBAT pin can be connected to an optional standby voltage supplied by a battery or by another source.

The VBAT pin powers the RTC unit, the LSE oscillator and the OSC32\_IN and OSC32\_OUT Pins, allowing the RTC to operate even when the main digital supply (VDD33) is turned off.

If no external battery is used in the application, it is recommended to connect VBAT externally to VDD33 with a 100nF external ceramic decoupling capacitor.

When the backup domain is supplied by VDD33 (analog switch connected to VDD33).

# 5.4 Voltage regulator

The voltage regulator is always enabled after Reset. It works in two different modes depending on the application modes.

- (1) In Run and Stop modes, the regulator supplies full power to the 1.2V domain (core, memories, digital peripherals and interconnect logic).

- (2) In Standby Mode, the regulator is powered off. The contents of the registers and SRAM are lost except for the Standby circuitry and the Backup Domain.

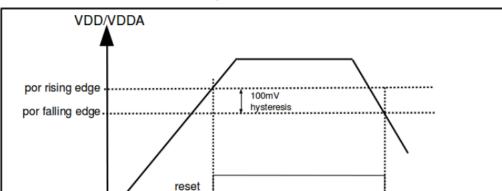

# 5.5 Power on reset (POR)/power down reset (PDR)

The device has an integrated POR/PDR circuitry that allows proper operation starting from/down to 2.2V. The device remains in Reset mode when VDD33/VDDA is below a specified threshold, VPOR/PDR, without the need for an external reset circuit.

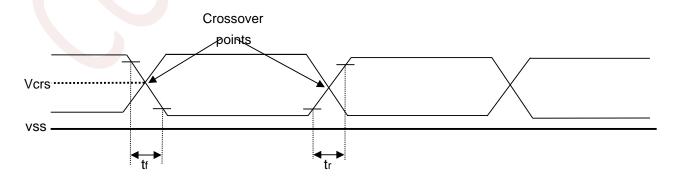

Power on reset/power down reset waveform

# 5.6 Low-power modes

By default, the micro-controller is in Run mode after a system or a power Reset. Several low-power modes are available to save power when the CPU does not need to be kept running. It is up to the user to select the mode that gives the best compromise between low-power consumption, short startup time and available wakeup sources.

The AG32VF devices feature three low-power modes:

- (1) Sleep mode (CPU clock off, all peripherals including core peripherals are kept running)

- (2) Stop mode (all clocks are stopped)

- (3) Standby mode (1.2V domain powered-off)

In addition, the power consumption in Run mode can be reduce by one of the following means:

- (1) Slowing down the system clocks.

- (2) Gating the clocks to the APB and AHB peripherals when they are unused.

# 5.6.1 Slowing down system clocks

In Run mode the speed of the system clocks can be reduced. And also slow down peripherals before entering Sleep mode.

### 5.6.2 Peripheral clock gating

In Run mode, the clocks for individual peripherals and memories can be stopped at any time to reduce power consumption.

To further reduce power consumption in Sleep mode the peripheral clocks can be disabled prior to executing the WFI or WFE instructions.

## 5.6.3 Sleep mode

#### Entering Sleep mode

The Sleep mode is entered by executing the WFI (Wait For Interrupt) or WFE (Wait for Event) instructions. Two options are available to select the Sleep mode entry mechanism, depending on the SLEEPONEXIT bit in the System Control register:

- (1) Sleep-now: if the SLEEPONEXIT bit is cleared, the MCU enters Sleep mode as soon as WFI or WFE instruction is executed.

- (2) Sleep-on-exit: if the SLEEPONEXIT bit is set, the MCU enters Sleep mode as soon as it exits the lowest priority ISR.

In the Sleep mode, all I/O pins keep the same state as in the Run mode.

#### Exiting Sleep mode

If the WFI instruction is used to enter Sleep mode, any peripheral interrupt acknowledged by the nested vectored interrupt controller (NVIC) can wake up the device from Sleep mode. If the WFE instruction is used to enter Sleep mode, the MCU exits Sleep mode as soon as an event occurs. The wakeup event can be generated either by:

- (1) enabling an interrupt in the peripheral control register but not in the NVIC, and enabling the SEVONPEND bit in the System Control register. When the MCU resumes from WFE, the peripheral interrupt pending bit and the peripheral NVIC IRQ channel pending bit (in the NVIC interrupt clear pending register) have to be cleared.

- (2) or configuring an external or internal EXTI line in event mode. When the CPU resumes from WFE, it is not necessary to clear the peripheral interrupt pending bit or the NVIC IRQ channel pending bit as the pending bit corresponding to the event line is not set. This mode offers the lowest wakeup time as no time is wasted in interrupt entry/exit.

Table 1. Sleep-now

| Sleep-now mode | Description                                                                                                                                               |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Mode entry     | WFI (Wait for Interrupt) or WFE (Wait for Event) while:  - SLEEPDEEP = 0 and  - SLEEPONEXIT = 0  Refer to the System Control register.                    |  |  |  |

| Mode exit      | If WFI was used for entry: Interrupt: Refer to: Interrupt and exception vectors If WFE was used for entry Wakeup event: Refer to: Wakeup event management |  |  |  |

| Wakeup latency | None                                                                                                                                                      |  |  |  |

Table 2. Sleep-on-exit

| Sleep-on-exit | Description                     |  |

|---------------|---------------------------------|--|

| Mode entry    | WFI (wait for interrupt) while: |  |

|                | - SLEEPDEEP = 0 and                                   |  |  |  |

|----------------|-------------------------------------------------------|--|--|--|

|                | - SLEEPONEXIT = 1                                     |  |  |  |

|                | Refer to the System Control register.                 |  |  |  |

| Mode exit      | Interrupt: refer to: Interrupt and exception vectors. |  |  |  |

| Wakeup latency | None                                                  |  |  |  |

## 5.6.4 Stop mode

The Stop mode is based on the MCU deep-sleep mode combined with peripheral clock gating.

In Stop mode, all clocks in the 1.2V domain are stopped, the PLL, the HSI and the HSE oscillators are disabled. SRAM and register contents are preserved.

In the Stop mode, all I/O pins keep the same state as in the Run mode.

#### Entering Stop mode

Refer to Table 3 for details on how to enter the Stop mode.

If Flash memory programming is ongoing, the Stop mode entry is delayed until the memory access is finished.

If an access to the APB domain is ongoing, The Stop mode entry is delayed until the APB access is finished.

In Stop mode, the following features can be selected by programming individual control bits:

- (1) Independent watchdog (IWDG): the IWDG is started by writing to its enable register or by hardware option. Once started it cannot be stopped except by a Reset.

- (2) Real-time clock (RTC): this is configured by the RTCEN bit in the Backup domain control register (RCC\_BDCR).

- (3) External 32.768 kHz oscillator (LSE OSC): this is configured by the LSEON bit in the Backup domain control register (RCC\_BDCR).

The ADC or DAC can also consume power during the Stop mode, unless they are disabled before entering it.

#### Exiting Stop mode

Refer to Table 3 for more details on how to exit Stop mode.

When exiting Stop mode by issuing an interrupt or a wakeup event, the HSI RC oscillator is selected as system clock.

Table 3. Stop mode

| Stop mode  | Description                                                                                                                                                  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode entry | WFI (Wait for Interrupt) or WFE (Wait for Event) while:  – Set SLEEPDEEP bit in System Control register  – Clear PDDS bit in Power Control register (PWR CR) |

|                | Note: To enter Stop mode, all EXTI Line pending bits (in Pending register (EXTI_PR)), all peripheral interrupt pending bits, and RTC Alarm flag must be reset. Otherwise, the Stop mode entry procedure is ignored and program execution continues. |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | If WFI was used for entry: Any EXTI Line configured in Interrupt mode (the corresponding EXTI                                                                                                                                                       |

|                | Interrupt vector must be enabled in the NVIC). Refer to:                                                                                                                                                                                            |

| Mode exit      | Interrupt and exception vectors.                                                                                                                                                                                                                    |

|                | If WFE was used for entry:                                                                                                                                                                                                                          |

|                | Any EXTI Line configured in event mode. Refer to:                                                                                                                                                                                                   |

|                | Wakeup event management                                                                                                                                                                                                                             |

| Wakeup latency | HSI RC wakeup time                                                                                                                                                                                                                                  |

## 5.6.5 Standby mode

The Standby mode allows to achieve the lowest power consumption. It is based on the deep-sleep mode, with the voltage regulator disabled. The 1.2V domain is consequently powered off. The PLL, the HSI oscillator and the HSE oscillator are also switched off. SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

#### Entering Standby mode

Refer to Table 4 for more details on how to enter Standby mode.

In Standby mode, the following features can be selected by programming individual control bits:

- (1) Independent watchdog (IWDG): the IWDG is started by writing to its enable register or by hardware option. Once started it cannot be stopped except by a reset.

- (2) Real-time clock (RTC): this is configured by the RTCEN bit in the Backup domain control register (RCC\_BDCR).

- (3) External 32.768 kHz oscillator (LSE OSC): this is configured by the LSEON bit in the Backup domain control register (RCC\_BDCR)

#### Exiting Standby mode

The micro-controller exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge or falling edge on the WKUP pin or the rising edge of an RTC alarm occurs. All registers are reset after wakeup from Standby.

After waking up from Standby mode, program execution restarts in the same way as after a Reset. The SBF status flag in the Power control/status register (PWR\_CSR) indicates that the MCU was in Standby mode.

Refer to Table 4 for more details on how to exit Standby mode.

Table 4. Standby mode

|--|

| Mode entry     | WFI (Wait for Interrupt) or WFE (Wait for Event) while:  - Set SLEEPDEEP in System Control register  - Set PDDS bit in Power Control register (PWR_CR)  - Clear WUF bit in Power Control/Status register (PWR_CSR)  - No interrupt (for WFI) or event (for WFI) is pending |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode exit      | WKUP pin rising edge, RTC alarm event's rising edge, external Reset in NRST pin, IWDG Reset.                                                                                                                                                                               |

| Wakeup latency | Reset phase                                                                                                                                                                                                                                                                |

I/O states in Standby mode

In Standby mode, all I/O pins are high impedance except:

- (1) Reset pin (still available)

- (2) CLKRTCOUT pin if configured for calibration out

- (3) WKUP pin, if enabled

# 5.6.6 Auto-wakeup (AWU) from low-power mode

The RTC can be used to wakeup the MCU from low-power mode without depending on an external interrupt (Auto-wakeup mode). The RTC provides a programmable time base for waking up from Stop or Standby mode at regular intervals. For this purpose, two of the three alternative RTC clock sources can be selected by programming the RTCSEL[1:0] bits in the Backup domain control register (RCC\_BDCR):

(1) Low-power 32.768 kHz external crystal oscillator (LSE OSC).

This clock source provides a precise time base with very low-power consumption.

(2) Low-power internal RC Oscillator (LSI RC)

This clock source has the advantage of saving the cost of the 32.768 kHz crystal.

# 6 Interrupt Controller

The AG32 device embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 44 maskable interrupt channels plus the 16 interrupt lines of the RISC-V core.

# **6.1 Local interrupts**

4 local interrupts (LOCAL\_INT0-3) are connected directly to the core and have lower latencies. They have fixed priorities.

# **6.2 External interrupts**

External interrupts are routed through the Platform-Level Interrupt Controller (PLIC). They have programmable priority levels and a threshold. The interrupt numbers are listed below:

| Interrupt Name | Interrupt Number | Comment |

|----------------|------------------|---------|

| FLASH          | 1                |         |

| RTC            | 2                |         |

| FCB0           | 3                |         |

| WATCHDOG0      | 4                |         |

| SPI0           | 5                |         |

| SPI1           | 6                |         |

| GPIO0          | 7                |         |

| GPIO1          | 8                |         |

| GPIO2          | 9                |         |

| GPIO3          | 10               |         |

| GPIO4          | 11               |         |

| GPIO5          | 12               |         |

| GPIO6          | 13               |         |

| GPIO8         15           GPIO9         16           TIMERO         17           TIMER1         18           GPTIMER0         19           GPTIMER1         20           GPTIMER2         21           GPTIMER3         22           GPTIMER4         23           UART0         24           UART1         25           UART2         26           UART3         27           UART4         28           CANO         29           I2C0         30           I2C1         31           DMAC0_INTE         32 DMA combined interrupt           DMAC0_INTER         34 DMA error interrupt           USBO         35           MAC0         36           EXT_INT0         37           EXT_INT1         38           EXT_INT2         39           EXT_INT3         40           EXT_INT4         41           EXT_INT5         42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GPIO7        | 14 |                              |

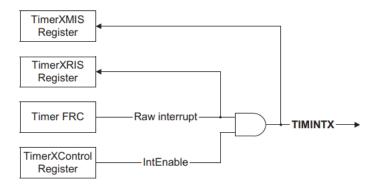

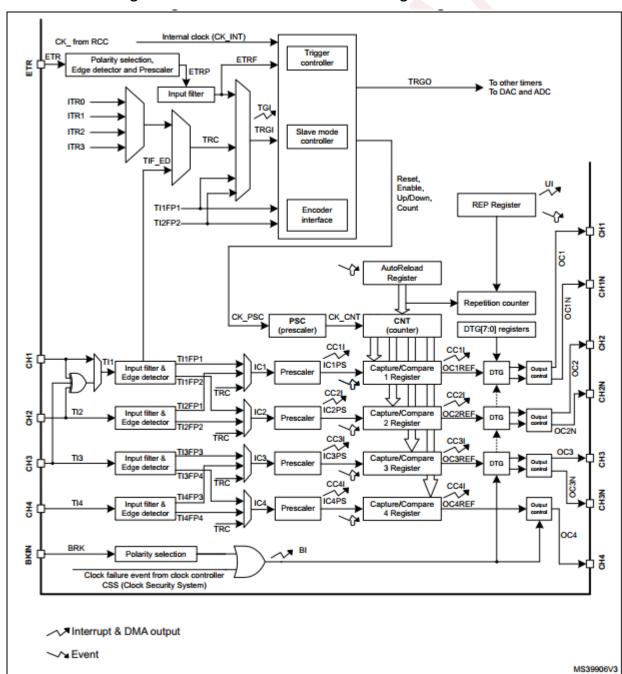

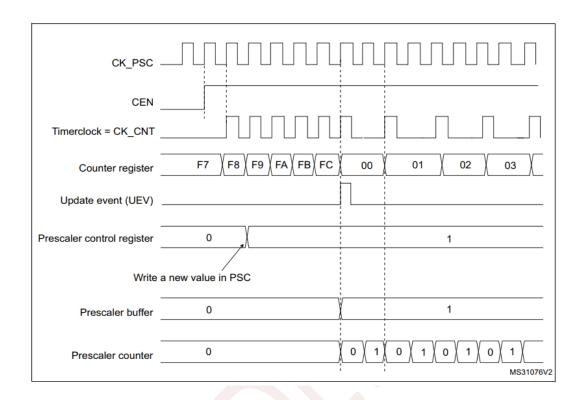

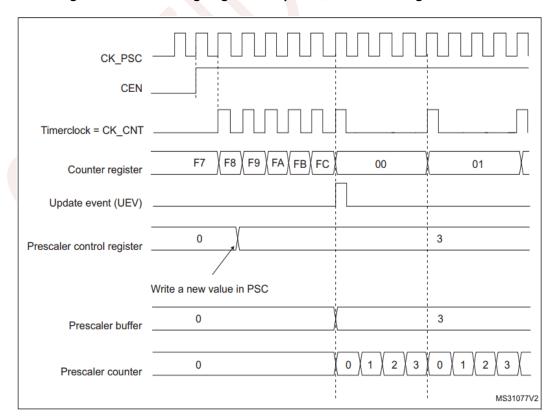

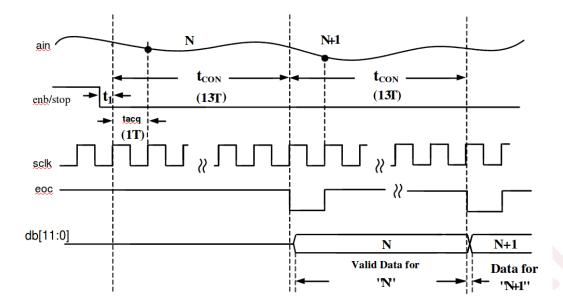

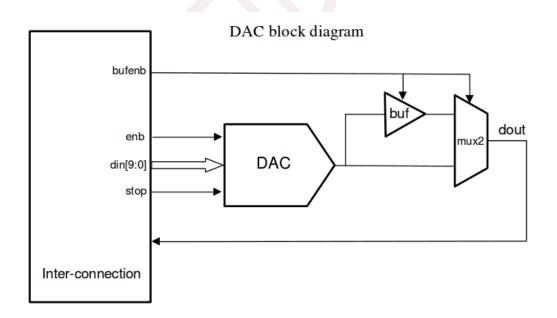

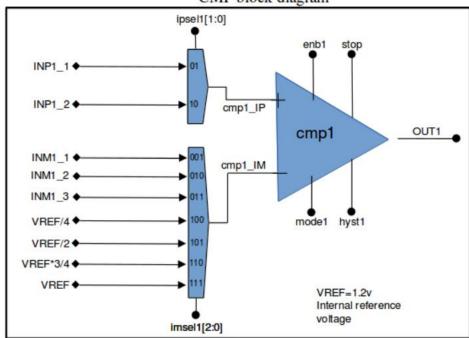

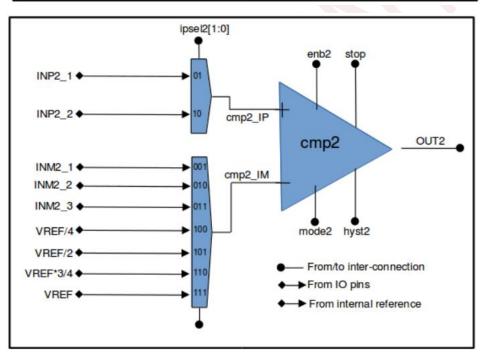

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----|------------------------------|