## PolarFire® FPGA

### **Overview**

This datasheet covers the electrical AC and DC specifications for four temperature grades of devices. AC and DC electrical characteristics and parametric values, unless otherwise noted, apply to all temperature grade devices. For example, worst-case STD speed grade applies to all temperature grade devices and –1 speed grade applies to all temperature grade devices except Military. In addition, Low-Power (L) devices are equivalent in performance to STD speed grade devices where offered. Users are expected to close timing using SmartTime for the speed and temperate grade of the device chosen.

Table 1. PolarFire Minimum and Maximum Junction Temperatures by Temperature Grade

| Temperature Grade        | Minimum Junction Temperature | Maximum Junction Temperature |

|--------------------------|------------------------------|------------------------------|

| Extended Commercial (E)  | 0 °C                         | 100 °C                       |

| Industrial (I)           | –40 °C                       | 100 °C                       |

| Automotive AECQ-100 (T2) | -40 °C                       | 125 °C                       |

| Military (M)             | −55 °C                       | 125 °C                       |

Table 2. PolarFire Speed Grade Options by Temperature Grade

| Temperature Grade       | Standard Speed Grade | –1 Speed Grade |

|-------------------------|----------------------|----------------|

| Extended Commercial (E) | Available            | Available      |

| Industrial (I)          | Available            | Available      |

| Automotive T2 (T2)      | Available            | Available      |

| Military (M)            | Available            | Not Available  |

Table 3. PolarFire Package Ball Composition by Temperature Grade

| Temperature Grade       |      | Package Decoupling Capacitor Solder Paste (FC484, FC784, FC1152) |

|-------------------------|------|------------------------------------------------------------------|

| Extended Commercial (E) | RoHS | RoHS                                                             |

| Industrial (I)          | RoHS | RoHS                                                             |

| Automotive T2 (T2)      | RoHS | RoHS                                                             |

| Military (M)            | Pb   | Pb                                                               |

PolarFire device programming functions (programming, verify, and digest check) are only allowed over the Industrial temperature range regardless of the temperature grade of the device selected. Retention characteristics for each temperature range explicitly describe the retention characteristics for that temperature-grade device. You cannot, for example, use the retention characteristics at 110 °C and apply them to the Extended Commercial or Industrial devices with a maximum  $T_J$  of 100 °C. Retention characteristics for Military-grade devices and Automotive-grade devices at the absolute maximum junction temperature of 125 °C can be profiled using the PolarFire Retention Calculator, which can be obtained by contacting technical support at <a href="https://www.microchip.com/support">www.microchip.com/support</a>.

# **Table of Contents**

| Ov  | erview.  |                                       | 1   |

|-----|----------|---------------------------------------|-----|

| 1.  | Refer    | rences                                | 3   |

| 2.  | Devic    | ce Offering                           | 4   |

| 3.  | Silico   | on and Libero Tool Status             | 5   |

| 4.  | DC C     | Characteristics                       | 7   |

|     | 4.1.     | Absolute Maximum Rating               | 7   |

|     | 4.2.     | Recommended Operating Conditions      |     |

|     | 4.3.     | Input and Output                      |     |

| 5.  | AC S     | witching Characteristics              | 27  |

|     | 5.1.     | I/O Standards Specifications          | 27  |

|     | 5.2.     | Clocking Specifications               |     |

|     | 5.3.     | Fabric Specifications                 | 50  |

|     | 5.4.     | Transceiver Switching Characteristics | 53  |

|     | 5.5.     | Transceiver Protocol Characteristics  | 67  |

|     | 5.6.     | Non-Volatile Characteristics          | 75  |

|     | 5.7.     | System Services                       | 84  |

|     | 5.8.     | Fabric Macros                         | 85  |

|     | 5.9.     | Power-Up to Functional Timing         | 89  |

|     | 5.10.    | Dedicated Pins                        | 93  |

|     | 5.11.    | User Crypto                           | 96  |

| 6.  | Revis    | sion History                          | 102 |

| The | Micro    | ochip Website                         | 106 |

| Pro | duct C   | Change Notification Service           | 106 |

| Cu  | stomer   | Support                               | 106 |

| Mic | rochip   | Devices Code Protection Feature       | 106 |

| Leç | al Not   | ice                                   | 106 |

| Tra | demar    | ks                                    | 107 |

| Qu  | ality Ma | anagement System                      | 108 |

| Wo  | rldwide  | e Sales and Service                   | 109 |

#### 1. References

The following documents are recommended references. For more information about PolarFire static and dynamic power data, see the PolarFire Power Estimator Spreadsheet.

- PolarFire FPGA Product Overview

- ER0217: PolarFire FPGA Pre-Production Device Errata

- UG0722: PolarFire FPGA Packaging and Pin Descriptions User Guide

- UG0726: PolarFire FPGA Board Design User Guide

- PolarFire FPGA and PolarFire SoC FPGA User I/O User Guide

- PolarFire FPGA and PolarFire SoC FPGA Fabric User Guide

- PolarFire FPGA and PolarFire SoC FPGA Programming User Guide

- PolarFire FPGA and PolarFire SoC FPGA Clocking Resources User Guide

- UG0687: PolarFire FPGA 1G Ethernet Solutions User Guide

- UG0727: PolarFire FPGA 10G Ethernet Solutions User Guide

- UG0748: PolarFire FPGA Low Power User Guide

- PolarFire FPGA and PolarFire SoC FPGA Memory Controller User Guide

- UG0743: PolarFire FPGA Debugging User Guide

- PolarFire FPGA and PolarFire SoC FPGA Power-Up and Resets User Guide

- PolarFire FPGA and PolarFire SoC FPGA Transceiver User Guide

- PolarFire FPGA and PolarFire SoC FPGA PCI Express User Guide

- PolarFire FPGA and PolarFire SoC FPGA Security User Guide

- UG0897: PolarFire and PolarFire SoC FPGA Power Estimator User Guide

#### **Device Offering** 2.

The following table lists the PolarFire FPGA device options using the MPF300T as an example. The MPF050T, MPF100T, MPF200T, and MPF500T device densities have identical offerings.

Table 2-1. PolarFire FPGA Device Options

| Device    | Extended    | Industrial    | STD | -1  | Transceivers | Lower Static | Data     |

|-----------|-------------|---------------|-----|-----|--------------|--------------|----------|

| Options   | Commercial  | -40 °C-100 °C |     |     | (T)          | Power        | Security |

|           | 0 °C-100 °C |               |     |     |              | (L)          | (S)      |

| MPF300T   | Yes         | Yes           | Yes | Yes | Yes          | _            | _        |

| MPF300TL  | Yes         | Yes           | Yes | _   | Yes          | Yes          | _        |

| MPF300TS  | _           | Yes           | Yes | Yes | Yes          | _            | Yes      |

| MPF300TLS | _           | Yes           | Yes | _   | Yes          | Yes          | Yes      |

Table 2-2. Orderable Military (–55  $^{\circ}$ C T $_{J}$  to 125  $^{\circ}$ C T $_{J}$ ) Device Part Numbers

| STD Speed Grade  | –1 Speed Grade |

|------------------|----------------|

| MPF200TS-FCS325M | N/A            |

| MPF300TS-FC484M  | N/A            |

| MPF300TS-FCV484M | N/A            |

| MPF300TS-FCS536M | N/A            |

| MPF300TS-FC784M  | N/A            |

| MPF500TS-FC784M  | N/A            |

| MPF500TS-FC1152M | N/A            |

Table 2-3. Orderable Automotive (–40  $^{\circ}\text{C T}_{J}$  to 125  $^{\circ}\text{C T}_{J})$  Device Part Numbers

| STD Speed Grade   | –1 Speed Grade     |

|-------------------|--------------------|

| MPF100T-FCG484T2  | MPF100T-1FCG484T2  |

| MPF100T-FCVG484T2 | MPF100T-1FCVG484T2 |

| MPF100T-FCSG325T2 | MPF100T-1FCSG325T2 |

| MPF200T-FCG484T2  | MPF200T-1FCG484T2  |

| MPF200T-FCVG484T2 | MPF200T-1FCVG484T2 |

| MPF200T-FCSG325T2 | MPF200T-1FCSG325T2 |

| MPF200T-FCSG536T2 | MPF200T-1FCSG536T2 |

| MPF300T-FCVG484T2 | MPF300T-1FCVG484T2 |

| MPF300T-FCSG536T2 | MPF300T-1FCSG536T2 |

## 3. Silicon and Libero Tool Status

There are three status levels:

- Advanced Initial estimated information based on simulations.

- **Preliminary** Information based on simulation and/or initial characterization.

- **Production** Final production data.

The following tables list the status of the PolarFire FPGA silicon and Libero Timing and Power tool.

Table 3-1. PolarFire FPGA Silicon Status

| Product              | Silicon                             |

|----------------------|-------------------------------------|

| MPF100T, TS, TL, TLS | Production – all temperature grades |

| MPF200T, TS, TL, TLS | Production – all temperature grades |

| MPF300T, TS, TL, TLS | Production – all temperature grades |

| MPF500T, TS, TL, TLS | Production – all temperature grades |

Table 3-2. PolarFire FPGA Tool Status

| Device                     | Status                                       | Libero Version         |        |            |        |                        |        |            |        |

|----------------------------|----------------------------------------------|------------------------|--------|------------|--------|------------------------|--------|------------|--------|

|                            |                                              | Timing                 |        |            |        | Power                  |        |            |        |

|                            |                                              | Extended<br>Commercial |        | Industrial |        | Extended<br>Commercial |        | Industrial |        |

|                            |                                              | STD                    | -1     | STD        | -1     | STD                    | -1     | STD        | -1     |

| MPF050T,<br>TS, TL,<br>TLS | Preliminary V <sub>DD</sub> = 1.0V,<br>1.05V | 2021.2                 | 2021.2 | 2021.2     | 2021.2 | 2021.2                 | 2021.2 | 2021.2     | 2021.2 |

| MPF100T,                   | Production V <sub>DD</sub> = 1.0V            | 12.1                   | 12.1   | 12.1       | 12.1   | 12.1                   | 12.1   | 12.1       | 12.1   |

| TS, TL,<br>TLS             | Production V <sub>DD</sub> = 1.05V           | 12.2                   | 12.2   | 12.2       | 12.2   | 12.2                   | 12.2   | 12.2       | 12.2   |

| MPF200T,<br>TS, TL,        | Production V <sub>DD</sub> = 1.0V            | 12.1                   | 12.1   | 12.1       | 12.1   | 12.1                   | 12.1   | 12.1       | 12.1   |

| TLS                        | Production V <sub>DD</sub> = 1.05V           | 12.2                   | 12.2   | 12.2       | 12.2   | 12.2                   | 12.2   | 12.2       | 12.2   |

| MPF300T,                   | Production V <sub>DD</sub> = 1.0V            | 12.1                   | 12.0   | 12.1       | 12.1   | 12.1                   | 12.1   | 12.1       | 12.1   |

| TS, TL,<br>TLS             | Production V <sub>DD</sub> = 1.05V           | 12.2                   | 12.2   | 12.2       | 12.2   | 12.2                   | 12.2   | 12.2       | 12.2   |

| MPF500T,<br>TS, TL,        | Production V <sub>DD</sub> = 1.0V            | 12.2                   | 12.2   | 12.2       | 12.2   | 12.2                   | 12.2   | 12.2       | 12.2   |

| TLS                        | Production V <sub>DD</sub> = 1.05V           | 12.2                   | 12.2   | 12.2       | 12.2   | 12.2                   | 12.2   | 12.2       | 12.2   |

Table 3-3. Military

| Device   | Status                             | Libero Version |          |  |  |

|----------|------------------------------------|----------------|----------|--|--|

|          |                                    | Timing         | Power    |  |  |

|          |                                    | Military       | Military |  |  |

|          |                                    | STD            | STD      |  |  |

| MPF200TS | Production V <sub>DD</sub> = 1.0V  | 12.5           | 12.5     |  |  |

|          | Production V <sub>DD</sub> = 1.05V | 12.5           | 12.5     |  |  |

| MPF300TS | Production V <sub>DD</sub> = 1.0V  | 12.3           | 12.3     |  |  |

|          | Production V <sub>DD</sub> = 1.05V | 12.5           | 12.5     |  |  |

| MPF500TS | Production V <sub>DD</sub> = 1.0V  | 12.5           | 12.5     |  |  |

|          | Production V <sub>DD</sub> = 1.05V | 12.5           | 12.5     |  |  |

Table 3-4. Automotive T2

| Device  | Status                             | Libero Version |      |               |      |  |  |

|---------|------------------------------------|----------------|------|---------------|------|--|--|

|         |                                    | Timing         |      | Power         |      |  |  |

|         |                                    | Automotive -   | Г2   | Automotive T2 |      |  |  |

|         |                                    | STD            | -1   | STD           | -1   |  |  |

| MPF100T | Production V <sub>DD</sub> = 1.0V  | 12.6           | 12.6 | 12.6          | 12.6 |  |  |

|         | Production V <sub>DD</sub> = 1.05V | 12.6           | 12.6 | 12.6          | 12.6 |  |  |

| MPF200T | Production V <sub>DD</sub> = 1.0V  | 12.6           | 12.6 | 12.6          | 12.6 |  |  |

|         | Production V <sub>DD</sub> = 1.05V | 12.6           | 12.6 | 12.6          | 12.6 |  |  |

| MPF300T | Production V <sub>DD</sub> = 1.0V  | 12.6           | 12.6 | 12.6          | 12.6 |  |  |

|         | Production V <sub>DD</sub> = 1.05V | 12.6           | 12.6 | 12.6          | 12.6 |  |  |

### 4. DC Characteristics

This section lists the DC characteristics of the PolarFire FPGA device.

## 4.1 Absolute Maximum Rating

The following table lists the absolute maximum ratings for PolarFire devices.

Table 4-1. Absolute Maximum Rating

| Parameter                                                | Symbol                             | Min  | Max  | Unit |

|----------------------------------------------------------|------------------------------------|------|------|------|

| FPGA core power supply                                   | V <sub>DD</sub>                    | -0.5 | 1.13 | V    |

| Transceiver Tx and Rx lanes supply                       | $V_{DDA}$                          | -0.5 | 1.13 | V    |

| Programming and HSIO receiver supply                     | V <sub>DD18</sub>                  | -0.5 | 2.0  | V    |

| FPGA core and FPGA PLL high-voltage supply               | $V_{DD25}$                         | -0.5 | 2.7  | V    |

| Transceiver PLL high-voltage supply                      | V <sub>DDA25</sub>                 | -0.5 | 2.7  | V    |

| Transceiver reference clock supply                       | V <sub>DD_XCVR_CLK</sub>           | -0.5 | 3.6  | V    |

| Global V <sub>REF</sub> for transceiver reference clocks | XCVR <sub>VREF</sub>               | -0.5 | 3.6  | V    |

| HSIO DC I/O supply <sup>2</sup>                          | V <sub>DDIx</sub>                  | -0.5 | 2.0  | V    |

| GPIO DC I/O supply <sup>2</sup>                          | V <sub>DDIx</sub>                  | -0.5 | 3.6  | V    |

| Dedicated I/O DC supply for JTAG and SPI                 | V <sub>DDI3</sub>                  | -0.5 | 3.6  | V    |

| GPIO auxiliary power supply for I/O bank x <sup>2</sup>  | $V_{DDAUXx}$                       | -0.5 | 3.6  | V    |

| Maximum DC input voltage on GPIO                         | V <sub>IN</sub>                    | -0.5 | 3.8  | V    |

| Maximum DC input voltage on HSIO                         | V <sub>IN</sub>                    | -0.5 | 2.2  | V    |

| Transceiver receiver absolute input voltage              | Transceiver V <sub>IN</sub>        | -0.5 | 1.26 | V    |

| Transceiver reference clock absolute input voltage       | Transceiver REFCLK V <sub>IN</sub> | -0.5 | 3.6  | V    |

| Storage temperature (ambient) <sup>1</sup>               | T <sub>STG</sub>                   | -65  | 150  | °C   |

| Junction temperature <sup>1</sup>                        | T <sub>J</sub>                     | -55  | 135  | °C   |

| Maximum soldering temperature RoHS                       | T <sub>SOLROHS</sub>               | _    | 260  | °C   |

- See Table 5-61. FPGA and μPROM Programming Cycles vs. Retention Characteristics for retention time vs.

temperature. The total time used in calculating the device retention includes the device operating temperature

time and temperature during storage time.

- 2. The power supplies for a given I/O bank x are shown as  $V_{DDIx}$  and  $V_{DDAUXx}$ .

- 3. Absolute maximum ratings are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the recommended operating conditions specified in Table 4-2. Recommended Operating Conditions is not implied. Stresses beyond those listed in the following table might cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 4.2 Recommended Operating Conditions

The following table lists the recommended operating conditions.

**Table 4-2. Recommended Operating Conditions**

| Parameter                                                             | Symbol                   | Min    | Тур     | Max                      | Unit | Condition                                                                                                                             |

|-----------------------------------------------------------------------|--------------------------|--------|---------|--------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| FPGA core supply at 1.0V mode <sup>1, 6</sup>                         | V <sub>DD</sub>          | 0.97   | 1.00    | 1.03                     | V    | _                                                                                                                                     |

| FPGA core supply at 1.05V mode <sup>1, 6</sup>                        | V <sub>DD</sub>          | 1.02   | 1.05    | 1.08                     | V    | _                                                                                                                                     |

| Transceiver Tx and Rx lanes supply (1.0V mode) <sup>6, 7</sup>        | $V_{DDA}$                | 0.97   | 1.00    | 1.03                     | V    | When all lane rates are 10.3125 Gbps or less. <sup>1</sup>                                                                            |

| Transceiver Tx and Rx lanes supply (1.05V mode) <sup>6</sup>          | V <sub>DDA</sub>         | 1.02   | 1.05    | 1.08                     | V    | Must when any lane rate is greater than 10.3125 Gbps. Lane rates 10.3125 Gbps or less may also be powered in 1.05V mode. <sup>1</sup> |

| Programming and HSIO receiver supply <sup>6</sup>                     | V <sub>DD18</sub>        | 1.71   | 1.80    | 1.89                     | V    | _                                                                                                                                     |

| FPGA core and FPGA PLL high-voltage supply <sup>6</sup>               | V <sub>DD25</sub>        | 2.425  | 2.50    | 2.575                    | V    | _                                                                                                                                     |

| Transceiver PLL high-voltage supply <sup>6</sup>                      | V <sub>DDA25</sub>       | 2.425  | 2.50    | 2.575                    | V    | _                                                                                                                                     |

| Transceiver reference clock supply <sup>6, 7</sup>                    | V <sub>DD_XCVR_CLK</sub> | 3.135  | 3.3     | 3.465                    | V    | 3.3V nominal                                                                                                                          |

| зирріу                                                                |                          | 2.375  | 2.5     | 2.625                    | V    | 2.5V nominal                                                                                                                          |

| Global V <sub>REF</sub> for transceiver reference clocks <sup>3</sup> | XCVR <sub>VREF</sub>     | Ground | _       | V <sub>DD_XCVR_CLK</sub> | V    | _                                                                                                                                     |

| HSIO DC I/O supply <sup>6</sup>                                       | V <sub>DDIx</sub>        | 1.14   | Various | 1.89                     | V    | Allowed nominal options: 1.2V, 1.35V, 1.5V, and 1.8V <sup>4, 5</sup>                                                                  |

| GPIO DC I/O supply <sup>6</sup>                                       | V <sub>DDIx</sub>        | 1.14   | Various | 3.465                    | V    | Allowed nominal options: 1.2V, 1.5V, 1.8V, 2.5V, and 3.3V <sup>2, 4, 5</sup>                                                          |

| Dedicated I/O DC supply for JTAG and SPI (GPIO Bank 3) <sup>6</sup>   | V <sub>DDI3</sub>        | 1.71   | Various | 3.465                    | V    | Allowed nominal options: 1.8V, 2.5V, and 3.3V                                                                                         |

| GPIO auxiliary supply <sup>6</sup>                                    | V <sub>DDAUXx</sub>      | 3.135  | 3.3     | 3.465                    | V    | For I/O bank x with V <sub>DDIx</sub> = 3.3V nominal <sup>2, 4, 5</sup>                                                               |

|                                                                       |                          | 2.375  | 2.5     | 2.625                    | V    | For I/O bank x with V <sub>DDIx</sub> = 2.5V nominal or lower <sup>2</sup> , 4, 5                                                     |

| Extended commercial temperature range                                 | T <sub>J</sub>           | 0      | _       | 100                      | °C   | _                                                                                                                                     |

| continued                                         |                  |             |     |     |      |           |

|---------------------------------------------------|------------------|-------------|-----|-----|------|-----------|

| Parameter                                         | Symbol           | Min         | Тур | Max | Unit | Condition |

| Industrial temperature range                      | T <sub>J</sub>   | -40         | _   | 100 | °C   | _         |

| Automotive T2 temperature range                   | T <sub>J</sub>   | -40         | _   | 125 | °C   | _         |

| Military temperature range                        | T <sub>J</sub>   | <b>-</b> 55 | _   | 125 | °C   | _         |

| Extended commercial programming temperature range | T <sub>PRG</sub> | 0           | _   | 100 | °C   | _         |

| Industrial programming temperature range          | T <sub>PRG</sub> | -40         | _   | 100 | °C   | _         |

- V<sub>DD</sub> and V<sub>DDA</sub> can independently operate at 1.0V or 1.05V nominal. These supplies are not dynamically adjustable.

- 2. For GPIO buffers where I/O bank is designated as bank number, if V<sub>DDIx</sub> is 2.5V nominal or 3.3V nominal, V<sub>DDAUXx</sub> must be connected to the V<sub>DDIx</sub> supply for that bank. If V<sub>DDIx</sub> for a given GPIO bank is <2.5V nominal, V<sub>DDAUXx</sub> per I/O bank must be powered at 2.5V nominal.

- XCVR<sub>VREF</sub> globally sets the reference voltage of the transceiver's single-ended reference clock input buffers. It is typically near V<sub>DD\_XCVR</sub> <sub>CLK</sub>/2V but is allowed in the specified range.

- The power supplies for a given I/O bank x are shown as V<sub>DDIx</sub> and V<sub>DDAUXx</sub>.

- At power-up and power-down, the V<sub>DDIX</sub> and V<sub>DDAUXx</sub> supply sequencing can cause signal glitches. Refer to PolarFire FPGA and PolarFire SoC FPGA User I/O User Guide and UG0726: PolarFire FPGA Board Design User Guide for detailed explanation and recommended steps.

- The recommended power supply tolerances include DC offset of the supply plus any power supply ripple over the customer design frequencies of interest, as measured at the device package pins. An example for a valid power supply that meets the recommendations for the VDD supply is 1.0V ±10 mV or 1.05V ±10 mV for DC offset with an additional power supply ripple of ±20 mV for a total of 1.0V ±30 mV or 1.05V ±30 mV.

- Both V<sub>DDA</sub> and V<sub>DD XCVR CLK</sub> supplies must be powered when any of the transceivers are used. V<sub>DD XCVR CLK</sub> must power on within the I/O calibration time (as specified for the device in Libero). V<sub>DDA</sub> and V<sub>DD XCVR CLK</sub> must both then remain powered during operation. If V<sub>DDA</sub> needs to be powered down, V<sub>DD XCVR CLK</sub> must also be powered down. There is no required sequence for powering up or down V<sub>DDA</sub> and V<sub>DD XCVR</sub> CLK.

#### 4.2.1 **DC Characteristics over Recommended Operating Conditions**

The following table lists the DC characteristics over recommended operating conditions.

Table 4-3. DC Characteristics over Recommended Operating Conditions

| Parameter                               | Symbol                                       | Min | Max | Unit | Condition            |

|-----------------------------------------|----------------------------------------------|-----|-----|------|----------------------|

| Input pin capacitance <sup>1</sup>      | C <sub>IN</sub> (GPIO)  Dedicated input pins | _   | 5.6 | pf   | _                    |

|                                         | C <sub>IN</sub> (HSIO)                       | _   | 2.8 | pf   | _                    |

| Input or output leakage current per pin | I <sub>L</sub> (GPIO)                        | _   | 10  | μΑ   | I/O disabled, high—Z |

| current per pill                        | I <sub>L</sub> (HSIO)                        | _   | 10  | μΑ   | I/O disabled, high—Z |

| continued                                             |                 |     |     |      |                           |

|-------------------------------------------------------|-----------------|-----|-----|------|---------------------------|

| Parameter                                             | Symbol          | Min | Max | Unit | Condition                 |

| Pad pull-up when V <sub>IN</sub> = 0                  | I <sub>PU</sub> | 137 | 220 | μΑ   | V <sub>DDIx</sub> = 3.3V  |

| Pad pull-up when V <sub>IN</sub> = 0                  |                 | 102 | 166 | μA   | V <sub>DDIx</sub> = 2.5V  |

| Pad pull-up when V <sub>IN</sub> = 0                  |                 | 68  | 115 | μA   | V <sub>DDIx</sub> = 1.8V  |

| Pad pull-up when V <sub>IN</sub> = 0                  |                 | 51  | 88  | μA   | V <sub>DDIx</sub> = 1.5V  |

| Pad pull-up when V <sub>IN</sub> = 0                  |                 | 29  | 73  | μA   | V <sub>DDIx</sub> = 1.35V |

| Pad pull-up when V <sub>IN</sub> = 0                  |                 | 16  | 46  | μA   | V <sub>DDIx</sub> = 1.2V  |

| Pad pull-down when V <sub>IN</sub> = 3.3V (GPIO only) | I <sub>PD</sub> | 65  | 187 | μΑ   | V <sub>DDIx</sub> = 3.3V  |

| Pad pull-down when V <sub>IN</sub> = 2.5V (GPIO only) |                 | 63  | 160 | μΑ   | V <sub>DDIx</sub> = 2.5V  |

| Pad pull-down when V <sub>IN</sub> = 1.8V             |                 | 60  | 117 | μΑ   | V <sub>DDIx</sub> = 1.8V  |

| Pad pull-down when V <sub>IN</sub> = 1.5V             |                 | 57  | 95  | μΑ   | V <sub>DDIx</sub> = 1.5V  |

| Pad pull-down when V <sub>IN</sub> = 1.35V            |                 | 52  | 86  | μΑ   | V <sub>DDIx</sub> = 1.35V |

| Pad pull-down when V <sub>IN</sub> = 1.2V             |                 | 47  | 79  | μΑ   | V <sub>DDIx</sub> = 1.2V  |

1. Represents the die input capacitance at the pad (not the package).

Table 4-4. Minimum and Maximum Rise and Fall Times

| Parameter                                                     | Symbol            | Min                   | Мах                 | Unit | Maximum<br>Frequency        | Condition                                      |

|---------------------------------------------------------------|-------------------|-----------------------|---------------------|------|-----------------------------|------------------------------------------------|

| Input rise time <sup>1,4</sup> Input fall time <sup>1,4</sup> | T <sub>RISE</sub> | 200 ps <sup>2,3</sup> | 10% signal period   | ps   | F ≤ 100<br>KHz              | Min (10% signal period, 1 µs) <sup>5</sup>     |

|                                                               |                   |                       | 12.5% signal period | ps   | 100 KHz <<br>F ≤ 400<br>KHz | Min (12.5% signal period, 300 ns) <sup>6</sup> |

|                                                               |                   |                       | 20% signal period   | ps   | 400 KHz <<br>F ≤ 50 MHz     | Min (20% signal period, 50 ns) <sup>7</sup>    |

|                                                               |                   |                       | 4                   | ns   | 50 MHz < F<br>≤ 125 MHz     | Not to exceed 4 ns <sup>8</sup>                |

|                                                               |                   |                       | 50% signal period   | ns   | 125 MHz <<br>F ≤ 800<br>MHz | Sawtooth waveform <sup>9</sup>                 |

Voltage ramp must be monotonic. For single-ended I/O standards, input rise time is specified from 10%–90% of V<sub>DDIx</sub> and input fall time is specified from 90%–10% of V<sub>DDIx</sub>. For voltage referenced and differential I/O configurations, ramp times must always comply with I/O standard requirements to ensure compliance.

- Input slew rates must be controlled to never exceed PAD overshoot/undershoot requirements. Input pad 2. overshoot and undershoot specifications are shown in section Maximum Allowed Overshoot and Undershoot.

- 3. Rise and fall times in this table are for unterminated inputs. When inputs are terminated, minimum ramp time is not restricted. Recommended minimum ramp time is 25% of bit period, not to exceed a rate of 5 V/ns.

- 4. Ramp times must not exceed I/O standard requirements to ensure compliance.

- 5. For signal frequencies <100 KHz, maximum rise time is 1 µs. For example, if signal frequency (F) is 100 KHz, 10% of signal period is 1 µs. The maximum ramp time allowed is the 1 µs limit. However, if signal frequency is 10 KHz, then 10% of signal period is 10 µs which exceeds the maximum limit of 1 µs. The maximum ramp time allowed is therefore 1 µs.

- For 100 KHz < signal frequencies ≤ 400 KHz, maximum rise time is 300 ns. For example, if signal frequency is 400 KHz, then 12.5% of signal period is 312.5 ns. The maximum ramp time allowed is 300 µs. If the signal frequency is 200 KHz, then 12.5% of signal period is 625 ns. The maximum ramp time allowed is therefore 300 ns.

- For 400 KHz < signal frequencies ≤ 50 MHz, maximum rise time is 50 ns or 20% of signal period, whichever is less. For example, if signal frequency is 50 MHz, then 20% of signal period is 4 ns. The maximum ramp time allowed is therefore 4 ns, even if the max limit is 50 ns. If the signal frequency is 1 MHz, then 20% of signal period is 200 ns. The maximum ramp time allowed is therefore 50 ns.

- For 50 MHz < signal frequencies ≤ 125 MHz, maximum rise time is 4 ns. For example, if signal frequency is 125 MHz, then the maximum ramp time allowed is 4 ns (sawtooth signal). If the signal frequency is 75 MHz, the maximum ramp time allowed at 75 MHz is still 4 ns.

- For 125 MHz < signal frequencies ≤ 800 MHz, maximum rise time is 50% of signal frequency (sawtooth signal). For example, if signal frequency is 250 MHz, then the maximum ramp time allowed is 2 ns. If the signal frequency is 800 MHz, the maximum ramp time allowed is 0.625 ns.

#### 4.2.2 **Maximum Allowed Overshoot and Undershoot**

During transitions, input signals may overshoot and undershoot the voltage listed as follows. Input currents must be limited to less than 100 mA per latch-up specifications.

The maximum overshoot duration is specified as a high-time percentage over the lifetime of the device. A DC signal is equivalent to 100% of the duty cycle.

The following tables list the maximum AC input voltage (V<sub>IN</sub>) overshoot duration for HSIO.

Table 4-5. Maximum Overshoot During Transitions for HSIO at  $T_J$  = 100 °C

| AC (V <sub>IN</sub> ) Overshoot Duration as % at T <sub>J</sub> = 100 °C | Condition (V) |

|--------------------------------------------------------------------------|---------------|

| 100                                                                      | 1.8           |

| 100                                                                      | 1.85          |

| 100                                                                      | 1.9           |

| 100                                                                      | 1.95          |

| 100                                                                      | 2             |

| 100                                                                      | 2.05          |

| 100                                                                      | 2.1           |

| 100                                                                      | 2.15          |

| 100                                                                      | 2.2           |

| 90                                                                       | 2.25          |

| 30                                                                       | 2.3           |

| 7.5                                                                      | 2.35          |

| continued                                                 |               |  |  |

|-----------------------------------------------------------|---------------|--|--|

| AC ( $V_{IN}$ ) Overshoot Duration as % at $T_J$ = 100 °C | Condition (V) |  |  |

| 1.9                                                       | 2.4           |  |  |

**Note:** Overshoot level is for  $V_{DDI}$  at 1.8V.

Table 4-6. Maximum Overshoot During Transitions for HSIO at  $T_J$  = 125  $^{\circ}$ C

| AC (V <sub>IN</sub> ) Overshoot Duration as % at T <sub>J</sub> = 125 °C | Condition (V) |

|--------------------------------------------------------------------------|---------------|

| 100                                                                      | 1.8           |

| 100                                                                      | 1.85          |

| 100                                                                      | 1.9           |

| 100                                                                      | 1.95          |

| 100                                                                      | 2             |

| 100                                                                      | 2.05          |

| 100                                                                      | 2.1           |

| 100                                                                      | 2.15          |

| 100                                                                      | 2.2           |

| 35                                                                       | 2.25          |

| 8                                                                        | 2.3           |

| 2                                                                        | 2.35          |

| 0.5                                                                      | 2.4           |

Note: Overshoot level is for  $V_{DDI}$  at 1.8V.

The following table lists the maximum AC input voltage  $(V_{\text{IN}})$  undershoot duration for HSIO.

Table 4-7. Maximum Undershoot During Transitions for HSIO at  $T_{\rm J}$  = 100  $^{\circ}{\rm C}$

| AC ( $V_{IN}$ ) Undershoot Duration as % at $T_J$ = 100 °C | Condition (V) |

|------------------------------------------------------------|---------------|

| 100                                                        | -0.05         |

| 100                                                        | -0.1          |

| 100                                                        | -0.15         |

| 100                                                        | -0.2          |

| 100                                                        | -0.25         |

| 100                                                        | -0.3          |

| 100                                                        | -0.35         |

| 100                                                        | -0.4          |

| 44                                                         | -0.45         |

| 14                                                         | -0.5          |

| 4.8                                                        | -0.55         |

| continued                                                                 |               |

|---------------------------------------------------------------------------|---------------|

| AC (V <sub>IN</sub> ) Undershoot Duration as % at T <sub>J</sub> = 100 °C | Condition (V) |

| 1.6                                                                       | -0.6          |

Table 4-8. Maximum Undershoot During Transitions for HSIO at  $T_J$  = 125  $^{\circ}$ C

| AC (V <sub>IN</sub> ) Undershoot Duration as % at T <sub>J</sub> = 125 °C | Condition (V) |

|---------------------------------------------------------------------------|---------------|

| 100                                                                       | -0.05         |

| 100                                                                       | -0.1          |

| 100                                                                       | -0.15         |

| 100                                                                       | -0.2          |

| 100                                                                       | -0.25         |

| 100                                                                       | -0.3          |

| 86                                                                        | -0.35         |

| 26                                                                        | -0.4          |

| 8                                                                         | -0.45         |

| 2.6                                                                       | -0.5          |

| 0.8                                                                       | -0.55         |

| 0.3                                                                       | -0.6          |

The following table lists the maximum AC input voltage  $(V_{\text{IN}})$  overshoot duration for GPIO.

Table 4-9. Maximum Overshoot During Transitions for GPIO at  $T_J$  = 100  $^{\circ}$ C

| AC (V <sub>IN</sub> ) Overshoot Duration as % at T <sub>J</sub> = 100 °C | Condition (V) |

|--------------------------------------------------------------------------|---------------|

| 100                                                                      | 3.8           |

| 100                                                                      | 3.85          |

| 100                                                                      | 3.9           |

| 100                                                                      | 3.95          |

| 70                                                                       | 4             |

| 50                                                                       | 4.05          |

| 33                                                                       | 4.1           |

| 22                                                                       | 4.15          |

| 14                                                                       | 4.2           |

| 9.8                                                                      | 4.25          |

| 6.5                                                                      | 4.3           |

| 4.4                                                                      | 4.35          |

| 3                                                                        | 4.4           |

| 2                                                                        | 4.45          |

| continued                                                                |               |  |  |  |  |  |  |

|--------------------------------------------------------------------------|---------------|--|--|--|--|--|--|

| AC (V <sub>IN</sub> ) Overshoot Duration as % at T <sub>J</sub> = 100 °C | Condition (V) |  |  |  |  |  |  |

| 1.4                                                                      | 4.5           |  |  |  |  |  |  |

| 0.9                                                                      | 4.55          |  |  |  |  |  |  |

| 0.6                                                                      | 4.6           |  |  |  |  |  |  |

Note: Overshoot level is for  $V_{DDI}$  at 3.3V.

Table 4-10. Maximum Overshoot During Transitions for GPIO at  $T_J$  = 125  $^{\circ}$ C

| AC (V <sub>IN</sub> ) Overshoot Duration as % at T <sub>J</sub> = 125 °C | Condition (V) |

|--------------------------------------------------------------------------|---------------|

| 100                                                                      | 3.8           |

| 84                                                                       | 3.85          |

| 54                                                                       | 3.9           |

| 35                                                                       | 3.95          |

| 23                                                                       | 4             |

| 15                                                                       | 4.05          |

| 10                                                                       | 4.1           |

| 6.6                                                                      | 4.15          |

| 4.4                                                                      | 4.2           |

| 2.9                                                                      | 4.25          |

| 1.9                                                                      | 4.3           |

| 1.3                                                                      | 4.35          |

| 0.9                                                                      | 4.4           |

| 0.6                                                                      | 4.45          |

| 0.4                                                                      | 4.5           |

| 0.28                                                                     | 4.55          |

| 0.19                                                                     | 4.6           |

Note: Overshoot level is  $V_{DDI}$  at 3.3V.

The following table lists the maximum AC input voltage  $(V_{\text{IN}})$  undershoot duration for GPIO.

Table 4-11. Maximum Undershoot During Transitions for GPIO at  $T_J$  = 100  $^{\circ}$ C

| AC (V <sub>IN</sub> ) Undershoot Duration as % at T <sub>J</sub> = 100 °C | Condition (V) |

|---------------------------------------------------------------------------|---------------|

| 100                                                                       | -0.5          |

| 100                                                                       | -0.55         |

| 100                                                                       | -0.6          |

| 100                                                                       | -0.65         |

| 100                                                                       | -0.7          |

| 100                                                                       | -0.75         |

| continued                                                                 |               |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------|---------------|--|--|--|--|--|--|--|

| AC (V <sub>IN</sub> ) Undershoot Duration as % at T <sub>J</sub> = 100 °C | Condition (V) |  |  |  |  |  |  |  |

| 100                                                                       | -0.8          |  |  |  |  |  |  |  |

| 100                                                                       | -0.85         |  |  |  |  |  |  |  |

| 100                                                                       | -0.9          |  |  |  |  |  |  |  |

| 100                                                                       | -0.95         |  |  |  |  |  |  |  |

| 100                                                                       | -1            |  |  |  |  |  |  |  |

| 100                                                                       | -1.05         |  |  |  |  |  |  |  |

| 100                                                                       | -1.1          |  |  |  |  |  |  |  |

| 100                                                                       | -1.15         |  |  |  |  |  |  |  |

| 100                                                                       | -1.2          |  |  |  |  |  |  |  |

| 69                                                                        | -1.25         |  |  |  |  |  |  |  |

| 45                                                                        | -1.3          |  |  |  |  |  |  |  |

Table 4-12. Maximum Undershoot During Transitions for GPIO at  $T_J$  = 125  $^{\circ}$ C

| AC (V <sub>IN</sub> ) Undershoot Duration as % at T <sub>J</sub> = 125 °C | Condition (V) |

|---------------------------------------------------------------------------|---------------|

| 100                                                                       | -0.5          |

| 100                                                                       | -0.55         |

| 100                                                                       | -0.6          |

| 100                                                                       | -0.65         |

| 100                                                                       | -0.7          |

| 100                                                                       | -0.75         |

| 100                                                                       | -0.8          |

| 100                                                                       | -0.85         |

| 100                                                                       | -0.9          |

| 100                                                                       | -0.95         |

| 100                                                                       | <b>-1</b>     |

| 100                                                                       | -1.05         |

| 78                                                                        | -1.1          |

| 50                                                                        | -1.15         |

| 32                                                                        | -1.2          |

| 20                                                                        | -1.25         |

| 13                                                                        | -1.3          |

#### 4.2.2.1 **Power Supply Ramp Times**

The following table lists the allowable power-up ramp times. Times shown correspond to the ramp of the supply from 0V to the minimum recommended voltage as specified in the section Recommended Operating Conditions. All supplies must rise and fall monotonically.

**Table 4-13. Power Supply Ramp Times**

| Parameter                                                | Symbol                    | Min | Max | Unit |

|----------------------------------------------------------|---------------------------|-----|-----|------|

| FPGA core supply                                         | V <sub>DD</sub>           | 0.2 | 50  | ms   |

| Transceiver core supply                                  | $V_{DDA}$                 | 0.2 | 50  | ms   |

| Must connect to 1.8V supply                              | V <sub>DD18</sub>         | 0.2 | 50  | ms   |

| Must connect to 2.5V supply                              | V <sub>DD25</sub>         | 0.2 | 50  | ms   |

| Must connect to 2.5V supply                              | V <sub>DDA25</sub>        | 0.2 | 50  | ms   |

| HSIO bank I/O power supplies                             | V <sub>DDI[0,1,6,7]</sub> | 0.2 | 50  | ms   |

| GPIO bank I/O power supplies                             | V <sub>DDI[2,4,5]</sub>   | 0.2 | 50  | ms   |

| Bank 3 dedicated I/O buffers (GPIO)                      | V <sub>DDI3</sub>         | 0.2 | 50  | ms   |

| GPIO bank auxiliary power supplies                       | V <sub>DDAUX[2,4,5]</sub> | 0.2 | 50  | ms   |

| Transceiver reference clock supply                       | V <sub>DD_XCVR_CLK</sub>  | 0.2 | 50  | ms   |

| Global V <sub>REF</sub> for transceiver reference clocks | XCVR <sub>VREF</sub>      | 0.2 | 50  | ms   |

**Note:** For proper operation of programming recovery mode, if a  $V_{DD}$  supply brown-out occurs during programming, a minimum supply ramp down time for only the  $V_{DD}$  supply is recommended to be 10 ms or longer by using a programmable regulator or on-board capacitors.

#### 4.2.2.2 Hot Socketing

The following table lists the hot socketing DC characteristics over recommended operating conditions.

Table 4-14. Hot Socketing DC Characteristics over Recommended Operating Conditions

| Parameter                                                                            | Symbol                  | Min | Тур | Max | Unit | Condition                               |

|--------------------------------------------------------------------------------------|-------------------------|-----|-----|-----|------|-----------------------------------------|

| Current per transceiver Rx input pin (P or N single-ended) <sup>1, 2</sup>           | I <sub>XCVRRX_HS</sub>  | _   | _   | ±4  | mA   | V <sub>DDA</sub> = 0V                   |

| Current per transceiver Tx output pin (P or N single-ended) $^{3}$                   | I <sub>XCVRTX_HS</sub>  | _   | _   | ±10 | mA   | V <sub>DDA</sub> = 0V                   |

| Current per transceiver reference clock input pin (P or N single-ended) <sup>4</sup> | I <sub>XCVRREF_HS</sub> |     | _   | ±1  | mA   | V <sub>DD_XCVR_CLK</sub> = 0V           |

| Current per GPIO pin (P or N single-ended) <sup>5</sup>                              | I <sub>GPIO_HS</sub>    | _   | _   | ±1  | mA   | V <sub>DDIx</sub> = 0V                  |

| Current per HSIO pin (P or N single-ended)                                           | _                       |     | _   | _   | _    | Hot socketing is not supported in HSIO. |

- Assumes device is powered-down, all supplies are grounded, AC-coupled interface, and input pin pairs are driven by a CML driver at the maximum amplitude (1V pk-pk) that is toggling at any rate with PRBS7 data.

- 2. Each P and N transceiver input has less than the specified maximum input current.

- 3. Each P and N transceiver output is connected to a 40Ω resistor (50Ω CML termination—20% tolerance) to the maximum allowed output voltage (V<sub>DDAmax</sub> + 0.3V = 1.4V) through an AC-coupling capacitor with all PolarFire device supplies grounded. This shows the current for a worst-case DC-coupled interface. As an AC-coupled interface, the output signal will settle at ground and no hot socket current will be seen.

- 4.  $V_{DD\_XCVR\_CLK}$  is powered down and the device is driven to  $-0.3V < V_{IN} < V_{DD\_XCVR\_CLK}$ .

- 5.  $V_{DDIx}$  is powered down and the device is driven to  $-0.3V < V_{IN} < GPIO V_{DDImax}$ .

**Note:** The following dedicated pins do not support hot socketing: TMS, TDI, TRSTB, and DEVRST\_N. Weak pull-up (as specified in GPIO) is always enabled.

# 4.3 Input and Output

The following section describes DC I/O levels, differential and complementary differential DC I/O levels, HSIO and GPIO on-die termination specifications, and LVDS specifications.

#### 4.3.1 DC Input and Output Levels

The following tables list the DC I/O levels.

Table 4-15. DC Input Levels

| I/O Standard          | V <sub>DDI</sub><br>Min (V) | V <sub>DDI</sub><br>Typ (V) | V <sub>DDI</sub><br>Max (V) | V <sub>IL</sub><br>Min (V) | V <sub>IL</sub><br>Max (V) | V <sub>IH</sub><br>Min (V) | V <sub>IH</sub> <sup>1</sup><br>Max (V) |

|-----------------------|-----------------------------|-----------------------------|-----------------------------|----------------------------|----------------------------|----------------------------|-----------------------------------------|

| PCI                   | 3.15                        | 3.3                         | 3.45                        | -0.3                       | 0.3 × V <sub>DDI</sub>     | 0.5 × V <sub>DDI</sub>     | 3.45                                    |

| LVTTL                 | 3.15                        | 3.3                         | 3.45                        | -0.3                       | 0.8                        | 2                          | 3.45                                    |

| LVCMOS33              | 3.15                        | 3.3                         | 3.45                        | -0.3                       | 0.8                        | 2                          | 3.45                                    |

| LVCMOS25              | 2.375                       | 2.5                         | 2.625                       | -0.3                       | 0.7                        | 1.7                        | 2.625                                   |

| LVCMOS18              | 1.71                        | 1.8                         | 1.89                        | -0.3                       | 0.35 × V <sub>DDI</sub>    | 0.65 × V <sub>DDI</sub>    | 1.89                                    |

| LVCMOS15              | 1.425                       | 1.5                         | 1.575                       | -0.3                       | 0.35 × V <sub>DDI</sub>    | 0.65 × V <sub>DDI</sub>    | 1.575                                   |

| LVCMOS12              | 1.14                        | 1.2                         | 1.26                        | -0.3                       | 0.35 × V <sub>DDI</sub>    | 0.65 × V <sub>DDI</sub>    | 1.26                                    |

| SSTL25l <sup>2</sup>  | 2.375                       | 2.5                         | 2.625                       | -0.3                       | V <sub>REF</sub> – 0.15    | V <sub>REF</sub> + 0.15    | 2.625                                   |

| SSTL25II <sup>2</sup> | 2.375                       | 2.5                         | 2.625                       | -0.3                       | V <sub>REF</sub> – 0.15    | V <sub>REF</sub> + 0.15    | 2.625                                   |

| SSTL18I <sup>2</sup>  | 1.71                        | 1.8                         | 1.89                        | -0.3                       | V <sub>REF</sub> – 0.125   | V <sub>REF</sub> + 0.125   | 1.89                                    |

| SSTL18II <sup>2</sup> | 1.71                        | 1.8                         | 1.89                        | -0.3                       | V <sub>REF</sub> – 0.125   | V <sub>REF</sub> + 0.125   | 1.89                                    |

| SSTL15I               | 1.425                       | 1.5                         | 1.575                       | -0.3                       | V <sub>REF</sub> – 0.1     | V <sub>REF</sub> + 0.1     | 1.575                                   |

| SSTL15II              | 1.425                       | 1.5                         | 1.575                       | -0.3                       | V <sub>REF</sub> – 0.1     | V <sub>REF</sub> + 0.1     | 1.575                                   |

| SSTL135I              | 1.283                       | 1.35                        | 1.418                       | -0.3                       | V <sub>REF</sub> – 0.09    | V <sub>REF</sub> + 0.09    | 1.418                                   |

| SSTL135II             | 1.283                       | 1.35                        | 1.418                       | -0.3                       | V <sub>REF</sub> – 0.09    | V <sub>REF</sub> + 0.09    | 1.418                                   |

| HSTL15I               | 1.425                       | 1.5                         | 1.575                       | -0.3                       | V <sub>REF</sub> – 0.1     | V <sub>REF</sub> + 0.1     | 1.575                                   |

| HSTL15II              | 1.425                       | 1.5                         | 1.575                       | -0.3                       | V <sub>REF</sub> – 0.1     | V <sub>REF</sub> + 0.1     | 1.575                                   |

| HSTL135I              | 1.283                       | 1.35                        | 1.418                       | -0.3                       | V <sub>REF</sub> – 0.09    | V <sub>REF</sub> + 0.09    | 1.418                                   |

| HSTL135II             | 1.283                       | 1.35                        | 1.418                       | -0.3                       | V <sub>REF</sub> – 0.09    | V <sub>REF</sub> + 0.09    | 1.418                                   |

| HSTL12I               | 1.14                        | 1.2                         | 1.26                        | -0.3                       | V <sub>REF</sub> – 0.1     | V <sub>REF</sub> + 0.1     | 1.26                                    |

| HSTL12II              | 1.14                        | 1.2                         | 1.26                        | -0.3                       | V <sub>REF</sub> – 0.1     | V <sub>REF</sub> + 0.1     | 1.26                                    |

| HSUL18I               | 1.71                        | 1.8                         | 1.89                        | -0.3                       | 0.3 × V <sub>DDI</sub>     | $0.7 \times V_{DDI}$       | 1.89                                    |

| HSUL18II              | 1.71                        | 1.8                         | 1.89                        | -0.3                       | 0.3 × V <sub>DDI</sub>     | $0.7 \times V_{DDI}$       | 1.89                                    |

| continued    |                             |                             |                             |                            |                            |                            |                                         |

|--------------|-----------------------------|-----------------------------|-----------------------------|----------------------------|----------------------------|----------------------------|-----------------------------------------|

| I/O Standard | V <sub>DDI</sub><br>Min (V) | V <sub>DDI</sub><br>Typ (V) | V <sub>DDI</sub><br>Max (V) | V <sub>IL</sub><br>Min (V) | V <sub>IL</sub><br>Max (V) | V <sub>IH</sub><br>Min (V) | V <sub>IH</sub> <sup>1</sup><br>Max (V) |

| HSUL12I      | 1.14                        | 1.2                         | 1.26                        | -0.3                       | V <sub>REF</sub> – 0.1     | V <sub>REF</sub> + 0.1     | 1.26                                    |

| POD12I       | 1.14                        | 1.2                         | 1.26                        | -0.3                       | V <sub>REF</sub> – 0.08    | V <sub>REF</sub> + 0.08    | 1.26                                    |

| POD12II      | 1.14                        | 1.2                         | 1.26                        | -0.3                       | V <sub>REF</sub> – 0.08    | V <sub>REF</sub> + 0.08    | 1.26                                    |

- 1. GPIO  $V_{\text{IH}}$  max is 3.45V with PCI clamp diode turned off regardless of mode, that is, over-voltage tolerant.

- 2. For external stub-series resistance. This resistance is on-die for GPIO.

- 3. PolarFire FPGA inputs are designed to support mixing assignment for certain I/O standards, allowing I/O using compatible standards to be placed in the same I/O bank. Refer to the description of the mixed I/O receiver capability in UG0686: PolarFire FPGA User I/O User Guide.

Note: 3.3V and 2.5V are only supported in GPIO banks.

Table 4-16. DC Output Levels

| I/O Standard           | V <sub>DDI</sub><br>Min (V) | V <sub>DDI</sub><br>Typ (V) | V <sub>DDI</sub><br>Max (V) | V <sub>OL</sub><br>Max (V) | V <sub>OH</sub><br>Min (V) | I <sub>OL</sub> <sup>2,6</sup><br>mA | I <sub>OH</sub> <sup>2,6</sup><br>mA     |  |

|------------------------|-----------------------------|-----------------------------|-----------------------------|----------------------------|----------------------------|--------------------------------------|------------------------------------------|--|

| PCI <sup>1</sup>       | 3.15                        | 3.3                         | 3.45                        | 0.1 × V <sub>DDI</sub>     | 0.9 × V <sub>DDI</sub>     | 1.5                                  | 0.5                                      |  |

| LVTTL                  | 3.15                        | 3.3                         | 3.45                        | 0.4                        | 2.4                        | Refer to Note 2                      |                                          |  |

| LVCMOS33               | 3.15                        | 3.3                         | 3.45                        | 0.4                        | V <sub>DDI</sub> – 0.4     |                                      |                                          |  |

| LVCMOS25               | 2.375                       | 2.5                         | 2.625                       | 0.4                        | V <sub>DDI</sub> – 0.4     |                                      |                                          |  |

| LVCMOS18               | 1.71                        | 1.8                         | 1.89                        | 0.45                       | V <sub>DDI</sub> – 0.45    |                                      |                                          |  |

| LVCMOS15               | 1.425                       | 1.5                         | 1.575                       | 0.25 × V <sub>DDI</sub>    | 0.75 × V <sub>DDI</sub>    |                                      |                                          |  |

| LVCMOS12               | 1.14                        | 1.2                         | 1.26                        | 0.25 × V <sub>DDI</sub>    | 0.75 × V <sub>DDI</sub>    |                                      |                                          |  |

| SSTL25I <sup>3</sup>   | 2.375                       | 2.5                         | 2.625                       | V <sub>TT</sub> – 0.608    | V <sub>TT</sub> + 0.608    | 8.1                                  | 8.1                                      |  |

| SSTL25II <sup>3</sup>  | 2.375                       | 2.5                         | 2.625                       | V <sub>TT</sub> – 0.810    | V <sub>TT</sub> + 0.810    | 16.2                                 | 16.2                                     |  |

| SSTL18I <sup>3</sup>   | 1.71                        | 1.8                         | 1.89                        | V <sub>TT</sub> – 0.603    | V <sub>TT</sub> + 0.603    | 6.7                                  | 6.7                                      |  |

| SSTL18II <sup>3</sup>  | 1.71                        | 1.8                         | 1.89                        | V <sub>TT</sub> – 0.603    | V <sub>TT</sub> + 0.603    | 13.4                                 | 13.4                                     |  |

| SSTL15I <sup>4</sup>   | 1.425                       | 1.5                         | 1.575                       | 0.2 × V <sub>DDI</sub>     | 0.8 × V <sub>DDI</sub>     | V <sub>OL</sub> /40                  | (V <sub>DDI</sub> – V <sub>OH</sub> )/40 |  |

| SSTL15II <sup>4</sup>  | 1.425                       | 1.5                         | 1.575                       | 0.2 × V <sub>DDI</sub>     | 0.8 × V <sub>DDI</sub>     | V <sub>OL</sub> /34                  | (V <sub>DDI</sub> – V <sub>OH</sub> )/34 |  |

| SSTL135I <sup>4</sup>  | 1.283                       | 1.35                        | 1.418                       | 0.2 × V <sub>DDI</sub>     | 0.8 × V <sub>DDI</sub>     | V <sub>OL</sub> /40                  | (V <sub>DDI</sub> – V <sub>OH</sub> )/40 |  |

| SSTL135II <sup>4</sup> | 1.283                       | 1.35                        | 1.418                       | 0.2 × V <sub>DDI</sub>     | 0.8 × V <sub>DDI</sub>     | V <sub>OL</sub> /34                  | (V <sub>DDI</sub> – V <sub>OH</sub> )/34 |  |

| HSTL15I                | 1.425                       | 1.5                         | 1.575                       | 0.4                        | V <sub>DDI</sub> – 0.4     | 8                                    | 8                                        |  |

| HSTL15II               | 1.425                       | 1.5                         | 1.575                       | 0.4                        | V <sub>DDI</sub> – 0.4     | 16                                   | 16                                       |  |

| HSTL135I <sup>4</sup>  | 1.283                       | 1.35                        | 1.418                       | 0.2 × V <sub>DDI</sub>     | 0.8 × V <sub>DDI</sub>     | V <sub>OL</sub> /50                  | (V <sub>DDI</sub> – V <sub>OH</sub> )/50 |  |

| HSTL135II <sup>4</sup> | 1.283                       | 1.35                        | 1.418                       | 0.2 × V <sub>DDI</sub>     | 0.8 × V <sub>DDI</sub>     | V <sub>OL</sub> /25                  | (V <sub>DDI</sub> – V <sub>OH</sub> )/25 |  |

| continued              |                  |                  |                  |                        |                        |                                |                                          |  |  |

|------------------------|------------------|------------------|------------------|------------------------|------------------------|--------------------------------|------------------------------------------|--|--|

| I/O Standard           | V <sub>DDI</sub> | V <sub>DDI</sub> | V <sub>DDI</sub> | V <sub>OL</sub>        | V <sub>OH</sub>        | I <sub>OL</sub> <sup>2,6</sup> | I <sub>OH</sub> <sup>2,6</sup>           |  |  |

|                        | Min (V)          | Typ (V)          | Max (V)          | Max (V)                | Min (V)                | mA                             | mA                                       |  |  |

| HSTL12I <sup>4</sup>   | 1.14             | 1.2              | 1.26             | 0.1 × V <sub>DDI</sub> | 0.9 × V <sub>DDI</sub> | V <sub>OL</sub> /50            | (V <sub>DDI</sub> – V <sub>OH</sub> )/50 |  |  |

| HSTL12II <sup>4</sup>  | 1.14             | 1.2              | 1.26             | 0.1 × V <sub>DDI</sub> | 0.9 × V <sub>DDI</sub> | V <sub>OL</sub> /25            | (V <sub>DDI</sub> – V <sub>OH</sub> )/25 |  |  |

| HSUL18I <sup>4</sup>   | 1.71             | 1.8              | 1.89             | 0.1 × V <sub>DDI</sub> | 0.9 × V <sub>DDI</sub> | V <sub>OL</sub> /55            | (V <sub>DDI</sub> – V <sub>OH</sub> )/55 |  |  |

| HSUL18II <sup>4</sup>  | 1.71             | 1.8              | 1.89             | 0.1 × V <sub>DDI</sub> | 0.9 × V <sub>DDI</sub> | V <sub>OL</sub> /25            | (V <sub>DDI</sub> – V <sub>OH</sub> )/25 |  |  |

| HSUL12I <sup>4</sup>   | 1.14             | 1.2              | 1.26             | 0.1 × V <sub>DDI</sub> | 0.9 × V <sub>DDI</sub> | V <sub>OL</sub> /40            | (V <sub>DDI</sub> – V <sub>OH</sub> )/40 |  |  |

| POD12I <sup>4,5</sup>  | 1.14             | 1.2              | 1.26             | 0.5 × V <sub>DDI</sub> | _                      | V <sub>OL</sub> /48            | (V <sub>DDI</sub> – V <sub>OH</sub> )/48 |  |  |

| POD12II <sup>4,5</sup> | 1.14             | 1.2              | 1.26             | 0.5 × V <sub>DDI</sub> | _                      | V <sub>OL</sub> /34            | (V <sub>DDI</sub> – V <sub>OH</sub> )/34 |  |  |

- 1. Drive strengths per PCI specification V/I curves.

- 2. Refer to UG0686: PolarFire FPGA User I/O User Guide for details on supported drive strengths.

- 3. For external stub-series resistance. This resistance is on-die for GPIO.

- 4. I<sub>OL</sub>/I<sub>OH</sub> units for impedance standards in amps (not mA).

- 5. V<sub>OH MAX</sub> based on external pull-up termination (pseudo-open drain).

- 6. The total DC sink/source current of all I/Os within a lane is limited as follows:

- a. HSIO lane: 120 mA per 12 I/O buffers.

- b. GPIO lane: 160 mA per 12 I/O buffers.

Note: 3.3V and 2.5V are only supported in GPIO banks.

#### 4.3.2 Differential DC Input and Output Levels

The follow tables list the differential DC I/O levels.

Table 4-17. Differential DC Input Levels

| I/O Standard         | Bank Type | V <sub>ICM_RANGE</sub> Libero Setting | V <sub>ICM</sub> 1,3 |         |         | V <sub>ID</sub> <sup>2</sup> | V <sub>ID</sub> | V <sub>ID</sub> |

|----------------------|-----------|---------------------------------------|----------------------|---------|---------|------------------------------|-----------------|-----------------|

|                      |           |                                       | Min (V)              | Typ (V) | Max (V) | Min (V)                      | Typ (V)         | Max (V)         |

| LVDS33               | GPIO      | Mid (default)                         | 0.6                  | 1.25    | 2.35    | 0.1                          | 0.35            | 0.6             |

|                      |           | Low                                   | 0.05                 | 0.4     | 0.8     | 0.1                          | 0.35            | 0.6             |

| LVDS25 <sup>7</sup>  | GPIO      | Mid (default)                         | 0.6                  | 1.25    | 2.35    | 0.1                          | 0.35            | 0.6             |

|                      |           | Low                                   | 0.05                 | 0.4     | 0.8     | 0.1                          | 0.35            | 0.6             |

| LVDS18G <sup>4</sup> | GPIO      | Mid (default)                         | 0.6                  | 1.25    | 1.65    | 0.1                          | 0.35            | 0.6             |

|                      |           | Low                                   | 0.05                 | 0.4     | 0.8     | 0.1                          | 0.35            | 0.6             |

| LVDS18 <sup>7</sup>  | HSIO      | Mid (default)                         | 0.6                  | 1.25    | 1.65    | 0.1                          | 0.35            | 0.6             |

|                      |           | Low                                   | 0.05                 | 0.4     | 0.8     | 0.1                          | 0.35            | 0.6             |

| LCMDS33              | GPIO      | Mid (default)                         | 0.6                  | 1.25    | 2.35    | 0.1                          | 0.35            | 0.6             |

|                      |           | Low                                   | 0.05                 | 0.4     | 0.8     | 0.1                          | 0.35            | 0.6             |

| continue                | ed        |                                       |                                            |                                            |                                            |                                         |                            |                            |

|-------------------------|-----------|---------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|-----------------------------------------|----------------------------|----------------------------|

| I/O Standard            | Bank Type | V <sub>ICM_RANGE</sub> Libero Setting | V <sub>ICM</sub> <sup>1,3</sup><br>Min (V) | V <sub>ICM</sub> <sup>1,3</sup><br>Typ (V) | V <sub>ICM</sub> <sup>1,3</sup><br>Max (V) | V <sub>ID</sub> <sup>2</sup><br>Min (V) | V <sub>ID</sub><br>Typ (V) | V <sub>ID</sub><br>Max (V) |

| LCMDS18                 | HSIO      | Mid (default)                         | 0.6                                        | 1.25                                       | 1.65                                       | 0.1                                     | 0.35                       | 0.6                        |

|                         |           | Low                                   | 0.05                                       | 0.4                                        | 0.8                                        | 0.1                                     | 0.35                       | 0.6                        |

| LCMDS25                 | GPIO      | Mid (default)                         | 0.6                                        | 1.25                                       | 2.35                                       | 0.1                                     | 0.35                       | 0.6                        |

|                         |           | Low                                   | 0.05                                       | 0.4                                        | 0.8                                        | 0.1                                     | 0.35                       | 0.6                        |

| RSDS33                  | GPIO      | Mid (default)                         | 0.6                                        | 1.25                                       | 2.35                                       | 0.1                                     | 0.2                        | 0.6                        |

|                         |           | Low                                   | 0.05                                       | 0.4                                        | 0.8                                        | 0.1                                     | 0.2                        | 0.6                        |

| RSDS25                  | GPIO      | Mid (default)                         | 0.6                                        | 1.25                                       | 2.35                                       | 0.1                                     | 0.2                        | 0.6                        |

|                         |           | Low                                   | 0.05                                       | 0.4                                        | 0.8                                        | 0.1                                     | 0.2                        | 0.6                        |

| RSDS18 <sup>5</sup>     | HSIO      | Mid (default)                         | 0.6                                        | 1.25                                       | 1.65                                       | 0.1                                     | 0.2                        | 0.6                        |

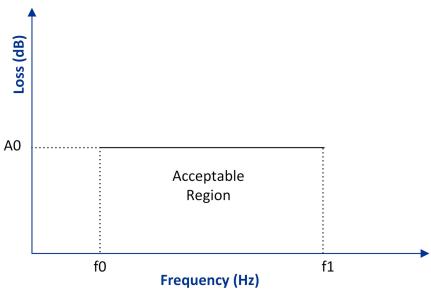

|                         |           | Low                                   | 0.05                                       | 0.4                                        | 0.8                                        | 0.1                                     | 0.2                        | 0.6                        |