# **Contents**

| 1 | Brief D   | escription                                       | 2  |

|---|-----------|--------------------------------------------------|----|

| 2 | Electric  | cal Characteristics                              | 3  |

|   | 2.1. Ab   | solute Maximum Ratings                           | 3  |

|   | 2.2. Op   | erating Conditions                               | 4  |

|   | 2.3. Ele  | ectrical Parameters                              | 5  |

|   | 2.3.1.    | Supply Current and System Operation Conditions   | 5  |

|   | 2.3.2.    | Analog Front-End Characteristics                 | 5  |

|   | 2.3.3.    | Temperature Measurement                          | 5  |

|   | 2.3.4.    | Sensor Diagnostics                               | 6  |

|   | 2.3.5.    | A2D Conversion                                   | 6  |

|   | 2.3.6.    | DAC and Analog Output (AOUT Pin)                 | 6  |

|   | 2.3.7.    | System Response                                  | 7  |

|   |           | erface Characteristics and Nonvolatile Memory    |    |

|   | 2.4.1.    | I <sup>2</sup> C <sup>™</sup> Interface          | 8  |

|   | 2.4.2.    | ZACwire™ One-Wire Interface (OWI at AOUT pin)    | 8  |

|   | 2.4.3.    | Nonvolatile Memory (NVM)                         | 9  |

| 3 | ESD P     | rotection and EMC Specification                  | 10 |

|   | 3.1. ES   | D Protection                                     | 10 |

|   | 3.2. La   | tch-Up Immunity                                  | 10 |

|   | 3.3. Ele  | ectromagnetic Emission                           | 10 |

|   | 3.4. Co   | nducted Susceptibility (DPI)                     | 10 |

| 4 | Reliabi   | lity and RoHS Conformity                         | 11 |

| 5 | Glossa    | ry                                               | 11 |

| 6 | Docum     | ent Revision History                             | 12 |

| L | ist of F  | igures                                           |    |

| F | igure 1.1 | ZSSC4151 Block Diagram                           | 2  |

| L | ist of 1  | - Tables                                         |    |

| T | able 2.1  | Absolute Maximum Ratings                         | 3  |

|   | able 2.2  | Operating Conditions                             |    |

|   | able 2.3  | Electrical Parameters                            |    |

|   | able 2.4  | Interface Characteristics and Nonvolatile Memory |    |

|   | able 3.1  | Conducted Susceptibility (DPI) Tests             |    |

|   |           |                                                  |    |

## 1 Brief Description

The ZSSC4151 sensor signal conditioner (SSC) is a CMOS integrated circuit for highly accurate amplification and sensor-specific correction of bridge sensor signals. Digital compensation of sensor offset, sensitivity, temperature drift, and non-linearity is accomplished via an internal 16-bit RISC microcontroller running a correction algorithm with calibration coefficients stored in an EEPROM.

The ZSSC4151 is adjustable to nearly all bridge sensor types. Measured values are provided at the analog voltage output and at the digital I<sup>2</sup>C<sup>™</sup>\* or ZACwire<sup>™</sup> interface, also referred to as the One-Wire Interface (OWI). The digital interfaces can be used for a simple PC-controlled calibration procedure in order to program a set of calibration coefficients into an on-chip EEPROM. The specific sensor and the ZSSC4151 can be quickly calibrated together. The ZSSC4151 and the calibration equipment communicate digitally, so the noise sensitivity is greatly reduced. Digital calibration helps keep assembly cost low as no trimming by external devices or lasers is needed.

The ZSSC4151 is optimized for automotive environments by overvoltage and reverse-polarity protection circuitry, excellent electromagnetic compatibility, full automotive temperature range, and multiple diagnostic features.

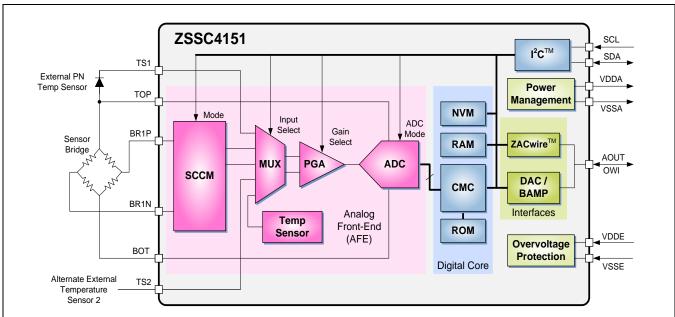

Figure 1.1 provides a block diagram of the ZSSC4151. Refer to section 5 for definitions of abbreviations.

Figure 1.1 ZSSC4151 Block Diagram

<sup>\*</sup> I2C™ is a trademark of NXP.

## 2 Electrical Characteristics

**Important note**: The absolute maximum ratings given in section 2.1 are stress ratings only. The ZSSC4151 might not function or be operable above the recommended operating conditions. Stresses exceeding the absolute maximum ratings might also damage the device. In addition, extended exposure to stresses above the recommended operating conditions might affect device reliability. IDT does not recommend designing to the specifications given under "Absolute Maximum Ratings."

**Important note**: The *operating conditions* given in section 2.2 set the conditions over which IDT specifies device operation. These are the conditions that the application circuit should provide to the device for it to function as intended. Unless otherwise noted, the limits for parameters that appear in the *operating conditions* section are used as test conditions for the limits given in the *electrical characteristics* (section 2.3), *operating conditions*, *and interface characteristics and nonvolatile memory* sections.

## 2.1. Absolute Maximum Ratings

Table 2.1 Absolute Maximum Ratings

|       |                           | •                 |            |      |           |      |

|-------|---------------------------|-------------------|------------|------|-----------|------|

| No.   | Parameter                 | Symbol            | Conditions | Min  | Max       | Unit |

| 2.1.1 | Supply voltage            | VDDE              |            | -40  | 40        | VDC  |

| 2.1.2 | Voltage at AOUT pin       | V <sub>AOUT</sub> |            | -40  | 40        | VDC  |

| 2.1.3 | Analog supply voltage     | VDDA              |            | -0.3 | 6.5       | VDC  |

| 2.1.4 | Digital supply voltage    | VDD               |            | -0.3 | 1.98      | VDC  |

| 2.1.5 | Voltage at all other pins | $V_{PIN}$         |            | -0.3 | VDDA +0.3 | V    |

| 2.1.6 | Storage temperature       | T <sub>STG</sub>  |            | -55  | 160       | °C   |

## 2.2. Operating Conditions

All voltages in this section are relative to VSSA.

## **Table 2.2 Operating Conditions**

Note: See important notes at the end of the table.

| No.   | Parameter                | Symbol                | Conditions                                        | Min          | Typical | Max  | Unit     |

|-------|--------------------------|-----------------------|---------------------------------------------------|--------------|---------|------|----------|

| 2.2.1 | Supply voltage           | VDDE                  | VDDE To VSSE                                      |              | 5       | 5.5  | V        |

|       |                          | VDDA                  | To VSSA VDDE minus drop through protection switch | (VDDE – 0.1) |         | VDDE | <b>V</b> |

| 2.2.2 | Junction temperature     | T <sub>TQE</sub>      | Extended Temperature Range (TQE)                  |              |         | 150  | °C       |

|       |                          | T <sub>AMB_TQA</sub>  | Advanced-Performance<br>Temperature Range (TQA)   | -40          |         | 125  | °C       |

|       |                          | T <sub>AMB_TQI</sub>  | Best-Performance<br>Temperature Range (TQI)       | -25          |         | 85   | °C       |

| 2.2.3 | Bridge resistance 1), 2) | R <sub>BR</sub>       |                                                   | 2            |         | 10   | kΩ       |

|       |                          | R <sub>BR_10-90</sub> | Output range 10-90%                               | 1            |         | 15   | kΩ       |

<sup>1)</sup> No measurement in mass production; parameter is guaranteed by design and/or quality observation.

<sup>2)</sup>  $R_{BR}$  greater than the maximum limit results in higher noise.

### 2.3. Electrical Parameters

All parameter values in this section are valid under the operating conditions specified in section 2.2. All voltages referenced to VSSA.

Note: All parameters measured/validated for  $r_{ADC}$  = 14-bit; segmentation of 1<sup>st</sup> and 2<sup>nd</sup> ADC stage = 8/6;  $f_{OSC}$  = 8MHz; analog gain = ~100;  $T_{AMB\_TQE}$  (see specification 2.2.2).

Table 2.3 Electrical Parameters

Note: See important table notes at the end of the table (page 7).

| No.     | Parameter                                           | Symbol               | Conditions                                                 | Min  | Тур | Max  | Unit                     |  |  |

|---------|-----------------------------------------------------|----------------------|------------------------------------------------------------|------|-----|------|--------------------------|--|--|

| 2.3.1.  | 3.1. Supply Current and System Operation Conditions |                      |                                                            |      |     |      |                          |  |  |

| 2.3.1.1 | Supply current 1)                                   | Is                   | Oscillator adjusted (typical f <sub>OSC</sub> = 8MHz).     |      | 5.5 | 7    | mA                       |  |  |

| 2.3.1.2 | Sensor bridge supply voltage                        | V <sub>SENS</sub>    | $V_{SENS} = V_{TOP} - V_{BOT}$<br>at $R_{BR} \ge 2k\Omega$ | 0.9  |     | 1    | VDDA                     |  |  |

| 2.3.1.3 | Oscillator frequency 2)                             | f <sub>OSC</sub>     |                                                            | 7.2  | 8   | 8.8  | MHz                      |  |  |

| 2.3.1.4 | Oscillator frequency temperature coefficient        | TC <sub>osc</sub>    |                                                            | -200 |     | 200  | ppm/K                    |  |  |

| 2.3.2.  | Analog Front-End Characteri                         | stics                |                                                            |      |     |      |                          |  |  |

| 2.3.2.1 | Input span                                          | V <sub>IN_SPAN</sub> | Analog gain = 1 to 200                                     | 1    |     | 800  | mV/V                     |  |  |

| 2.3.2.2 | Common mode input range                             | V <sub>IN_CM</sub>   | Depends on gain adjustment                                 | 0.25 |     | 0.75 | V <sub>SENS</sub>        |  |  |

| 2.3.2.3 | External capacitance at input                       | C <sub>IN_EXT</sub>  | Capacitance at pins BR1P and BR1N to VSSA                  | 0    |     | 12   | nF                       |  |  |

| 2.3.2.4 | Input leakage current 3)                            | I <sub>IN_leak</sub> |                                                            | -15  |     | 15   | nA                       |  |  |

| 2.3.3.  | Temperature Measurement                             |                      |                                                            |      |     |      |                          |  |  |

| 2.3.3.1 | PTAT internal temperature sensitivity               | ST <sub>TSI</sub>    | Raw values, without conditioning calculation               | 20   |     |      | LSB <sub>14</sub><br>/K  |  |  |

|         |                                                     |                      | Analog gain setting= 6                                     |      |     |      |                          |  |  |

| 2.3.3.2 | External temperature diode channel gain             | A <sub>TSE_D</sub>   |                                                            | 10   |     |      | LSB <sub>14</sub><br>/mV |  |  |

| 2.3.3.3 | External temperature diode bias current             | I <sub>TSE_D</sub>   |                                                            | 10   | 20  | 40   | μА                       |  |  |

| 2.3.3.4 | External temperature diode input range 31           | V <sub>TSE_D</sub>   | Relative to V <sub>TOP</sub>                               | -1   |     | -0.2 | V                        |  |  |

| No.     | Parameter                                         | Symbol                 | Conditions                                                                                    | Min  | Тур | Max  | Unit              |

|---------|---------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------|------|-----|------|-------------------|

| 2.3.3.5 | External RTD channel gain                         | A <sub>TSE_RTD</sub>   |                                                                                               | 10   |     |      | LSB<br>/mV        |

| 2.3.3.6 | External RTD input range 3)                       | V <sub>TSE_RTD</sub>   | Relative to VDDA                                                                              | -2   |     | -0.2 | V                 |

| 2.3.4.  | Sensor Diagnostics                                |                        |                                                                                               |      |     |      |                   |

| 2.3.4.1 | Sensor connection loss threshold                  | R <sub>SCC_open</sub>  |                                                                                               | 100  |     |      | kΩ                |

| 2.3.4.2 | Sensor short threshold to BOT or TOP pin          | R <sub>SCC_SH_BT</sub> |                                                                                               |      |     | 50   | Ω                 |

| 2.3.4.3 | Sensor short threshold between inputs             | R <sub>SCC_SH_IN</sub> |                                                                                               |      |     | 150  | Ω                 |

| 2.3.5.  | A2D Conversion                                    |                        |                                                                                               |      |     |      |                   |

| 2.3.5.1 | ADC resolution 3)                                 | r <sub>ADC</sub>       | Selection: 12, 14, 16 or 18 bit                                                               | 12   |     | 18   | Bit               |

| 2.3.5.2 | DNL <sup>3)</sup>                                 | DNL <sub>ADC</sub>     | Best fit; overall AFE; V <sub>ADC_IN</sub> according to 2.3.6.4.                              |      |     | 0.95 | LSB               |

| 2.3.5.3 | INL TQA temperature range (specified in 2.2.2) 3) | INL <sub>ADC_TQA</sub> | Best fit                                                                                      |      |     | 4    | LSB               |

| 2.3.5.4 | INL TQE temperature range (specified in 2.2.2)    | INL <sub>ADC_TQE</sub> | At 14-bit resolution                                                                          |      |     | 8    | LSB               |

| 2.3.5.5 | ADC input range                                   | V <sub>ADC_IN</sub>    |                                                                                               | 0.1  |     | 0.9  | V <sub>SENS</sub> |

| 2.3.6.  | DAC and Analog Output (AO                         | UT Pin)                |                                                                                               |      |     |      |                   |

| 2.3.6.1 | DAC resolution                                    | r <sub>DAC</sub>       | Analog output                                                                                 |      | 12  |      | Bit               |

| 2.3.6.2 | Output current sink/source                        | I <sub>OUT</sub>       | V <sub>AOUT</sub> : 5-95%, R <sub>LOAD</sub> ≥ 5kΩ                                            |      |     | 2.5  | mA                |

|         |                                                   |                        | $V_{AOUT}$ : 10-90%, $R_{LOAD} \ge 1 k\Omega$                                                 |      |     | 5    | mA                |

| 2.3.6.3 | Short-circuit current (AOUT to VSSE or VDDE)      | I <sub>OUT_max</sub>   | Short to VSSE or VDDE                                                                         | -25  |     | 25   | mA                |

| 2.3.6.4 | Addressable output range                          | $V_{R\_OUT}$           |                                                                                               | 0.01 |     | 0.99 | VDDE              |

| 2.3.6.5 | Load capacitance                                  | C <sub>LOAD</sub>      | Defined for best EMC performance                                                              | 4    | 10  | 150  | nF                |

| 2.3.6.6 | Output slew rate                                  | SR <sub>OUT</sub>      | C <sub>LOAD</sub> < 50nF                                                                      | 0.1  |     |      | V/µs              |

| 2.3.6.7 | Clipping levels                                   | LowLim                 | Configurable 8-bit value stored in NVM                                                        | 0    |     | 25   | %VDDE             |

| 2.3.0.7 | Clipping levels                                   | UppLim                 | Configurable 8-bit value stored in NVM                                                        | 75   |     | 100  | %VDDE             |

| 2.3.6.8 | Clipping adjustment step                          |                        |                                                                                               |      |     | 0.1  | %VDDE             |

| 2.3.6.9 | Output resistance in Diagnostic Mode              | R <sub>OUT_DIA</sub>   | Diagnostic Range:<br>4% to 96%, R <sub>LOAD</sub> ≥ 5kΩ<br>8% to 92%, R <sub>LOAD</sub> ≥ 1kΩ |      |     | 80   | Ω                 |

| No.      | Parameter                                                                  | Symbol                 | Conditions                                                                      | Min   | Тур  | Max  | Unit  |

|----------|----------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------|-------|------|------|-------|

| 2.3.6.10 | DNL                                                                        | DNL <sub>OUT</sub>     | r <sub>DAC</sub> =12 bit                                                        | -1.5  |      | 1.5  | LSB   |

| 2.3.6.11 | INL TQA temperature range (specified in 2.2.2) 3)                          | INL <sub>OUT</sub>     | Best fit, r <sub>DAC</sub> =12-Bit                                              | -5    |      | 5    | LSB   |

| 2.3.6.12 | INL TQE temperature range (specified in 2.2.2)                             | INL <sub>OUT</sub>     | Best fit, r <sub>DAC</sub> =12-Bit                                              | -8    |      | 8    | LSB   |

| 2.3.6.13 | Output leakage current at 125°C                                            | I <sub>LEAK_OUT</sub>  | In the event of power or ground loss                                            | -12   |      | 12   | μA    |

| 2.3.6.14 | Output leakage current at 150°C                                            | I <sub>LEAK_OUT</sub>  | In the event of power or ground loss                                            | -20   |      | 20   | μA    |

| 2.3.7.   | System Response                                                            |                        |                                                                                 |       |      |      |       |

| 2.3.7.1  | Startup time <sup>3), 4)</sup> (time to first valid output after power-on) | t <sub>STARTUP</sub>   | f <sub>OSC</sub> = 8MHz;<br>ADC: 14-bit and 2 <sup>nd</sup> order<br>conversion |       |      | 5    | ms    |

| 2.3.7.2  | Response time 3) 4)5)                                                      | t <sub>RESPONSE</sub>  | 100% input step, excluding transmission time                                    |       |      | 1.1  | ms    |

| 2.3.7.3  | Bandwidth <sup>3)</sup>                                                    |                        | In comparison to analog<br>signal conditioners;<br>66% jump                     |       | 1    |      | kHz   |

| 2.3.7.4  | Analog output noise peak-to-peak 3)                                        | V <sub>NOISE,PP</sub>  | DAC and output buffer only;<br>bandwidth ≤ 10kHz                                |       |      | 10   | mV    |

| 2.3.7.5  | Analog output noise RMS 3)                                                 | V <sub>NOISE,RMS</sub> | DAC and output buffer only;<br>bandwidth ≤ 10kHz                                |       |      | 3    | mV    |

| 2.3.7.6  | Ratiometricity error 3)                                                    | RE <sub>OUT_5</sub>    | Maximum error of VDDE range = 4.5V to 5.5V                                      | -1000 |      | 1000 | ppm   |

| 2.3.7.7  | Overall error <sup>6)</sup>                                                | F <sub>ALL</sub>       | TQA temperature range (specified in 2.2.2)                                      |       | 0.35 | _    | % FSO |

|          |                                                                            | FALL                   | TQE temperature range (specified in 2.2.2)                                      |       | 0.5  |      |       |

<sup>1)</sup> Excluding bridge supply current and excluding output current at AOUT pin.

<sup>2)</sup> Oscillator frequency can be trimmed via a setting in nonvolatile memory (NVM).

<sup>3)</sup> No measurement in mass production; parameter is guaranteed by design and/or quality observation.

<sup>4)</sup> No bridge settling included in timing.

<sup>5)</sup> Dependent on the configuration. The specified limit is valid only for ADC resolutions ≤15 bits.

<sup>6)</sup> FSO: full-scale output. No sensor-caused effects included in overall error. ADC input range from 10% to 90% of V<sub>SENS</sub>; DAC from 5% to 95% of output range.

# 2.4. Interface Characteristics and Nonvolatile Memory

## Table 2.4 Interface Characteristics and Nonvolatile Memory

Note: See important table notes at the end of the table.

| No.      | Parameter                               | Symbol                    | Conditions                                                   | Min   | Тур  | Max   | Unit                   |

|----------|-----------------------------------------|---------------------------|--------------------------------------------------------------|-------|------|-------|------------------------|

| 2.4.1.   | I <sup>2</sup> C <sup>™</sup> Interface |                           |                                                              |       |      |       |                        |

| 2.4.1.1  | I <sup>2</sup> C™ voltage level HIGH 1) | V <sub>I2C_HIGH</sub>     |                                                              | 0.5   |      |       | VDDA                   |

| 2.4.1.2  | I <sup>2</sup> C™ voltage level LOW 1)  | V <sub>I2C_LOW</sub>      |                                                              |       |      | 0.2   | VDDA                   |

| 2.4.1.3  | Slave output level LOW 1)               | V <sub>I2C_LOW_OUT</sub>  | Open drain, I <sub>OL</sub> < 4mA                            |       |      | 0.1   | VDDA                   |

| 2.4.1.4  | SDA load capacitance 1)                 | C <sub>I2C_SDA</sub>      |                                                              |       |      | 400   | pF                     |

| 2.4.1.5  | SCL clock frequency 1)                  | f <sub>I2C</sub>          |                                                              |       |      | 400   | kHz                    |

| 2.4.1.6  | Internal pull-up resistor 1)            | R <sub>I2C_PULLUP</sub>   |                                                              | 25    |      | 100   | kΩ                     |

| 2.4.2.   | ZACwire™ One-Wire Interfa               | ce (OWI at A              | OUT pin)                                                     |       |      |       |                        |

| 2.4.2.1  | OWI voltage level HIGH 1)               | V <sub>OWI_IN_H</sub>     | Master to slave                                              | 0.75  |      |       | VDDE                   |

| 2.4.2.2  | OWI voltage level LOW 1)                | V <sub>OWI_IN_L</sub>     | Master to slave                                              |       |      | 0.2   | VDDE                   |

| 2.4.2.3  | Slave output level LOW 1)               | V <sub>OWI_OUT_L</sub>    | Open drain, I <sub>OL</sub> ≤ 2mA                            |       |      | 0.1   | VDDE                   |

| 2.4.2.4  | Start window 1)                         | t <sub>OWI_STARTWIN</sub> |                                                              | 100   |      | 300   | ms                     |

| 2.4.2.5  | Bus free time                           | t <sub>OWI_IDLE</sub>     | Between stop and next start                                  | 25    |      |       | μs                     |

| 2.4.2.6  | Hold time start condition               | t <sub>OWI_START</sub>    | Valid minimum f <sub>clk</sub>                               | 25    |      |       | μs                     |

| 2.4.2.7  | Bit time                                | t <sub>OWI_BIT</sub>      | Maximum range                                                | 20    |      | 8000  | μs                     |

|          |                                         |                           | Typical operating range                                      | 40    |      | 4000  | μs                     |

| 2.4.2.8  | Duty ratio bit '0'                      | t <sub>OWI_0</sub>        |                                                              | 0.125 | 0.25 | 0.375 | t <sub>OWI_BIT</sub>   |

| 2.4.2.9  | Duty ratio bit '1'                      | t <sub>OWI_1</sub>        |                                                              | 0.625 | 0.75 | 0.875 | t <sub>OWI_BIT</sub>   |

| 2.4.2.10 | Hold time stop condition                | t <sub>OWI_STOP</sub>     | t <sub>OWI_BIT_L</sub> is the bit time of the last valid bit | 2     |      |       | t <sub>OWI_BIT_L</sub> |

| 2.4.2.11 | Bit period deviation                    | t <sub>OWI_BIT_DEV</sub>  |                                                              | 0.55  | 1.0  | 1.5   | t <sub>OWI_BIT</sub>   |

| No.     | Parameter                                              | Symbol               | Conditions                                              | Min | Тур | Max | Unit |

|---------|--------------------------------------------------------|----------------------|---------------------------------------------------------|-----|-----|-----|------|

| 2.4.3.  | Nonvolatile Memory (NVM)                               |                      |                                                         |     |     |     |      |

| 2.4.3.1 | Junction temperature for NVM programming <sup>2)</sup> | T <sub>AMB_NVM</sub> |                                                         | -40 |     | 150 | °C   |

| 2.4.3.2 | Re-write cycles 1)                                     | N <sub>NVM_TQA</sub> | For T <sub>TQA</sub> (see range in specification 2.2.2) | 100 |     |     |      |

| 2.4.3.3 | Re-write cycles at 150°C                               | N <sub>NVM_TQE</sub> | For T <sub>TQE</sub> (see range in specification 2.2.2) | 10  |     |     |      |

| 2.4.3.4 | Data retention 1)                                      | t <sub>NVM_RET</sub> | Temperature profile:<br>22h bake at 250°C               | 15  |     |     | Year |

| 2.4.3.5 | Programming time 1)                                    | t <sub>NVM_WRI</sub> | Per written word                                        |     | 2.2 | 5   | ms   |

<sup>1)</sup> No measurement in mass production; parameter is guaranteed by design and/or quality observation.

<sup>2)</sup> Valid for dice. Note: Additional package and temperature range cause restrictions.

# 3 ESD Protection and EMC Specification

#### 3.1. ESD Protection

All pins have an ESD protection of  $\geq$  2000V according to the Human Body Model (HBM, based on MIL883, Method 3015.7). The VDDE, VSSE, and AOUT pins have an additional ESD protection of  $\geq$  4000V (HBM).

In addition, Charged Device Model (CDM) tests are processed with protection levels of  $\geq$  750V for corner pins and  $\geq$  500V for all other pins.

The level of ESD protection has been tested with devices in QFN24 4X4mm packages during the product qualification.

#### 3.2. Latch-Up Immunity

All pins pass ±100mA latch-up test based on testing that conforms to the standard EIA/JESD 78.

#### 3.3. Electromagnetic Emission

The wired emission of externally connected pins of the device is measured according to the following standard: *IEC* 61967 4:2002 + A1:2006.

Measurements must be performed with the application circuits described in the ZSSC4151 Application Description.

For the off-board pins, the spectral power measured with the  $150\Omega$  method must not exceed the limits according to *IEC 61967\_4k*, *Annex B.4 code H10kN*. For the VSSE pin, the spectral power measured with the  $1\Omega$  method must not exceed the limits according to *IEC 61967\_4k*, *Annex B.4 code 15KmO*.

#### 3.4. Conducted Susceptibility (DPI)

The conducted susceptibility of externally connected pins of the device is measured according to the IEC 62132-4 standard, which describes the direct power injection (DPI) test method.

Measurements must be performed with the application circuit described in the ZSSC4151 Application Description.

Measurements are performed with an internal reference capacitor and internal temperature sensor. The sensing element is replaced by a resistive divider. Calibration is parameterized so that ~50% VDDA is output.

Table 3.1 gives the specifications for the DPI tests. RES refers to the coupling impedance.

Table 3.1 Conducted Susceptibility (DPI) Tests

| Test                | Frequency Range      | Target (dBm) | Load Pins  | Protocol   | Error<br>Band | Comment                                    |

|---------------------|----------------------|--------------|------------|------------|---------------|--------------------------------------------|

| DPI, direct coupled | 1MHz to 300MHz       | 26           | VDDE, AOUT | Analog out | ± 1%          | LOAD RES = $5k\Omega$<br>LOAD CAP = $10nF$ |

| DPI, direct coupled | 300MHz to<br>1000MHz | 32           | VDDE, AOUT | Analog out | ± 1%          | LOAD RES = 5kΩ<br>LOAD CAP = 10nF          |

# 4 Reliability and RoHS Conformity

The ZSSC4151 is qualified according to the AEC-Q100 standard, operating temperature grade 0. The qualification is extended to 3000h for the High Temperature Operating Life (HTOL) Test for one lot. Two manufacturing lots of extended HTOL qualification data (minimum of 3000h test time) for the ZSSC4151 or other products using identical technology (metallization), the same package supplier, the same package style, and the same die size within a specific tolerance are used to prove the package and bond reliability in the range of 3000h HTOL.

A FIT rate  $\leq$  10 FIT (temperature = 55°C, confidence level = 60%) is guaranteed. A typical FIT rate of TSMC's CV018BCD technology, which is used for the ZSSC4151, is 1 FIT.

The ZSSC4151 complies with the RoHS directive and does not contain hazardous substances.

# 5 Glossary

| Term                           | Description                                                         |

|--------------------------------|---------------------------------------------------------------------|

| ADC                            | Analog-to-Digital Converter                                         |

| AEC                            | Automotive Electronics Council                                      |

| AFE                            | Analog Front-End                                                    |

| BAMP                           | Buffer Amplifier                                                    |

| BR                             | Bridge Sensor                                                       |

| CDM                            | Charged Device Model                                                |

| СМ                             | Command Mode                                                        |

| CMC                            | Calibration Microcontroller                                         |

| DAC                            | Digital-to-Analog Converter                                         |

| DNL                            | Differential Nonlinearity                                           |

| DPI                            | Direct Power Injection                                              |

| EMC                            | Electromagnetic Compatibility                                       |

| ESD                            | Electrostatic Discharge                                             |

| FIT                            | Failures in Time                                                    |

| FSO                            | Full Scale Output                                                   |

| НВМ                            | Human Body Model                                                    |

| HTOL                           | High Temperature Operating Life                                     |

| I <sup>2</sup> C <sup>TM</sup> | Inter-Integrated Circuit—serial two-wire data bus, trademark of NXP |

| INL                            | Integral Nonlinearity                                               |

| LSB                            | Least Significant Bit                                               |

| MUX                            | Multiplexer                                                         |

| NVM                            | Nonvolatile Memory                                                  |

| Term                  | Description                                                           |

|-----------------------|-----------------------------------------------------------------------|

| OWI                   | One-Wire Interface                                                    |

| PGA                   | Programmable Gain Amplifier                                           |

| PTAT                  | Proportional-to-Absolute Temperature                                  |

| PTC                   | Thermistor – Positive Temperature Coefficient Resistor                |

| PWR                   | Power Management and Protection Unit                                  |

| QFN                   | Quad-Flat No-Leads – IC package                                       |

| RAM                   | Random Access Memory                                                  |

| RISC                  | Reduced Instruction Set Computing                                     |

| ROM                   | Read-Only Memory                                                      |

| RMS                   | Root-Mean-Square                                                      |

| RTD                   | Resistance Temperature Device                                         |

| SCCM                  | Sensor Check and Common Mode Adjustment Unit                          |

| SCL                   | Serial Clock                                                          |

| SDA                   | Serial Data                                                           |

| SSC                   | Sensor Short Check (diagnostic feature) or Sensor Signal Conditioner  |

| TQA, TQE, TQI         | Temperature range identifier. See specification 2.2.2 for definition. |

| ZACwire <sup>TM</sup> | IDT-specific One-Wire Interface                                       |

# 6 Document Revision History

| Revision | Date               | Description                                                                                                            |

|----------|--------------------|------------------------------------------------------------------------------------------------------------------------|

| 1.00     | September 13, 2015 | First release.                                                                                                         |

| 1.01     | November 10, 2015  | Extended leakage current description in section 2.3.6 for specifications 2.3.6.13 and 2.3.6.14                         |

|          |                    | Updates for table notes for Table 2.3.                                                                                 |

|          |                    | Revision of pin names BRP to BR1P and BRN to BR1N.                                                                     |

| 1.02     | April 12, 2016     | Added minimum value for ratiometricity error in Table 2.3.                                                             |

|          |                    | Updated section 4 regarding completion of AEC-Q100 qualification and extension of the minimum test time to 3000h.      |

|          |                    | Updated specification 2.3.7.7 for improved accuracy of ±0.35% of FSO at -40°C to 125°C and 0.5% FSO at -40°C to 150°C. |

|          | April 20, 2016     | Changed to IDT branding.                                                                                               |

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

# Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

## Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/