# ***LKS32AT089XL Datasheet***

© 2020, 版权归凌鸥创芯所有

机密文件，未经许可不得扩散

## 1 概述

### 1.1 功能简述

LKS32AT089XLN8Q9 是集成 32 位 Cortex-M0 内核的车规级 MCU，同时集成了三相全桥自举式栅极驱动模块，可直接驱动 6 个 N 型 MOSFET。

#### 性能

- 96MHz 32 位 Cortex-M0 内核

- 集成自主指令集电机控制专用 DSP

- 超低功耗休眠模式，MCU 低功耗休眠电流 10uA

- 三相全桥自举式栅极驱动模块

- 汽车级工作温度范围

- 超强抗静电和群脉冲能力

- 通过 AEC-Q100 检测认证

#### ● 存储器

- 64kB Flash，带加密功能

- 8kB RAM

#### ● 工作范围

- LKS32AT089XLN8Q9 双电源供电，MCU 部分采用 2.2V~5.5V 电源供电(B 版本芯片 3.0V~5.5V 电源供电)，内部集成 1 个 LDO，为数字部分电路供电，驱动模块电源供电请参考栅极驱动模块电气参数

- 当芯片使用 7~20V VCC 供电时，内部 LDO 可产生 5V 电源给 MCU 供电，或供电至片外

- 工作温度: -40~125°C

#### ● 时钟

- 内置 4MHz 高精度 RC 时钟，-40~105°C 范围内精度在±1%之内，-40~125°C 范围内精度在±1.5%之内

- 内置低速 32KHz 低速时钟，供低功耗模式使用

- 可外挂 4MHz 外部晶振

- 内部 PLL 可提供最高 96MHz 时钟

#### ● 外设模块

- 两路 UART

- 一路 SPI，支持主从模式

- 一路 IIC，支持主从模式

- 一路 CAN，建议使用外部晶振作为参考时钟

- 一路 LIN

- 2 个通用 16 位 Timer，支持捕捉和边沿对齐 PWM 功能

- 2 个通用 32 位 Timer，支持捕捉和边沿对齐 PWM 功能；支持正交编码输入，CW/CCW 输入，脉冲+符号输入

- 电机控制专用 PWM 模块，支持 8 路 PWM 输出，独立死区控制

- Hall 信号专用接口，支持测速、去抖功能

- 硬件看门狗

- 最多 4 组 16bit GPIO。P0.0/P0.1/P1.0/P1.1 4 个 GPIO 可以作为系统的唤醒源。P0.15 ~ P0.0 共 16 个 GPIO 可以用作外部中断源输入。

## ● 模拟模块

- 集成 1 路 12bit SAR ADC，同步双采样，3Msps 采样及转换速率，最多支持 13 通道

- 集成 4 路运算放大器，可设置为差分 PGA 模式

- 集成两路比较器，可设置滞回模式

- 集成 12bit DAC 数模转换器

- 内置 $\pm 2^{\circ}\text{C}$ 温度传感器

- 内置 1.2V 0.8%精度电压基准源

- 内置 1 路低功耗 LDO 和电源监测电路

- 集成高精度、低温飘高频 RC 时钟

- 集成晶体起振电路

## 1.2 性能优势

- 高可靠性、高集成度、最终产品体积小、节约 BOM 成本；

- 内部集成 4 路高速运放和两路比较器，可满足单电阻/双电阻/三电阻电流采样拓扑架构的不同需求；

- 内部高速运放集成高压保护电路，可以允许高电压共模信号直接输入芯片，可以用最简单的电路拓扑实现 MOSFET 电阻直接电流采样模式；

- 应用专利技术使 ADC 和高速运放达到最佳配合，可处理更宽的电流动态范围，同时兼顾高速小电流和低速大电流的采样精度；

- 整体控制电路简洁高效，抗干扰能力强，稳定可靠；

- 集成三相全桥自举式栅极驱动模块；

- 支持 IEC/UL60730 功能安全认证；

适用于有感 BLDC/无感 BLDC/有感 FOC/无感 FOC 及步进电机、永磁同步、异步电机等控制系统。

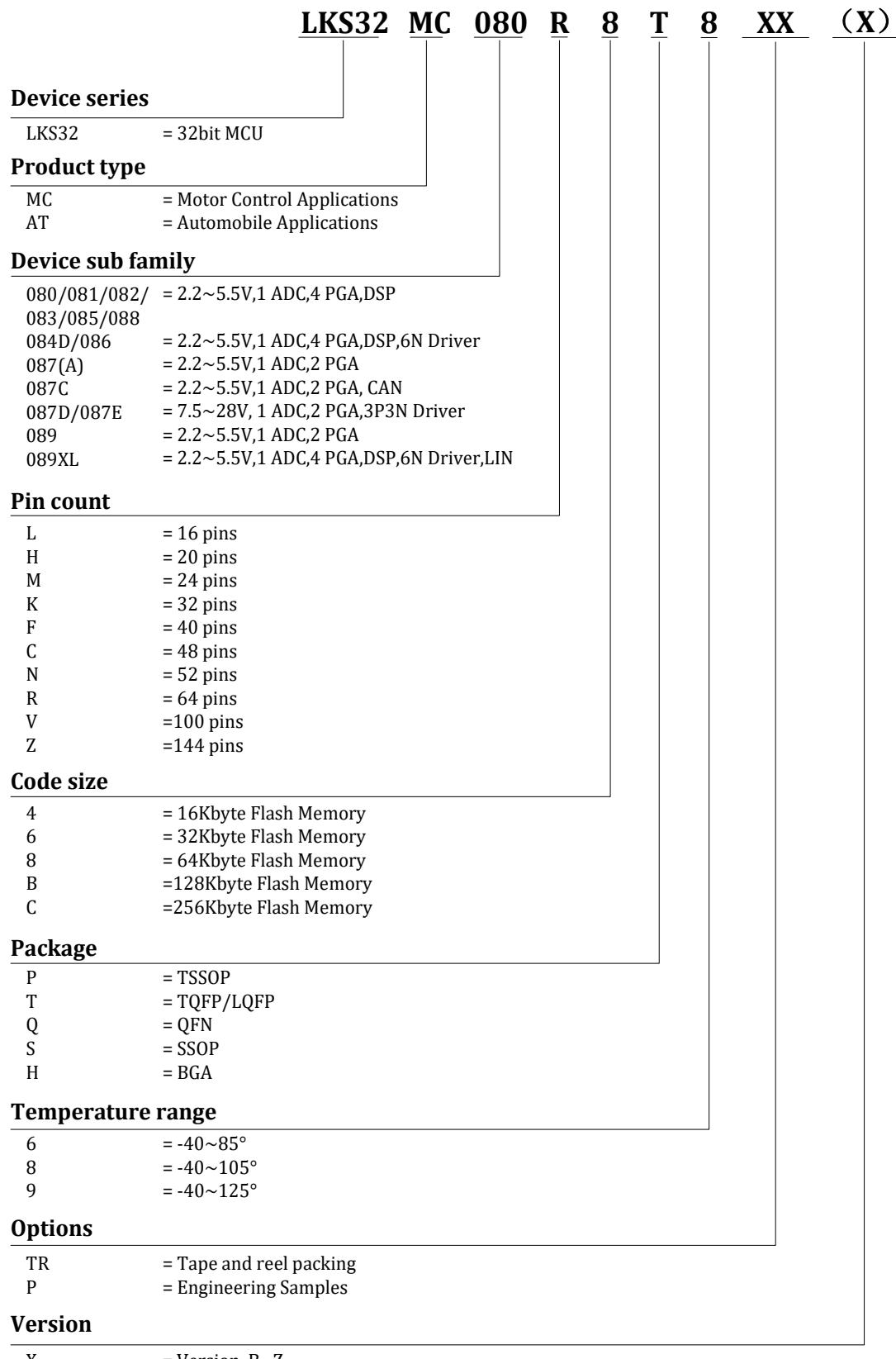

### 1.3 命名规则

图 1-1 凌鸥创芯器件命名规则

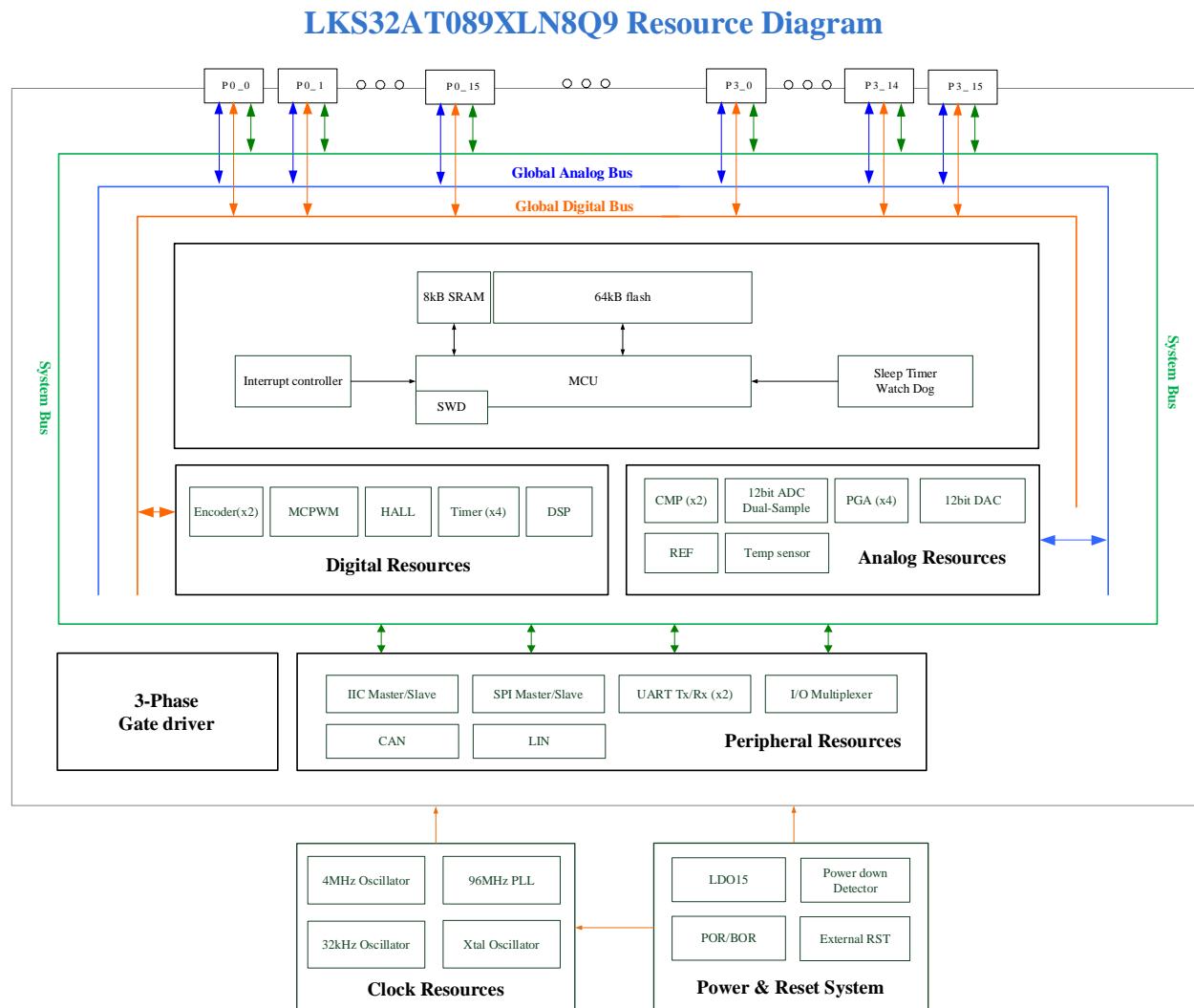

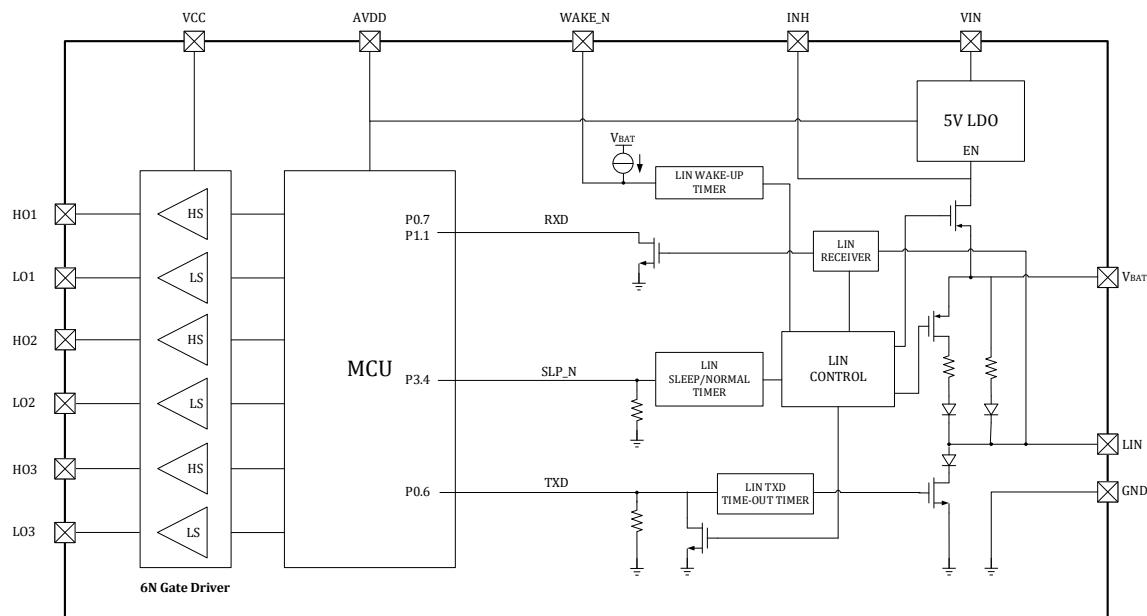

## 1.4 系统资源框图

图 1-2 LKS32AT089XLN8Q9 系统框图

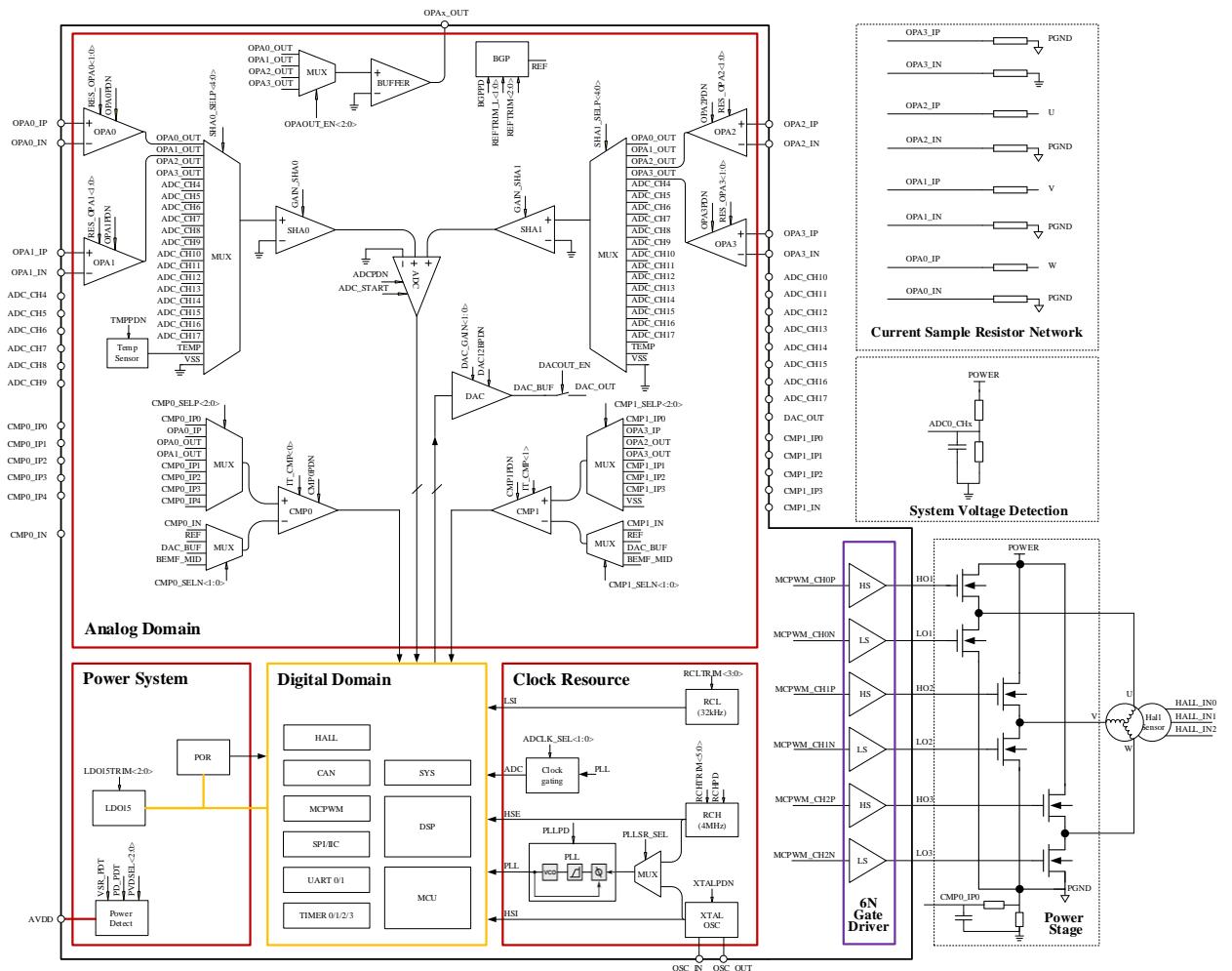

## 1.5 矢量正弦控制系统

图 1-3 LKS32AT089XLN8Q9 矢量正弦控制系统简化原理图

## 2 器件选型表

表 2-1 LKS08x 系列器件选型表

|                    | 主频 (MHz) | Flash (kB) | RAM (kB) | ADC 通道数 | DAC     | 比较器<br>比较器通道数 | OPA | HALL | SPI | IIC | UART | CAN | Temp. Sensor | PLL | QEP | Gate driver | 预驱电流 (A) | 预驱电源(V)    | 栅浮耐压 (V)             | 其他  | Package              |                 |

|--------------------|----------|------------|----------|---------|---------|---------------|-----|------|-----|-----|------|-----|--------------|-----|-----|-------------|----------|------------|----------------------|-----|----------------------|-----------------|

| LKS32MC080R8T8(B)  | 96       | 64         | 8        | 13      | 12BITx1 | 2             | 9   | 4    | 3 路 | 1   | 1    | 2   | Yes          | Yes | Yes | Yes         |          |            |                      |     | LQFP64               |                 |

| LKS32MC081C8T8(B)  | 96       | 64         | 8        | 12      | 12BITx1 | 2             | 9   | 4    | 3 路 | 1   | 1    | 2   |              | Yes | Yes |             |          |            |                      |     | TQFP48               |                 |

| LKS32MC082K8Q8(B)  | 96       | 64         | 8        | 8       | 12BITx1 | 2             | 6   | 3    | 3 路 | 1   | 1    | 2   |              | Yes | Yes |             |          |            |                      |     | QFN5*5 32L-0.75      |                 |

| LKS32MC083C8T8(B)  | 96       | 64         | 8        | 12      | 12BITx1 | 2             | 9   | 4    | 3 路 | 1   | 1    | 2   | Yes          | Yes | Yes | Yes         |          |            |                      |     | TQFP48               |                 |

| LKS32MC084DF6Q8    | 96       | 32         | 8        | 11      | 12BITx1 | 2             | 7   | 4    | 3 路 | 1   | 1    | 2   |              | Yes | Yes |             | 6N       | +1.2/-1.5  | 4.5~20 <sup>*1</sup> | 200 |                      | QFN5*5 40L-0.75 |

| LKS32AT085C8Q9     | 96       | 64         | 8        | 12      | 12BITx1 | 2             | 9   | 4    | 3 路 | 1   | 1    | 2   | Yes          | Yes | Yes | Yes         |          |            |                      |     |                      | QFN6*6 48L-0.55 |

| LKS32AT086N8Q9     | 96       | 64         | 8        | 11      | 12BITx1 | 2             | 9   | 4    | 3 路 | 1   | 1    | 2   | Yes          | Yes | Yes | Yes         | 6N       | +1.2/-1.5  | 4.5~20               | 200 |                      | QFN6*6 52L-0.55 |

| LKS32MC086N8Q8     | 96       | 64         | 8        | 11      | 12BITx1 | 2             | 9   | 4    | 3 路 | 1   | 1    | 2   | Yes          | Yes | Yes | Yes         | 6N       | +1.2/-1.5  | 4.5~20               | 200 |                      | QFN6*6 52L-0.55 |

| LKS32MC087M6S8(B)  | 96       | 32         | 8        | 5       | 12BITx1 | 2             | 6   | 2    | 3 路 |     |      | 1   |              | Yes | Yes |             |          |            |                      |     |                      | SSOP24L         |

| LKS32MC087AM6S8(B) | 96       | 32         | 8        | 5       | 12BITx1 | 2             | 6   | 2    | 3 路 |     |      | 1   |              | Yes | Yes |             |          |            |                      |     |                      | SSOP24L         |

| LKS32MC087CM8S8(B) | 96       | 64         | 8        | 5       | 12BITx1 | 2             | 6   | 2    | 3 路 |     |      | 1   | Yes          | Yes | Yes |             |          |            |                      |     |                      | SSOP24L         |

| LKS32MC087DM6S8    | 96       | 32         | 8        | 5       | 12BITx1 | 2             | 6   | 2    | 3 路 |     |      | 1   |              | Yes | Yes |             | 3P3N     | +0.05/-0.3 | 7~28                 |     | 5V LDO <sup>*2</sup> | SSOP24L         |

| LKS32MC087EM6S8    | 96       | 32         | 8        | 5       | 12BITx1 | 2             | 7   | 2    | 3 路 |     |      | 1   |              | Yes | Yes |             | 3P3N     | +0.05/-0.3 | 7~28                 |     | 5V LDO               | SSOP24L         |

| LKS32MC088C6T8(B)  | 96       | 32         | 8        | 12      | 12BITx1 | 2             | 9   | 4    | 3 路 | 1   | 1    | 2   |              | Yes | Yes |             |          |            |                      |     |                      | TQFP48          |

| LKS32MC088KU8Q8    | 96       | 64         | 8        | 8       | 12BITx1 | 2             | 7   | 3    | 3 路 | 1   | 1    | 2   | Yes          | Yes | Yes | Yes         | 6N       | +0.45/-1   | 4.5~20               | 600 | 5V LDO               | QFN43L          |

| LKS32AT089XLN8Q9   | 96       | 64         | 8        | 11      | 12BITx1 | 2             | 9   | 4    | 3 路 | 1   | 1    | 2   | Yes          | Yes | Yes | Yes         | 6N       | +1.2/-1.5  | 4.5~20               | 200 | 5V LDO               | QFN6*6 52L-0.55 |

\*1：部分型号由于集成多种预驱，分为多种版本，预驱供电电压范围不同，具体参考电气性能参数。

\*2：部分型号集成 5V LDO，当芯片使用 5.5~18V VBAT 供电时，内部 LDO 可产生 5V 电源给 MCU 供电，或供电至片外，具体以管脚说明为准。

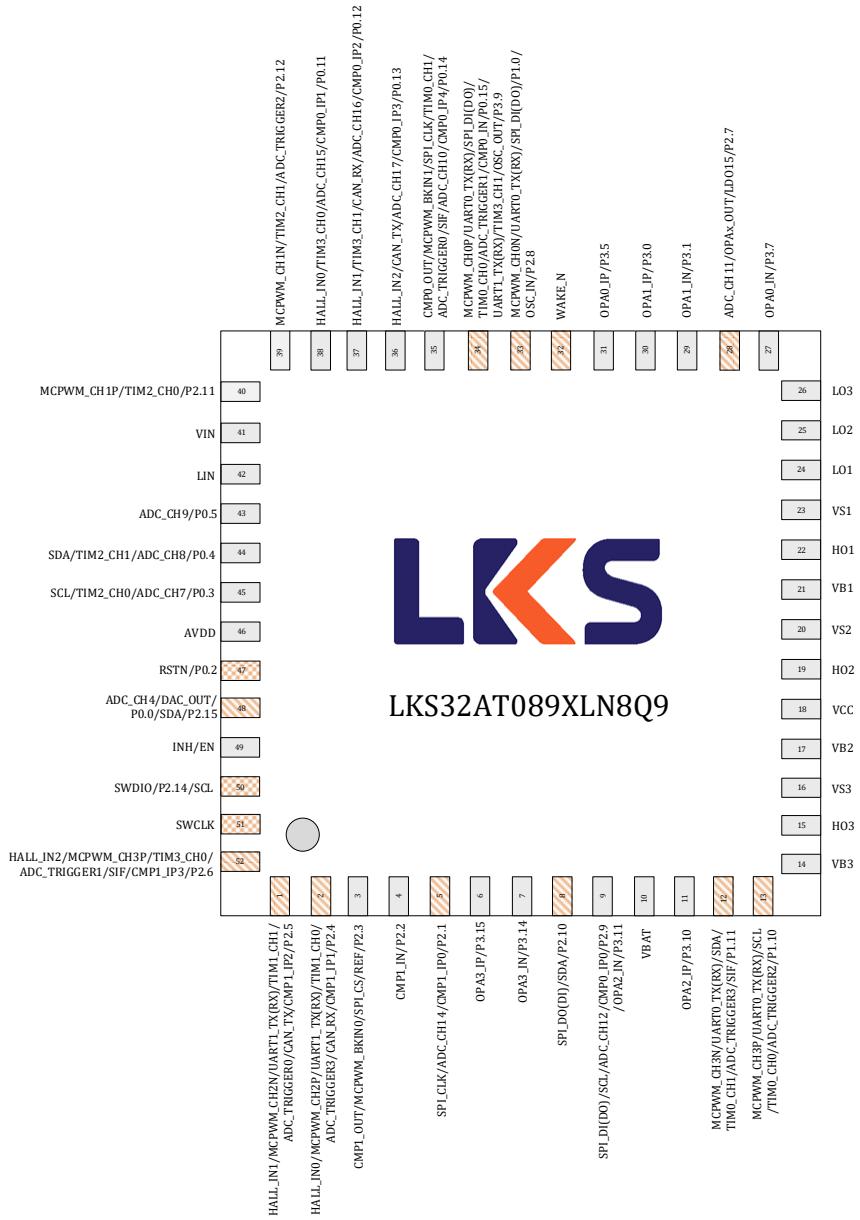

### 3 管脚分布

#### 3.1 管脚分布图及管脚说明

##### 3.1.1 特别说明

下列引脚图中红色 PIN 脚内置上拉至 AVDD 的电阻：

RSTN 引脚内置  $100\text{k}\Omega$  上拉电阻，固定开启上拉

SWDIO/SWCLK 内置  $10\text{k}\Omega$  上拉电阻，固定开启上拉

其余红色 PIN 脚内置  $10\text{k}\Omega$  上拉电阻，可软件控制开启关闭上拉

**UARTx\_TX(RX):** UART 的 TX 和 RX 支持互换。当 GPIO 第二功能选择为 UART，且 GPIO\_PIE 即输入使能时，可以作为 UART\_RX 使用；当 GPIO\_POE 使能时，可以作为 UART\_TX 使用。一般同一 GPIO 不同时使能输入和输出，否则输入 PDI 会接收到 PDO 发出的数据。

**SPI\_DI(DO):** SPI 的 DI 和 DO 支持互换，当 GPIO 第二功能选择为 SPI，且 GPIO\_PIE 即输入使能时，可以作为 SPI\_DI 使用；当 GPIO\_POE 即输出使能时，可以作为 SPI\_DO 使用。一般同一 GPIO 不同时使能输入和输出，否则输入 PDI 会接收到 PDO 发出的数据。

### 3.1.2 LKS32AT089XLN8Q9

图 3-1 LKS32AT089XLN8Q9 管脚分布图

表 3-1 LKS32AT089XLN8Q9 管脚说明

| 编号 | 名称                                                                           | 类型    | 功能说明                                                                                                             |

|----|------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------|

| 0  | GND                                                                          | 地     | 系统地                                                                                                              |

| 1  | HALL_IN1/MCPWM_CH2N/UART1_TX(RX)/TIM1_CH1/ADC_TRIGGER0 /CMP1_IP2/CAN_TX/P2.5 | 输入/输出 | Hall 传感器 B 相输入/电机 PWM 通道 2 低边 /UART1_TX(RX)/Timer1 通道 1/ADC 触发信号 0/比较器 1 同相端输入通道 2/CAN 发送/P2.5，内置可软件开启的 10k 上拉电阻 |

| 2  | HALL_IN0/MCPWM_CH2P/UART1_TX(RX)/TIM1_CH0/                                   | 输入/输出 | Hall 传感器 A 相输入/电机 PWM 通道 2 高边                                                                                    |

| 编号 | 名称                                                            | 类型    | 功能说明                                                                                                                                |

|----|---------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------|

|    | ADC_TRIG3/ CMP1_IP1/CAN_RX/P2.4                               |       | /UART1_TX(RX)/Timer1 通道 0/ADC 触发信号 3/比较器 1 同相端输入通道 1/CAN 接收/P2.4, 内置可软件开启的 10k 上拉电阻                                                 |

| 3  | CMP1_OUT/MCPWM_BKIN0/SPI_CS/REF/P2.3                          | 输入/输出 | 比较器 1 输出/电机 PWM 终止信号 0/SPI 片选信号/电压参考信号/P2.3                                                                                         |

| 4  | CMP1_IN/P2.2                                                  | 输入/输出 | 比较器 1 反相端输入/P2.2                                                                                                                    |

| 5  | SPI_CLK/ADC_CH14/CMP1_IP0/P2.1                                | 输入/输出 | SPI 时钟/ADC 通道 14/比较器 1 同相端输入通道 0/P2.1, 内置可软件开启的 10k 上拉电阻                                                                            |

| 6  | OPA3_IP/P3.15                                                 | 输入/输出 | 运放 3 同相端输入/P3.15                                                                                                                    |

| 7  | OPA3_IN/P3.14                                                 | 输入/输出 | 运放 3 反相端输入/P3.14                                                                                                                    |

| 8  | SPI_DO(DI)/SDA/P2.10                                          | 输入/输出 | SPI_DO(DI)/IIC 数据/P2.10, 内置可软件开启的 10k 上拉电阻                                                                                          |

| 9  | SPI_DI(DO)/SCL/ADC_CH12/CMP0_IP0/P2.9/OPA2_IN/P3.11           | 输入/输出 | SPI_DI(DO)/IIC 时钟/ADC 通道 12/比较器 0 同相端输入通道 0/P2.9/运放 2 反相端输入/P3.11                                                                   |

| 10 | VBAT                                                          | 电源    | LIN 收发器电源电压(VBAT)                                                                                                                   |

| 11 | OPA2_IP/P3.10                                                 | 输入/输出 | 运放 2 同相端输入/P3.10                                                                                                                    |

| 12 | MCPWM_CH3N/UART0_TX(RX)/SDA/TIM0_CH1/ADC_TRIG3/SIF/P1.11      | 输入/输出 | 电机 PWM 通道 3 低边/UART0_TX(RX)/IIC 数据/Timer0 通道 1/ADC 触发信号 3/SIF 接口/P1.11, 内置可软件开启的 10k 上拉电阻                                           |

| 13 | ADC_CH13/MCPWM_CH3P/UART0_TX(RX)/SCL/TIM0_CH0/ADC_TRIG2/P1.10 | 输入/输出 | 电机 PWM 通道 3 高边/UART0_TX(RX)/IIC 时钟/Timer0 通道 0/ADC 触发信号 2/P1.10, 内置可软件开启的 10k 上拉电阻                                                  |

| 14 | VB3                                                           | 输入/输出 | 高侧浮动输入电源电压 3                                                                                                                        |

| 15 | HO3                                                           | 输出    | 高侧栅极驱动信号输出 3, 由 MCU P1.8 口输出信号控制, HO3 输出与 P1.8 信号为同相关系, 即输入为'1'时, HO3 输出'1'                                                         |

| 16 | VS3                                                           | 输入/输出 | 高侧浮动偏置电压 3                                                                                                                          |

| 17 | VB2                                                           | 输入/输出 | 高侧浮动输入电源电压 2                                                                                                                        |

| 18 | VCC                                                           | 电源    | 全桥驱动模块供电电源                                                                                                                          |

| 19 | HO2                                                           | 输出    | 高侧栅极驱动信号输出 2, 由 MCU P1.6 口输出信号控制, HO2 输出与 P1.6 信号为同相关系, 即输入为'1'时, HO2 输出'1'                                                         |

| 20 | VS2                                                           | 输入/输出 | 高侧浮动偏置电压 2                                                                                                                          |

| 21 | VB1                                                           | 输入/输出 | 高侧浮动输入电源电压 1                                                                                                                        |

| 22 | HO1                                                           | 输出    | 高侧栅极驱动信号输出 1, 由 MCU P1.4 口输出信号控制, HO1 输出与 P1.4 信号为同相关系, 即输入为'1'时, HO1 输出'1'                                                         |

| 23 | VS1                                                           | 输入/输出 | 高侧浮动偏置电压 1                                                                                                                          |

| 24 | LO1                                                           | 输出    | 低侧栅极驱动信号输出 1, 由 MCU P1.5 口的 PWM 输出功能控制, 即需配置 GPIO1_F7654[7:4], 同时 P3.13 需设置为输出态, 即需配置 GPIO3_POE[13]。LO1 输出与 P1.5 信号为同相关系, 即输入为'0'时, |

| 编号 | 名称                                                                                   | 类型    | 功能说明                                                                                                                                        |

|----|--------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                                                                      |       | LO1 输出'0'                                                                                                                                   |

| 25 | LO2                                                                                  | 输出    | 低侧栅极驱动信号输出 2，由 MCU P1.7 口的 PWM 输出功能控制，即需配置 GPIO1_F7654[15:12]，同时 P1.12 需设置为输出态，即需配置 GPIO1_POE[12]。 LO2 输出与 P1.7 信号为同相关系，即输入为'0'时， LO2 输出'0' |

| 26 | LO3                                                                                  | 输出    | 低侧栅极驱动信号输出 3，由 MCU P1.9 口的 PWM 输出功能控制，即需配置 GPIO_FBA98[3:0]，同时 P1.15 需设置为输出态，即需配置 GPIO1_POE[15]。 LO3 输出与 P1.9 信号为同相关系，即输入为'0'时， LO3 输出'0'    |

| 27 | OPA0_IN/P3.7                                                                         | 输入/输出 | 运放 0 反相端输入/P3.7                                                                                                                             |

| 28 | ADC_CH11/OPAx_OUT/LDO15/P2.7                                                         | 输入/输出 | ADC 通道 11/OPAx 输出/LDO15 输出/P2.7，内置可软件开启的 10k 上拉电阻                                                                                           |

| 29 | OPA1_IN/P3.1                                                                         | 输入/输出 | 运放 1 反相端输入/P3.1                                                                                                                             |

| 30 | OPA1_IP/P3.0                                                                         | 输入/输出 | 运放 1 同相端输入/P3.0                                                                                                                             |

| 31 | OPA0_IP/P3.5                                                                         | 输入/输出 | 运放 0 同相端输入/P3.5                                                                                                                             |

| 32 | WAKE_N                                                                               | 输入    | 本地唤醒输入端口（低电平有效），下降沿触发该唤醒事件，内置上拉电阻，低电平持续时间超过 50us 可以进行 LIN PHY 唤醒，唤醒后内部 5V LDO 通过 AVDD 给 MCU 进行供电                                            |

| 33 | MCPWM_CH0N/UART0_TX(RX)/SPI_DI(DO)/P1.0/<br>OSC_IN/P2.8                              | 输入/输出 | 电机 PWM 通道 0 低边/UART0_TX(RX)/SPI_DI(DO)/P1.0，内置可软件开启的 10k 上拉电阻/晶体输入引脚/P2.8。如接晶体，该引脚接一个 15pf 电容到地。                                            |

| 34 | MCPWM_CH0P/UART0_TX(RX)/SPI_DI(DO)/TIM0_CH0<br>/ADC_TRIG1/CMP0_IN/P0.15/OSC_OUT/P3.9 | 输入/输出 | 电机 PWM 通道 0 高边/UART0_TX(RX)/SPI_DI(DO)/Timer0 通道 0/ADC 触发信号 1/比较器 0 反相端输入/P0.15/晶体输出引脚/P3.9。如接晶体，该引脚接一个 15pf 电容到地。                          |

| 35 | CMP0_OUT/MCPWM_BKIN1/SPI_CLK/TIM0_CH1/<br>ADC_TRIG0/SIF/ADC_CH10/CMP0_IP4/P0.14      | 输入/输出 | 比较器 0 输出/电机 PWM 终止信号 1/SPI 时钟/Timer0 通道 1/ADC 触发信号 0/SIF 接口/ADC 通道 10/比较器 0 同相端输入通道 4/P0.14                                                 |

| 36 | HALL_IN2/ADC_CH17/CMP0_IP3/CAN_TX/P0.13                                              | 输入/输出 | Hall 传感器 C 相输入/ADC 通道 17/比较器 0 同相端输入通道 3/CAN 发送/P0.13                                                                                       |

| 37 | HALL_IN1/TIM3_CH1/<br>ADC_CH16/CMP0_IP2/CAN_RX/P0.12                                 | 输入/输出 | Hall 传感器 B 相输入/Timer3 通道 1/ADC 通道 16/比较器 0 同相端输入通道 2/CAN 接收/P0.12                                                                           |

| 38 | HALL_IN0/TIM3_CH0/ADC_CH15/CMP0_IP1/P0.11                                            | 输入/输出 | Hall 传感器 A 相输入/Timer3 通道 0/ADC 通道 15/比较器 0 同相端输入通道 1/P0.11                                                                                  |

| 39 | MCPWM_CH1N/TIM2_CH1/ADC_TRIG2/P2.12                                                  | 输入/输出 | 电机 PWM 通道 1 低边/Timer2 通道 1/ADC 触发信号 2/P2.12                                                                                                 |

| 40 | MCPWM_CH1P/TIM2_CH0/P2.11                                                            | 输入/输出 | 电机 PWM 通道 1 高边/Timer2 通道 0/P2.11                                                                                                            |

| 41 | VIN                                                                                  | 输入    | 5V LDO 输入引脚，输入电源范围 2.7~40V                                                                                                                  |

| 42 | LIN                                                                                  | 输入/输出 | LIN 总线输入、输出端口                                                                                                                               |

| 43 | ADC_CH9/P0.5                                                                         | 输入/输出 | ADC 通道 9/P0.5                                                                                                                               |

| 编号 | 名称                                                       | 类型    | 功能说明                                                                                                                                              |

|----|----------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 44 | SDA/TIM2_CH1/ADC_CH8/P0.4                                | 输入/输出 | IIC 数据/Timer2 通道 1/ADC 通道 8/P0.4                                                                                                                  |

| 45 | SCL/TIM2_CH0/ADC_CH7/P0.3                                | 输入/输出 | IIC 时钟/Timer2 通道 0/ADC 通道 7/P0.3                                                                                                                  |

| 46 | AVDD                                                     | 电源    | LDO 输出可产生 5V 电源给 MCU 供电，或供电至片外/芯片电源输入，最大输出电流能力 100mA。片外去耦电容建议 $\geq 1\mu F$ ，并尽量靠近 AVDD 引脚                                                        |

| 47 | RSTN/P0.2                                                | 输入/输出 | RSTN/P0.2， 默认作为 RSTN 使用， 外部接一个 10nF~100nF 的电容到地即可， 内部已有 100k 上拉电阻。建议 PCB 上在 RSTN 和 AVDD 之间放一个 10k~20k 的上拉电阻，外部有上拉电阻的情况，RSTN 的电容固定为 100nF          |

| 48 | ADC_CH4/DAC_OUT/P0.0/SDA/P2.15                           | 输入/输出 | ADC 通道 4/DAC 输出/P0.0， 内置可软件开启的 10k 上拉电阻/IIC 数据/P2.15                                                                                              |

| 49 | INH/EN                                                   | 输出    | 用于控制外部电源的工作状态，发生唤醒事件后置为高电平/LDO 使能引脚<br>LIN PHY 被远程唤醒或本地唤醒后，INH 输出高电平，休眠时输出浮空，可通过外界上拉或下拉电阻控制 5V LDO 使能 EN。若外接上拉，则 5v LDO 始终保持供电，若下拉则在休眠时停止给 MCU 供电 |

| 50 | SWDIO/SCL/P2.14                                          | 输入/输出 | SWD 数据/ IIC 时钟/P2.14， 内置固定上拉的 10k 电阻                                                                                                              |

| 51 | SWCLK                                                    | 输入    | SWD 时钟， 内置固定上拉的 10k 电阻                                                                                                                            |

| 52 | HALL_IN2/MCPWM_CH3P/TIM3_CH0/ADC_TRIG1/SIF/CMP1_IP3/P2.6 | 输入/输出 | Hall 传感器 C 相输入/电机 PWM 通道 3 高边 /Timer3 通道 0/ADC 触发信号 1/SIF 接口/比较器 1 同相端输入通道 3/P2.6， 内置可软件开启的 10k 上拉电阻                                              |

### 3.2 管脚复用功能说明

表 3-2 LKS32AT089XLN8Q9 引脚功能选择

| Port  | AF1      | AF2      | AF3         | AF4          | AF5        | AF6 | AF7      | AF8      | AF9       | AF10 | AF11 | AFE               |

|-------|----------|----------|-------------|--------------|------------|-----|----------|----------|-----------|------|------|-------------------|

| P0.0  |          |          |             |              |            |     |          |          |           |      |      | ADC_CH4, DAC_OUT  |

| P0.1  |          |          |             |              |            |     |          |          |           |      |      | ADC_CH6           |

| P0.2  |          |          |             |              |            |     |          |          |           |      |      |                   |

| P0.3  |          |          |             |              |            | SCL |          | TIM2_CH0 |           |      |      | ADC_CH7           |

| P0.4  |          |          |             |              |            | SDA |          | TIM2_CH1 |           |      |      | ADC_CH8           |

| P0.5  |          |          |             |              |            |     |          |          |           |      |      | ADC_CH9           |

| P0.6  |          |          |             | UART1_TX(RX) |            |     | TIM1_CH0 |          |           |      |      |                   |

| P0.7  |          |          |             | UART1_TX(RX) |            |     | TIM1_CH1 |          |           |      |      |                   |

| P0.8  |          |          |             |              |            |     |          |          |           |      |      |                   |

| P0.9  |          |          |             |              |            | SCL |          | TIM2_CH0 |           |      |      |                   |

| P0.10 |          |          |             |              |            | SDA |          | TIM2_CH1 |           |      |      |                   |

| P0.11 |          | HALL_IN0 |             |              |            |     |          | TIM3_CH0 |           |      |      | ADC_CH15/CMP0_IP1 |

| P0.12 |          | HALL_IN1 |             |              |            |     |          | TIM3_CH1 |           |      |      | ADC_CH16/CMP0_IP2 |

| P0.13 |          | HALL_IN2 |             |              |            |     |          |          |           |      |      | ADC_CH17/CMP0_IP3 |

| P0.14 | CMP0_OUT |          | MCPWM_BKIN1 |              | SPI_CLK    |     | TIM0_CH1 |          | ADC_TRIGO |      | SIF  | ADC_CH10/CMP0_IP4 |

| P0.15 |          |          | MCPWM_CH0P  | UART0_TX(RX) | SPI_DI(DO) |     | TIM0_CH0 |          | ADC_TRIG1 |      |      | CMP0_IN           |

| Port  | AF1 | AF2 | AF3        | AF4          | AF5        | AF6 | AF7      | AF8      | AF9       | AF10 | AF11 | AFE      |

|-------|-----|-----|------------|--------------|------------|-----|----------|----------|-----------|------|------|----------|

| P1.0  |     |     | MCPWM_CH0N | UART0_TX(RX) | SPI_DI(DO) |     |          |          |           |      |      |          |

| P1.1  |     |     |            |              | SPI_CS     |     |          |          |           |      |      |          |

| P1.2  |     |     |            |              |            |     |          | TIM3_CH0 |           |      |      |          |

| P1.3  |     |     |            |              |            |     |          | TIM3_CH1 |           |      |      | ADC_CH5  |

| P1.4  | LRC |     | MCPWM_CH0P |              |            |     |          |          |           |      |      |          |

| P1.5  | HRC |     | MCPWM_CH0N |              |            |     |          |          |           |      |      |          |

| P1.6  |     |     | MCPWM_CH1P |              |            |     |          |          |           |      |      |          |

| P1.7  |     |     | MCPWM_CH1N |              |            |     |          |          |           |      |      |          |

| P1.8  |     |     | MCPWM_CH2P |              |            |     |          |          |           |      |      |          |

| P1.9  |     |     | MCPWM_CH2N |              |            |     |          |          |           |      |      |          |

| P1.10 |     |     | MCPWM_CH3P | UART0_TX(RX) |            | SCL | TIM0_CH0 |          | ADC_TRIG2 |      |      | ADC_CH13 |

| P1.11 |     |     | MCPWM_CH3N | UART0_TX(RX) |            | SDA | TIM0_CH1 |          | ADC_TRIG3 |      | SIF  |          |

| P1.12 |     |     | MCPWM_CH1N |              |            |     |          |          |           |      |      |          |

| P1.13 |     |     |            |              | SPI_CLK    |     | TIM0_CH0 |          |           |      |      |          |

| P1.14 |     |     |            |              | SPI_DI(DO) |     | TIM0_CH1 |          |           |      |      |          |

| P1.15 |     |     | MCPWM_CH2N |              |            |     |          |          |           |      |      |          |

| Port  | AF1      | AF2      | AF3         | AF4          | AF5        | AF6 | AF7      | AF8      | AF9       | AF10 | AF11 | AFE                             |

|-------|----------|----------|-------------|--------------|------------|-----|----------|----------|-----------|------|------|---------------------------------|

| P2.0  |          |          |             |              | SPI_CS     |     |          | TIM2_CH1 |           |      |      |                                 |

| P2.1  |          |          |             |              | SPI_CLK    |     |          |          |           |      |      | ADC_CH14/<br>CMP1_IP0           |

| P2.2  |          |          |             |              |            |     |          |          |           |      |      | CMP1_IN                         |

| P2.3  | CMP1_OUT |          | MCPWM_BKIN0 |              | SPI_CS     |     |          |          |           |      |      | REF                             |

| P2.4  |          | HALL_IN0 | MCPWM_CH2P  | UART1_TX(RX) |            |     | TIM1_CH0 |          | ADC_TRIG3 |      |      | CMP1_IP1                        |

| P2.5  |          | HALL_IN1 | MCPWM_CH2N  | UART1_TX(RX) |            |     | TIM1_CH1 |          | ADC_TRIG0 |      |      | CMP1_IP2                        |

| P2.6  |          | HALL_IN2 | MCPWM_CH3P  |              |            |     |          | TIM3_CH0 | ADC_TRIG1 |      | SIF  | CMP1_IP3                        |

| P2.7  |          |          |             |              |            |     |          |          |           |      |      | ADC_CH11/<br>OPAx_OUT/<br>LDO15 |

| P2.8  |          |          |             | UART1_TX(RX) |            |     |          | TIM3_CH0 |           |      |      | OSC_IN                          |

| P2.9  |          |          |             |              | SPI_DI(DO) | SCL |          |          |           |      |      | ADC_CH12/<br>CMP0_IP0           |

| P2.10 |          |          |             |              | SPI_DI(DO) | SDA |          |          |           |      |      |                                 |

| P2.11 |          |          | MCPWM_CH1P  |              |            |     |          | TIM2_CH0 |           |      |      |                                 |

| P2.12 |          |          | MCPWM_CH1N  |              |            |     |          | TIM2_CH1 | ADC_TRIG2 |      |      |                                 |

| P2.13 |          |          | MCPWM_CH3N  |              |            |     |          | TIM3_CH1 |           |      |      |                                 |

| P2.14 |          |          |             |              |            | SCL |          |          |           |      |      |                                 |

| P2.15 |          |          |             |              |            | SDA |          |          |           |      |      |                                 |

| Port  | AF1 | AF2 | AF3        | AF4          | AF5 | AF6 | AF7 | AF8      | AF9 | AF10 | AF11 | AFE     |

|-------|-----|-----|------------|--------------|-----|-----|-----|----------|-----|------|------|---------|

| P3.0  |     |     |            |              |     |     |     |          |     |      |      | OPA1_IP |

| P3.1  |     |     |            |              |     |     |     |          |     |      |      | OPA1_IN |

| P3.2  |     |     |            |              |     |     |     |          |     |      |      |         |

| P3.3  |     |     |            |              |     |     |     |          |     |      |      |         |

| P3.4  |     |     |            |              |     |     |     |          |     |      |      |         |

| P3.5  |     |     |            |              |     |     |     |          |     |      |      | OPA0_IP |

| P3.6  |     |     |            |              |     |     |     |          |     |      |      |         |

| P3.7  |     |     |            |              |     |     |     |          |     |      |      | OPA0_IN |

| P3.8  |     |     |            |              |     |     |     |          |     |      |      |         |

| P3.9  |     |     |            | UART1_TX(RX) |     |     |     | TIM3_CH1 |     |      |      | OSC_OUT |

| P3.10 |     |     |            |              |     |     |     |          |     |      |      | OPA2_IP |

| P3.11 |     |     |            |              |     |     |     |          |     |      |      | OPA2_IN |

| P3.12 |     |     |            |              |     |     |     |          |     |      |      |         |

| P3.13 | HRC |     | MCPWM_CH0N |              |     |     |     |          |     |      |      |         |

| P3.14 |     |     |            |              |     |     |     |          |     |      |      | OPA3_IN |

| P3.15 |     |     |            |              |     |     |     |          |     |      |      | OPA3_IP |

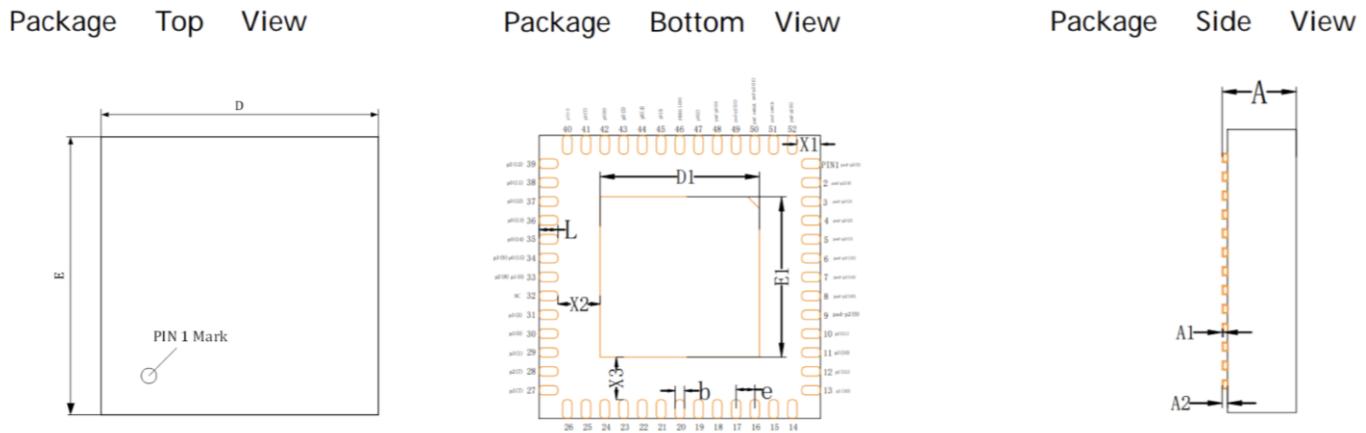

## 4 封装尺寸

### 4.1 LKS32AT089XLN8Q9

QFN6\*6 52L-0.55 Profile Quad Flat Package:

图 4-1 LKS32AT089XLN8Q9 封装图示

表 4-1 LKS32AT089XLN8Q9 封装尺寸

| SYMBOL | MILLIMETER |       |       |

|--------|------------|-------|-------|

|        | MIN        | NOM   | MAX   |

| A      | 0.500      | 0.550 | 0.600 |

| A1     | 0.007      | 0.012 | 0.017 |

| A2     |            | 0.040 |       |

| D      | 5.90       | 6.00  | 6.10  |

| E      | 5.90       | 6.00  | 6.10  |

| D1     | 3.350      | 3.400 | 3.450 |

| E1     | 3.350      | 3.400 | 3.450 |

| L      | 0.350      | 0.400 | 0.450 |

| b      | 0.150      | 0.200 | 0.250 |

| e      | 0.350      | 0.400 | 0.450 |

| X1     | 0.450      | 0.500 | 0.550 |

| X2     | 0.850      | 0.900 | 0.950 |

| X3     | 0.850      | 0.900 | 0.950 |

## 5 电气性能参数

表 5-1 LKS32AT089XLN8Q9 电气极限参数

| 参数                | 最小   | 最大    | 单位 | 说明 |

|-------------------|------|-------|----|----|

| MCU 电源电压(AVDD)    | -0.3 | +6.0  | V  |    |

| 预驱电源电压(VCC)       | -0.3 | +25.0 | V  |    |

| 5v LDO 输入电压(VIN)  | -0.3 | +45   | V  |    |

| LIN 收发器电源电压(VBAT) | -0.3 | +58   | V  |    |

| LIN 引脚电压          | -58  | +58   | V  |    |

| 5v LDO 输出电流       |      | 100   | mA |    |

| 工作温度              | -40  | +125  | °C |    |

| 存储温度              | -40  | +150  | °C |    |

| 结温                | -    | 150   | °C |    |

| 引脚温度(焊接 10 秒)     | -    | 260   | °C |    |

表 5-2 LKS32AT089XLN8Q9 建议工况参数

| 参数                | 最小  | 典型 | 最大  | 单位 | 说明                  |  |

|-------------------|-----|----|-----|----|---------------------|--|

| MCU 电源电压(AVDD)    | 3.0 | 5  | 5.5 | V  | AVDD 复位电平 2.7V±0.2V |  |

| 模拟工作电压(AVDDA)     | 3.3 | 5  | 5.5 | V  | ADC 选择 2.4V 内部基准源   |  |

|                   | 2.8 | 5  | 5.5 | V  | ADC 选择 1.2V 内部基准源   |  |

| 预驱电源电压(VCC)       | 7   |    | 20  | V  | 6N 预驱供电             |  |

| 5v LDO 输入电压(VIN)  | 2.7 |    | 40  | V  |                     |  |

| LIN 收发器电源电压(VBAT) | 5.5 | 12 | 27  | V  |                     |  |

运算放大器可以在 2.2V 下工作，但输出幅度受限。

表 5-3 LKS32AT089XLN8Q9 ESD 性能参数

| 项目          | 管脚                                            | 最小    | 最大   | 单位 |

|-------------|-----------------------------------------------|-------|------|----|

| ESD 测试(HBM) | 预驱管脚(PIN14~26)                                | -2000 | 2000 | V  |

|             | LIN 管脚：VBAT(PIN10), WAKE_N(PIN32), LIN(PIN42) | -4000 | 4000 | V  |

|             | 其他管脚                                          | -6000 | 6000 | V  |

根据《MIL-STD-883J Method 3015.9》，在 25°C, 55% 相对湿度环境下，在被测芯片的所有 IO 引脚施加进行静电放电 3 次，每次间隔 1s。若对 ESD 有更高要求，建议在相关外部引脚放置 TVS 二极管保护。

表 5-4 LKS32AT089XLN8Q9 Latch-up 性能参数

| 项目                 | 最小   | 最大  | 单位 |

|--------------------|------|-----|----|

| Latch-up 电流 (85°C) | -200 | 200 | mA |

根据《JEDEC STANDARD NO.78E NOVEMBER 2016》，对所有电源 IO 施加过压，在每个信号 IO 上注入 200mA 电流。测试结果显示芯片抗拴锁等级为 200mA。

表 5-5 LKS32AT089XLN8Q9 IO 极限参数

| 参数                   | 描述           | 最小    | 最大   | 单位 |

|----------------------|--------------|-------|------|----|

| V <sub>IN-GPIO</sub> | GPIO信号输入电压范围 | -0.3  | 6.0  | V  |

| I <sub>INJ_PAD</sub> | 单个GPIO最大注入电流 | -11.2 | 11.2 | mA |

| I <sub>INJ_SUM</sub> | 所有GPIO最大注入电流 | -50   | 50   | mA |

表 5-6 LKS32AT089XLN8Q9 IO DC 参数

| 参数                  | 描述              | AVDD | 条件           | 最小       | 典型  | 最大       | 单位 |

|---------------------|-----------------|------|--------------|----------|-----|----------|----|

| V <sub>H</sub>      | 数字IO输入高电压       | 5V   | -            | 0.7*AVDD |     |          | V  |

|                     |                 | 3.3V |              | 2.0      |     |          |    |

| V <sub>IL</sub>     | 数字IO输入低电压       | 5V   | -            |          |     | 0.3*AVDD | V  |

|                     |                 | 3.3V |              |          |     | 0.8      |    |

| V <sub>HYS</sub>    | 施密特迟滞范围         | 5V   | -            | 0.1*AVDD |     |          | V  |

|                     |                 | 3.3V |              |          |     |          |    |

| I <sub>IH</sub>     | 数字IO输入高电压, 电流消耗 | 5V   | -            |          |     | 1        | uA |

|                     |                 | 3.3V |              |          |     |          |    |

| I <sub>IL</sub>     | 数字IO输入低电压, 电流消耗 | 5V   | -            | -1       |     |          | uA |

|                     |                 | 3.3V |              |          |     |          |    |

| V <sub>OH</sub>     | 数字IO输出高电压       |      | 最大驱动电流11.2mA | AVDD-0.8 |     |          | V  |

| V <sub>OL</sub>     | 数字IO输出低电压       |      | 最大驱动电流11.2mA |          |     | 0.5      | V  |

| R <sub>pup</sub>    | 上拉电阻大小*         | 复位引脚 |              | 100      | 200 | 400      | kΩ |

|                     |                 | 普通IO |              | 8        | 10  | 12       |    |

| R <sub>io-ana</sub> | IO与内部模拟电路间连接电阻  |      |              | 100      |     | 200      | Ω  |

| C <sub>IN</sub>     | 数字IO输入电容        | 5V   | -            |          |     | 10       | pF |

|                     |                 | 3.3V |              |          |     |          |    |

\*仅部分 IO 内置上拉，详见引脚说明章节

表 5-7 LKS32AT089XLN8Q9 电路模块电流消耗 IDD

| 模块               | Min | Typ   | Max | 单位 |

|------------------|-----|-------|-----|----|

| 模拟比较器CMP(1个)     |     | 0.005 |     | mA |

| 运算放大器OPA(1个)     |     | 0.450 |     | mA |

| 模数转换器ADC         |     | 3.710 |     | mA |

| 数模转换器DAC         |     | 0.710 |     | mA |

| 温度传感器Temp Sensor |     | 0.150 |     | mA |

| 带隙基准BGP          |     | 0.154 |     | mA |

| 4MHz RC时钟        |     | 0.105 |     | mA |

| 锁相环PLL           |     | 0.080 |     | mA |

|                        |    |       |    |    |

|------------------------|----|-------|----|----|

| CPU+flash+SRAM (96MHz) |    | 8.667 |    | mA |

| CPU+flash+SRAM (12MHz) |    | 1.600 |    | mA |

| CRC                    |    | 0.070 |    | mA |

| DSP                    |    | 3.421 |    | mA |

| UART                   |    | 0.107 |    | mA |

| DMA                    |    | 1.340 |    | mA |

| MCPWM                  |    | 0.053 |    | mA |

| TIMER                  |    | 0.269 |    | mA |

| SPI                    |    | 0.500 |    | mA |

| IIC                    |    | 0.500 |    | mA |

| CAN                    |    | 2.200 |    | mA |

| 休眠                     | 10 | 30    | 50 | uA |

以上测试如无特别标注，均为室温 25°5V 供电，使用 96MHz 时钟工作情况下的测试，由于制造工艺存在器件模型偏差，不同芯片的电流消耗会存在个体差异。

表 5-8 LKS32AT089XLN8Q9 休眠电流消耗 Iq

| 模块               | Min | Typ | Max  | 单位 |

|------------------|-----|-----|------|----|

| VIN (12V, INH=1) | 40  | 70  | 100  | uA |

| VIN (12V, INH=0) | 0.1 | 0.2 | 0.25 | uA |

| VCC (12V)        | 40  | 43  | 95   | uA |

| VBAT (12V)       | 10  | 20  | 40   | uA |

## 6 模拟性能参数

表 6-1 LKS32AT089XLN8Q9 模拟性能参数

| 参数                | 最小   | 典型   | 最大       | 单位     | 说明                   |

|-------------------|------|------|----------|--------|----------------------|

| <b>模数转换器(ADC)</b> |      |      |          |        |                      |

| 工作电源              | 3.3  | 5    | 5.5      | V      | ADC 选择 2.4V 内部基准源    |

|                   | 2.8  | 5    | 5.5      | V      | ADC 选择 1.2V 内部基准源    |

| 输出码率              |      | 3    |          | MHz    | $f_{adc}/16$         |

| 差分输入信号范围          | -REF |      | +REF     | V      | Gain=1 时; REF=2.4V   |

|                   | -3.6 |      | +3.6     | V      | Gain=2/3 时; REF=2.4V |

| 单端输入信号范围          | -0.3 |      | AVDD+0.3 | V      | 受限于 IO 口输入电压限制       |

| 直流失调(offset)      |      | 5    | 10       | mV     | 可校正                  |

| 有效位数(ENOB)        | 10.5 | 11   |          | bit    |                      |

| INL               |      | 2    | 3        | LSB    |                      |

| DNL               |      | 1    | 2        | LSB    |                      |

| SNR               | 63   | 66   |          | dB     |                      |

| 输入电阻              | 100k |      |          | Ohm    |                      |

| 输入电容              |      | 10pF |          | F      |                      |

| <b>基准电压(REF)</b>  |      |      |          |        |                      |

| 工作电源              | 3.0  | 5    | 5.5      | V      |                      |

| 输出偏差              | -9   |      | 9        | mV     |                      |

| 电源抑制比             |      | 70   |          | dB     |                      |

| 温度系数              |      | 20   |          | ppm/°C |                      |

| 输出电压              |      | 1.2  |          | V      |                      |

| <b>数模转换器(DAC)</b> |      |      |          |        |                      |

| 工作电源              | 3.0  | 5    | 5.5      | V      |                      |

| 负载电阻              | 5k   |      |          | Ohm    | 输出 BUFFER 开启         |

| 负载电容              |      |      | 50p      | F      |                      |

| 输出电压范围            | 0.05 |      | AVDD-0.1 | V      |                      |

| 转换速度              |      |      | 1M       | Hz     |                      |

| DNL               |      | 1    | 2        | LSB    |                      |

| INL               |      | 2    | 4        | LSB    |                      |

| OFFSET            |      | 5    | 10       | mV     |                      |

| SNR               | 57   | 60   | 66       | dB     |                      |

| <b>运算放大器(OPA)</b> |      |      |          |        |                      |

| 工作电源              | 2.8  | 5    | 5.5      | V      |                      |

| 带宽                |      | 10M  | 20M      | Hz     |                      |

| 负载电阻              | 20k  |      |          | Ohm    |                      |

| 负载电容              |      |      | 5p       | F      |                      |

| 输入共模范围            | 0    |      | AVDD     | V      |                      |

| 输出信号范围            | 0    |      | 2*Vcm    | V      | 最小负载电阻下              |

| 共模电平(Vcm)         | 1.65 | 1.9  | 2.2      | V      | 测量条件：常温。             |

| 参数              | 最小  | 典型    | 最大   | 单位   | 说明                                                                                                                                    |

|-----------------|-----|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------|

|                 |     |       |      |      | 运放摆幅 = $2 \times \min(\text{AVDD}-\text{Vcm}, \text{Vcm})$ 。建议使用 OPA 单端输出的应用上电后进行 Vcm 测量并进行软件减除校正。更多分析请参考官网应用笔记《ANN009-运放差分和单端工作模式区别》 |

| OFFSET          |     | 10    | 15   | mV   | 此 OFFSET 为 OPA 差分输入短接时，测量 OPA_OUT 偏离 0 电平，得到的等效差分输入端偏差。<br>OPA 输出端偏差为 OPA 放大倍数 $\times \text{OFFSET}$                                 |

| 共模抑制(CMRR)      |     | 80    |      | dB   |                                                                                                                                       |

| 电源抑制(PSRR)      |     | 80    |      | dB   |                                                                                                                                       |

| 负载电流            |     |       | 500  | uA   |                                                                                                                                       |

| 摆率(Slew rate)   |     | 5     |      | V/us |                                                                                                                                       |

| 相位裕度            |     | 60    |      | 度    |                                                                                                                                       |

| <b>比较器(CMP)</b> |     |       |      |      |                                                                                                                                       |

| 工作电源            | 3.0 | 5     | 5.5  | V    |                                                                                                                                       |

| 输入信号范围          | 0   |       | AVDD | V    |                                                                                                                                       |

| OFFSET          |     | 5     | 10   | mV   |                                                                                                                                       |

| 传输延时            |     | 0.15u |      | S    | 默认功耗                                                                                                                                  |

|                 |     | 0.6u  |      | S    | 低功耗                                                                                                                                   |

| 回差(Hysteresis)  |     | 20    |      | mV   | HYS='0'                                                                                                                               |

|                 |     | 0     |      | mV   | HYS='1'                                                                                                                               |

模拟寄存器表说明：

地址 0x40000040~0x40000050 是各个模块的校正寄存器，这些寄存器在出厂之前都会填上各自的校正值。一般情况下用户不要去配置或改变这些值。如果需要对模拟参数进行微调，需要读取原校正值，并以此为基础进行微调。

地址 0x40000020~0x4000003c 是开放给用户的寄存器，其中空白部分的寄存器必须全部配置为 0(芯片上电后会被复位为 0)。其他寄存器根据应用场合需要进行配置。

## 7 电源管理系统

### AVDD 引脚电源系统

电源管理系统由 LDO15 模块、电源检测模块(PVD)、上电/掉电复位模块(POR)组成。

MCU 由 3.0V~5.5V 电源供电，芯片内部集成一路 LDO15 给内部所有数字电路、PLL 模块供电。

LDO 上电后自动开启，无需软件配置，但 LDO 输出电压可通过软件实现微调。

LDO15 在芯片出厂前已经过校正。

LKS32AT089XLN8Q9 集成了一路 5V 的 LDO，当芯片使用 7~20V VCC 供电时，内部 LDO 可产生 5V 电源给 MCU 供电，或供电至片外。

POR 模块监测 LDO15 的电压，在 LDO15 电压低于 1.1V 时(例如上电之初，或者掉电之时)，为数字电路提供复位信号以避免数字电路工作产生异常。

PVD 模块对 5V 输入电源进行检测，如低于某一设定阈值，则产生报警(中断)信号以提醒 MCU。中断提醒阈值可通过寄存器 PVDSEL<1:0>设置为不同的电压。PVD 模块可通过设置 PD\_PDT='1'关闭。具体寄存器所对应值见模拟寄存器表说明。

### VCC 引脚电源系统

VCC 引脚供电范围是 4.5~20V，为芯片内驱动模块提供供电，欠压位典型值为 4V。

## 8 时钟系统

时钟系统包括内部 32KHz RC 时钟、内部 4MHz RC 时钟、外部 4MHz 晶体起振电路、PLL 电路组成。

32K RC 时钟作为 MCU 系统慢时钟使用，作为诸如滤波模块或者低功耗状态下的 MCU 时钟使用。4MHz RC 时钟作为 MCU 主时钟使用，配合 PLL 可提供最高到 96MHz 的时钟。外部 4MHz 晶体起振电路作为备份时钟使用。

32k 和 4M RC 时钟均带有出厂校正。32K RC 时钟在-40~105°C 范围内的精度为±50%，4M RC 时钟在该温度范围的精度为±1%。

4M RC 时钟通过设置 RCHPD = '0' 打开(默认打开，设'1'关闭)，RC 时钟需要 Bandgap 电压基准源模块提供基准电压和电流，因此开启 RC 时钟需要先开启 BGP 模块。芯片上电的默认状态下，4M RC 时钟和 BGP 模块都是开启的。32K RC 时钟是始终开启的，不能关闭。

PLL 对 4M RC 时钟进行倍频，以提供给 MCU、ADC 等模块更高速的时钟。MCU 和 PWM 模块的最高时钟为 96MHz，ADC 模块典型工作时钟为 48MHz，通过寄存器 ADCLKSEL<1:0>可设置为不同的 ADC 工作频率。

PLL 通过设置 PLLPDN='1' 打开(默认关闭，设 1 打开)，开启 PLL 模块之前，同样也需要开启 BGP(Bandgap)模块。开启 PLL 之后，PLL 需要 6us 的稳定时间来输出稳定时钟。芯片上电的默认状态下，RCH 时钟和 BGP 模块都是开启的，但 PLL 默认是关闭的，需要软件来开启。

晶体起振电路内置了放大器，需在 IO OSC\_IN/OSC\_OUT 之间接入一个晶体，且 OSC\_IN/OSC\_OUT 上各放一个 15pF 的电容到地，并设置 XTALPDN='1' 即可起振。

## 9 基准电压源

该基准源为 ADC、DAC、RC 时钟、PLL、温度传感器、运算放大器、比较器和 FLASH 提供基准电压和电流，使用上述任何一个模块之前，都需要开启 BGP 基准电压源。

芯片上电的默认状态下，BGP 模块是开启的。基准源通过设置 BGPPD ='0' 打开，从关闭到开启，BGP 需要约 2us 达到稳定。BGP 输出电压约 1.2V，精度为±0.8%

基准源可通过设置 REF\_AD\_EN='1'，将基准电压送至 IO P2.3 进行测量。

## 10 ADC 模块

芯片内部集成 1 路同步双采样的 SAR 结构 ADC，芯片上电的默认状态下，ADC 模块是关闭的。ADC 开启前，需要先开启 BGP 和 4M RC 时钟和 PLL 模块，并选择 ADC 工作频率。默认配置下 ADC 工作时钟是 48M，对应 3MHz 的转换数据率。

同步双采样电路可在同一时刻对两路输入信号进行采样，采样完成之后 ADC 按先后顺序将这两路信号进行转换，并写入相应的数据寄存器中。

ADC 完成一次转换需要 16 个 ADC 时钟周期，其中 13 个为转换周期，3 个为采样周期。即  $f_{conv} = f_{adc} / 16$ 。在 ADC 时钟设为 48M 时，转换速率是 3MHz。

ADC 在降频应用时，可通过寄存器 CURRIT<1:0>降低 ADC 的功耗水平。

ADC 可工作在如下模式：单次单通道触发、连续单通道、单次 1~20 通道扫描、连续 1~20 通道扫描。每路 ADC 都有 20 组独立寄存器对应每一个通道。

ADC 触发事件可以来自外部的定时器信号 T0、T1、T2、T3 发生到预设次数，或者为软件触发。

20 个通道里最后一个通道用来测量 ADC 自身的 offset，将其保存在通道寄存器中，其他通道的 ADC 值都已自动减去该 offset。在芯片上电之初，应由 MCU 发起 offset 校正信号，校正控制模块将 ADC 通道设置为通道 1，并将值储存在通道寄存器中。如果客户对 offset 要求较高，可定期(例如一小时/一天)在 ADC 空闲时将 offset 校正一次。

在 GAIN\_REF=0 时，基准电压源为 2.4V。ADC 带有两种增益模式，通过 GAIN\_SHAx 进行设置，对应 1 倍和 2/3 倍增益。1 倍增益对应±2.4V 的输入信号，2/3 倍增益对应±3.6V 的输入信号幅度。在测量运放的输出信号时，根据运放可能输出的最大信号来选择具体的 ADC 增益。

## 11 运算放大器

4 路输入输出 rail-to-rail 运算放大器，内置反馈电阻 R2/R1，外部引脚需串联一个电阻 R0。反馈电阻 R2:R1 的阻值可通过寄存器 RES\_OPA0<1:0>设置，以实现不同的放大倍数。具体寄存器所对应值见模拟寄存器表说明。

最终的放大倍数为  $R2/(R1+R0)$ ，其中 R0 是外部电阻的阻值，

对于 MOS 管电阻直接采样的应用，建议接 $>20\text{k}\Omega$  的外部电阻，以减小 MOS 管关断时，往芯片引脚里流入的电流。

对于小电阻采样的应用，建议接  $100\Omega$  的外部电阻。

放大器可通过设置 OPAOUT\_EN<2:0>选择将 4 路放大器中的某一路输出信号通过 BUFFER 送至 P2.7 IO 口进行测量和应用(对应关系见 datasheet 芯片管脚说明)。因为有 BUFFER 存在，在运放正常工作模式下也可以选择送一路运放输出信号出来。

芯片上电的默认状态下，放大器模块是关闭的。放大器可通过设置 OPAXPDN ='1' 打开，开启放大器之前，需要先开启 BGP 模块。

运放输入同相和反相端内置钳位二极管，电机相线通过一匹配电阻后直接接入输入端，从而简化了 MOSFET 电流采样的外置电路。

## 12 比较器

内置 2 路输入 rail-to-rail 比较器，比较器比较速度可编程、迟滞电压可编程、信号源可编程。比较器的比较延时可通过寄存器 IT\_CMP 设置为 0.15uS/0.6uS。迟滞电压通过 CMP\_HYS 设置为 20mV/0mV。

比较器同相和反相两个输入端的信号来源都可通过寄存器 CMP\_SELP<2:0>和 CMP\_SELN<1:0>编程，详见寄存器模拟说明。

芯片上电的默认状态下，比较器模块是关闭的。比较器通过设置 CMPxPDN ='1' 打开，开启比较器之前，需要先开启 BGP 模块。

## 13 温度传感器

芯片内置温度传感器，在-40~85°C范围内典型精度为 2°C。85~105°C范围内典型精度为 3°C。

芯片出厂前会经温度校正，校正值保存在 flash info 区。

芯片上电的默认状态下，温度传感器模块是关闭的。开启传感器之前，需要先开启 BGP 模块。

温度传感器通过设置 TMPPDN='1'打开，开启到稳定需要约 2us，因此需在 ADC 测量传感器之前 2us 打开。

## 14 DAC 模块

芯片内置一路 12bit DAC，输出信号的最大量程可通过寄存器 `DAC_GAIN<1:0>` 设置为 1.2V/3V/4.85V。

12bit DAC 可通过配置寄存器 `DACOUT_EN=1`，将 DAC 输出送至 IO 口 P0.0，可驱动 $>5\text{k}\Omega$  的负载电阻和 50pF 的负载电容。

DAC 最大输出码率为 1MHz。

芯片上电的默认状态下，DAC 模块是关闭的。DAC 可通过设置 `DAC12BPDN =1` 打开，开启 DAC 模块之前，需要先开启 BGP 模块。

## 15 处理器核心

- 32 位 Cortex-M0+DSP 双核处理器

- 2 线 SWD 调试管脚

- 最高工作频率 96MHz

## 16 存储资源

### 16.1 Flash

- 内置 flash 包括 32kB/64kB 主存储区，1kB NVR 信息存储区

- 可反复擦除写入不低于 2 万次

- 室温 25°C 数据保持长达 100 年

- 单字节编程时间最长 7.5us，Sector 擦除时间最长 5ms

- Sector 大小 512 字节，可按 Sector 擦除写入，支持运行时编程，擦写一个 Sector 的同时读取访问另一个 Sector

- Flash 数据防窃取(最后一个 word 须写入非 0xFFFFFFFF 的任意值)

### 16.2 SRAM

- 内置 8kB SRAM

## 17 电机驱动专用 MCPWM

- MCPWM 最高工作时钟频率 96MHz

- 支持最大 4 通道相位可调的互补 PWM 输出

- 每个通道死区宽度可独立配置

- 支持边沿对齐 PWM 模式

- 支持软件控制 IO 模式

- 支持 IO 极性控制功能

- 内部短路保护，避免因为配置错误导致短路

- 外部短路保护，根据对外部信号的监控快速关断

- 内部产生 ADC 采样中断

- 采用加载寄存器预存定时器配置参数

- 可配置加载寄存器加载时刻和周期

## 18 Timer

- 4 路通用定时器,2 路 16bit 位宽计时器, 2 路 32bit 位宽计时器。

- 4 路支持捕获模式, 用于测量外部信号宽度

- 4 路支持比较模式, 用于产生边沿对齐 PWM/定时中断

## 19 Hall 传感器接口

- 内置最大 1024 级滤波

- 三路 Hall 信号输入

- 24 位计数器，提供溢出和捕获中断

## 20 DSP

- 电机控制算法专用 DSP，自主指令集，三级流水

- 最高工作频率 96MHz

- 32/16 位除法器 10 周期计算完成

- 32 位硬件开方 8 周期计算完成

- Q15 格式 Cordic 三角函数模块，sin/cos/artanc 8 周期计算完成

- DSP 配备独立的程序区和数据区，可自主执行 DSP 程序，亦可由 MCU 调用进行某项计算

- 支持中断暂停，与 MCU 进行数据交互

## 21 LIN 收发器

- LIN 传输数据速率高达 20kbps

- 集成 30kΩ LIN 上拉电阻

- 使用 INH 引脚控制系统级功耗

- 在 LIN 总线和 RXD 输出实现上电/断电无干扰运行

- 保护功能: ±58V LIN 总线容错、42V 负载突降支持、IEC ESD 保护、VBAT 输入端上的欠压保护、TXD 显性状态超时、热关断、系统级未供电节点或接地断开失效防护。

图 21-1 电源及休眠相关引脚说明

LIN 收发器的 RXD 引脚连接至 MCU 内核的 P0.7(UART\_RXD)和 P1.1(GPIO\_WAKE)， TXD 引脚连接至 MCU 内核的 P0.6 UART\_TXD， MCU 内核的 P3.4 控制收发器的 SLP\_N 引脚。

在正常模式下，当 MCU 配置 SLP\_N 信号出现下降沿，且 SLP\_N 的低电平维持时间大于 10us，同时 WAKE\_N 引脚为高，则 LIN-PHY 进入休眠模式。在休眠模式下 INH 信号将一直处于悬空状态，其他模式下 INH 引脚均为高电平。

根据应用情况，INH/EN 引脚可外接上拉或下拉电阻。当外接下拉电阻时，LIN-PHY 休眠后，INH 信号被外接下拉电阻拉低，5V LDO 被关闭，不再通过 AVDD 向 MCU 供电，此时可取得更小的休眠功耗 (5V LDO 供电 VIN 电流<1uA)；当外接上拉电阻时，LIN-PHY 休眠后，5V LDO 仍向 MCU 供电，MCU 可进入休眠。

VCC 为芯片内部集成预驱电源。休眠时不受影响，可在休眠时掉电。

VBAT 为芯片 LIN-PHY 独立供电, VIN 为 5V LDO 供电。通常休眠时不掉电。

LIN TXD 引脚配 500k $\Omega$ 下拉电阻, SLP\_N 引脚配 500k $\Omega$ 下拉电阻, WAKE\_N 引脚配 500k $\Omega$ 上拉电阻。

LIN 收发器主要有四种工作模式, 分别为休眠模式、待机模式、正常模式和上电模式。

休眠模式: 该模式是功耗最低的模式, 可通过 LIN 引脚对其进行远程唤醒, 也可通过 WAKE\_N 引脚对其进行本地唤醒, 或者通过 SLP\_N 引脚直接唤醒。在休眠模式下被唤醒的必要条件为: 通过 LIN 引脚对其进行远程唤醒的时间必须大于  $t_{wake(dom)LIN}$ (LIN 的唤醒时间 150 $\mu$ s); 通过 WAKE\_N 引脚对其进行本地唤醒的时间必须大于  $t_{wake(dom)WAKE_N}$ (WAKE\_N 的唤醒时间 60 $\mu$ s); 通过 SLP\_N 引脚直接唤醒的时间必须大于  $t_{gotonorm}$ (10 $\mu$ s)。LIN-PHY 被唤醒后, 可通过 P1.1 引脚进一步唤醒 MCU 内核。

待机模式: 当处于休眠模式时, 若检测到本地或远程唤醒事件, 器件会立即自动进入待机模式, RXD 引脚上的低电平会表示该唤醒过程。器件由休眠模式进入到待机模式后, INH 引脚被置为高。若在待机模式下将 SLP\_N 引脚置为高电平, 可能会出现以下情况:

- (1) 立即复位唤醒源标志; 造成在执行实际模式切换之前( $t_{gotonorm}$ 之后)释放掉 TXD 上可能存在的强下拉状态。

- (2) 当 SLP\_N 引脚上的高电平维持时间超过  $t_{gotonorm}$  时, 器件进入正常模式。

- (3) RXD 引脚上的唤醒请求信号被立即复位。

正常模式: LIN 总线电平 12V, LIN 接收时, 转为 5V 通过 RXD 给到 MCU, 发送时将 MCU TXD 转为 12V 输出到总线。在休眠、待机或上电模式下, 只要 SLP\_N 引脚的高电平维持时间大于  $t_{gotonorm}$ , 器件就会进入正常模式。如果 SLP\_N 引脚上的低电平维持时间大于  $t_{gotosleep}$ (10 $\mu$ s), 则器件切换到休眠模式。

上电模式: 当处于上电模式时, RXD 引脚悬空, TXD 引脚弱下拉, 但发送器和接收器均未激活。若 SLP\_N 引脚的高电平维持时间大于  $t_{gotonorm}$ , 则器件进入正常模式。

在正常模式下, 当 SLP\_N 引脚出现下降沿, 且 SLP\_N 的低电平维持时间大于  $t_{gotosleep}$ , 则进入休眠模式。在休眠模式下 INH 引脚将一直处于悬空状态, 其他模式下 INH 引脚均为高电平, 可通过外界上拉或下拉电阻控制 5V LDO 使能 EN。若外接上拉, 则 5V LDO 始终保持供电, 若下拉则在休眠时停止给 MCU 供电, 芯片整体休眠功耗会更低。

## 22 通用外设

- 两路 UART，全双工工作，支持 7/8 位数据位、1/2 停止位、奇/偶/无校验模式，带 1 字节发送缓存、1 字节接收缓存，支持 Multi-drop Slave/Master 模式，波特率支持 300~115200

- 一路 SPI，支持主从模式

- 一路 IIC，支持主从模式

- 一路 CAN

- 硬件看门狗，使用 RC 时钟驱动，独立于系统高速时钟，写入保护，2/4/8/64 秒复位间隔

## 23 栅极驱动模块

### 23.1 模块参数

#### 23.1.1 LKS32AT089XLN8Q9(YYWWXC)

表 23-1 LKS32AT089XLN8Q9(YYWWXC)器件参数

| 参数                                         | 最小     | 典型  | 最大      | 单位   | 说明                   |

|--------------------------------------------|--------|-----|---------|------|----------------------|

| 极限参数                                       |        |     |         |      |                      |

| 电源电压 VCC                                   | -0.3   |     | +25.0   | V    | 相对于地                 |

| 浮动电压 VB <sub>1,2,3</sub>                   | -0.3   |     | +250    | V    |                      |

| 浮动偏置 VS <sub>1,2,3</sub>                   | VB-25  |     | VB+0.3  | V    |                      |

| 高侧输出电压 HO <sub>1,2,3</sub>                 | VS-0.3 |     | VB+0.3  | V    |                      |

| 低侧输出电压 LO <sub>1,2,3</sub>                 | -0.3   |     | VCC+0.3 | V    |                      |

| 逻辑输入 HIN/LIN <sub>1,2,3</sub>              | -0.3   |     | VCC+0.3 | V    |                      |

| 开关电压摆率 dVs/dt                              |        |     | 50      | V/ns |                      |

| 结温 TJ                                      | -40    |     | 150     | °C   |                      |

| 存储温度 Ts                                    | -55    |     | 150     | °C   |                      |

| 焊接温度                                       |        |     | 300     | °C   | 焊接 10s               |

| 建议工况                                       |        |     |         |      |                      |

| 电源电压 VCC                                   | +7     |     | +20.0   | V    | 相对于地                 |

| 浮动电压 VB <sub>1,2,3</sub>                   | VS+8   |     | VS+20   | V    |                      |

| 浮动偏置 VS <sub>1,2,3</sub>                   | -5     |     | 200     | V    |                      |

| 高侧输出电压 HO <sub>1,2,3</sub>                 | VS     |     | VB      | V    |                      |

| 低侧输出电压 LO <sub>1,2,3</sub>                 | 0      |     | VCC     | V    |                      |

| 逻辑输入 HIN/LIN <sub>1,2,3</sub>              | 0      |     | VCC     | V    |                      |

| 工作温度 TA                                    | -40    |     | 125     | °C   |                      |

| 门极驱动器电气参数                                  |        |     |         |      |                      |

| VCC 静态电流 I <sub>QCC</sub>                  |        | 50  | 100     | uA   | HIN=LIN=0V           |

| VB 静态电流 I <sub>QBS</sub>                   |        | 20  | 40      | uA   | HIN=LIN=0V           |

| 浮动电压漏电流 I <sub>LK</sub>                    |        |     | 10      | uA   | VB=VS=220V           |

| VCC 欠压触发电压                                 | 3.6    | 4.9 | 6.4     | V    |                      |

| VCC 欠压回滞                                   | 0.25   | 0.5 | 0.8     | V    |                      |

| VBS 欠压触发电压                                 | 3.5    | 4.8 | 6.2     | V    |                      |

| VBS 欠压回滞                                   | 0.25   | 0.5 | 0.8     | V    |                      |

| 高输入阈值 V <sub>IH</sub>                      | 2.8    |     |         | V    |                      |

| 低输入阈值 V <sub>IL</sub>                      |        |     | 0.8     | V    |                      |

| 输入偏置电流 I <sub>source</sub>                 |        | 32  | 120     | uA   | HIN=LIN=5V           |

| 输入偏置电流 I <sub>sink</sub>                   |        |     | 1       | uA   | HIN=LIN=0V           |

| 高电平输出电压, V <sub>BIAS</sub> -V <sub>O</sub> |        |     | 1       | V    | I <sub>O</sub> =20mA |

| 低电平输出电压, V <sub>O</sub>                    |        |     | 1       | V    | I <sub>O</sub> =20mA |

|                      |     |      |     |    |                                    |

|----------------------|-----|------|-----|----|------------------------------------|

| 高电平输出短路脉冲电流 $I_{O+}$ | 650 | 1000 |     | mA | $V_{CC}/V_{BS}=15V$                |

| 低电平输出短路脉冲电流 $I_{O-}$ | 650 | 1000 |     | mA | $V_{CC}/V_{BS}=15V$                |

| 输出上升时间 $T_r$         |     | 15   | 30  | ns | $C_L=1nF$                          |

| 输出下降时间 $T_f$         |     | 12   | 30  | ns |                                    |

| 导通延迟时间 $T_{on}$      |     | 270  | 500 | ns |                                    |

| 关断延迟时间 $T_{off}$     |     | 80   | 150 | ns |                                    |

| 死区 $D_T$             | 100 | 200  | 400 | ns |                                    |

| 延时匹配度 $M_T$          |     |      | 80  | ns | $T_{on} \& T_{off}$ for<br>(HS-LS) |

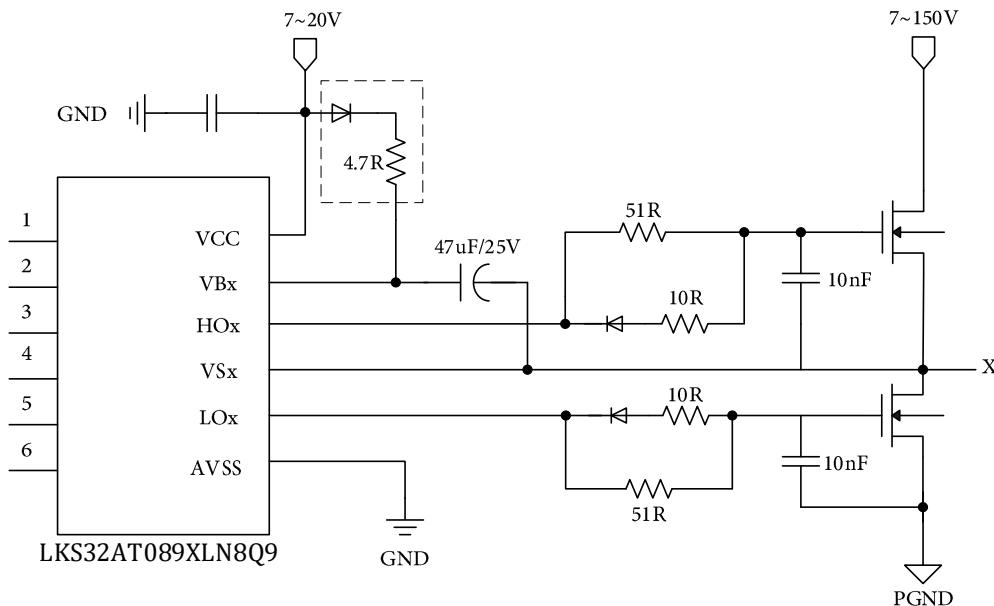

## 23.2 推荐应用图

图 23-1 LKS32AT089XLN8Q9 驱动模块典型应用图

图中只保留了栅极驱动模块管脚， $x=1,2,3$ ，分别对应 3 组 MOS 栅极驱动输出。

驱动模块的输出引脚信号 LO1/HO1 对应 MCU 的 GPIO P1.5/P1.4 的 MCPWM 功能输出，LO2/HO2 对应 MCU 的 GPIO P1.7/P1.6 的 MCPWM 功能输出，LO3/HO3 对应 MCU 的 GPIO P1.9/P1.8 的 MCPWM 功能输出，同时 P3.13 / P1.12 / P1.15 这 3 个 GPIO 需设置为输出态。需注意的是，控制驱动模块的 LOx 的各个 GPIO，为高电平'1'对应 LOx 输出'1'。

栅极驱动模块输入输出极性对应关系如下：

表 23-2 LKS32AT089XLN8Q9(YYWWXC)栅极驱动极性真值表

| {HIN, LIN} | HO | LO |       |

|------------|----|----|-------|

| 00         | 0  | 0  | 上下管关断 |

| 01         | 0  | 1  | 下管导通  |

| 10         | 1  | 0  | 上管导通  |

|    |   |   |                |

|----|---|---|----------------|

| 11 | 0 | 0 | 上下管同时导通，硬件短路保护 |

|----|---|---|----------------|

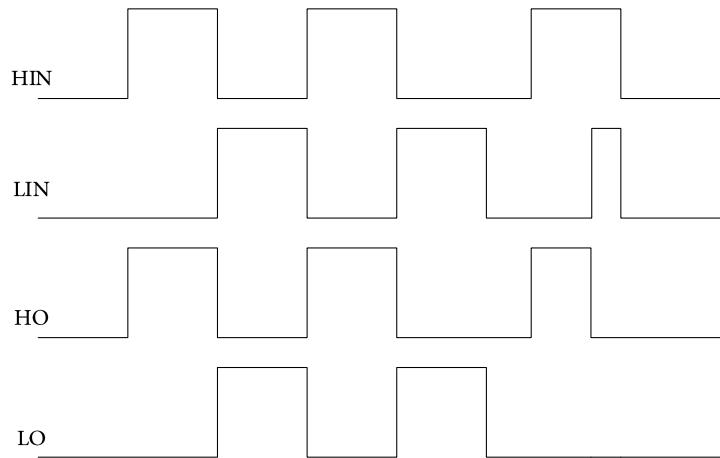

图 23-2 LKS32AT089XLN8Q9(YYWWXC)栅极驱动极性示意图

## 24 特殊 IO 复用

### LKS08x 特殊 IO 复用注意事项

SWD 协议包含两根信号线: SWDCLK 和 SWDIO。SWDCLK 是时钟信号, 在 SWD 模式下一直为输入。SWDIO 是数据信号, 在 SWD 模式下为双向 IO, 默认是输入状态。

LKS08x 部分型号 SWD 引脚同时有 GPIO 功能。通常为 P0.0、P2.15。注意事项如下:

- 默认状态不开启 SWD 引脚的 GPIO 功能, 需要软件开启。即芯片硬复位结束后, 初始状态是 SWD 用途, SWD 引脚在芯片内部有上拉(芯片内部上拉电阻约为 10K), 应用对初始电平有要求的, 需注意。

- 如开启 GPIO 功能后, 如果 GPIO 功能与 SWD 功能冲突, 比如设置 GPIO 为输出, 则可能导致 KEIL 等工具无法通过 SWD 协议访问芯片, 此时 Debug 和擦除下载功能均失效。**因此建议:**

- 其一, 软件开启 GPIO 复用前留有一定延时, 建议 1s 以上, 保证凌鸥离线下载器能在芯片上电后软件延时期间完成芯片擦除动作。延时越大, 一次性擦除成功的概率越大。

- 其二, 软件设置有 GPIO 复用退出机制, 例如某个其它 IO 电平发生变化(一般为输入)或串行通讯, 表明需要用 SWD, 软件接收到指令后关闭 SWD 引脚的 GPIO 功能。此时, 可以恢复 KEIL 的功能。

在 SSOP24 封装和 QFN40 封装中, SWDIO 同 P0.0、P2.15 直接 bonding 在一起, 可以直接使能对应 GPIO。建议复用 SWDIO 时 SWDCLK 需保持不变(恒为 1 或者恒为 0)。

在 LKS087E 封装中, SWDCLK 同 P2.6 直接 bonding 在一起, 可以直接使能对应 GPIO。若同时复用 SWDIO 和 SWDCLK, SWDCLK 复用的注意事项如下:

- 默认状态不开启 SWD 引脚的 GPIO 功能, 需要软件开启。即芯片硬复位结束后, 初始状态是 SWD 用途, SWD 引脚在芯片内部有上拉(芯片内部上拉电阻约为 10K), 应用对初始电平有要求的, 需注意。

- 如开启 GPIO 功能后, 如果 GPIO 功能与 SWD 功能冲突, 比如设置 GPIO 为输出, 则可能导致 KEIL 等工具无法通过 SWD 协议访问芯片, 此时 Debug 和擦除下载功能均失效。**因此建议:**

- 其一, 软件开启 GPIO 复用前留有一定延时, 建议 1s 以上, 保证凌鸥离线下载器能在芯片上电后软件延时期间完成芯片擦除动作。延时越大, 一次性擦除成功的概率越大。

- 其二, 软件设置有 GPIO 复用退出机制, 例如某个其它 IO 电平发生变化(一般为输入)或串行通讯, 表明需要用 SWD, 软件接收到指令后关闭 SWD 引脚的 GPIO 功能。此时, 可以恢复 KEIL 的功能。

- SWDCLK 和 SWDIO 引脚都作为 GPIO 使用时不应同时动作。即 SWDCLK 复用开启, 且变化的时候, SWDIO 能保持为 0 电平(类似时分复用)。

若此时, 仅复用了 SWDCLK, 没有复用 SWDIO, 注意事项同上。

RSTN 信号, 默认是用于 LKS08x 芯片的外部复位脚。

LKS08x 可实现 RSTN 复用为其它 IO 的功能, 复用的 IO 是 P0.2。注意事项如下:

- 默认状态是不开启复用, 需要软件开启复用。即芯片初始状态是 RSTN 用途, RSTN 在芯片内部

- 有上拉(芯片内部上拉电阻约为 100K)，应用对初始电平有要求的，需注意。

- 默认状态是 RSTN，只有 RSTN 正常释放后才能开始程序的执行，应用需要保证 RSTN 有足够的保护，例如外围电路带上拉，若能加电容更佳。

- 开启复用后，RSTN 用途失效，若需产生芯片硬复位，源头只能是掉电/看门狗。

- RSTN 的复用，不影响 KEIL 的使用。

SYS\_RST\_CFG 寄存器的 BIT[5]，为 RSTN 和 P0.2 的复用控制开关。

## 25 订购包装信息

| 型号               | 封装形式            | 每盘/管数量 | 内盒数量    | 外箱数量     |

|------------------|-----------------|--------|---------|----------|

| LKS32AT089XLN8Q9 | QFN6*6 52L-0.55 | 490/盘  | 4900PCS | 29400PCS |

## 26 版本历史

表 26-1 文档版本历史

| 时间         | 版本号  | 说明                                       |

|------------|------|------------------------------------------|

| 2024.06.05 | 1.21 | 更新 ESD 等级信息                              |

| 2023.12.12 | 1.20 | 增加关于上拉电阻值的说明                             |

| 2023.11.09 | 1.19 | OPA OFFSET 增加说明，更新储存温度                   |

| 2023.09.25 | 1.18 | 电气性能参数更新                                 |

| 2023.07.09 | 1.17 | 去掉“如果 INH 下拉，不推荐使用 SLP_N 进入休眠”的表述        |

| 2023.04.28 | 1.16 | 增加 B 版本芯片，其 AVDD 供电范围 3.0~5.5V<br>修改封装名称 |

| 2023.04.03 | 1.15 | 修订 AVDD 工作范围，最低电压从 2.2V 提高到 3.0V         |

| 2023.03.20 | 1.14 | 修改驱动模块典型应用图                              |

| 2023.03.18 | 1.13 | 修改时钟精度的描述                                |

| 2023.02.24 | 1.12 | 更新休眠功耗信息及休眠流程的说明                         |

| 2023.02.18 | 1.11 | 增加 5V LDO 输出电流参数                         |

| 2023.01.13 | 1.1  | 增加订购包装信息                                 |

| 2022.12.18 | 1.0  | 初始版本                                     |

## 免责声明

LKS 和 LKO 为凌鸥创芯注册商标。

南京凌鸥创芯电子有限公司（以下简称：“Linko”）尽力确保本文档内容的准确和可靠，但是保留随时更改、更正、增强、修改产品和/或 文档的权利，恕不另行通知。用户可在下单前获取最新相关信息。

客户应针对应用需求选择合适的 Linko 产品，详细设计、验证和测试您的应用，以确保满足相应标准以及任何安全、安保或其它要求。客户应对此独自承担全部责任。

Linko 在此确认未以明示或暗示方式授予 Linko 或第三方的任何知识产权许可。

Linko 产品的转售，若其条款与此处规定不同，Linko 对此类产品的任何保修承诺无效。

禁止用于军事用途或生命监护、维持系统。

如有更早期版本文档，一切信息以此文档为准。