# Programmable Multi-Channel PMIC

Advanced Datasheet P9180A

### **Features**

- Single 3.15-5.25V supply input

- 3 x SVID IMVP8/VR12.1 compatible 5A synchronous step-down switching regulator with DPU interface to support up to four additional 6A phases

- 2 x step-down switching controller with DPU interface to support up to four 6A phases

- 2 x 2.3A synchronous step-down switching regulators

- Programmable mode selection:

- Automatic PWM/PFM mode transition for high efficiency at light load or

- PWM-only mode for low noise applications

- 6 x 50-400mA linear regulators, LDO0-2 with optional pass switch feature

- 1 x ±550mA Vtt linear regulator

- 10-bit ADC monitors internal and external voltages, currents and temperature

- Host interface and system management

- Interrupt controller with mask-able interrupts

- Reset function

- Power control state machine

- Programmable sequencing of output rails

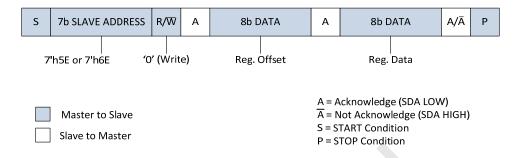

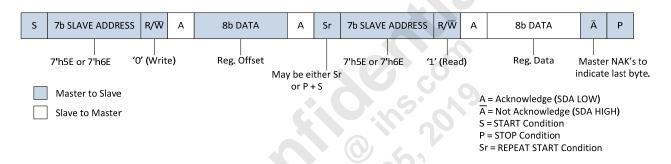

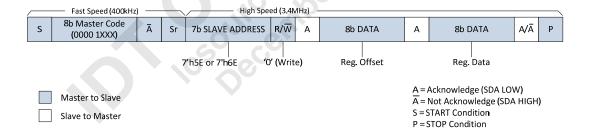

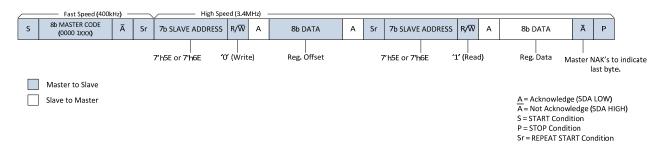

- High speed I<sup>2</sup>C interface (3.4Mbit/s)

- Programmable enable outputs for external switches

- 15 x GPIOs

- -40°C to +85°C operating temperature range

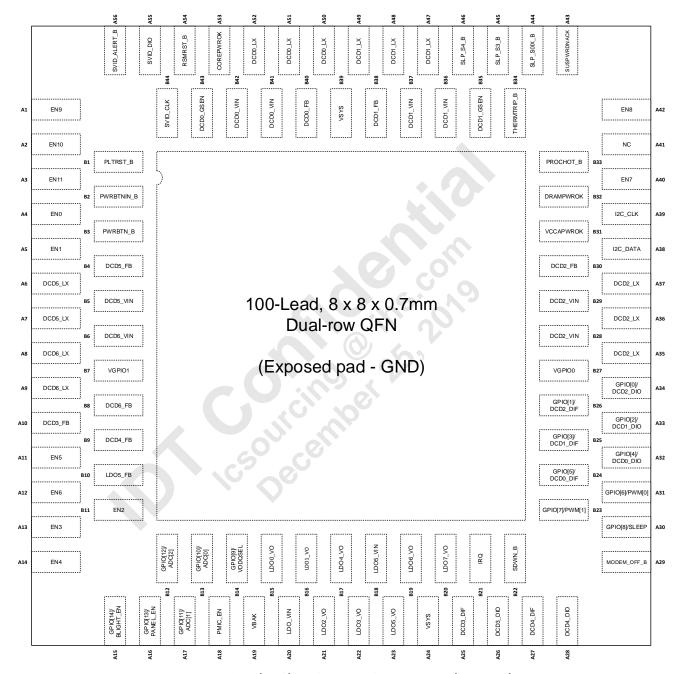

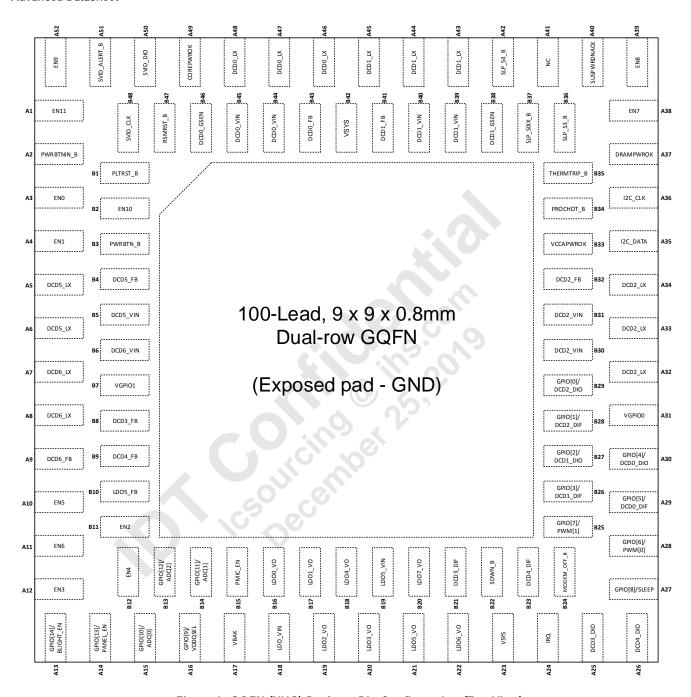

- Two thermally-enhanced package options:

100-ld, 8mm x 8mm x 0.7mm dual-row QFN

100-ld, 9mm x 9mm x 0.8mm dual-row GQFN or

# **Applications**

- Mobile (phones, tablets etc.)

- General Embedded Applications

- Print Imaging & Multi-Function Printers

- µServers

- Storage

- Industrial & Embedded Systems

# **Description**

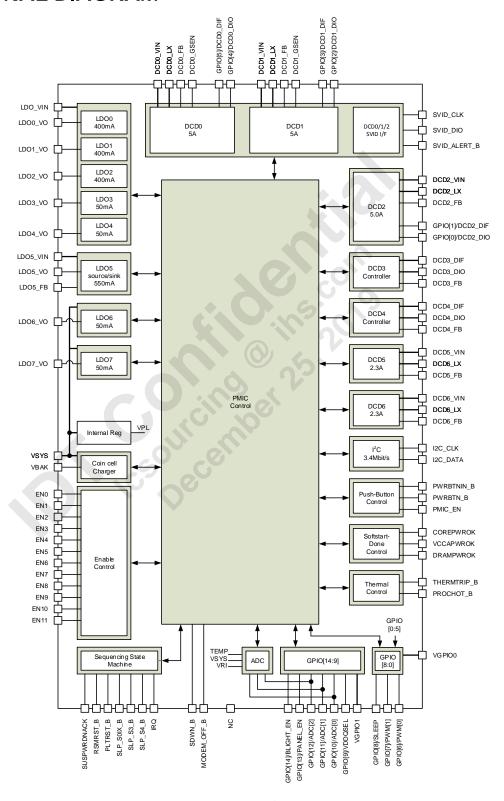

The P9180A is a highly programmable, multiple channel Power Management Integrated Circuit (PMIC) designed for the Intel™ ATOM® SoC to meet the high performance requirements as well as to provide a high level of integration to minimize system board area and BOM cost.

The PMIC includes sub-systems for voltage regulation, power sequencing management, A/D conversion, GPIOs, PWMs and others. The P9180A device is controlled and programmed via an I<sup>2</sup>C interface that operates in conjunction with the SoC. There is also a SerialVID (SVID) interface between the SoC and PMIC for handling VCC, VNN & VDDQ voltage rails control supporting the VR12.1 specification.

The P9180A is capable of providing current levels sufficient for entry level platforms with its internal regulators and is scalable to higher current requirements by adding IDT's unique Distributed Power Units (DPUs) (P9147/P9148) to source additional current for those DCDC rails.

Also included are 7 LDOs which are programmable over a wide output voltage range and offer output currents up to 550mA. These LDOs are designed for low noise, high PSRR and excellent transient response.

The default output voltages of all regulators as well as device sequencing can be programmed by OTP (at the factory) to adjust to nonstandard configurations. Contact IDT marketing for specific requirements.

# **Table of Contents**

| Absolute Maximum Ratings                                 | 3    |

|----------------------------------------------------------|------|

| Pin Configuration & Description                          |      |

| Functional Diagram                                       | 10   |

| Descriptions, Specification Tables & Registers           | 11   |

| General Specification                                    | 11   |

| Linear Regulators LDO0, LDO1, LDO2                       | 11   |

| Linear Regulators LDO3, LDO4                             | 14   |

| Linear Regulator LDO5                                    | 17   |

| Linear Regulator LDO6                                    | 19   |

| Linear Regulator LDO7                                    | 22   |

| LDO Current Limit Flags                                  | 22   |

| Switching Regulators for SoC Core, Graphics Memory Rails |      |

| Switching Regulator DCD0, DCD1                           | 24   |

| Switching Regulator DCD2                                 | 28   |

| Controllers DCD3, DCD4                                   | . 41 |

| Switching Regulator DCD5, DCD6                           |      |

| DCDs' General Registers                                  | 38   |

| Power Consumption at Light Load Considerations           |      |

| Enable Pins                                              |      |

| Sequencing Signal Registers                              | 46   |

| General Purpose IOs                                      | 47   |

| I <sup>2</sup> C Interface                               | 53   |

| Analog to Digital Converter (ADC)                        | 56   |

| Power Buttons PWRBTNIN_B and PMIC_EN | 57 |

|--------------------------------------|----|

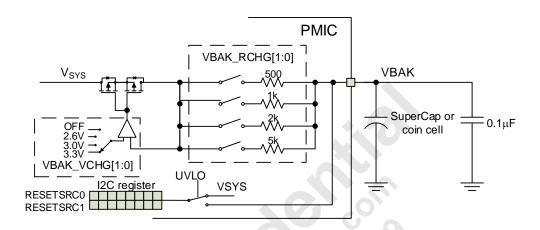

| VBAK Charger                         | 59 |

| Theory of Operation                  | 60 |

| Control Signals                      | 60 |

| SVID Interface                       | 62 |

| Control and Monitoring               | 67 |

| Input Power Source Detection         | 67 |

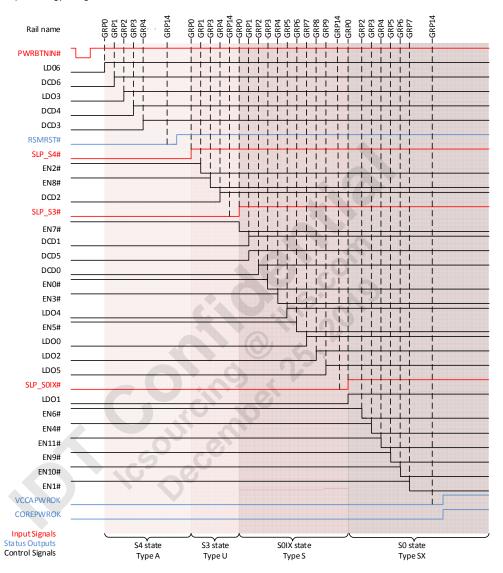

| Power States                         | 67 |

| Power State Transitions              | 73 |

| PMIC Resets                          | 78 |

| Interrupt Request (IRQ)              | 80 |

| Interrupting the SoC                 | 80 |

| Interrupt Request (IRQ) Control Unit | 81 |

| Second-Level Interrupts              | 82 |

| GPIO IRQ Registers                   | 83 |

| General Purpose ADC (GPADC)          | 86 |

| VR Current Monitoring                | 89 |

| Thermal Monitoring                   | 90 |

| Thermal Alerts                       | 91 |

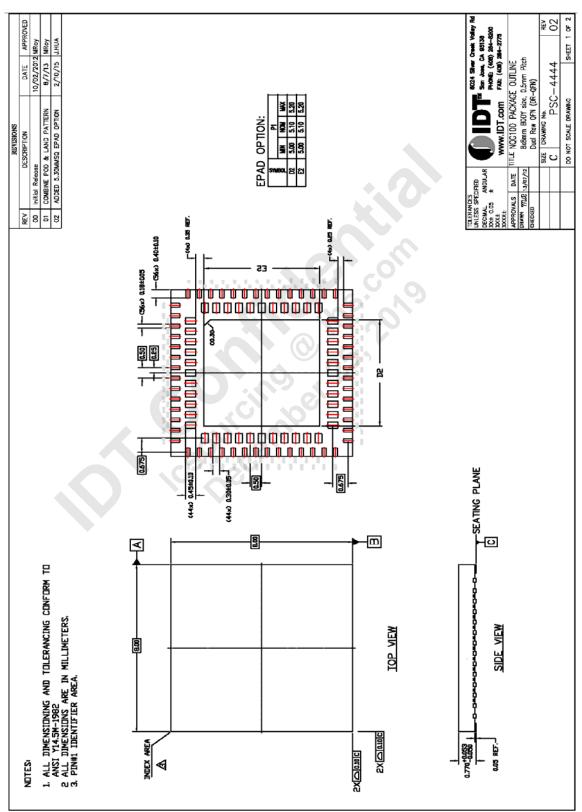

| Package Outline: QFN (NQG)           | 94 |

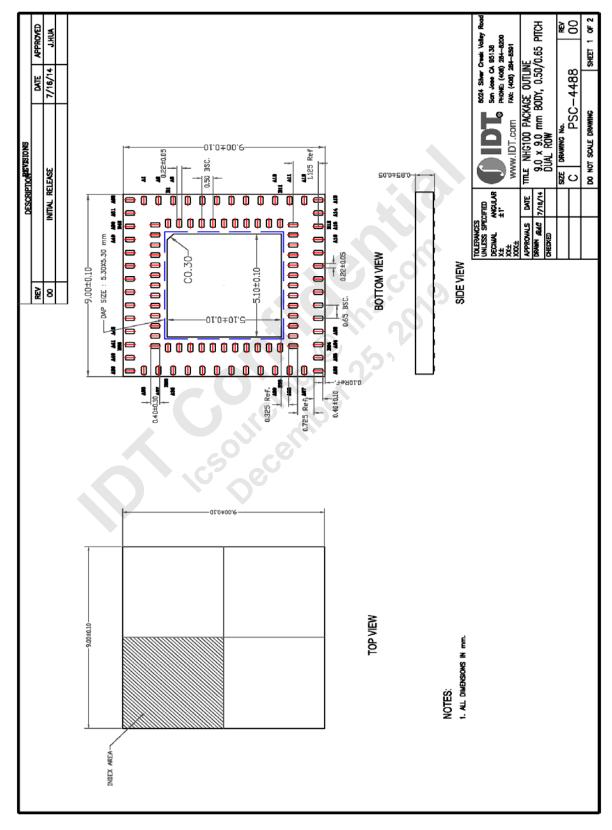

| Package Outline: GQFN (NHG)          | 95 |

| Ordering Guide                       | 96 |

# **ABSOLUTE MAXIMUM RATINGS**

**Table 1: Absolute Maximum Voltage**

| PIN NAME                          |                                                          |  | MAXIMUM RATING |  |

|-----------------------------------|----------------------------------------------------------|--|----------------|--|

| LDO_VIN, LDO5_<br>DCD[0:2]_FB, DC | -0.3 to 2.2 V                                            |  |                |  |

| GPIO[14:9]                        |                                                          |  | -0.3 to 3.6 V  |  |

| DCD0_LX, DCD1                     | -0.3 to 6.0 V                                            |  |                |  |

| DCD0_LX, DCD1                     | DCD0_LX, DCD1_LX, DCD2_LX, DCD5_LX, DCD6_LX AC (T<500ns) |  |                |  |

| All other pins                    |                                                          |  | -0.3 to 6.0 V  |  |

| CCD Dating                        | (HBM) Human Body Model (all pins)                        |  | ±1500 V        |  |

| ESD Rating                        | (CDM) Charged Device Model (all pins)                    |  | $\pm500~V$     |  |

| L otob up                         | GPIO pins, Grade II                                      |  | 40 mA          |  |

| Latch-up                          | All other pins, Grade II                                 |  | 100 mA         |  |

Table 2 - Package Thermal Information

| SYMBOL            | DESCRIPTION                                             | RA        | UNITS      |      |

|-------------------|---------------------------------------------------------|-----------|------------|------|

|                   | Thermal Resistances                                     | QFN (NQG) | GQFN (NHG) |      |

| θЈΑ               | Thermal Resistance Junction to Ambient                  | 24.4      | 24.0       | °C/W |

| θ <sub>JC</sub>   | Thermal Resistance Junction to Top of Case              | 21.7      | 19.3       | °C/W |

| θ <sub>ЈВ</sub>   | Thermal Resistance Junction to Board (1mm from package) | 1.0       | 0.7        | °C/W |

| TJ                | Junction Temperature                                    | -40 to    | °C         |      |

| T <sub>A</sub>    | Ambient Operating Temperature                           | -40 t     | °C         |      |

| T <sub>STG</sub>  | Storage Temperature                                     | -55 to    | °C         |      |

| T <sub>LEAD</sub> | Lead Temperature (soldering, 10s)                       | +3        | °C         |      |

Note 1: The maximum power dissipation is  $P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$  where  $T_{J(MAX)}$  is 125°C. Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the device will enter thermal shutdown.

Note 2: The thermal rating is calculated based on a JEDEC standard 2S2P 4-layer board (114 mm x 101 mm in still air condition with 2 oz. internal planes) and 5x5 mm EPAD solder down and a 25 thermal via array to the internal plane.

Note 3: Actual thermal resistance is affected by PCB size, solder joint quality, layer count, copper thickness, air flow, altitude, and other unlisted variables.

**Table 3: Recommended Operating Conditions**

| SYMBOL               | PARAMETER                                  | CONDITIONS | MIN  | TYP  | MAX  | UNITS |

|----------------------|--------------------------------------------|------------|------|------|------|-------|

| Vsys                 | PMIC Input voltage                         |            | 3.15 |      | 5.25 | V     |

| $V_{PVIN}$           | DCD0,1, 2, 5 & 6 Power Stage Input voltage |            | 2.8  |      | 5.25 | V     |

| V <sub>IN_LDO</sub>  | LDO0 – 4 Input voltage                     |            | 1.0  | 1.8  | 2.0  | V     |

| V <sub>IN_LDO5</sub> | LDO5 Input voltage                         |            | 1.2  | 1.35 | 1.5  | V     |

Table 4: Overview of the Power Supplies

| REGULATOR         | I <sub>OUT_MAX</sub> (A) | lout_max with<br>DPUs (A) 1,2 | V <sub>IN</sub> RANGE (V) <sup>3</sup>                 | V <sub>0</sub> RANGE (V) | C₀/L⁵                                                                            |

|-------------------|--------------------------|-------------------------------|--------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------|

| 2020              | DCD0 5.0 29              |                               |                                                        | SVID: 0.25 – 1.3V        |                                                                                  |

| DCD0              | 5.0                      | 29                            |                                                        | Non-SVID: 1.1 – 1.9V     | Factory-enabled loadline (DCD0,1 default): $C_0=6 \times 47 \mu F; L=0.47 \mu H$ |

| DCD1              | 5.0                      | 29                            | $V_{SYS} = V_{IN\_DCD0,1,2} =$                         | SVID: 0.25 – 1.3V        | Factory-disabled loadline (DCD2 default):                                        |

| וטטט              | 5.0                      | 29                            | 3.15 – 5.25V                                           | Non-SVID: 1.1 – 1.9V     | C <sub>O</sub> = 3 x 47μF; L=0.47μH                                              |

| DCD2              | 5.0                      | 29                            | 4. ()                                                  | SVID: 0.25 – 1.3V        | See DPU datasheet for additional Co                                              |

| DCD2              | 5.0                      | 29                            |                                                        | Non-SVID: 1.1 – 1.9V     | See DPO datastreet for additional Co                                             |

| DCD3_CTRL         | -                        | 24                            | V <sub>SYS</sub> =3.15 – 5.25                          | 0.525 – 3.6              | Co= 3 x 47µF per DPU; See DPU datasheet for L                                    |

| DCD4_CTRL         | -                        | 24                            | V <sub>SYS</sub> =3.15 – 5.25                          | 0.525 – 3.6              | C <sub>0</sub> = 3 x 47µF per DPU; See DPU datasheet for L                       |

| DCD5              | 2.3                      |                               | V <sub>SYS</sub> = V <sub>IN_DCD5</sub> = 3.15 – 5.25V | 0.525 – 3.375            | C <sub>O</sub> = 2 x 47μF; L=1.0μH                                               |

| DCD6              | 2.3                      | 1.10                          | V <sub>SYS</sub> = V <sub>IN_DCD6</sub> = 3.15 – 5.25V | 0.525 – 3.375            | Co= 2 x 47μF; L=1.0μH                                                            |

| LDO04             | 0.400                    | -                             |                                                        | 1.0 - 1.65               | C <sub>O</sub> = 2.2µF                                                           |

| LDO1 <sup>4</sup> | 0.400                    | -                             |                                                        | 1.0 - 1.65               | C <sub>0</sub> = 2.2µF                                                           |

| LDO2 <sup>4</sup> | 0.400                    | -                             | V <sub>LDO_VIN</sub> =1.0 – 2.0                        | 1.0 - 1.65               | C <sub>O</sub> = 2.2µF                                                           |

| LDO3              | 0.05                     | -                             |                                                        | 1.0 - 1.65               | C <sub>O</sub> = 1.0μF                                                           |

| LDO4              | 0.05                     | -                             |                                                        | 1.0 - 1.65               | C <sub>O</sub> = 1.0μF                                                           |

| LDO5              | 0.550                    | -                             | V <sub>LDO5_VIN</sub> =1.2 – 1.5                       | V <sub>IN_LDO5</sub> /2  | Co= 22µF                                                                         |

| LDO6              | 0.1                      | -                             | V <sub>SYS</sub> =3.15 – 5.25                          | 1.20 – 3.55              | C <sub>O</sub> = 1.0uF                                                           |

| LDO7              | 0.1                      | -                             | V <sub>SYS</sub> =3.15 – 5.25                          | 1.80                     | C <sub>0</sub> = 1.0uF                                                           |

Note 1: Ensure that DPU's PVIN voltage is above PVIN UVLO ( $V_{UV}$ ) before  $V_{SYS}$  reaches  $V_{SYS\_MIN}$ .

Note 2: PWRBTNIN\_B (or PMIC\_EN when used) should not be asserted until DPU is powered on.

Note 3: During power up ensure that the voltage seen by VSYS is monotonic, which can be achieved by adding appropriate RC filter.

Note 4: Can be configured as a pass switch

Note 5: The output capacitor recommendation is with X5R, 20%, 0805 minimum case size. Derating of ceramic capacitor due to operating conditions, such as bias voltage and temperature, should be considered as part of the component selection.

# PIN CONFIGURATION & DESCRIPTION

Figure 1: QFN (NQG) Package Pin Configuration (Top View)

Figure 2: GQFN (NHG) Package Pin Configuration (Top View)

Table 5: Pin Descriptions

|          | 1         | T .                    |     | T                                                                                                                                |

|----------|-----------|------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------|

| NQG(QFN) | NHG(GQFN) | LABEL                  | I/O | DESCRIPTION                                                                                                                      |

| A1       | A52       | EN9                    | 0   | Open drain output enable signal.                                                                                                 |

| A2       | B2        | EN10                   | 0   | Open drain output enable signal.                                                                                                 |

| A3       | A1        | EN11                   | 0   | Open drain output enable signal.                                                                                                 |

| A4       | A3        | EN0                    | 0   | Open drain output enable signal.                                                                                                 |

| A5       | A4        | EN1                    | 0   | Open drain output enable signal.                                                                                                 |

| A6       | A5        | DCD5_LX                | 0   | DCD5 switch node - this pin connects to the output inductor.                                                                     |

| A7       | A6        | DCD5_LX                | 0   | DCD5 switch node - this pin connects to the output inductor.                                                                     |

| A8       | A7        | DCD6 LX                | 0   | DCD6 switch node - this pin connects to the output inductor.                                                                     |

| A9       | A8        | DCD6_LX                | 0   | DCD6 switch node - this pin connects to the output inductor.                                                                     |

| A10      | В8        | DCD3_FB                | I   | Feedback voltage for DCD3 controller. This pin must be connected to the output voltage of the P9180A.                            |

| A11      | A10       | EN5                    | 0   | Open drain output enable signal.                                                                                                 |

| A12      | A11       | EN6                    | 0   | Open drain output enable signal.                                                                                                 |

| A13      | A12       | EN3                    | 0   | Open drain output enable signal.                                                                                                 |

| A14      | B12       | EN4                    | 0   | Open drain output enable signal.                                                                                                 |

| A15      | A13       | GPIO[14]/BLIGHT_E<br>N | I/O | General purpose input/output 14 or backlight enable output.                                                                      |

| A16      | A14       | GPIO[13]/PANEL_E<br>N  | I/O | General purpose input/output 13 or LCD panel enable output.                                                                      |

| A17      | B14       | GPIO[11]/ADC[1]        | I/O | General purpose input/output 11 or ADC1 input.                                                                                   |

| A18      | B15       | PMIC_EN                |     | PMIC enable input                                                                                                                |

| A19      | A17       | VBAK                   | 0   | Coin cell backup battery connection.                                                                                             |

| A20      | A18       | LDO VIN                |     | Input supply voltage for LDOs 0, 1, 2, 3 and 4.                                                                                  |

| A21      | A19       | LDO2 VO                | 0   | Linear regulator 2 output terminal.                                                                                              |

| A22      | A20       | LDO3 VO                | 0   | Linear regulator 3 output terminal.                                                                                              |

| A23      | A21       | LDO5_VO                | 0   | Source-sink regulator 5 output terminal.                                                                                         |

| A24      | A23       | VSYS                   | 1   | Input power supply powering the PMIC internal circuitry. Connect a 2.2µF capacitor from as close this pin to ground as possible. |

| A25      | B21       | DCD3_DIF               | I/O | DCD3 switching regulator digital interface output signal. This pin must be connected to the DIF pin of the P9147/P9148.          |

| A26      | A25       | DCD3_DIO               | I/O | DCD3 regulator digital interface input/output signal. This pin must be connected to the DIO P9147/P9148.                         |

| A27      | B23       | DCD4_DIF               | I/O | DCD4 regulator digital interface output signal. This pin must be connected to the DIF pin of the P9147/P9148.                    |

| A28      | A26       | DCD4_DIO               | I/O | DCD4 regulator digital interface input/output signal. This pin must be connected to the DIO pin of the P9147/P9148.              |

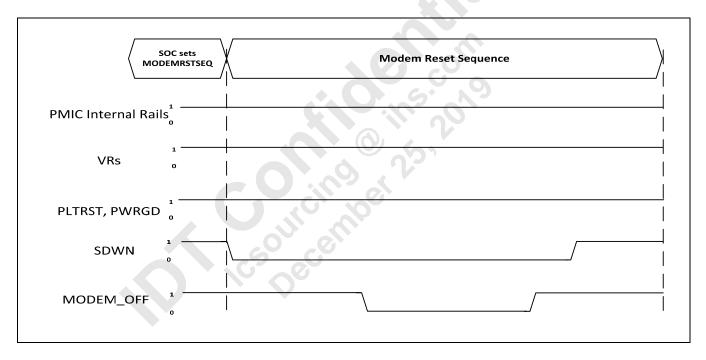

| A29      | B24       | MODEM_OFF_B            | 0   | Active low Modem Hard Reset Signal.                                                                                              |

| A30      | A27       | GPIO[8]/SLEEP          | I/O | General purpose input/output 8 or sleep mode control signal                                                                      |

| A31      | A28       | GPIO[6]/PWM[0]         | I/O | General purpose input/output 6 or PWM[0] output control signal.                                                                  |

| A32      | A30       | GPIO[4]/DCD0_DIO       | I/O | General purpose input/output 4 or DCD0 regulator digital interface input/output.                                                 |

| A33      | B27       | GPIO[2]/DCD1_DIO       | I/O | General purpose input/output 2 or DCD1 regulator digital interface input/output.                                                 |

| A34      | B29       | GPIO[0]/DCD2_DIO       | I/O | General purpose input/output 0 or DCD2 regulator digital interface input/output.                                                 |

| A35      | A32       | DCD2_LX                | 0   | DCD2 switch node - this pin connects to the output inductor.                                                                     |

| A36      | A33       | DCD2_LX                | 0   | DCD2 switch node - this pin connects to the output inductor.                                                                     |

|          |           |                        |     |                                                                                                                                  |

| NQG(QFN) | NHG(GQFN) | LABEL           | I/O | DESCRIPTION                                                                                                                                        |

|----------|-----------|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|

| A37      | A34       | DCD2 LX         | 0   | DCD2 switch node - this pin connects to the output inductor.                                                                                       |

| A38      | A35       | I2C_DATA        | I/O | I <sup>2</sup> C data                                                                                                                              |

| A39      | A36       | I2C CLK         | 1   | I <sup>2</sup> C clock                                                                                                                             |

| A40      | A38       | EN7             | 0   | Open drain output enable signal.                                                                                                                   |

| A41      | A41       | N/C             | -   | No connect                                                                                                                                         |

| A42      | A39       | EN8             | 0   | Open drain output enable signal.                                                                                                                   |

| A43      | A40       | SUSPWRDNACK     | Ī   | Suspend power down acknowledgment.                                                                                                                 |

| A44      | B37       | SLP_S0IX_B      | -   | Active low input signal. When connected to logic high, all the "SX" power type rails are enabled. When pulled low, the regulators shutdown.        |

| A45      | B36       | SLP_S3_B        | I   | Active low input signal. When connected to logic high, all the "S" power type rails are enabled. When pulled low, the regulators shutdown.         |

| A46      | A42       | SLP_S4_B        | Ι   | Active low input signal. When connected to logic high, all the "U" power type rails are enabled. When pulled low, the regulators shutdown.         |

| A47      | A43       | DCD1_LX         | 0   | DCD1 switch node - this pin connects to the output inductor.                                                                                       |

| A48      | A44       | DCD1_LX         | 0   | DCD1 switch node - this pin connects to the output inductor.                                                                                       |

| A49      | A45       | DCD1_LX         | 0   | DCD1 switch node - this pin connects to the output inductor.                                                                                       |

| A50      | A46       | DCD0_LX         | 0   | DCD0 switch node - this pin connects to the output inductor.                                                                                       |

| A51      | A47       | DCD0_LX         | 0   | DCD0 switch node - this pin connects to the output inductor.                                                                                       |

| A52      | A48       | DCD0_LX         | 0   | DCD0 switch node - this pin connects to the output inductor.                                                                                       |

| A53      | A49       | COREPWROK       | 0   | Active high soft start done signal.                                                                                                                |

| A54      | B47       | RSMRST_B        | 0   | Resume reset pin is an active low soft start done signal.                                                                                          |

| A55      | A50       | SVID_DIO        | 1/0 | SVID data input and open drain output.                                                                                                             |

| A56      | A51       | SVID_ALERT_B    | 0   | SVID interrupt from PMIC to SOC. Open drain output.                                                                                                |

| B1       | B1        | PLTRST_B        | I + | Platform reset is an active low reset input signal from SoC to PMIC.                                                                               |

| B2       | A2        | PWRBTNIN_B      |     | System power button input (active low). The button must be pressed for greater than 30ms to turn on all the A rails.                               |

| В3       | В3        | PWRBTN_B        | 0   | Power button output signal. It is a level shifted copy of PWRBTNIN_B after the 30ms de-bouncing circuit.                                           |

| B4       | B4        | DCD5_FB         | 1   | Feedback voltage for DCD5. This pin must be connected to the output voltage of the DCD5.                                                           |

| B5       | B5        | DCD5_VIN        | _   | Input voltage for DCD5. Connect a bypass capacitor from this pin to ground.                                                                        |

| B6       | В6        | DCD6_VIN        | Ι   | Input voltage for DCD6. Connect a bypass capacitor from this pin to ground.                                                                        |

| В7       | B7        | VGPIO1          | I   | Supply voltage for GPIO [9] through GPIO [14]. This pin must be connected to 3.3V.                                                                 |

| B8       | A9        | DCD6_FB         | I   | Feedback voltage for DCD6. This pin must be connected to the output voltage of the DCD6.                                                           |

| В9       | В9        | DCD4_FB         | _   | Feedback voltage for DCD4. This pin must be connected to the output voltage of the P9147/P9148.                                                    |

| B10      | B10       | LDO5_FB         | Ι   | Feedback voltage for LDO5. This pin must be connected to the output voltage of the LDO5. This pin is internally connected to LDO5_VO with 180 Ohm. |

| B11      | B11       | EN2             | 0   | Open drain output enable signal.                                                                                                                   |

| B12      | B13       | GPIO[12]/ADC[2] | I   | General purpose input/output 13 or ADC[2] input.                                                                                                   |

| B13      | A15       | GPIO[10]/ADC[0] | I   | General purpose input/output 11 or ADC[0] input.                                                                                                   |

| B14      | A16       | GPIO[9]/VDDQSEL | I   | General purpose input/output 9 or DCD2 output voltage select                                                                                       |

| B15      | B16       | LDO0_VO         | 0   | Linear regulator 0 output terminal.                                                                                                                |

| B16      | B17       | LD01_V0         | 0   | Linear regulator 1 output terminal.                                                                                                                |

| NQG(QFN)    | NHG(GQFN)      | LABEL            | I/O | DESCRIPTION                                                                                                                                                                                                  |

|-------------|----------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B17         | B18            | LDO4_VO          | 0   | Linear regulator 4 output terminal.                                                                                                                                                                          |

| B18         | B19            | LDO5_VIN         | I   | Input supply voltage for source-sink regulator LDO5.                                                                                                                                                         |

| B19         | A22            | LDO6_VO          | 0   | Linear regulator 6 output terminal.                                                                                                                                                                          |

| B20         | B20            | LDO7_VO          | 0   | 1.8V regulator output terminal for DPS control interface and internal biasing.                                                                                                                               |

| B21         | A24            | IRQ              | 0   | Interrupt request output.                                                                                                                                                                                    |

| B22         | B22            | SDWN_B           | 0   | Shutdown warning. In the event of system shutdown, PMIC issues a system shutdown warning to the modem.                                                                                                       |

| B23         | B25            | GPIO[7]/PWM[1]   | -   | General purpose input/output 7 or PWM[1] output control signal                                                                                                                                               |

| B24         | A29            | GPIO[5]/DCD0_DIF | 0   | General purpose input/output 5 or DCD0 regulator digital interface output.                                                                                                                                   |

| B25         | B26            | GPIO[3]/DCD1_DIF | 0   | General purpose input/output 3 or DCD1 regulator digital interface output.                                                                                                                                   |

| B26         | B28            | GPIO[1]/DCD2_DIF | 0   | General purpose input/output 1 or DCD2 regulator digital interface output.                                                                                                                                   |

| B27         | A31            | VGPI00           | Τ   | Input supply voltage for GPIO[0] to GPIO[8]. This pin must be connected to 1.8V voltage rail.                                                                                                                |

| B28         | B30            | DCD2_VIN         | _   | Input voltage for DCD2. Connect two 10µF bypass capacitors from this pin to ground.                                                                                                                          |

| B29         | B31            | DCD2_VIN         | _   | Input voltage for DCD2. Connect two 10µF bypass capacitors from this pin to ground.                                                                                                                          |

| B30         | B32            | DCD2_FB          | T   | Feedback voltage for DCD2. This pin must be connected to the output filter of the regulator.                                                                                                                 |

| B31         | B33            | VCCAPWROK        | 0   | Active high open drain soft start done signal.                                                                                                                                                               |

| B32         | A37            | DRAMPWROK        | 0   | Active high open drain soft start done signal.                                                                                                                                                               |

| B33         | B34            | PROCHOT_B        | 0   | Active low open drain output signal.                                                                                                                                                                         |

| B34         | B35            | THERMTRIP_B      | ) 1 | Active low thermal trip input signal. Catastrophic thermal event indicator to PMIC to shut off all power rails.                                                                                              |

| B35         | B38            | DCD1_GSEN        | - I | DCD1 ground sense pin.                                                                                                                                                                                       |

| B36         | B39            | DCD1_VIN         | 1   | Input voltage for DCD1. Connect two 10µF bypass capacitors from this pin to ground.                                                                                                                          |

| B37         | B40            | DCD1_VIN         | _   | Input voltage for DCD1. Connect two 10µF bypass capacitors from this pin to ground.                                                                                                                          |

| B38         | B41            | DCD1_FB          | Ι   | Feedback voltage for DCD1. This pin must be connected to the output filter of the DCD1.                                                                                                                      |

| B39         | B42            | VSYS             | I   | PMIC input supply voltage. Connect a 2.2µF capacitor from as close this pin to ground as possible.                                                                                                           |

| B40         | B43            | DCD0_FB          | I   | Feedback voltage for DCD0. This pin must be connected to the output filter of the DCD0.                                                                                                                      |

| B41         | B44            | DCD0_VIN         | I   | Input voltage for DCD0. Connect two 10µF bypass capacitors from this pin to ground.                                                                                                                          |

| B42         | B45            | DCD0_VIN         | Ι   | Input voltage for DCD0. Connect two 10µF bypass capacitors from this pin to ground.                                                                                                                          |

| B43         | B46            | DCD0_GSEN        | I   | DCD0 ground sense pin.                                                                                                                                                                                       |

| B44         | B48            | SVID_CLK         | I   | SVID clock input.                                                                                                                                                                                            |

| EXPOSED PAD | EXPOSED<br>PAD | PGND             | I   | Ground. Exposed pad is the connection for current return path, and is also used for thermal dissipation. Connect to PCB ground with sufficient vias to support the returned current and thermal requirement. |

# **FUNCTIONAL DIAGRAM**

Figure 3: Functional Diagram

# **DESCRIPTIONS, SPECIFICATION TABLES & REGISTERS**

# **General Specification**

Table 6: Electrical Characteristics – PMIC VSYS, UVLO, thermal shutdown threshold  $V_{SYS}$ = 5.0V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.

| SYMBOL                | PARAMETER              | CONDITIONS                                     | MIN  | TYP  | MAX  | UNITS |

|-----------------------|------------------------|------------------------------------------------|------|------|------|-------|

| Vsys                  | Input voltage range    |                                                | 3.15 |      | 5.25 | V     |

|                       |                        | Device in G3 (OFF state)                       |      | 7    |      | μA    |

| I <sub>Q</sub> (vsys) | VSYS quiescent current | Device in S4 state, all regulators powered-off |      | 0.75 | 1.1  | mA    |

| Vsys(UVLO) UV         | LIV/LO Horoschoold     | VSYS rising (VSYSREF <sub>R</sub> )            |      | 2.9  |      | V     |

|                       | UVLO threshold         | VSYS falling (VSYSREF <sub>F</sub> )           |      | 2.5  |      | V     |

| T <sub>SDN</sub>      | Thermal shutdown       | Temperature increasing                         | 125  | 132  |      | °C    |

# Linear Regulators LDO0, LDO1, LDO2

Table 7: Electrical Characteristics – LDO0, LDO1, LDO2

$V_{SYS} = 5V$ ,  $V_{IN\_LDO} = 1.8V$ ,  $V_{OUT} = 1.5V$  (default),  $C_{IN} = 10\mu F$ ,  $C_{O} = 2.2\mu F$ ,  $T_{A} = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .

| SYMBOL                                       | PARAMETER                     | CONDITIONS                                            | MIN  | TYP  | MAX   | UNITS |

|----------------------------------------------|-------------------------------|-------------------------------------------------------|------|------|-------|-------|

| V <sub>IN_LDO</sub>                          | Input voltage range           | 40° 10°                                               | 1.0  | 1.8  | 2.0   | V     |

| Vo                                           | Programmable output voltage   |                                                       | 1.0  | 1.5  | 1.65  | V     |

| Ishdn                                        | Shutdown current              | 0 20                                                  |      | 0.5  |       | μΑ    |

| lq                                           | Quiescent current             | No Load                                               |      | 22   |       | μΑ    |

|                                              | Regulation voltage accuracy   |                                                       | -2.0 |      | +2.0  | %     |

| $\Delta V_{\text{OUT}}/\Delta V_{\text{IN}}$ | Line regulation               | ~                                                     |      | 1.0  |       | ppm/V |

| $\Delta V_{ m OUT}/\Delta I_{ m OUT}$        | Load regulation               |                                                       |      | 5.0  |       | μV/mA |

| I <sub>O</sub>                               | Maximum output current        |                                                       | 300  |      |       | mA    |

| Iым                                          | Current limit                 |                                                       | 400  |      |       | mA    |

| V <sub>DROP</sub>                            | Dropout voltage               | I <sub>O</sub> = 300mA                                |      |      | 150   | mV    |

| R <sub>DIS</sub>                             | Output discharge resistance   |                                                       |      | 10   |       | kΩ    |

|                                              |                               | $V_{IN\_LDO} - V_O = 500$ mV, $I_O = 30$ mA           |      |      |       |       |

|                                              | Dower Cupply Dipple           | <200Hz                                                |      | >100 |       |       |

| PSRR                                         | Power Supply Ripple Rejection | 1kHz                                                  |      | 100  |       | dB    |

|                                              |                               | 10kHz                                                 |      | 85   |       |       |

|                                              |                               | 100kHz                                                |      | 55   |       |       |

| e <sub>n</sub>                               | Output noise voltage          | $V_0 = 1.5V$ , $I_0 = 100\mu A$ , BW = 10Hz to 100kHz | 28   |      | μVRMS |       |

| T <sub>SSR</sub>                             | LDO soft-start ramp rate      |                                                       |      | 30   |       | mV/μs |

Table 8: I<sup>2</sup>C Control Register – LDO0, LDO1, LDO2

| Register Name | R/W | D7 | D6       | D5   | D4    | D3 | D2 | D1       | D0      | Initial<br>Value | Address |

|---------------|-----|----|----------|------|-------|----|----|----------|---------|------------------|---------|

| LDO0_CTL      | R/W |    | Reserved |      |       |    |    | LDO0_SEL | LDO0_EN | 0x00             | 0x65    |

| LDO1_CTL      | R/W |    | Reserved |      |       |    |    | LDO1_SEL | LDO1_EN | 0x00             | 0x61    |

| LDO2_CTL      | R/W |    |          | Rese | erved |    |    | LDO2_SEL | LDO2_EN | 0x00             | 0x66    |

| BIT    | Name     | Function                                                                                                               | Default |

|--------|----------|------------------------------------------------------------------------------------------------------------------------|---------|

| D[7:2] | Reserved | Reserved                                                                                                               | 0       |

| D[1]   | LDOx_SEL | ON/OFF select bit  0 = ON/OFF is controlled by configured device sequence.  1 = ON/OFF is controlled by D[0] register. | 0       |

| D[0]   | LDOx_EN  | Enable bit 0 = OFF 1 = ON                                                                                              | 0       |

## Table 9: ON/OFF Select Bit Truth Table – LDO0, LDO1, LDO2

| D[1] | D[0] | Sequencer control | LDO |

|------|------|-------------------|-----|

| 0    | X    | 0                 | OFF |

| 0    | X    | 1/                | ON  |

| 1    | 0    | X                 | OFF |

| 1    | 1    | X                 | ON  |

# Table 10: I<sup>2</sup>C Output Voltage Setting – LDO0, LDO1, LDO2

| Register Name | R/W | D7       | D6       | D5       | D4 | D3                                       | D2                       | D1  | D0   | Initial<br>Value | Address |

|---------------|-----|----------|----------|----------|----|------------------------------------------|--------------------------|-----|------|------------------|---------|

| LDO0_VOUT     | R/W |          | Reserved | 000      |    | Output Voltage Setting (see<br>Table 12) |                          |     |      |                  | 0x12    |

| LDO1_VOUT     | R/W |          | Reserved | <b>V</b> |    |                                          | ltage Settir<br>able 12) |     | OTP  | 0x13             |         |

| LDO2_VOUT     | R/W | Reserved |          |          |    |                                          | ltage Settir<br>able 12) | OTP | 0x14 |                  |         |

## Table 11: I<sup>2</sup>C Sequencing Control Register – LDO0, LDO1, LDO2

| Register<br>Name | R/W | D7   | D6    | D5    | D4   | D3         | D2     | D1  | D0   | Initial<br>Value | Address |

|------------------|-----|------|-------|-------|------|------------|--------|-----|------|------------------|---------|

| LDO0_GRP         | R/W | Rese | erved | LDO0_ | TYPE |            | LD00_0 | OTP | 0xED |                  |         |

| LDO1_GRP         | R/W | Rese | erved | LDO1  | TYPE | LDO1_GROUP |        |     |      | OTP              | 0xEE    |

| LDO2_GRP         | R/W | Rese | erved | LDO2  | TYPE | LDO2_GROUP |        |     |      | OTP              | 0xEF    |

| BIT    | Name       | Function                                                                                                                                                                                                                                            | Default |

|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| D[7:6] | Reserved   | Reserved                                                                                                                                                                                                                                            | 0       |

| D[5:4] | LDOX_TYPE  | Rail Type Select Bit  00 = "A" rail type.  01 = "U" rail type.  10 = "S" rail type.  11 = "SX" rail type.                                                                                                                                           | ОТР     |

| D[3:0] | LDOX_GROUP | Group Delay Bits  0000b = Group 0  0001b = Group 1  0010b = Group 2  0011b = Group 3  0100b = Group 4  0100b = Group 10  1010b = Group 11  1000b = Group 12  1100b = Group 12  1101b = Group 13  0110b = Group 6  1110b = Group 14  0111b = Group 7 | ОТР     |

Table 12: LDO0, LDO1, LDO2 Output Voltage Setting

| Vout        | Decimal | Hex | Binary |

|-------------|---------|-----|--------|

| 1.000       | 0       | 00  | 00000  |

| 1.025       | 1       | 01  | 00001  |

| 1.050       | 2       | 02  | 00010  |

| 1.075       | 3       | 03  | 00011  |

| 1.100       | 4       | 04  | 00100  |

| 1.125       | 5       | 05  | 00101  |

| 1.150       | 6       | 06  | 00110  |

| 1.175       | 7       | 07  | 00111  |

| 1.200       | 8       | 08  | 01000  |

| 1.225       | 9       | 09  | 01001  |

| 1.250       | 10      | 0A  | 01010  |

| 1.275       | 11      | 0B  | 01011  |

| 1.300       | 12      | 0C  | 01100  |

| 1.325       | 13      | 0D  | 01101  |

| 1.350       | 14      | 0E  | 01110  |

| 1.375       | 15      | 0F  | 01111  |

| 1.400       | 16      | 10  | 10000  |

| 1.425       | 17      | 11  | 10001  |

| 1.450       | 18      | 12  | 10010  |

| 1.475       | 19      | 13  | 10011  |

| 1.500       | 20      | 14  | 10100  |

| 1.525       | 21      | 15  | 10101  |

| 1.550       | 22      | 16  | 10110  |

| 1.575       | 23      | 17  | 10111  |

| 1.600       | 24      | 18  | 11000  |

| 1.625       | 25      | 19  | 11001  |

| 1.650       | 26      | 1A  | 11010  |

| Pass switch | ≥27     | ≥1B | ·      |

# Linear Regulators LDO3, LDO4

Table 13: Electrical Characteristics - LDO3, LDO4

$V_{IN\_LDO}$  = 1.8V,  $V_{OUT}$  = 1.2V (default),  $C_{IN}$  = 10 $\mu$ F,  $C_{O}$  = 1.0 $\mu$ F,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_{A}$  = +25°C.

| SYMBOL                         | PARAMETER                     | CONDITIONS                                                | MIN  | TYP  | MAX  | UNITS |

|--------------------------------|-------------------------------|-----------------------------------------------------------|------|------|------|-------|

| V <sub>IN_LDO</sub>            | Input voltage range           |                                                           | 1.0  | 1.8  | 2.0  | V     |

| Vo                             | Output voltage range          |                                                           | 1.0  | 1.2  | 1.65 | V     |

| Ishdn                          | Shutdown current              |                                                           |      | 0.5  |      | μΑ    |

| IQ                             | Quiescent current             | No Load                                                   |      | 20   |      | μΑ    |

|                                | Regulation voltage accuracy   |                                                           | -2.0 |      | +2.0 | %     |

| $\Delta V_{OUT}/\Delta V_{IN}$ | Line regulation               |                                                           |      | 1.0  |      | ppm/V |

| $\Delta V$ оυт $/\Delta I$ ουτ | Load regulation               |                                                           |      | 19   |      | μV/mA |

| lo                             | Maximum output current        |                                                           | 50   |      |      | mA    |

| I <sub>LIM</sub>               | Current limit                 |                                                           | 60   |      |      | mA    |

| V <sub>DROP</sub>              | Dropout voltage               | I <sub>O</sub> = 50mA                                     |      |      | 100  | mV    |

| R <sub>DIS</sub>               | Output discharge resistance   |                                                           |      | 10   |      | kΩ    |

|                                |                               | $V_{IN\_LDO} - V_O = 500 \text{mV}, I_O = 10 \text{mA}$   |      |      |      |       |

|                                |                               | < 200Hz                                                   |      | >100 |      |       |

| PSRR                           | Power Supply Ripple Rejection | 1kHz                                                      |      | 100  |      | dB    |

|                                |                               | 10kHz                                                     |      | 85   |      |       |

|                                |                               | 100kHz                                                    | 55   |      |      | ]     |

| e <sub>n</sub>                 | Output noise voltage          | $V_0 = 1.2V$ , $I_0 = 100\mu A$ , $BW = 10Hz$ to $100kHz$ | 28   |      |      | μVRMS |

| T <sub>SSR</sub>               | LDO soft-start ramp rate      | 0.                                                        |      | 30   |      | mV/μs |

## Table 14: I<sup>2</sup>C Control Register – LDO3, LDO4

| Register Name | R/W | D7 | D6       | D5 | D4 | D3 | D2 | D1 | D0      | Initial<br>Value | Address |

|---------------|-----|----|----------|----|----|----|----|----|---------|------------------|---------|

| LDO3_CTL      | R/W |    | Reserved |    |    |    |    |    | LDO3_EN | 0x00             | 0x5E    |

| LDO4_CTL      | R/W |    | Reserved |    |    |    |    |    | LDO4_EN | 0x00             | 0x60    |

| BIT    | Name     | Function                                                                                                               | Default |

|--------|----------|------------------------------------------------------------------------------------------------------------------------|---------|

| D[7:2] | Reserved | Reserved                                                                                                               | 0       |

| D[1]   | LDOx_SEL | ON/OFF select bit  0 = ON/OFF is controlled by configured device sequence.  1 = ON/OFF is controlled by D[0] register. | 0       |

| D[0]   | LDOx_EN  | Enable bit  0 = OFF  1 = ON                                                                                            | 0       |

Table 15: Select Bit Truth Table - LDO3, LDO4

| D[1] | D[0] | Sequencer control | LDO |

|------|------|-------------------|-----|

| 0    | X    | 0                 | ON  |

| 0    | X    | 1                 | OFF |

| 1    | 0    | X                 | OFF |

| 1    | 1    | X                 | ON  |

## Table 16: I2C Output Voltage Setting - LDO3, LDO4

| Register Name | R/W | D7       | D6       | D5 | D4                                    | D3          | D2  | D1   | D0 | Initial<br>Value | Address |

|---------------|-----|----------|----------|----|---------------------------------------|-------------|-----|------|----|------------------|---------|

| LDO3_VOUT     | R/W |          | Reserved |    |                                       | tput Voltag | OTP | 0x16 |    |                  |         |

| LDO4_VOUT     | R/W | Reserved |          |    | Output Voltage Setting (see Table 18) |             |     |      |    | OTP              | 0x17    |

## Table 17: I<sup>2</sup>C Sequencing Control Register – LDO3, LDO4

| Register Name | R/W | D7   | D6       | D5   | D4        | D3 | D2     | D1  | D0   | Initial<br>Value | Address |

|---------------|-----|------|----------|------|-----------|----|--------|-----|------|------------------|---------|

| LDO3_GRP      | R/W | Rese | Reserved |      | LDO3_TYPE |    | LDO3_0 | OTP | 0xF0 |                  |         |

| LDO4_GRP      | R/W | Rese | erved    | LDO4 | _TYPE     | R  | LDO4_0 | OTP | 0xF1 |                  |         |

| BIT    | Name       | Function                                                                                                                                                                                                                                               | Default |

|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| D[7:6] | Reserved   | Reserved                                                                                                                                                                                                                                               | 0       |

| D[5:4] | LDOx_TYPE  | Rail Type Select Bit  00 = "A" rail type.  01 = "U" rail type.  10 = "S" rail type.  11 = "SX" rail type.                                                                                                                                              | ОТР     |

| D[3:0] | LDOx_GROUP | Group Delay Bits  0000b = Group 0 0001b = Group 1 1001b = Group 9 0010b = Group 2 1010b = Group 10 0011b = Group 3 1010b = Group 11 0100b = Group 4 1100b = Group 12 0101b = Group 5 1101b = Group 13 0110b = Group 6 1110b = Group 14 0111b = Group 7 | ОТР     |

## Table 18: LDO3, LDO4 Output Voltage Setting

| Vout  | Decimal | Hex | Binary |

|-------|---------|-----|--------|

| 1.000 | 0       | 00  | 000000 |

| 1.025 | 1       | 01  | 000001 |

| 1.050 | 2       | 02  | 000010 |

| 1.075 | 3       | 03  | 000011 |

| 1.100 | 4       | 04  | 000100 |

| 1.125 | 5       | 05  | 000101 |

| 1.150 | 6       | 06  | 000110 |

| 1.175 | 7       | 07  | 000111 |

| Vout  | Decimal   | Hex | Binary |

|-------|-----------|-----|--------|

| 1.200 | 8         | 08  | 001000 |

| 1.225 | 9         | 09  | 001001 |

| 1.250 | 10        | 0A  | 001010 |

| 1.275 | 11        | 0B  | 001011 |

| 1.300 | 12        | 0C  | 001100 |

| 1.325 | 13        | 0D  | 001101 |

| 1.350 | 14        | 0E  | 001110 |

| 1.375 | 15        | 0F  | 001111 |

| 1.400 | 16        | 10  | 010000 |

| 1.425 | 17        | 11  | 010001 |

| 1.450 | 18        | 12  | 010010 |

| 1.475 | 19        | 13  | 010011 |

| 1.500 | 20        | 14  | 010100 |

| 1.525 | 21        | 15  | 010101 |

| 1.550 | 22        | 16  | 010110 |

| 1.575 | 23        | 17  | 010111 |

| 1.600 | 24        | 18  | 011000 |

| 1.625 | 25        | 19  | 011001 |

| 1.650 | 26        | 1A  | 011010 |

|       | Collicing |     |        |

# **Linear Regulator LDO5**

LDO5 is a source-sink linear regulator capable of delivering load currents as high as  $\pm 550$ mA. The output voltage is designed to regulate at  $V_{IN\_LDO5}/2$ . The regulator is controlled either through the sequencing state machine or by  $I^2C$ .

### Table 19: Electrical Characteristics - LDO5

$V_{\text{IN}\_LD05}$  = 1.24V,  $V_{\text{OUT}}$  = 0.620V (default),  $C_{\text{IN}}$  = 22 $\mu$ F,  $C_{\text{O}}$  = 22 $\mu$ F,  $T_{\text{A}}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_{\text{A}}$  = +25°C.

| SYMBOL                | PARAMETER                     | CONDITIONS                          | MIN  | TYP        | MAX  | UNITS |

|-----------------------|-------------------------------|-------------------------------------|------|------------|------|-------|

| V <sub>IN_LDO5</sub>  | Input voltage range           |                                     | 1.20 | 1.24       | 1.50 | V     |

| V <sub>O_LDO5</sub>   | Output voltage                |                                     |      | VIN_LDO5/2 |      | V     |

| I <sub>SHDN</sub>     | Shutdown current              |                                     |      | 1          |      | μA    |

| la                    | Quiescent current             | No Load                             |      | 60         | 95   | μA    |

|                       | Regulation voltage accuracy   | -550mA ≤ I <sub>LOAD</sub> ≤ +550mA | -5   |            | +5   | %     |

| I <sub>(source)</sub> | Maximum source output current |                                     | 550  |            |      | mA    |

| I <sub>(sink)</sub>   | Maximum sink output current   |                                     | 550  |            |      | mA    |

| Rois                  | Output discharge resistance   |                                     |      | 80         |      | Ω     |

## Table 20: I<sup>2</sup>C Control Register – LDO5

| Register Name | R/W | D7 | D6       | D5 | D4 | D3 | D2 | D1 | D0      | Initial<br>Value | Address |

|---------------|-----|----|----------|----|----|----|----|----|---------|------------------|---------|

| LDO5_CTL      | R/W |    | Reserved |    |    |    |    |    | LDO5_EN | 0x00             | 0x58    |

| BIT    | Name     | Function                                                                                                             | Default |

|--------|----------|----------------------------------------------------------------------------------------------------------------------|---------|

| D[7:2] | Reserved | Reserved                                                                                                             | 0       |

| D[1]   | LDO5_SEL | ON/OFF select bit 0 = ON/OFF is controlled by configured device sequence. 1 = ON/OFF is controlled by D[0] register. | 0       |

| D[0]   | LDO5_EN  | Enable bit  0 = OFF  1 = ON                                                                                          | 0       |

### Table 21: Select Bit Truth Table - LDO5

| D[1] | D[0] | Sequencer control | LDO5 |

|------|------|-------------------|------|

| 0    | X    | 0                 | OFF  |

| 0    | X    | 1                 | ON   |

| 1    | 0    | X                 | OFF  |

| 1    | 1    | X                 | ON   |

Table 22: I<sup>2</sup>C Sequencing Control – LDO5

| Register Name | R/W | D7   | D6    | D5        | D4 | D3 | D2    | D1    | D0 | Initial<br>Value | Address |

|---------------|-----|------|-------|-----------|----|----|-------|-------|----|------------------|---------|

| LDO5_GRP      | R/W | Rese | erved | LDO5_TYPE |    |    | LDO5_ | GROUP |    | OTP              | 0xF2    |

| BIT    | Name       | Function                                                                                                                                                                                                                            | Default |

|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| D[7:6] | Reserved   | Reserved                                                                                                                                                                                                                            | 0       |

| D[5:4] | LDO5_TYPE  | Rail Type Select Bit  00 = "A" rail type.  01 = "U" rail type.  10 = "S" rail type.  11 = "SX" rail type.                                                                                                                           | ОТР     |

| D[3:0] | LDO5_GROUP | Group Delay Bits  0000b = Group 0  0001b = Group 1  0010b = Group 2  0011b = Group 3  0100b = Group 10  1010b = Group 11  1010b = Group 11  1100b = Group 12  1101b = Group 13  1101b = Group 13  1110b = Group 14  0111b = Group 7 | ОТР     |

|        |            | Councillo et 223,                                                                                                                                                                                                                   |         |

# **Linear Regulator LD06**

Table 23: Electrical Characteristics - LDO6

$V_{SYS}$ = 5.0V,  $V_{OUT}$  = 3.3V,  $C_0$  = 1 $\mu$ F,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.

| SYMBOL                                       | PARAMETER                         | CONDITIONS                                                            | MIN  | TYP   | MAX  | UNITS |  |

|----------------------------------------------|-----------------------------------|-----------------------------------------------------------------------|------|-------|------|-------|--|

| Vsys                                         | Input voltage range               |                                                                       | 3.15 | 5.0   | 5.25 | V     |  |

| Vo                                           | Output voltage range              |                                                                       | 1.0  | 3.3   | 3.55 | V     |  |

| I <sub>SHDN</sub>                            | Shutdown current                  |                                                                       |      | 0.5   |      | μΑ    |  |

| lq                                           | Quiescent current                 | No Load                                                               | _    | 20    |      | μΑ    |  |

|                                              | Regulation voltage accuracy       |                                                                       | -2   |       | +2   | %     |  |

| $\Delta V_{\text{OUT}}/\Delta V_{\text{IN}}$ | Line regulation                   |                                                                       |      | 1     |      | ppm/V |  |

| $\Delta V_{OUT}/\Delta I_{OUT}$              | Load regulation                   |                                                                       |      | 40    |      | μV/mA |  |

| lo                                           | Maximum output current            |                                                                       | 100  |       |      | mA    |  |

| I <sub>LIM</sub>                             | Current limit                     |                                                                       | 120  |       |      | mA    |  |

| V <sub>DROP</sub>                            | Dropout voltage                   | I <sub>O</sub> = 50mA                                                 |      |       | 125  | mV    |  |

| R <sub>DIS</sub>                             | Output discharge resistance       |                                                                       |      | 10    |      | kΩ    |  |

|                                              |                                   | $V_{SYS} - V_0 = 1V$ , $I_0 = 30$ mA                                  | (9)  |       |      |       |  |

|                                              | Power Supply Ripple               | < 200Hz                                                               |      | > 120 |      |       |  |

| PSRR                                         | Rejection <sup>1</sup>            | 1kHz                                                                  |      | 120   |      | dB    |  |

|                                              | ,,,,,,,                           | 10kHz                                                                 |      | 95    |      |       |  |

|                                              |                                   | 100kHz                                                                |      | 57    |      | ]     |  |

| <b>e</b> n                                   | Output noise voltage <sup>1</sup> | V <sub>0</sub> = 3.3V, I <sub>0</sub> = 100μA,<br>BW = 10Hz to 100kHz |      | 28    |      | μVRMS |  |

| T <sub>SSR</sub>                             | LDO soft-start ramp rate          | 0, 0,                                                                 |      | 32    | •    | mV/μs |  |

# Table 24: I<sup>2</sup>C Control Register – LDO6

| Register Name | R/W | D7 | D6       | D5 | D4 | D3 | D2 | D1 | D0      | Initial<br>Value | Address |

|---------------|-----|----|----------|----|----|----|----|----|---------|------------------|---------|

| LDO6_CTL      | R/W |    | Reserved |    |    |    |    |    | LDO6_EN | 0x00             | 0x6A    |

|   | BIT    | Name     | Function                                                                                                               | Default |

|---|--------|----------|------------------------------------------------------------------------------------------------------------------------|---------|

|   | D[7:2] | Reserved | Reserved                                                                                                               | 0       |

| - | D[1]   | LDO6_SEL | ON/OFF select bit  0 = ON/OFF is controlled by configured device sequence.  1 = ON/OFF is controlled by D[0] register. | 0       |

| - | D[0]   | LDO6_EN  | Control bit 0 = OFF 1 = ON                                                                                             | 0       |

Table 25: Select Bit Truth Table - LDO6

| D[1] | D[0] | Sequencer control | LDO6 |

|------|------|-------------------|------|

| 0    | Х    | 0                 | ON   |

| 0    | Х    | 1                 | OFF  |

| 1    | 0    | Х                 | OFF  |

| 1    | 1    | Х                 | ON   |

## Table 26: I<sup>2</sup>C Output Voltage Setting – LDO6

| Table 20. I-C Output voltage Setting - LDO0 |     |       |     |    |      |      |    |    |    |                  |         |

|---------------------------------------------|-----|-------|-----|----|------|------|----|----|----|------------------|---------|

| Register Name                               | R/W | D7    | D6  | D5 | D4   | D3   | D2 | D1 | D0 | Initial<br>Value | Address |

| LDO6_VOUT                                   | R/W | Reser | ved |    | 0x00 | 0x18 |    |    |    |                  |         |

# Table 27: I<sup>2</sup>C Sequencing Control – LDO6

| Register Name | R/W | D7   | D6    | D5    | D4   | D3 | D2     | D1    | D0 | Initial<br>Value | Address |

|---------------|-----|------|-------|-------|------|----|--------|-------|----|------------------|---------|

| LDO6_GRP      | R/W | Rese | erved | LD06_ | TYPE |    | LD06_0 | GROUP | -  | OTP              | 0xF3    |

| BIT    | Name       | Function                                                                                                                                                                                                                                                                             | Default |

|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| D[7:6] | Reserved   | Reserved                                                                                                                                                                                                                                                                             | 0       |

| D[5:4] | LDO6_TYPE  | Rail Type Select Bit  00 = "A" rail type.  01 = "U" rail type.  10 = "S" rail type.  11 = "SX" rail type.                                                                                                                                                                            | ОТР     |

| D[3:0] | LDO6_GROUP | Group Delay Bits  0000b = Group 0  1000b = Group 8  0001b = Group 1  1001b = Group 9  0010b = Group 2  1010b = Group 10  0011b = Group 3  1010b = Group 11  0100b = Group 4  1100b = Group 12  0101b = Group 5  1101b = Group 13  0110b = Group 6  1110b = Group 14  0111b = Group 7 | ОТР     |

## Table 28: LDO6 Output Voltage Setting

| V <sub>OUT</sub> | Decimal | Hex | Binary |

|------------------|---------|-----|--------|

| 1.00             | 0       | 00  | 000000 |

| 1.05             | 1       | 01  | 000001 |

| 1.10             | 2       | 02  | 000010 |

| 1.15             | 3       | 03  | 000011 |

| 1.20             | 4       | 04  | 000100 |

| 1.25             | 5       | 05  | 000101 |

| 1.30             | 6       | 06  | 000110 |

| 1.35             | 7       | 07  | 000111 |

| 1.40             | 8       | 08  | 001000 |

| Vout | Decimal | Hex | Binary |

|------|---------|-----|--------|

| 1.45 | 9       | 09  | 001001 |

| 1.50 | 10      | 0A  | 001010 |

| 1.55 | 11      | 0B  | 001011 |

| 1.60 | 12      | 0C  | 001100 |

| 1.65 | 13      | 0D  | 001101 |

| 1.70 | 14      | 0E  | 001110 |

| 1.75 | 15      | 0F  | 001111 |

| 1.80 | 16      | 10  | 010000 |

| 1.85 | 17      | 11  | 010001 |

| 1.90 | 18      | 12  | 010010 |

| 1.95 | 19      | 13  | 010011 |

| 2.00 | 20      | 14  | 010100 |

| 2.05 | 21      | 15  | 010101 |

| 2.10 | 22      | 16  | 010110 |

| 2.15 | 23      | 17  | 010111 |

| 2.20 | 24      | 18  | 011000 |

| 2.25 | 25      | 19  | 011001 |

| 2.30 | 26      | 1A  | 011010 |

| 2.35 | 27      | 1B  | 011011 |

| 2.40 | 28      | 1C  | 011100 |

| 2.45 | 29      | 1D  | 011101 |

| 2.50 | 30      | 1E  | 011110 |

| 2.55 | 31      | 1F  | 011111 |

| 2.60 | 32      | 20  | 100000 |

| 2.65 | 33      | 21  | 100001 |

| 2.70 | 34      | 22  | 100010 |

| 2.75 | 35      | 23  | 100011 |

| 2.80 | 36      | 24  | 100100 |

| 2.85 | 37      | 25  | 100101 |

| 2.90 | 38      | 26  | 100110 |

| 2.95 | 39      | 27  | 100111 |

| 3.00 | 40      | 28  | 101000 |

| 3.05 | 41      | 29  | 101001 |

| 3.10 | 42      | 2A  | 101010 |

| 3.15 | 43      | 2B  | 101011 |

| 3.20 | 44      | 2C  | 101100 |

| 3.25 | 45      | 2D  | 101101 |

| 3.30 | 46      | 2E  | 101110 |

| 3.35 | 47      | 2F  | 101111 |

| 3.40 | 48      | 30  | 110000 |

| 3.45 | 49      | 31  | 110001 |

| 3.50 | 50      | 32  | 110010 |

| 3.55 | 51      | 33  | 110011 |

| 3.60 | 52      | 34  | 110100 |

| 3.65 | 53      | 35  | 110101 |

| 3.70 | 54      | 36  | 110110 |

| 3.75 | 55      | 37  | 110111 |

# **Linear Regulator LD07**

LDO7 is an always-on LDO, mainly for supplying the 1.8V rated GPIO[8:0] through the VGPIO0 input. LDO7 also supplies the DIF/DIO interfaces for DCD3 and DCD4, MODEM\_OFF\_B, SDWN\_B, PWRBTN\_B, and IRQ output buffers. The LDO can also be used for general purposes, as long as the total output current is limited below 100mA.

LDO is enabled once the PMIC enters S4 state und remains enabled until the PMIC powers down to G3 state.

Table 29: Electrical Characteristics – LDO7

$V_{SYS}$ = 5.0V,  $V_{OUT}$  = 1.8V,  $C_O$  = 1 $\mu$ F,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.

| SYMBOL                         | PARAMETER                                     | CONDITIONS                                                            | MIN | TYP   | MAX | UNITS |

|--------------------------------|-----------------------------------------------|-----------------------------------------------------------------------|-----|-------|-----|-------|

| Vo                             | Output voltage range                          |                                                                       |     | 1.8   |     | V     |

| Ishdn                          | Shutdown current                              | _                                                                     |     | 0.5   |     | μA    |

| IQ                             | Quiescent current                             | No Load                                                               |     | 20    |     | μA    |

|                                | Regulation voltage accuracy                   |                                                                       | -2  |       | +2  | %     |

| $\Delta V_{OUT}/\Delta V_{IN}$ | Line regulation                               |                                                                       |     | 1     |     | ppm/V |

| $\Delta V$ оυτ $/\Delta I$ ουτ | Load regulation                               |                                                                       |     | 40    |     | μV/mA |

| lo                             | Maximum output current                        |                                                                       | 100 |       |     | mA    |

| I <sub>LIM</sub>               | Current limit                                 | 4 6:                                                                  | 120 |       |     | mA    |

| $V_{DROP}$                     | Dropout voltage                               | I <sub>O</sub> = 50mA                                                 |     |       | 125 | mV    |