## RTKA788152DE0000BU

RTKA788152DE0000BU, the RS-485 evaluation board, allows you to evaluate the half-duplex transceivers of the RAA78815x family of RS-485 transceivers.

## Specifications

- 4.5V to 5.5V Supply Voltage

- 115kbps Half-Duplex Transceiver RAA788152

## Features

- Single 115kbps Half-Duplex Transceiver

- RAA788152 (115kbps version currently installed) can be unsoldered and replaced by RAA788155 (1Mbps version) or RAA788158 (20Mbps version)

- Place holders for fail-safe biasing resistors

- Configuration jumpers to operate the transceiver as transmitter or receiver, or as a transmitter with loopback

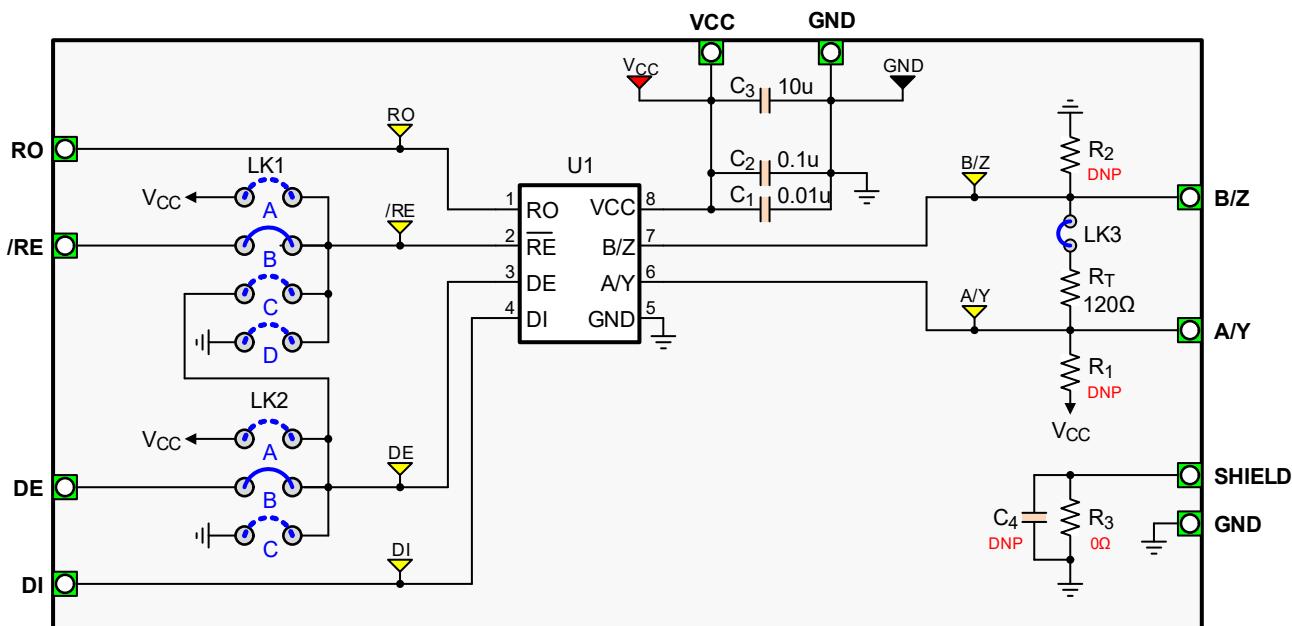

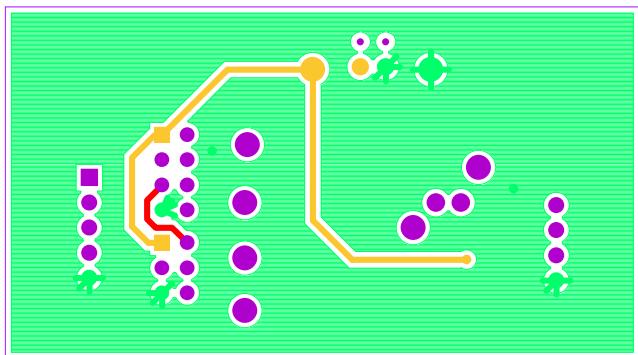

Figure 1. Block Diagram

## Contents

|                                            |           |

|--------------------------------------------|-----------|

| <b>1. Functional Description</b> .....     | <b>3</b>  |

| 1.1 Operational Characteristics .....      | 3         |

| 1.1.1 Driver Operation .....               | 3         |

| 1.1.2 Receiver Operation .....             | 3         |

| 1.2 Bus and Receiver Output Voltages ..... | 4         |

| 1.2.1 Set Up .....                         | 4         |

| 1.2.2 Measurement Graphs .....             | 5         |

| <b>2. Board Design</b> .....               | <b>7</b>  |

| 2.1 Schematic Diagrams .....               | 8         |

| 2.2 Bill of Materials .....                | 8         |

| 2.3 Board Layout .....                     | 9         |

| <b>3. Ordering Information</b> .....       | <b>10</b> |

| <b>4. Revision History</b> .....           | <b>10</b> |

# 1. Functional Description

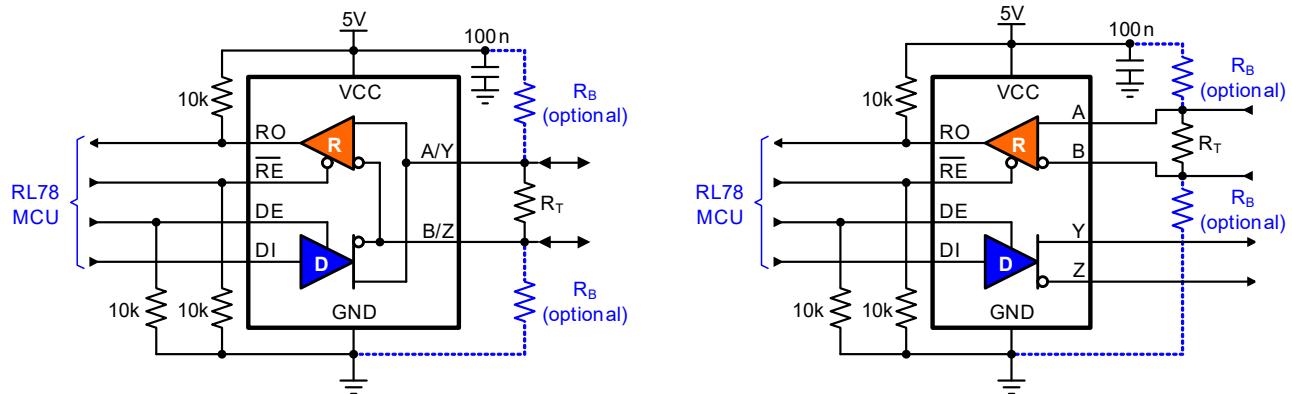

Figure 2. Typical Operating Circuits of Half-Duplex and Full-Duplex Transceivers

## 1.1 Operational Characteristics

### 1.1.1 Driver Operation

A logic high at the driver enable pin (DE) activates the driver and causes the differential driver outputs (Y and Z) to follow the logic states at the data input (DI). A logic high at DI causes Y to turn high and Z to turn low. In this case, the differential output voltage, defined as  $V_{OD} = V_Y - V_Z$ , is positive. A logic low at DI reverses the output states, turning Y low and Z high, therefore, making  $V_{OD}$  negative. A logic low at DE disables the driver, making Y and Z high-impedance. In this condition, the logic state at DI is irrelevant. To ensure the driver remains disabled after device power-up, Renesas recommends connecting DE through a 1k $\Omega$  to 10k $\Omega$  pull-down resistor to ground.

Table 1. Driver Truth Table

| Inputs |    |    | Outputs |   | Function                                                        |

|--------|----|----|---------|---|-----------------------------------------------------------------|

| RE     | DE | DI | Y       | Z |                                                                 |

| X      | H  | H  | H       | L | Actively drives bus high                                        |

| X      | H  | L  | L       | H | Actively drives bus low                                         |

| L      | L  | X  | Z       | Z | Driver disabled, outputs high-impedance                         |

| H      | L  | X  | Z       | Z | Shutdown mode: driver and receiver disabled for more than 600ns |

### 1.1.2 Receiver Operation

A logic low at the receiver enable pin ( $\overline{RE}$ ) activates the receiver and causes its output (RO) to follow the bus voltage at the differential receiver inputs (A and B); the bus voltage is defined as  $V_{AB} = V_A - V_B$ . For  $V_{AB} \geq -0.05V$ , RO turns high, and for  $V_{AB} \leq -0.2V$ , RO turns low. For input voltages between -50mV and -200mV, the state of RO is undetermined, and therefore can be high or low. A logic high at  $\overline{RE}$  disables the receiver, making RO high-impedance. In this condition, the polarity and magnitude of the input voltage is irrelevant. To ensure the receiver output remains high when the receiver is disabled, Renesas recommends connecting RO, using a 1k $\Omega$  to 10k $\Omega$  pull-up resistor to VCC. To enable the receiver to immediately monitor the bus traffic after device power-up, connect  $\overline{RE}$  through a 1k $\Omega$  to 10k $\Omega$  pull-down resistor to ground.

Table 2. Receiver Truth Table

| Inputs |    |                          | Outputs      | Function                                                        |

|--------|----|--------------------------|--------------|-----------------------------------------------------------------|

| RE     | DE | A-B                      | RO           |                                                                 |

| L      | X  | $V_{AB} \geq -0.05V$     | H            | RO is data-driven high                                          |

| L      | X  | $-0.05 > V_{AB} > -0.2V$ | Undetermined | Actively drives bus low                                         |

| L      | X  | $V_{AB} \leq -0.02$      | L            | RO is data-driven low                                           |

| L      | X  | Inputs Open/Shorted      | H            | RO is failsafe-high                                             |

| H      | H  | X                        | Z            | Receiver disabled, RO is high-impedance                         |

| H      | L  | X                        | Z            | Shutdown mode: driver and receiver disabled for more than 600ns |

## 1.2 Bus and Receiver Output Voltages

### 1.2.1 Set Up

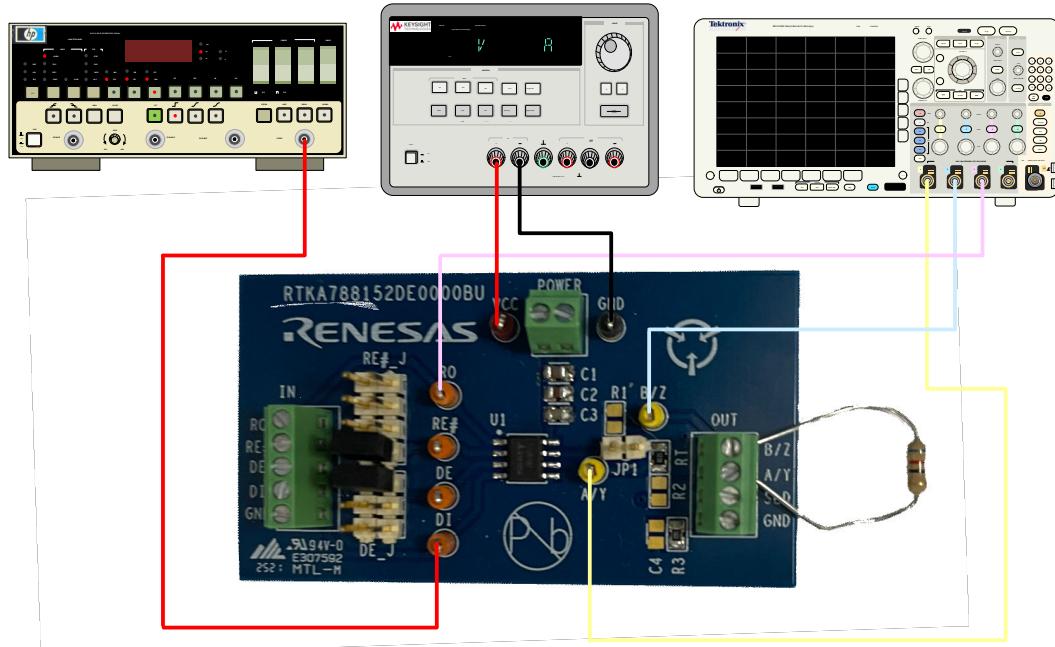

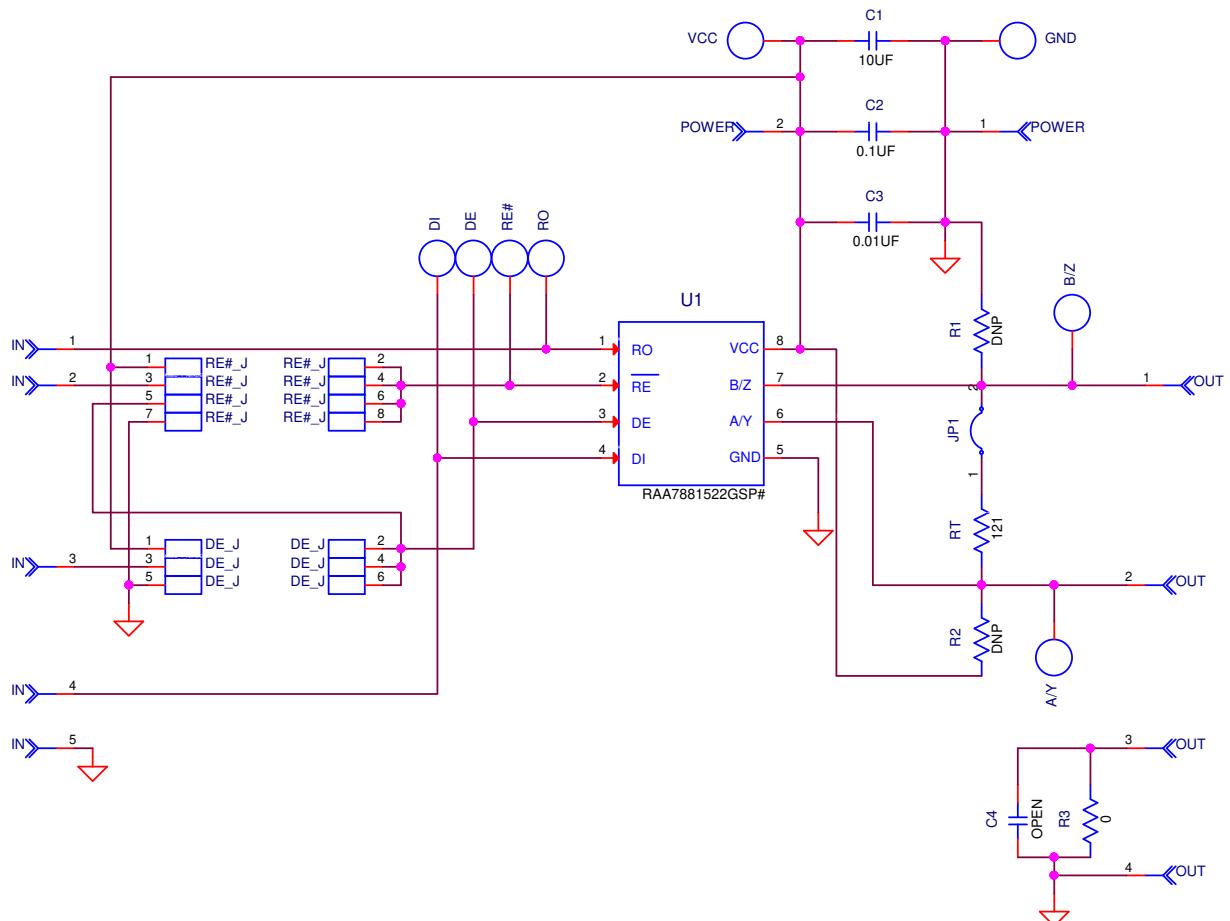

Before connecting measurement equipment, set up the evaluation board and make sure to remove the JP1 socket, which is a jumper connection between two output channels A/Y and B/Z. Removal of JP1 socket allows for measurement of output voltage across driver outputs. Follow the schematic diagram to enable driver by placing sockets to connect DE\_J positions 1 and 2. Enable the receiver by placing the socket to connect RE#\_J positions 7 and 8. Placing a socket between positions 1 and 2 connects the Driver Enable function to  $V_{CC}$  and activates the driver. Otherwise, placing a socket between positions 7 and 8 connects the Receiver Enable function to ground, and because this function is inverted, the receiver is activated. To ensure there is voltage across the bus, attach the load resistor of  $60\Omega$  over the A/Y and B/Z channels. Without this resistive load, the bus is an open circuit. Therefore, no voltage reading would be across the bus.

Attach  $V_{CC}$  to the power supply and set the voltage to  $5V_{DC}$ . Attach the Oscilloscope channel 1 and channel 2 probes to the A/Y and B/Z channels accordingly for bus voltage reading. For channel 3, attach to RO for receiver output voltage reading. Connect the pulse generator to driver input (DI) and set it up for square wave function.

Figure 3. Setup for Bus and Receiver Output Voltage Measurement with Oscilloscope, Power Supply, and Function Generator

## 1.2.2 Measurement Graphs

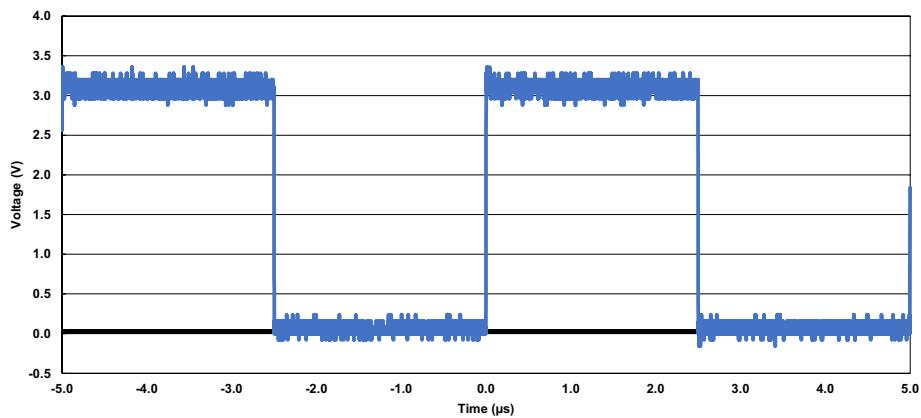

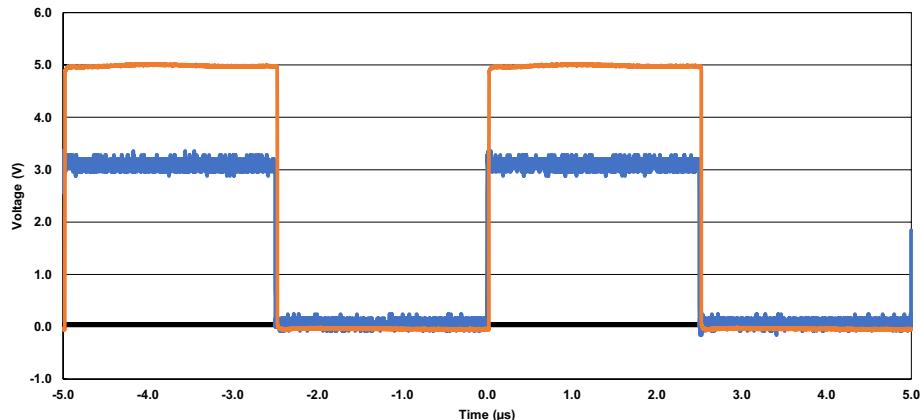

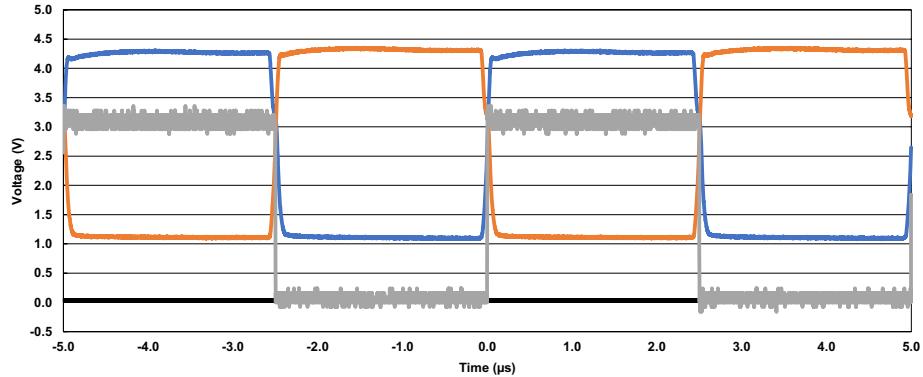

Figure 4. Driver Input Voltage vs Time

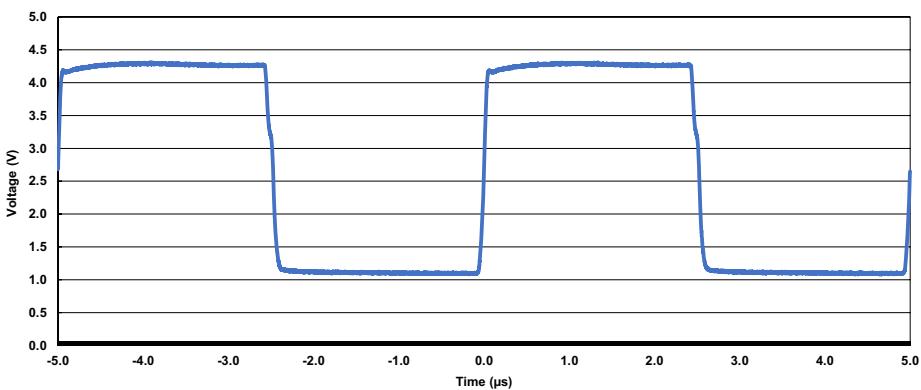

Figure 5. A/Y Channel Output Voltage vs Time

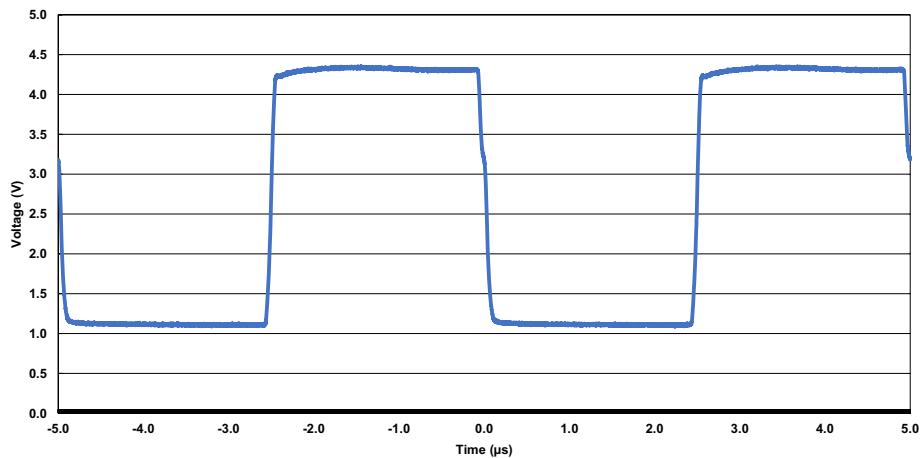

Figure 6. B/Z Channel Output Voltage vs Time

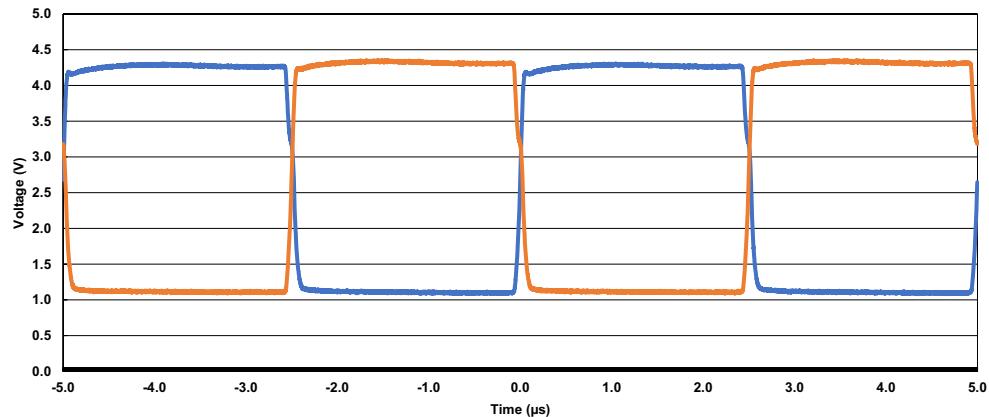

Figure 7. Bus Output Voltages vs Time

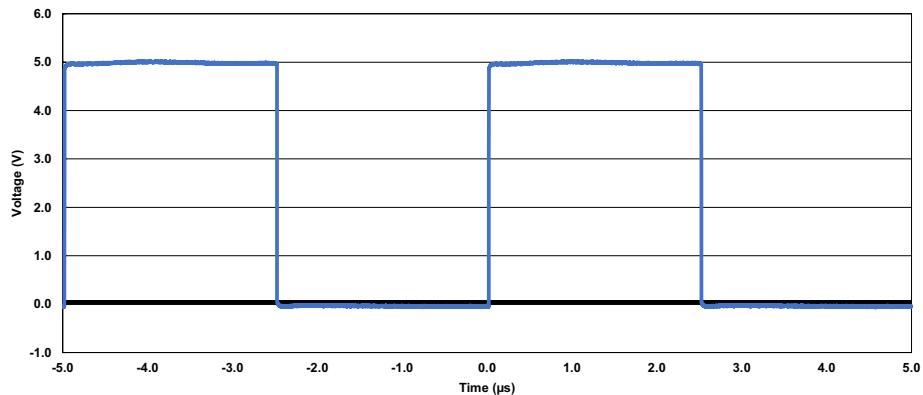

Figure 8. Receiver Output Voltage vs Time

Figure 9. Driver Input Voltage vs Receiver Output Voltage

Figure 10. Bus Output Voltage vs Receiver Output Voltage

## 2. Board Design

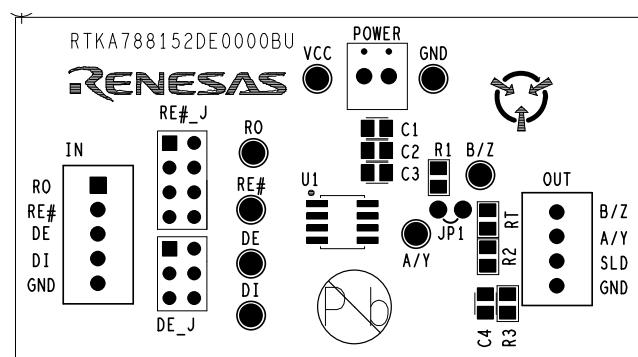

Figure 11. RTKA788152DE0000BU Evaluation Board (Top)

## 2.1 Schematic Diagrams

Figure 12. RTKA788152DE0000BU Schematic

## 2.2 Bill of Materials

| Qty | Reference Designator | Description                                       | Manufacturer | Manufacturer Part Number |

|-----|----------------------|---------------------------------------------------|--------------|--------------------------|

| 1   | POWER                | 2 Position at 100 Mil Micro-Pitch Terminal Block  | Phoenix      | 1725656                  |

| 1   | OUT                  | 4 Position at 100 Mil Micro-Pitch Terminal Block  | Phoenix      | 1725672                  |

| 1   | IN                   | In-line 5 pins x 0.1 inch 6A Terminal Block       | Phoenix      | 1725685                  |

| 1   | VCC                  | Miniature Red Test Point 0.100 Pad 0.040 Thole    | Keystone     | 5000                     |

| 1   | GND                  | Miniature Black Test Point 0.100 Pad 0.040 Thole  | Keystone     | 5001                     |

| 4   | DE, DI, RO, RE#      | Miniature Orange Test Point 0.100 Pad 0.040 Thole | Keystone     | 5003                     |

| 2   | A/Y, B/Z             | Miniature Yellow Test Point 0.100 Pad 0.040 Thole | Keystone     | 5004                     |

| 1   | DE_J                 | Dual Row Vertical PCB Connector                   | Molex        | 90151-3X06               |

| 1   | RE#_J                | Dual Row Vertical PCB Connector                   | Molex        | 90151-3X08               |

| Qty | Reference Designator | Description                                | Manufacturer        | Manufacturer Part Number |

|-----|----------------------|--------------------------------------------|---------------------|--------------------------|

| 1   | C1                   | Ceramic CAP                                | Murata              | GRM21BR61E106MA73        |

| 1   | C3                   | Multilayer Cap                             | Various             | Generic                  |

| 1   | C2                   | Multilayer Cap                             | Various             | Generic                  |

| 1   | C4                   | Multilayer Cap                             | Various             | Generic                  |

| 2   | R1, R2               | Metal Film Chip Resistor (Do Not Populate) | Various             | Generic                  |

| 1   | R3                   | Thick Film Chip Resistor                   | Various             | Generic                  |

| 1   | RT                   | Thick Film Chip Resistor                   | Various             | Generic                  |

| 1   | JP1                  | Two Pin Jumper                             | Various             | Generic                  |

| 1   | U1                   | RS-485 Transceiver                         | Renesas Electronics | RAA7881522GSP#           |

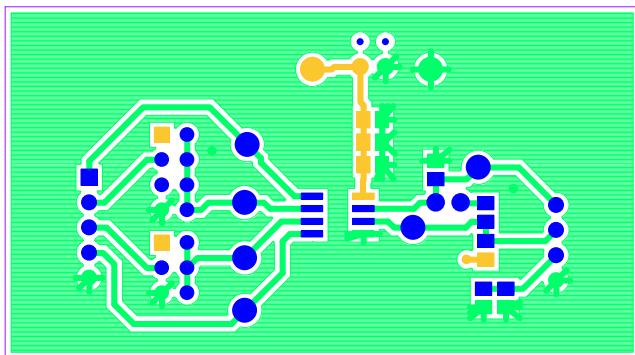

## 2.3 Board Layout

Figure 13. Top Layer

Figure 14. Bottom Layer

Figure 15. Top Silkscreen

### 3. Ordering Information

| Part Number        | Description                |

|--------------------|----------------------------|

| RTKA788152DE0000BU | RAA788152 Evaluation Board |

### 4. Revision History

| Revision | Date        | Description     |

|----------|-------------|-----------------|

| 1.00     | Oct 6, 2021 | Initial release |

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

[www.renesas.com/contact/](http://www.renesas.com/contact/)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.