# L9960 L9960T

# Automotive Single/Dual H-Bridge, SPI programmable DC Brushed Motor Driver

Datasheet - production data

#### **Features**

- · AEC-Q100 qualified

- Flexible driving strategy via configurable pins PWM/DIR (IN1/IN2)

- RDSon < 400 m $\Omega$  (full path at T<sub>i</sub> =150° C)

- Operating battery supply voltage from 4.5 V up to 28 V

- Operating VDD5 supply voltage from 4.5 V to 5.5 V

- Input switching frequency up to 20 kHz

- Built in charge pump supporting 100% duty cycle

- Logic levels compatible to 3.3 V and 5 V

- Monitoring of VDD5 supply voltage with bidirectional switch-off pin

- · Current limitation SPI-adjustable in four steps.

- Output stage current limitation with dependence on temperature

- 2 Programmable voltage and current slew rate control

- Short circuit and programmable thermal warning and shutdown thresholds

- Open Load diagnosis in ON condition

- All I/O pins can withstand up to 19 V

- SPI interface for configuration and diagnosis

- Two independent enable/disable pins NDIS and DIS and SOPC (Switch-off Path Check) available

- Spread Spectrum function for EMI reduction

- Available in single (L9960) and Twin (L9960T) option, both in PSSO36 package

### **Description**

The device is an integrated H-Bridge for resistive and inductive loads for automotive applications. Target application includes throttle control actuators, exhaust gas recirculation control valves and general purpose DC motors such as turbo, flap control and electric pumps.

The driving strategy is enhanced by configurable PWM / DIR pins and IN1/IN2.

The H-Bridge contains integrated free-wheel diodes. In case of freewheeling condition, the low-side only is switched on in parallel of its diode to reduce power dissipation.

The integrated Serial Peripheral Interface (SPI) makes it possible to adjust device parameters, to control all operating modes and read out diagnostic information.

Table 1. Device summary

| Order code | Package     | Packing       |  |

|------------|-------------|---------------|--|

| L9960      |             | Tube          |  |

| L9960TR    | PowerSSO-36 | Tape and Reel |  |

| L9960T     | Fower330-30 | Tube          |  |

| L9960T-TR  |             | Tape and Reel |  |

Contents L9960, L9960T

# **Contents**

| 1.1 Block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1    | Bloc | k diagra  | am and pin description                            | 8   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------|---------------------------------------------------|-----|

| 1.2.1 PowerSO36 package  2 Application description 2.1 Application circuit 2.2 Bill of materials  3 General electrical characteristics 3.1 Absolute maximum ratings 3.2 Thermal ratings 3.3 Range of functionality 3.4 Electrical characteristics 3.5 Timing characteristics 4 Functional description 4.1 Device supply 4.1.1 Functional State 4.1.2 Vps power supply 4.1.3 VDD5 regulated voltage supply 4.1.4 VDDIO voltage supply 4.1.5 Device supply electrical characteristics 4.2 Power on reset (POR) and SW reset 4.2.1 Power on reset (POR) electrical characteristics 2.3 As System clock electrical characteristics 2.4 As System clock electrical characteristics 3.5 Digital input controls 4.5 Digital input controls 4.5 Digital inputs control electrical characteristics 3.6 Control inputs DIR and PWM 3.7 As Digital inputs control electrical characteristics 4.5 Digital inputs control electrical characteristics 4.5 Digital inputs DIR and PWM 3.5 As Control inputs DIR and PWM 3.5 As Digital inputs control electrical characteristics 4.5 Digital inputs control electrical characteristics |      | 1.1  | Block o   | diagram                                           | 8   |

| 2       Application description       12         2.1       Application circuit       13         2.2       Bill of materials       13         3       General electrical characteristics       14         3.1       Absolute maximum ratings       14         3.2       Thermal ratings       15         3.3       Range of functionality       15         3.4       Electrical characteristics       16         3.5       Timing characteristics       16         4.5       Timing characteristics       17         4       Functional description       18         4.1       Device supply       16         4.1.1       Functional State       11         4.1.2       Vps power supply       18         4.1.3       VDD5 regulated voltage supply       21         4.1.4       VDDIO voltage supply       22         4.1.4       VDDIO voltage supply electrical characteristics       22         4.2.1       Power on reset (POR) and SW reset       22         4.2.1       Power on reset (POR) electrical characteristics       23         4.3       System clock electrical characteristics       25         4.3       System clock electrical characteristics <td></td> <td>1.2</td> <td>Pin des</td> <td>scription</td> <td> 9</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | 1.2  | Pin des   | scription                                         | 9   |

| 2.1       Application circuit       13         2.2       Bill of materials       13         3       General electrical characteristics       14         3.1       Absolute maximum ratings       14         3.2       Thermal ratings       18         3.3       Range of functionality       18         3.4       Electrical characteristics       16         3.5       Timing characteristics       16         4.1       Functional description       18         4.1       Device supply       18         4.1.1       Functional State       11         4.1.1       Functional State       11         4.1.2       Vps power supply       18         4.1.3       VDDF regulated voltage supply       22         4.1.4       VDDIO voltage supply       22         4.1.4       VDDIO voltage supply electrical characteristics       23         4.2       Power on reset (POR) and SW reset       25         4.2.1       Power on reset (POR) electrical characteristics       25         4.3       System clock electrical characteristics       26         4.4       Hardware self check (HWSC) and LBIST       30         4.4.1       HWSC test procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |      | 1.2.1     | PowerSSO36 package                                | 9   |

| 2.2       Bill of materials       13         3       General electrical characteristics       14         3.1       Absolute maximum ratings       14         3.2       Thermal ratings       15         3.3       Range of functionality       18         3.4       Electrical characteristics       16         3.5       Timing characteristics       16         4.1       Device supply       18         4.1       Punctional description       18         4.1       Pevice supply       18         4.1       Functional State       18         4.1.1       Functional State       18         4.1.2       Vps power supply       18         4.1.3       VDD5 regulated voltage supply       22         4.1.4       VDDIO voltage supply       22         4.1.4       VDDIO voltage supply electrical characteristics       22         4.2       Power on reset (POR) and SW reset       22         4.2       Power on reset (POR) electrical characteristics       24         4.3       System clock electrical characteristics       25         4.4       Hardware self check (HWSC) and LBIST       30         4.4.1       HWSC test procedure       31 </td <td>2</td> <td>Арр</td> <td>lication</td> <td>description</td> <td>12</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2    | Арр  | lication  | description                                       | 12  |

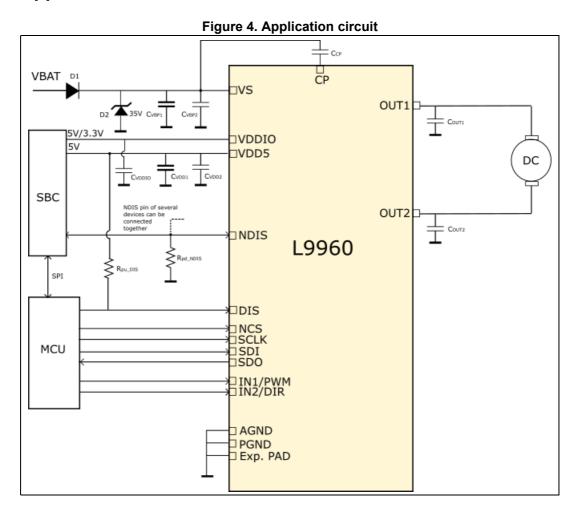

| 3.1 Absolute maximum ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 2.1  | Applica   | ation circuit                                     | 12  |

| 3.1 Absolute maximum ratings  3.2 Thermal ratings  3.3 Range of functionality  3.4 Electrical characteristics  3.5 Timing characteristics  4.1 Device supply  4.1.1 Functional State  4.1.2 Vps power supply  4.1.3 VDD5 regulated voltage supply  4.1.4 VDDIO voltage supply  4.1.5 Device supply electrical characteristics  4.2 Power on reset (POR) and SW reset  4.2.1 Power on reset (POR) electrical characteristics  4.3 System clock electrical characteristics  4.4 Hardware self check (HWSC) and LBIST  4.4.1 HWSC test procedure  4.4.2 HWSC/LBIST electrical characteristics  3.5 Timing characteristics  4.6 Digital input controls  4.5 Digital input controls  4.5.1 Bridge functional modes  4.5.2 Disable inputs DIS and NDIS  4.5.3 Control inputs DIR and PWM  3.5 Digital inputs control electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | 2.2  | Bill of n | materials                                         | 13  |

| 3.2 Thermal ratings 3.3 Range of functionality 3.4 Electrical characteristics 3.5 Timing characteristics 4.5 Timing characteristics 4.7 Functional description 4.1 Device supply 4.1.1 Functional State 4.1.2 Vps power supply 4.1.3 VDD5 regulated voltage supply 4.1.4 VDDIO voltage supply 4.1.5 Device supply electrical characteristics 4.2 Power on reset (POR) and SW reset 4.2.1 Power on reset (POR) electrical characteristics 4.3 System clock electrical characteristics 4.4 Hardware self check (HWSC) and LBIST 4.4.1 HWSC test procedure 4.4.2 HWSC/LBIST electrical characteristics 3.5 Digital input controls 4.5.1 Bridge functional modes 4.5.2 Disable inputs DIS and NDIS 4.5.3 Control inputs DIS and PWM 4.5.4 Digital inputs control electrical characteristics 4.5 Digital inputs control electrical characteristics 4.5 Digital inputs DIS and PWM 4.5.4 Digital inputs control electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3    | Gen  | eral elec | trical characteristics                            | 14  |

| 3.3 Range of functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | 3.1  | Absolu    | te maximum ratings                                | 14  |

| 3.4 Electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | 3.2  | Therma    | al ratings                                        | 15  |

| 4       Functional description       18         4.1       Device supply       18         4.1.1       Functional State       18         4.1.2       Vps power supply       18         4.1.3       VDD5 regulated voltage supply       22         4.1.4       VDDIO voltage supply       26         4.1.5       Device supply electrical characteristics       22         4.2       Power on reset (POR) and SW reset       23         4.2.1       Power on reset (POR) electrical characteristics       25         4.3       System clock electrical characteristics       25         4.4       Hardware self check (HWSC) and LBIST       30         4.4.1       HWSC test procedure       30         4.4.2       HWSC/LBIST electrical characteristics       33         4.5.1       Bridge functional modes       33         4.5.2       Disable inputs DIS and NDIS       36         4.5.3       Control inputs DIR and PWM       33         4.5.4       Digital inputs control electrical characteristics       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | 3.3  | Range     | of functionality                                  | 15  |

| 4.1 Device supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | 3.4  | Electric  | cal characteristics                               | 16  |

| 4.1       Device supply       18         4.1.1       Functional State       18         4.1.2       Vps power supply       18         4.1.3       VDD5 regulated voltage supply       22         4.1.4       VDDIO voltage supply       26         4.1.5       Device supply electrical characteristics       22         4.2       Power on reset (POR) and SW reset       25         4.2.1       Power on reset (POR) electrical characteristics       29         4.3       System clock electrical characteristics       29         4.4       Hardware self check (HWSC) and LBIST       36         4.4.1       HWSC test procedure       36         4.4.2       HWSC/LBIST electrical characteristics       33         4.5.1       Bridge functional modes       33         4.5.2       Disable inputs DIS and NDIS       36         4.5.3       Control inputs DIR and PWM       37         4.5.4       Digital inputs control electrical characteristics       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      | 3.5  | Timing    | characteristics                                   | 17  |

| 4.1.1       Functional State       18         4.1.2       Vps power supply       18         4.1.3       VDD5 regulated voltage supply       22         4.1.4       VDDIO voltage supply       26         4.1.5       Device supply electrical characteristics       27         4.2       Power on reset (POR) and SW reset       26         4.2.1       Power on reset (POR) electrical characteristics       29         4.3       System clock electrical characteristics       29         4.4       Hardware self check (HWSC) and LBIST       30         4.4.1       HWSC test procedure       30         4.4.2       HWSC/LBIST electrical characteristics       33         4.5       Digital input controls       33         4.5.1       Bridge functional modes       33         4.5.2       Disable inputs DIS and NDIS       36         4.5.3       Control inputs DIR and PWM       35         4.5.4       Digital inputs control electrical characteristics       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4    | Fund | ctional d | lescription                                       | 18  |

| 4.1.2       Vps power supply       16         4.1.3       VDD5 regulated voltage supply       22         4.1.4       VDDIO voltage supply       26         4.1.5       Device supply electrical characteristics       22         4.2       Power on reset (POR) and SW reset       25         4.2.1       Power on reset (POR) electrical characteristics       26         4.3       System clock electrical characteristics       25         4.4       Hardware self check (HWSC) and LBIST       30         4.4.1       HWSC test procedure       30         4.4.2       HWSC/LBIST electrical characteristics       33         4.5.1       Bridge functional modes       33         4.5.2       Disable inputs DIS and NDIS       36         4.5.3       Control inputs DIR and PWM       33         4.5.4       Digital inputs control electrical characteristics       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | 4.1  | Device    | supply                                            | 18  |

| 4.1.3 VDD5 regulated voltage supply 2.2.4.1.4 VDDIO voltage supply 4.1.5 Device supply electrical characteristics 2.3.4.2 Power on reset (POR) and SW reset 4.2.1 Power on reset (POR) electrical characteristics 2.5.4.3 System clock electrical characteristics 2.6.4.4 Hardware self check (HWSC) and LBIST 4.4.1 HWSC test procedure 4.4.2 HWSC/LBIST electrical characteristics 3.6.4.5 Digital input controls 4.5.1 Bridge functional modes 4.5.2 Disable inputs DIS and NDIS 4.5.3 Control inputs DIR and PWM 3.5.4 Digital inputs control electrical characteristics 4.5.5 Digital inputs control electrical characteristics 4.5.6 Digital inputs DIR and PWM 3.5.7 Digital inputs control electrical characteristics 4.5.7 Digital inputs control electrical characteristics 4.5.7 Digital inputs control electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |      | 4.1.1     | Functional State                                  | 18  |

| 4.1.4 VDDIO voltage supply 4.1.5 Device supply electrical characteristics 2.2 4.2 Power on reset (POR) and SW reset 4.2.1 Power on reset (POR) electrical characteristics 2.5 4.3 System clock electrical characteristics 2.6 4.4 Hardware self check (HWSC) and LBIST 4.4.1 HWSC test procedure 4.4.2 HWSC/LBIST electrical characteristics 3.6 4.5 Digital input controls 4.5.1 Bridge functional modes 4.5.2 Disable inputs DIS and NDIS 4.5.3 Control inputs DIR and PWM 4.5.4 Digital inputs control electrical characteristics 4.5 4.5 4.5 4.5 5 6 6 6 6 7 6 7 6 7 6 7 6 7 7 7 7 7 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |      | 4.1.2     | Vps power supply                                  | 18  |

| 4.1.5 Device supply electrical characteristics 22 4.2 Power on reset (POR) and SW reset 4.2.1 Power on reset (POR) electrical characteristics 25 4.3 System clock electrical characteristics 25 4.4 Hardware self check (HWSC) and LBIST 36 4.4.1 HWSC test procedure 36 4.4.2 HWSC/LBIST electrical characteristics 33 4.5 Digital input controls 36 4.5.1 Bridge functional modes 37 4.5.2 Disable inputs DIS and NDIS 36 4.5.3 Control inputs DIR and PWM 37 4.5.4 Digital inputs control electrical characteristics 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |      | 4.1.3     | VDD5 regulated voltage supply                     | 22  |

| 4.2 Power on reset (POR) and SW reset 4.2.1 Power on reset (POR) electrical characteristics 2.9 4.3 System clock electrical characteristics 2.9 4.4 Hardware self check (HWSC) and LBIST 4.4.1 HWSC test procedure 3.0 4.4.2 HWSC/LBIST electrical characteristics 3.1 4.5 Digital input controls 4.5.1 Bridge functional modes 4.5.2 Disable inputs DIS and NDIS 4.5.3 Control inputs DIR and PWM 3.1 4.5.4 Digital inputs control electrical characteristics 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      | 4.1.4     | VDDIO voltage supply                              | 26  |

| 4.2.1 Power on reset (POR) electrical characteristics 29 4.3 System clock electrical characteristics 29 4.4 Hardware self check (HWSC) and LBIST 30 4.4.1 HWSC test procedure 30 4.4.2 HWSC/LBIST electrical characteristics 32 4.5 Digital input controls 33 4.5.1 Bridge functional modes 33 4.5.2 Disable inputs DIS and NDIS 36 4.5.3 Control inputs DIR and PWM 37 4.5.4 Digital inputs control electrical characteristics 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      | 4.1.5     | Device supply electrical characteristics          | 27  |

| 4.3 System clock electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | 4.2  | Power     | on reset (POR) and SW reset                       | 27  |

| 4.4 Hardware self check (HWSC) and LBIST 4.4.1 HWSC test procedure 4.4.2 HWSC/LBIST electrical characteristics 33 4.5 Digital input controls 4.5.1 Bridge functional modes 4.5.2 Disable inputs DIS and NDIS 4.5.3 Control inputs DIR and PWM 33 4.5.4 Digital inputs control electrical characteristics 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |      | 4.2.1     | Power on reset (POR) electrical characteristics   | 29  |

| 4.4.1 HWSC test procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | 4.3  | System    | n clock electrical characteristics                | 29  |

| 4.4.2 HWSC/LBIST electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | 4.4  | Hardwa    | are self check (HWSC) and LBIST                   | 30  |

| 4.5 Digital input controls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |      |           | , ,                                               |     |

| 4.5.1 Bridge functional modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |      | 4.4.2     | HWSC/LBIST electrical characteristics             | 32  |

| 4.5.2 Disable inputs DIS and NDIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | 4.5  | Digital   | input controls                                    | 33  |

| 4.5.3 Control inputs DIR and PWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |      | 4.5.1     | Bridge functional modes                           | 33  |

| 4.5.4 Digital inputs control electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |      | 4.5.2     | Disable inputs DIS and NDIS                       | 36  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |      | 4.5.3     | Control inputs DIR and PWM                        | 37  |

| 2/05 DS44415 Day 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |      | 4.5.4     | Digital inputs control electrical characteristics | 41  |

| ZIBO DO ILLIO KEV IU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2/95 |      |           | DS11115 Rev 10                                    | 47/ |

|   | 4.6   | Driver c | onfiguration                                                                       | 42 |

|---|-------|----------|------------------------------------------------------------------------------------|----|

|   |       | 4.6.1    | Slew rate control                                                                  | 42 |

|   |       | 4.6.2    | Current slew rate                                                                  | 42 |

|   |       | 4.6.3    | Voltage slew rate                                                                  | 43 |

|   |       | 4.6.4    | Current limitation                                                                 | 46 |

|   | 4.7   | Driver p | rotections                                                                         | 54 |

|   |       | 4.7.1    | Over-temperature protection                                                        | 54 |

|   |       | 4.7.2    | Over-temperature monitoring electrical characteristics                             | 56 |

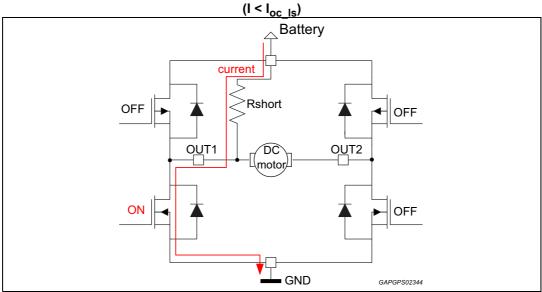

|   |       | 4.7.3    | Short-circuit to battery: over-current detection in low-side transistors $\ . \ .$ | 57 |

|   |       | 4.7.4    | Short-circuit to ground: over-current detection in high-side transistor $\ .$ .    | 58 |

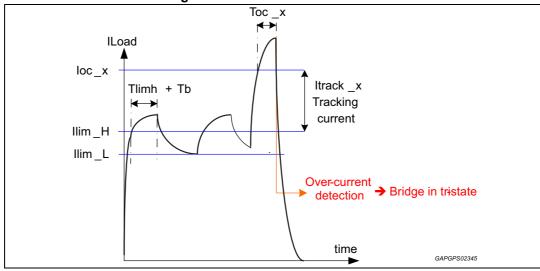

|   |       | 4.7.5    | Load in short-circuit                                                              | 58 |

|   |       | 4.7.6    | Over-current detection electrical characteristics                                  | 59 |

|   | 4.8   | Diagnos  | tics and registers descriptions in case of validity bit configuration              | 60 |

|   |       | 4.8.1    | Diagnostic Reset strategy                                                          | 60 |

|   |       | 4.8.2    | Diagnostic reset bit                                                               | 61 |

|   |       | 4.8.3    | Global Failure Bit NGFAIL definition                                               | 64 |

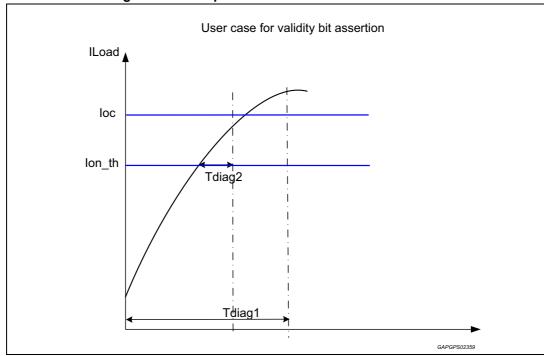

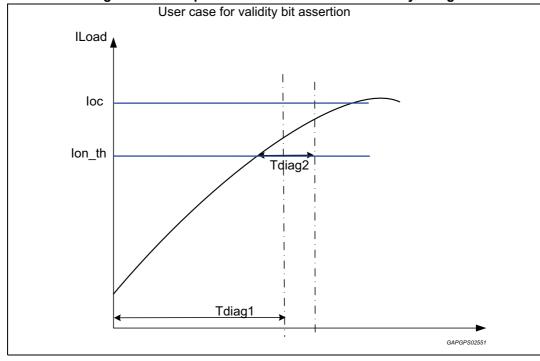

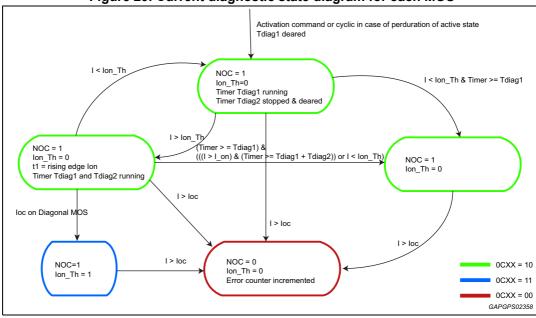

|   |       | 4.8.4    | Diagnostic of "Over-current" in on-state                                           | 65 |

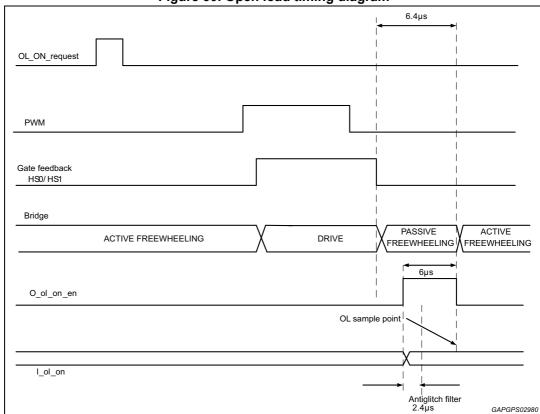

|   |       | 4.8.5    | Diagnostic of "Open Load" in on-state                                              | 69 |

|   |       | 4.8.6    | On-state diagnostics electrical characteristics                                    | 70 |

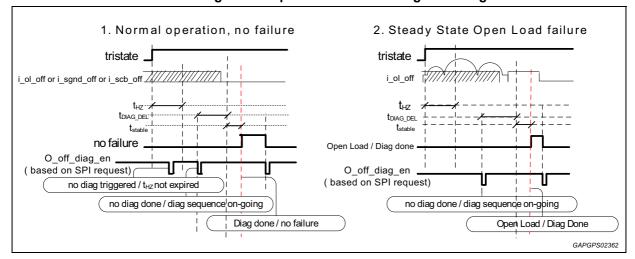

|   |       | 4.8.7    | Off-state diagnostic                                                               | 71 |

|   |       | 4.8.8    | Off-state diagnostic electrical characteristics                                    | 73 |

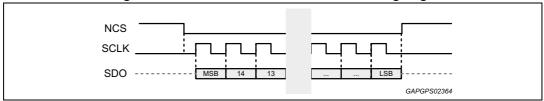

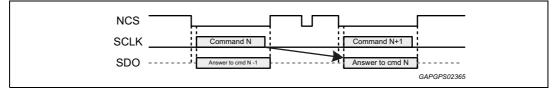

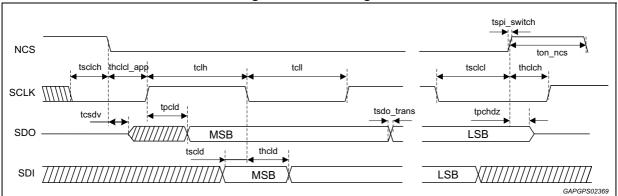

|   | 4.9   | SPI      |                                                                                    | 73 |

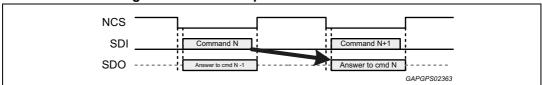

|   |       | 4.9.1    | Protocol description                                                               | 74 |

|   |       | 4.9.2    | SPI command and response words format                                              | 75 |

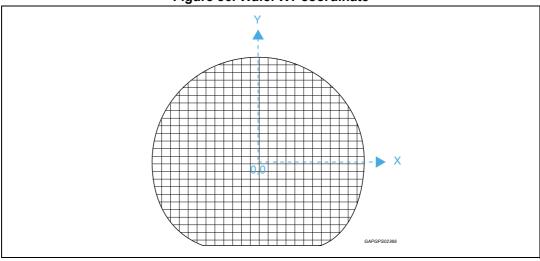

|   |       | 4.9.3    | Read ASIC traceability number                                                      | 77 |

|   |       | 4.9.4    | Read Logic HW version                                                              | 78 |

|   |       | 4.9.5    | Parity bit                                                                         | 78 |

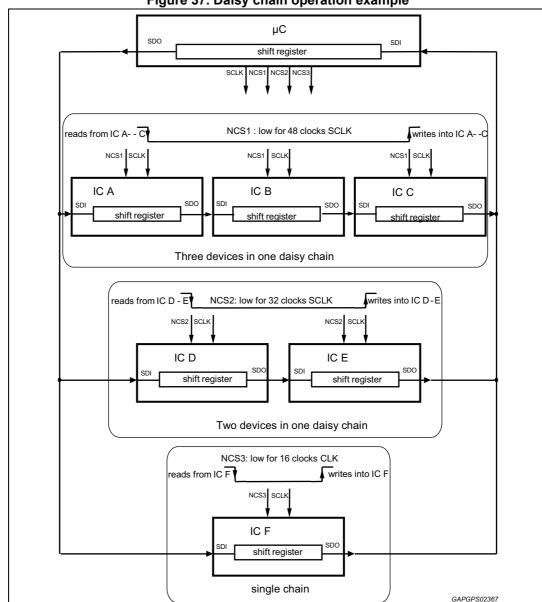

|   |       | 4.9.6    | SPI communication mode (Parallel and Daisy chain mode)                             | 79 |

|   |       | 4.9.7    | Communication check                                                                | 80 |

|   |       | 4.9.8    | Electrical characteristics                                                         | 81 |

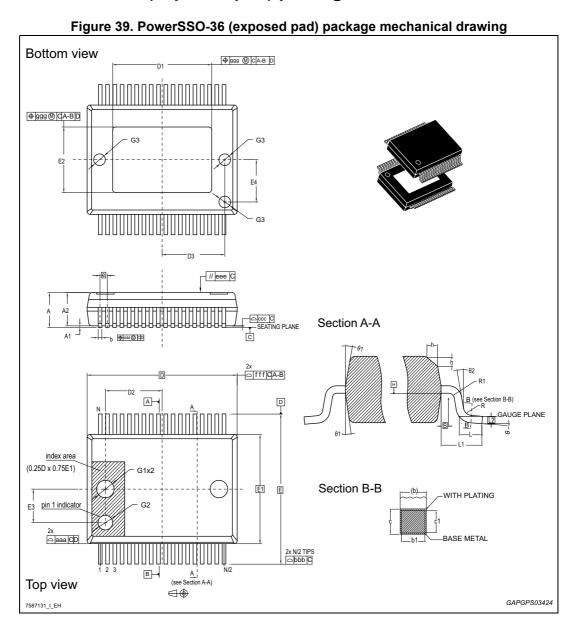

| 5 | Packa | age info | rmation                                                                            | 89 |

|   | 5.1   | PowerS   | SO-36 (exposed pad) package mechanical data                                        | 89 |

|   |       |          |                                                                                    |    |

| 6 | Keter | ence do  | cument                                                                             | 92 |

| 7 | Revis | ion hist | ory                                                                                | 93 |

List of tables L9960, L9960T

# List of tables

| Table 1.  | Device summary                                     | . 1 |

|-----------|----------------------------------------------------|-----|

| Table 2.  | Pin definition (PSSO36twin die) and function       | 10  |

| Table 3.  | Application circuit - BOM                          | 13  |

| Table 4.  | Absolute maximum ratings                           | 14  |

| Table 5.  | Thermal ratings                                    | 15  |

| Table 6.  | Range of functionality                             | 15  |

| Table 7.  | Bridge output drivers                              | 16  |

| Table 8.  | Timing characteristics                             | 17  |

| Table 9.  | VPS_UV                                             | 19  |

| Table 10. | VPS_UV_REG                                         |     |

| Table 11. | VPS electrical characteristics                     | 20  |

| Table 12. | UV PROT EN                                         | 20  |

| Table 13. | UV_PROT_EN_echo                                    | 20  |

| Table 14. | UV_WIN                                             |     |

| Table 15. | UV_WIN_echo                                        |     |

| Table 16. | UV_CNT_REACHED                                     |     |

| Table 17. | VDD_UV_REG                                         |     |

| Table 18. | VDD_UV                                             |     |

| Table 19. | VDD OV REG                                         |     |

| Table 20. | VDD_OV                                             |     |

| Table 21. | VDD_OV_L[2:0]                                      |     |

| Table 22. | VDD5 voltage monitoring Electrical characteristics |     |

| Table 23. | Device supply electrical characteristic            |     |

| Table 24. | SW reset [1:0]                                     |     |

| Table 25. | POR status                                         |     |

| Table 26. | POR electrical characteristics                     |     |

| Table 27. | System clock electrical characteristics            |     |

| Table 28. | NSPREAD                                            |     |

| Table 29. | NSPREAD_echo                                       |     |

| Table 30. | HWSC/LBIST Trigger                                 |     |

| Table 31. | HWSC/LBIST_status                                  |     |

| Table 32. | HWSC/LBIST electrical characteristics              |     |

| Table 33. | VVL MODE                                           |     |

| Table 34. |                                                    |     |

| Table 35. | TVVL[3:0] (µs)                                     |     |

| Table 36. | TVVL_echo[3:0]                                     |     |

| Table 37. | BRIDGE_EN                                          |     |

| Table 38. | NDIS_status                                        |     |

| Table 39. | DIS status                                         |     |

| Table 40. | Normal mode H-bridge input                         |     |

| Table 41. | IN1/IN2 mode H-bridge input                        |     |

| Table 42. | VVL mode H-bridge input                            |     |

| Table 43. | TSW_low_current                                    |     |

| Table 44. | TSW low current echo                               |     |

| Table 45. | Digital inputs control electrical characteristics  |     |

| Table 46. | ISR                                                |     |

| Table 47. | Range current slew rate                            |     |

| Table 48  | · ·                                                | 43  |

L9960, L9960T List of tables

| Table 49.  | VSR                                                    | 43 |

|------------|--------------------------------------------------------|----|

| Table 50.  | Voltage slew rate                                      | 43 |

| Table 51.  | VSR_echo                                               | 43 |

| Table 52.  | NOSR                                                   | 44 |

| Table 53.  | NOSR_echo                                              |    |

| Table 54.  | TDSR                                                   | 44 |

| Table 55.  | TDSR_ECHO                                              | 44 |

| Table 56.  | ILIM_REG                                               | 46 |

| Table 57.  | CL[1:0]                                                |    |

| Table 58.  | CL_echo[1:0]                                           |    |

| Table 59.  | OTwarn_thr_var                                         |    |

| Table 60.  | OTwarn_thr_var_echo                                    | 50 |

| Table 61.  | OTsd_thr_var                                           | 51 |

| Table 62.  | OTsd_thr_var_echo                                      | 51 |

| Table 63.  | Electrical characteristics                             | 52 |

| Table 64.  | NOTSD                                                  | 54 |

| Table 65.  | NOTSD_REG                                              | 54 |

| Table 66.  | OTWARN_TSEC_EN                                         | 55 |

| Table 67.  | OTWARN_TSEC_EN_echo                                    | 55 |

| Table 68.  | OTWARN                                                 |    |

| Table 69.  | OTWARN_REG                                             | 56 |

| Table 70.  | Over-temperature monitoring electrical characteristics | 56 |

| Table 71.  | Over-current detection electrical characteristics      | 59 |

| Table 72.  | DIAG_CLR_EN                                            | 61 |

| Table 73.  | DIAG_CLR_EN_echo                                       | 61 |

| Table 74.  | Status bits description                                | 62 |

| Table 75.  | Diagnostics bits description                           | 62 |

| Table 76.  | NGFAIL                                                 |    |

| Table 77.  | Diagnostic of "Over-current" in on-state               | 65 |

| Table 78.  | Error_count[3:0]                                       |    |

| Table 79.  | TDIAG1 (μs)                                            |    |

| Table 80.  | TDIAG1_echo[2:0]                                       |    |

| Table 81.  | OL_ON                                                  |    |

| Table 82.  | OL_ON_STATUS [1:0]                                     |    |

| Table 83.  | Open Load in ON-state electrical characteristics       |    |

| Table 84.  | TRIG                                                   |    |

| Table 85.  | DIAG_OFF[2:0]                                          |    |

| Table 86.  | Off-state diagnostic electrical characteristics        |    |

| Table 87.  | SPI command word format                                |    |

| Table 88.  | SPI response word format                               |    |

| Table 89.  | Supplier ID code                                       |    |

| Table 90.  | Silicon version identifier                             |    |

| Table 91.  | Wafer coordinate                                       |    |

| Table 92.  | Traceability code and wafer number                     |    |

| Table 93.  | CC_latch                                               |    |

| Table 94.  | Config_CC                                              |    |

| Table 95.  | Config_CC_state_echo7                                  |    |

| Table 96.  | Electrical characteristics serial data output          |    |

| Table 97.  | SPI electrical characteristics                         |    |

| Table 98.  | SPI communication command and answer words             |    |

| Table 99.  | SPI communication configuration                        |    |

| Table 100. | PowerSSO-36 (exposed pad) package mechanical data      | 90 |

| List of table | es                        | L9960, L996 | τO |

|---------------|---------------------------|-------------|----|

|               |                           |             |    |

| Table 101.    | Document revision history |             | 93 |

L9960, L9960T List of figures

# **List of figures**

| Figure 1.  | Block diagram for L9960                                                                         | . 8 |

|------------|-------------------------------------------------------------------------------------------------|-----|

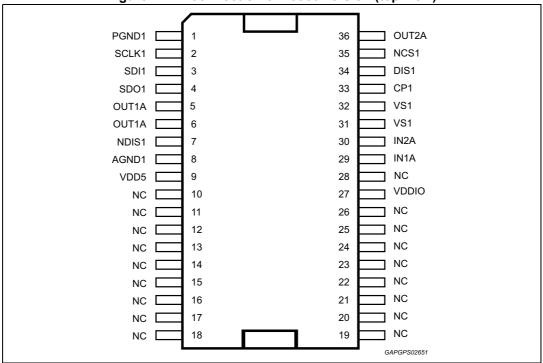

| Figure 2.  | Pin connection of L9960 version (top view)                                                      | . 9 |

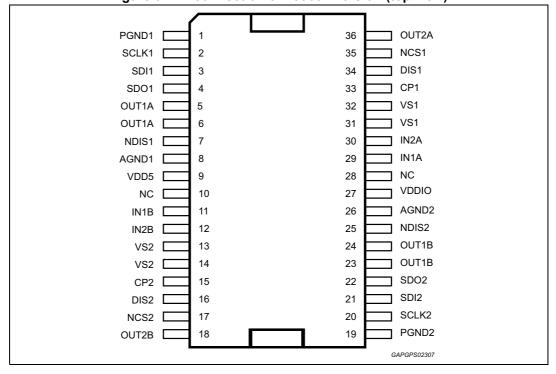

| Figure 3.  | Pin connection of L9960T version (top view)                                                     | . 9 |

| Figure 4.  | Application circuit                                                                             | 12  |

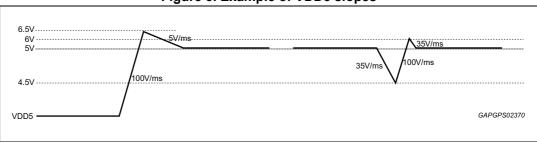

| Figure 5.  | Example of VDD5 slopes                                                                          | 16  |

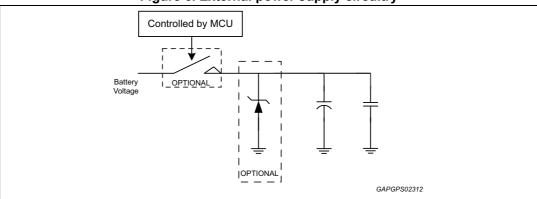

| Figure 6.  | External power supply circuitry                                                                 | 18  |

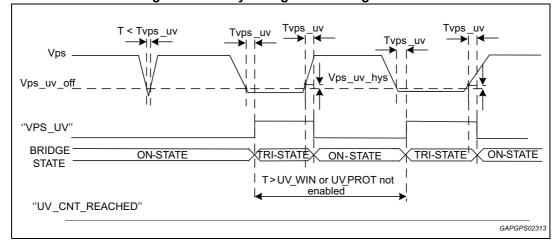

| Figure 7.  | Battery voltage monitoring – case1                                                              | 21  |

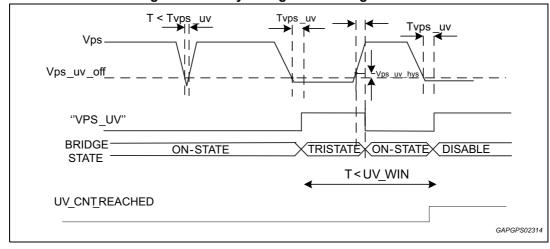

| Figure 8.  | Battery voltage monitoring – case2                                                              | 22  |

| Figure 9.  | VDD5 under voltage monitoring                                                                   | 23  |

| Figure 10. | VDD5 over voltage monitoring                                                                    | 24  |

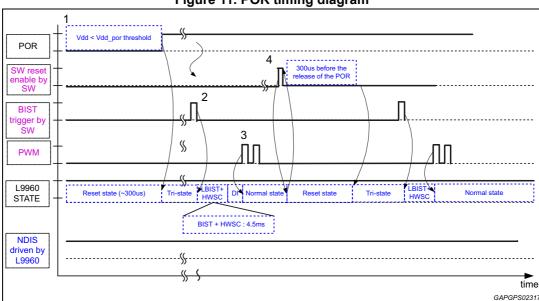

| Figure 11. | POR timing diagram                                                                              | 28  |

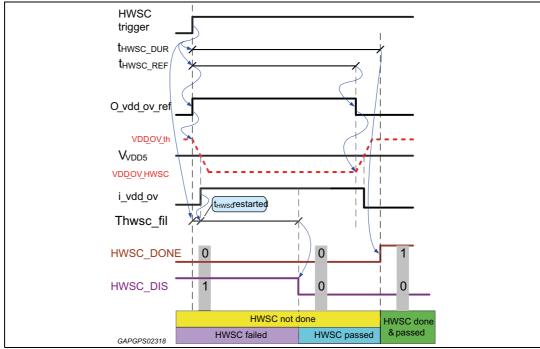

| Figure 12. | HWSC timing diagram                                                                             | 31  |

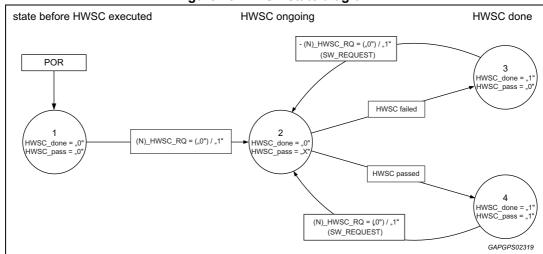

| Figure 13. | HWSC state diagram                                                                              | 32  |

| Figure 14. | Bridge STATE diagram                                                                            | 33  |

| Figure 15. | Bridge STATE diagram in VVL mode                                                                | 34  |

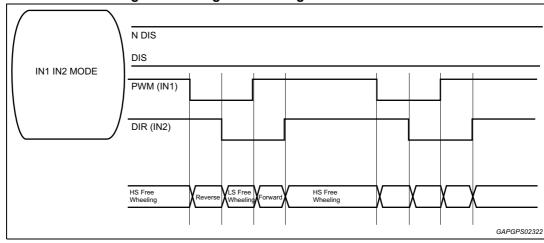

| Figure 16. | Bridge STATE diagram in IN1/IN2 mode                                                            | 36  |

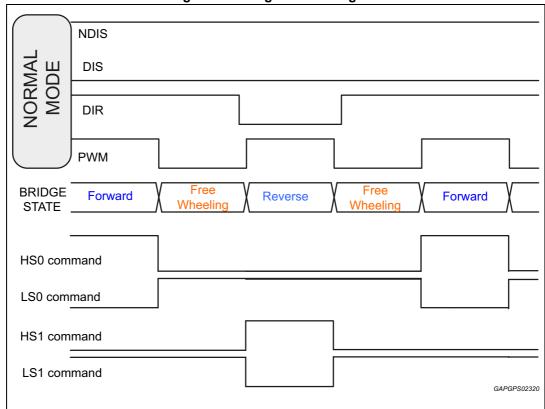

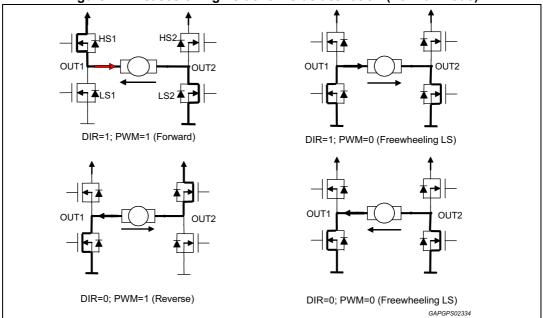

| Figure 17. | 4 cases of high-side/low-side activation (normal mode)                                          | 39  |

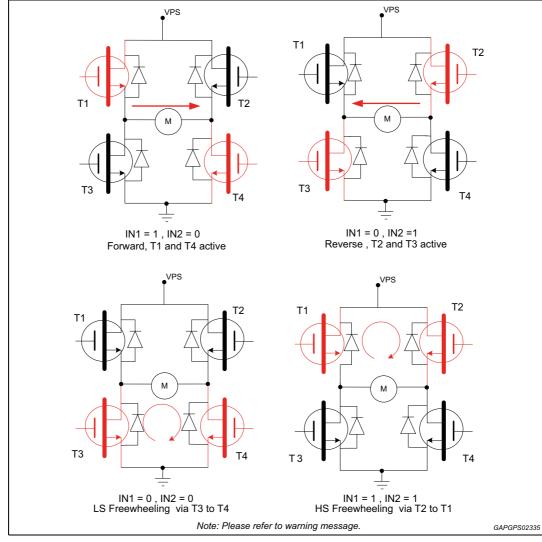

| Figure 18. | 4 cases of high-side/low-side activation (IN1/IN2 mode)                                         | 40  |

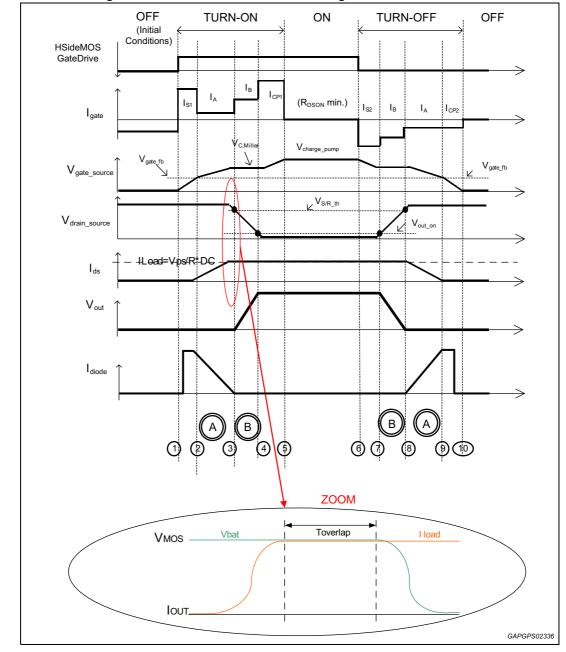

| Figure 19. | Ideal waveforms of switching with slew rate control                                             | 45  |

| Figure 20. | Tdiag2 blanking time depends on the Vps voltage                                                 | 47  |

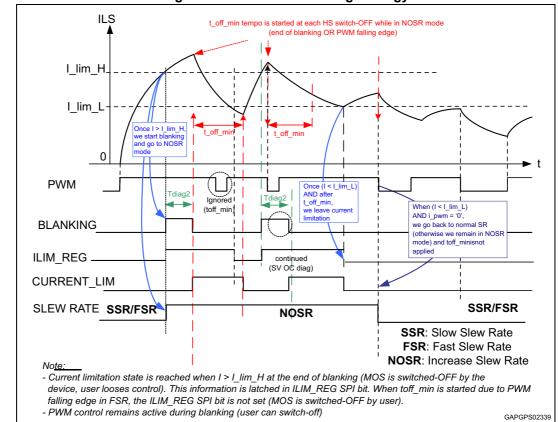

| Figure 21. | Slew rate switching strategy                                                                    | 47  |

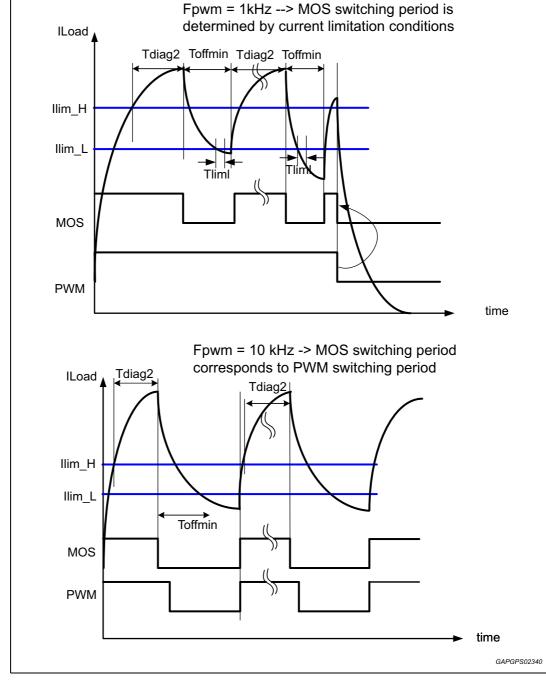

| Figure 22. | Current limitation schemes                                                                      | 48  |

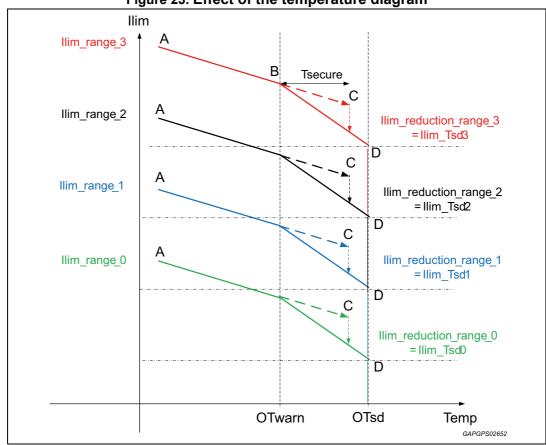

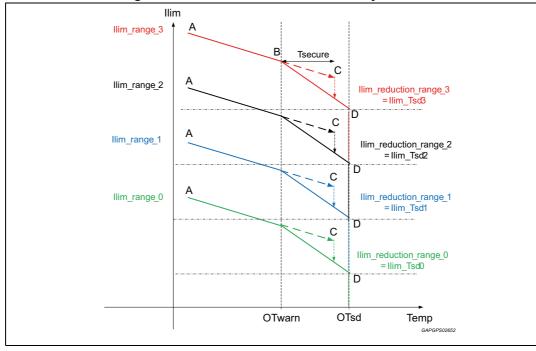

| Figure 23. | Effect of the temperature diagram                                                               | 49  |

| Figure 24. | Thermal current limitation adjustment                                                           | 55  |

| Figure 25. | Example of low-side transistor low impedance short circuit to battery (I < I <sub>oc Is</sub> ) | 57  |