A Product Line of Diodes Incorporated

PI5USB31213

## USB 3.1 GEN2 10Gbps Mux/Demux Switch with I2C Control for Type-C Connector

### **Features**

- → USB Type-C<sup>™</sup> Specification 1.1

- → Dual Differential Channel, 10Gbps 2:1 USB 3.1 Gen 2 Mux/DeMux

- → Switches USB controller and Type-C connector

- → Supports Host-mode/Device-mode/Dual-role mode

- → Auto-configure ports orientation through CC detection

- → Supports VCONN to power active cables and other accessories

- → Supports over-current protection and over-voltage protection for VCONN

- → Allow both pin control and I<sup>2</sup>C interface

- → Integrated power switches, high-precision resistors and current sources for CC pins

- → Provides support for default current, 1.5A and 3A modes with I<sup>2</sup>C control

- → Output indicator for plug-in detection

- → Power saving mode

- → Wide power supply range: 2.7V 5.5V

- → Temperature Range: -40°C to 85°C

- → Packaging (Pb-free & Green):

- 24- contact, TQFN(2mm x 4mm)

## **Applications**

- Notebooks

- Mobile Phones

- Tablets

- · Docking Station

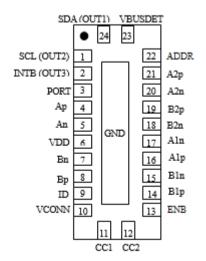

# **Pin Configuration**

Figure 1 Pin Assignment (Top View)

## **Description**

The PI5USB31213 is a 10Gbps dual differential channel bidirectional multiplexer/de-multiplexer switch solution for USB 3.1 Gen2 Type-C connector applications. PI5USB31213 switches between the USB controller and the new Type-C connector. It supports host mode, device mode and dual-role mode ports with automatic configuration based on the voltage levels detected on CC pin. It offers excellent signal integrity for high-speed signals at low power dissipation.

PI5USB31213 supports both pin and I<sup>2</sup>C control base on ADDR pin setting. In pin control mode, the PORT input pin determines the port setting, whether this is a host, device or dual-role port. In host mode, the system can monitor ID pin to know the connector status while default current mode is set. Systems running in device mode can monitor system VBUS for connector status as well as OUT1 and OUT2 pins for host's charging profile capability.

Enabling I<sup>2</sup>C control mode allow high flexibility for port control and communications through registers read/write in PI5USB31213. There is also flexibility to support Default, 1.5A and 3A current modes. An interrupt signal for indicating changes with the I<sup>2</sup>C registers is sent to the master to notify the system any change in the Type-C connector while in parallel the system can still monitor ID pin.

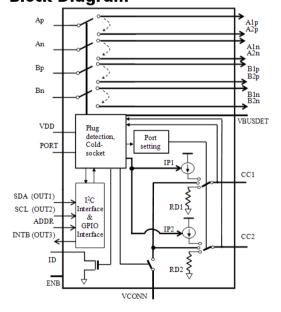

## **Block Diagram**

Figure 2. PI5USB31213 Block diagram

**Pin Descriptions**

| Pin Descrip Pin Number | Pin Name     | I/O          | Description                                                                                    |

|------------------------|--------------|--------------|------------------------------------------------------------------------------------------------|

| Pin Number             | Pin Name     | 1/0          | Description 12C assumption also being a                                                        |

|                        |              |              | I <sup>2</sup> C communication clock signal.                                                   |

|                        |              |              | Dual function as open drain Type-C Current Mode Detect 1 in pin control                        |

| 1                      |              | 1/0          | mode when port is a device;                                                                    |

| 1                      | SCL/OUT2     | I/O          | OUT2 OUT1 Current Mode                                                                         |

|                        |              |              | Hi-Z Hi-Z Default                                                                              |

|                        |              |              | Hi-Z Low Medium                                                                                |

|                        |              |              | Low Low High                                                                                   |

|                        |              |              | Open drain output. In I <sup>2</sup> C control mode, this is an active LOW interrupt signal    |

|                        |              |              | for indicating changes in I <sup>2</sup> C registers.                                          |

| 2                      | INTB/OUT3    | О            | Dual function as analog audio adapter detection in pin control mode:                           |

|                        |              |              | OUT3=Hi-Z – Not detected;                                                                      |

|                        |              |              | OUT3=Low - Analog audio adapter detected                                                       |

|                        |              |              | Tri-level input pin to indicate port mode (for pin control only):                              |

|                        |              |              | PORT is floating –Try.SNK Dual Role (DRP);                                                     |

| 3                      | PORT         | I            | PORT=VDD – Host (SRC);                                                                         |

|                        |              |              | PORT=GND – Device (SNK)                                                                        |

| 4                      | Ap           | I/O          | Differential USB 3.1 GEN2 signal A (PHY side)                                                  |

| 5                      | An           | I/O          | Differential USB 3.1 GEN2 signal A (PHY side)                                                  |

| 6                      | VDD          | Power        | Positive supply voltage from VBAT                                                              |

| 7                      | Bn           | I/O          | Differential USB 3.1 GEN2 signal B (PHY side)                                                  |

| 8                      | Вр           | I/O          | Differential USB 3.1 GEN2 signal B (1111 side)  Differential USB 3.1 GEN2 signal B (PHY side)  |

| 0                      | Бр           | 1/0          | Open drain output. Asserted low when CC pin detected device attachment                         |

| 9                      | ID           | O            | when port is a Host (or dual-role acting as Host), otherwise ID is hi-z.                       |

| 10                     | VCONN        | Danner       | 2                                                                                              |

| 10                     | VCONN<br>CC1 | Power<br>I/O | Supply voltage for VCONN                                                                       |

| 12                     |              | I/O          | Type-C Configuration channel signals                                                           |

| 12                     | CC2          | 1/0          | Type-C Configuration channel signals  Active-low enable input pin (with internal weak pull up) |

| 13                     | ENB          | I            | ENB=VDD – Disabled/Low Power State                                                             |

| 13                     | END          | 1            | ENB=GND – Enabled/Active State                                                                 |

| 14                     | B1p          | I/O          | Differential USB 3.1 GEN2 signal B for position 1 connection                                   |

| 15                     | B1p<br>B1n   | I/O          | Differential USB 3.1 GEN2 signal B for position 1 connection                                   |

| 16                     | A1p          | I/O          | Differential USB 3.1 GEN2 signal A for position 1 connection                                   |

| 17                     | A1p<br>A1n   | I/O          | Differential USB 3.1 GEN2 signal A for position 1 connection                                   |

| 18                     | B2n          | I/O          | Differential USB 3.1 GEN2 signal A for position 2 connection                                   |

| 19                     | B2p          | I/O          | Differential USB 3.1 GEN2 signal B for position 2 connection                                   |

| 20                     | A2n          | I/O          | Differential USB 3.1 GEN2 signal A for position 2 connection                                   |

| 21                     | A2p          | I/O          | Differential USB 3.1 GEN2 signal A for position 2 connection                                   |

| 21                     | AZP          | 1/0          | Tri-level input pin to indicate I <sup>2</sup> C address or pin control mode:                  |

|                        |              |              | ADDR is floating – Pin control mode;                                                           |

| 22                     | ADDR         | I            |                                                                                                |

|                        |              |              | ADDR=VDD $-I^2C$ enabled with ADDR bit 6 equal to 1;                                           |

| 22                     | LIDLIGDEE    |              | ADDR=GND – I <sup>2</sup> C enabled with ADDR bit 6 equal to 0                                 |

| 23                     | VBUSDET      | I            | VBUS detection                                                                                 |

|                        |              |              | I <sup>2</sup> C communication data signal.                                                    |

|                        |              |              | Dual function as open drain Type-C Current Mode Detect 1 in pin control                        |

|                        |              |              | mode when port is a device;                                                                    |

| 24                     | SDA/OUT1     | I/O          | OUT2 OUT1 Current Mode                                                                         |

|                        |              |              | Hi-Z Hi-Z Default                                                                              |

|                        |              |              | Hi-Z Low Medium                                                                                |

|                        |              |              | Low Low High                                                                                   |

| Thermal Pad            | GND          | Ground       | Ground                                                                                         |

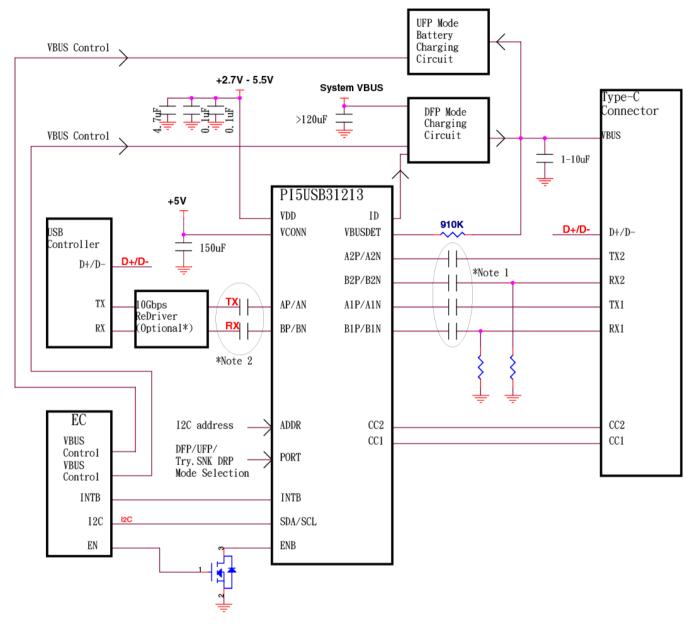

\*Note 1: USB 3.1 spec requires the TX signals are RX signals are AC coupled to support non-

AC coupled. complaint Type-C devices.

\*Note 2: TX signals are AC coupled if ReDriver TX RX signals are AC coupled if ReDriver RX

bias level is >0.8V. bias level is >0.8V.

# PI5USB31213 - Typical Application Circuit

## **Maximum Ratings**

| 65°C to +150°C     |

|--------------------|

| 0.5V to +6.0V      |

| 0.5V to +3V        |

| 10mA               |

| 2000V              |

| 3mA                |

| 0.1mA              |

| Internally Limited |

|                    |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

**Recommended Operation Conditions**

| Symbol                  | Parameter                                          | Min.    | Max.    | Units |

|-------------------------|----------------------------------------------------|---------|---------|-------|

| $V_{ m DD}$             | Battery Supply Voltage                             | 2.7     | 5.5     | V     |

| $V_{\mathrm{BUS}}$      | System VBUS Voltage                                | 4       | 28      | V     |

| $V_{\mathrm{BAT\_TH}}$  | Battery Supply Under-Voltage Lockout, falling edge | 2.2     | 2.65    | V     |

| $V_{CONN}$              | VCONN Supply Voltage Range                         | 2.7     | 5.5     | V     |

| $V_{SWCM}$              | Switch I/O Common Mode Voltage                     | 0       | 2       | V     |

| $V_{ m IH}$             | High level input voltage (SCL, SDA, ENB)           | 1.05    |         | V     |

| $V_{ m IL}$             | Low level input voltage (SCL, SDA, ENB)            |         | 0.4     | V     |

| V3 <sub>IH</sub>        | High level input voltage (ADDR,PORT)               | VDD-0.4 |         | V     |

| V3 <sub>IL</sub>        | Low level input voltage (ADDR,PORT)                |         | 0.4     | V     |

| V <sub>IN CC12</sub>    | CC1, CC2 input voltage <sup>(1)</sup>              |         | VDD+0.5 | V     |

| V <sub>IN_VBUSDET</sub> | VBUSDET input voltage <sup>(2)</sup>               |         | 4.5     | V     |

| $T_{A}$                 | Operating Temperature                              | -40     | 85      | °C    |

Note:

### **DC Electrical Characteristics**

Min and Max apply for  $T_A$  between -40°C to 85°C and  $T_J$  up to +125°C (unless otherwise noted). Typical values are referenced to  $V_{DD}$ =3.6V,  $T_A$ =+25°C

| Symbol                           | Parameter                                            | Test Conditions                                   | Min.    | Tym  | Max. | Units |  |

|----------------------------------|------------------------------------------------------|---------------------------------------------------|---------|------|------|-------|--|

|                                  |                                                      | Test Conditions                                   | IVIIII. | Тур. | Max. | Units |  |

| USB SuperSpee                    | ed Switches (Axp, Axn, Bxp, Bxn)                     |                                                   |         |      | 1    |       |  |

| R <sub>SSON</sub> <sup>(1)</sup> | USB3.0 SS TX/RX Switch On-<br>Resistance             | $I_{LOAD} = -8mA, V_{in} = 0V$                    | -       | 6    | 9    | Ω     |  |

| $R_{SSBIAS}$                     | USB3.0 DC Bias Resistance to Ground                  |                                                   | -       | 200  | -    | kΩ    |  |

| CC1/CC2 Confi                    | iguration(Device mode, SNK)                          |                                                   |         |      |      |       |  |

| $R_{\mathrm{D}}$                 | Device mode pull down resistor                       |                                                   | 4.6     | 5.1  | 5.6  | kΩ    |  |

| $V_{TH3\_SNK}$                   | High current mode entry threshold                    |                                                   | 1.16    | 1.23 | 1.31 | V     |  |

| $V_{TH2\_SNK}$                   | Medium current mode entry threshold                  |                                                   | 0.61    | 0.66 | 0.70 | V     |  |

| V <sub>TH1_SNK</sub>             | Default current mode entry threshold                 |                                                   | 0.15    | 0.2  | 0.25 | V     |  |

| CC1/CC2 Confi                    | iguration(Host mode, SRC)                            |                                                   |         |      |      |       |  |

|                                  |                                                      | Default current mode                              | 64      | 80   | 96   | μΑ    |  |

| $I_P$                            |                                                      | Medium current mode (1.5A)                        | 166     | 180  | 194  |       |  |

|                                  |                                                      | High current mode (3A)                            | 304     | 330  | 356  |       |  |

| VBUS Detection                   | 1                                                    |                                                   |         |      |      |       |  |

| $V_{ m VBUS}$                    | VBUS detection threshold                             | Rvbus=910kohm                                     | 2.5     | 3.0  | 4.0  | V     |  |

| VCONN                            |                                                      |                                                   |         |      |      |       |  |

| R <sub>VCONN</sub>               | VCONN switch on-resistance                           | $I_{LOAD} = 100 \text{mA}, V_{CONN} = 5 \text{V}$ | -       | 0.5  | 0.6  | Ω     |  |

| I <sub>VCONN@80%</sub>           | VCONN output current at 80% VCONN                    | V <sub>CONN</sub> = 5V, Vcc1 or Vcc2=4.5V         | 500     | 570  | 650  | mA    |  |

| V <sub>OVP</sub>                 | VCONN over voltage protection                        |                                                   | 5.8     | 6.0  | 6.2  | V     |  |

| Host Interface l                 | Pins (INTB,ID,OUT1,OUT2,OUT3)                        |                                                   | •       | •    | •    |       |  |

| V <sub>OL</sub>                  | Output Low Voltage at 1.6mA Sink current(Open-Drain) |                                                   | 0       | -    | 0.4  | V     |  |

<sup>(1)</sup> CC1 and CC2 are internally clamped to ~VDD+1.0V.

<sup>(2)</sup> VBUSDET is internally clamped to ~5.5V

| Symbol                 | Parameter                         | Test Conditions                             |    | Тур. | Max. | Units |

|------------------------|-----------------------------------|---------------------------------------------|----|------|------|-------|

| $I_{OFF}$              | Off-state leakage current         | V <sub>INTB.ID/ID/OUT1/OUT2/OUT3</sub>      | -  | -    | 1    | μA    |

| <b>Input Control I</b> | Pins (ENB, ADDR, PORT, SCL, SDA)  |                                             |    |      |      |       |

| $I_{\mathrm{IH}}$      | High-level input current          |                                             | -5 | -    | 5    | μA    |

| $ m I_{IL}$            | Low-level input current           |                                             | -5 | -    | 5    | μA    |

| <b>Current Consu</b>   | mption                            |                                             |    |      |      |       |

|                        | operating current, Device mode    | SNK connects to SRC                         | -  | 200  | 300  | μA    |

| $I_{DD}$               | operating current. Host mode      | SRC connects to SNK Default current mode    | -  | 280  | 400  | μΑ    |

| I <sub>DEV_STBY</sub>  | Device mode standby current       | V <sub>DD</sub> =3.6V, Floating CC1 and CC2 | -  | 45   | 65   | μΑ    |

| I <sub>DUAL_STBY</sub> | II Juai-Roie mode standby current | $V_{DD}$ =3.6V, Floating CC1 and CC2        | -  | 55   | 75   | μΑ    |

| I <sub>HOST_STBY</sub> | Host mode standby current         | $V_{DD}$ =3.6V, Floating CC1 and CC2        |    | 65   | 85   | μΑ    |

| I <sub>DISABLE</sub>   | Chip is disabled ENB=VDD          |                                             | -  |      | 5    | μA    |

| Thermal Shutd          | own                               |                                             |    |      |      |       |

| $T_{OTP}$              | Thermal shutdown threshold        |                                             | -  | 155  | -    | °C    |

| $T_{hys}$              | Thermal shutdown hysteresis       |                                             | -  | 20   | -    | °C    |

Note:

## **AC Electrical Characteristics**

Min and Max apply for  $T_A$  between -40°C to 85°C and  $T_J$  up to +125°C (unless otherwise noted). Typical values are referenced to  $T_A$ =+25°C,  $V_{DD}$ =3.8V.

| Symbol                       | Parameter                          | <b>Test Conditions</b> | Min. | Typ. | Max. | Units |

|------------------------------|------------------------------------|------------------------|------|------|------|-------|

| $\mathrm{BW}_{\mathrm{USB}}$ | -3dB Differential Bandwidth of USB |                        | -    | 8    | -    | GHz   |

|                              | channel                            |                        |      |      |      |       |

| $I_{L}$                      | Differential insertion loss        |                        | -    | -1.9 | -    | dB    |

| $R_{\mathrm{L}}$             | Differential return loss           | f=5GHz, Vcm=0V         | -    | -11  | -    | dB    |

| $X_{TALK}$                   | Differential crosstalk             |                        | -    | -30  | -    | dB    |

| $T_{on}$                     | Turn-On Time                       |                        | -    | 20   | -    | μs    |

| ${ m T}_{ m off}$            | Turn-Off Time                      |                        | -    | 1    | -    | μs    |

Capacitance ( $T_A = -40$ °C to 85°C)

| Symbol       | Parameter                             | Test Conditions | Min. | Тур. | Max. | Units |

|--------------|---------------------------------------|-----------------|------|------|------|-------|

| $C_{ONUSB}$  | TXn+, TXn- On Capacitance (USB Mode)  |                 | -    | 1.5  | -    | pF    |

| $C_{ m off}$ | TXn+, TXn- OFF Capacitance (USB Mode) |                 | -    | 1    | -    | pF    |

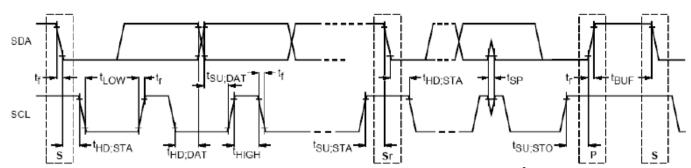

# I<sup>2</sup>C AC Electrical Characteristics

| Symbol            | Parameter                                                         | Fast Mode | Units |        |

|-------------------|-------------------------------------------------------------------|-----------|-------|--------|

| Symbol            | rarameter                                                         | Min.      | Max.  | Ullits |

| $f_{SCL}$         | SCL Clock Frequency                                               | 0         | 400   | kHz    |

| $t_{ m HDSTA}$    | Hold Time (Repeated) START Condition                              | 0.6       | -     | μs     |

| $t_{LOW}$         | LOW Period of SCL Clock                                           | 1.3       | -     | μs     |

| $t_{ m HIGH}$     | HIGH Period of SCL Clock                                          | 0.6       | -     | μs     |

| $t_{SETSTA}$      | Set-up Time for Repeated START Condition                          | 0.6       | -     | μs     |

| $t_{ m HDDAT}$    | Data Hold Time                                                    | 0         | 0.9   | μs     |

| $T_{SUDAT}$       | Data Set-up Time                                                  | 250       | -     | ns     |

| $t_{\rm r}$       | Rise Time of SDA and SCL Signals                                  | -         | 300   | nc     |

| $t_{\mathrm{f}}$  | Fall Time of SDA and SCL Signals                                  | -         | 300   | ns     |

| $t_{SETSTO}$      | Set-up Time for STOP Condition                                    | 0.6       | -     | μs     |

| $t_{ m BUF}$      | Bus-Free Time between STOP and START Conditions                   | 1.3       | -     | μs     |

| $t_{\mathrm{SP}}$ | Pulse Width of Spikes that Must Be Suppressed by the Input Filter | 0         | 50    | ns     |

<sup>1.</sup> On-resistance is the voltage drop between the two terminals at the indicated current through the switch.

Figure 3. Definition of Timing for Full-Speed Mode Devices on the I<sup>2</sup>C Bus

## Table 1. I<sup>2</sup>C Slave Address

| Name                  | Size (Bits) | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------------------|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Slave Address(ADDR=1) | 0           | 0     | 1     | 0     | 1     | 1     | 0     | 1     | R/W   |

| Slave Address(ADDR=0) | 8           | 0     | 0     | 0     | 1     | 1     | 0     | 1     | R/W   |

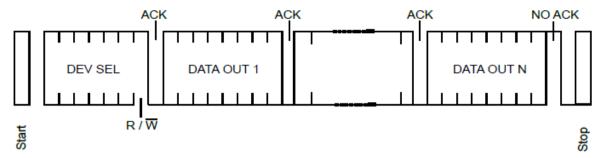

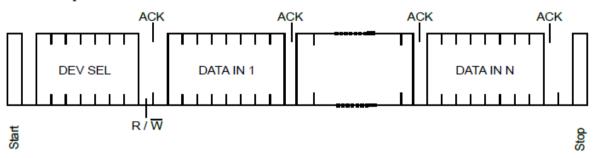

## I<sup>2</sup>C Data Transfer

## 1. Read Sequence

## 2. Write Sequence

### Note:

1. PI5USB31213 does not have offset byte. All registers must be read or written sequentially from 0x00. For example, in order to read address 0x04, PI5USB31213 I2C registers must be read sequentially from 0x01, 0x02, 0x03 to 0x04. In order to write address 0x02, it must be written sequentially from 0x01 to 0x02.

## **Detailed Description**

#### **ADDR**

ADDR is a tri-level input pin to indicate I2C or pin control (or GPIO) mode. When ADDR pin is floating, the part is set to pin control mode. When ADDR is set to VDD or GND, I2C mode is enabled, and bit 6 of I2C address is equal to 1 or 0 according to ADDR set to VDD or GND (see Table 1: I2C Slave Address).

### Configuration

The PI5USB31213 requires minimal configuration for proper detection and reporting. Write register 0x02 (Control Register) to configure different charging profiles and port settings.

#### **Processor Communication**

Processor shall use following procedure to process PI5USB31213 interrupt request:

- 1. INTB asserted LOW, indicating Type-C port status change.

- 2. Processor first masks PI5USB31213 interrupt by writing a '1' to Bit 0 of Control Register(0x02). INTB returned high.

- 3. Processor then read Register(0x01), Control Register (0x02), Interrupt Register(0x03) and CC Status Register(0x04). Interrupt Register(0x03) indicates if an attach or detach event was detected. All interrupt flags in Interrupt Register will be cleared after the I2C read action. CC Status Register(0x04) is used to determine plugin details and charging profile. Processor can configure the power and USB channels according to information in CC Status Register.

- 4. Processor unmask PI5USB31213 interrupt by writing a '0' to Bit 0 of Address 0x02 before ending the interrupt service routine.

### **Interrupts**

The baseband processor recognizes interrupt signals by observing the INTB signal, which is active LOW. Interrupts are masked upon bit 0 of Control Register 0x02 (Interrupt Mask Bit). After the Interrupt Mask Bit is cleared by the baseband processor, the INTB pin is hi-z in preparation for a future interrupt. When an interruptible event occurs, INTB transitions LOW and returns hi-z when the processor reads the Interrupt Register (0x03). Subsequent to the initial power up or reset; if the processor writes a "1" to Interrupt Mask Bit when the system is already powered up, the INTB pin stays hi-z and ignores all interrupts until the Interrupt Mask Bit is cleared.

Besides monitoring the I<sup>2</sup>C registers, the system can also monitor ID pin and VBUS for connector status. If the port is configured as a device (or dual-role acting as device), VBUS will go to 5V when host attachment is detected. If the port is configured as a host (or dual-role acting as host), ID pin will pull low when device attachment is detected, and system should assert VBUS.

#### **Port Setting (Host/Device/Dual-Role)**

When power is applied to VDD, an internal Power-On Reset (POR) holds the PI5USB31213 in a reset condition until VDD has reached 2.7V. At that point, the reset condition is released and the PI5USB31213 registers and I<sup>2</sup>C-bus state machine will initialize to their default states. [2:1] of Control Register (0x02) are initialized according to the PORT pin setting (see Table 3 I<sup>2</sup>C Register Table). Type-C connector can be configured as host, device or dual-role port per the register. After power up, the port setting can still be changed by I2C writes to Bits [2:1] of Control Register (0x02). Thereafter, VDD must be lowered below 1.0V to reset the device (both registers and I<sup>2</sup>C-bus state machine).

PI5USB31213 connects current sources to CC1 and CC2 when operating in host mode. It will also set the current level according to the charging current setting. In device mode, PI5USB31213 will connect two integrated resistor Rd1 and Rd2 to CC1 and CC2 respectively. Dual-Role mode enables CC1 and CC2 toggle between host mode and device mode alternatively every 50ms. The toggling will stop after connection is made and role negotiated.

### **Current Mode Setting and Detection**

Type-C connector can be configured as different current modes per CC1/CC2 setting. Host mode (or dual role acting as Host) allows the system to configure between high current mode (3A), medium current mode (1.5A) and default current mode. Different current modes can be set by writing control register (x02h). When in Device mode (or dual role acting as device), CC1/CC2 pins allow the system to detect the host charging capability. The charging capability is reported in CC Status Register (0x04) which can help the system configure the charging current accordingly.

#### ID

When PI5USB31213 is configured as host mode (or dual role acting as host), ID pin will be pulled low when a device is attached to the type-C connector. The ID pin will work as interrupt signal to acknowledge system when there is device attachment. It should be noted the ID pin will not be driven low when an audio or debug accessory is detected, and ID pin will always stay hi-z when port is in device mode.

#### **Audio and Debug Accessory**

PI5USB31213 can detect Audio or Debug Accessory attachment as per CC1/CC2 setting. This is reported in CC Status Register (0x04) to help system configure Audio Adapter Accessory and Debug Accessory Mode accordingly.

### **VBUS Detection**

PI5USB31213 detects VBUS to determine the attached state when port is a device. A 910kohm +/- 5% is required to connect VBUS of the connector to VBUSDET input pin to protect the IC from the possible high voltage of VBUS during alternative mode.

#### **ENB**

ENB is an active low enable input pin. When ENB pin is high, part is in disable and low power state. All outputs, with the exception of CC1, CC2, SCL & SDA are in High-Z state. CC1 and CC2 pins are pulled low with resistors Rd in disable state. I<sup>2</sup>C port will also be reset during disable state. SCL & SDA are still functional when the part is disable and ADDR is not floating. I2C port will also reset during every transition (rising or falling edge) of ENB. Connection State will also be reset and forced to be "DISABLED" state. However, disable has no effect on the value of Register 02H (Control).

When ENB pin is low, part is enabled. The connection state will activate and detection will restart.

### **Dead Battery startup**

PI5USB31213 ensures dead battery charging when VDD=0V. Both CC1 and CC2 will be pulled down when VDD=0V. Such configuration helps other host port detect the dead battery port as a device mode port and enable charging through VBUS.

#### VCONN Power Path at CC1/CC2 Pin

PI5USB31213 offers low-resistance switch path between CC1/CC2 to VCONN pin for powering accessories or active cables. There are over-voltage, over-current and thermal protections online to protect the system from fault connection.

#### VCONN Fault Condition Trigger and Recover

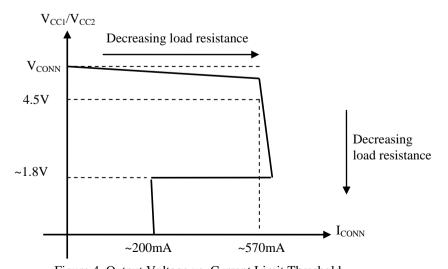

Over-current protection is online in PI5USB31213 to protect VCONN from being drawn a continuous current exceeding 700mA. Graph below further describes the characteristic of the over-current protection scheme. If the voltage at CC1/CC2 is lower than ~1.8V, the current limit will further be reduced down to 200mA. When the current limit is hit (OCP event), PI5USB31213 pulls low INTB pin to acknowledge the processor a fault condition happened.

Figure 4. Output Voltage vs. Current Limit Threshold

## **Power Delivery Communication**

*USB Power Delivery* is a feature on the USB Type-C connector. When *USB PD* is implemented, *USB PD* Bi-phase Mark Coded (BMC) carried on the CC wire shall be used for *USB PD* communications between USB Type-C ports.

At attach, VBUS shall be operationally stable prior to initiating *USB PD* communications. As a UFP may wait for 200msec to establish a successful connection after VBUS is detected. USB PD communications from DFP should be initiated at least 200msec after VBUS is turned on and stable. Otherwise, the connection may not be successfully established until USB PD communication is finished.

## **Pin Control Functional Description**

### **Type-C connector port setting (PORT)**

Type-C connector can be configured as different ports by changing PORT pin voltage level.

Table 2A. Port Setting

| Port setting                             | PORT          |

|------------------------------------------|---------------|

| Device (SNK)                             | GND           |

| <b>Dual-role port (DRP) with Try.SNK</b> | No Connection |

| Host (SRC)                               | VDD           |

### Type-C connector current mode detection (OUT1, OUT2)

Type-C connector can detect different host current modes and other accessories per CC1/CC2 setting. When PI5USB31213 operates in device mode (or dual role mode acting as device), it detects CC1/CC2 status to determine host charging current modes and reports to the system using OUT1 and OUT2 pins. OUT1 and OUT2 will always stay hi-z unless medium or high current mode is detected.

Table 2B. Current Mode Detection

|                            | OUT2 | OUT1 |

|----------------------------|------|------|

| Default current mode       | Hi-Z | Hi-Z |

| Medium current mode (1.5A) | Hi-Z | Low  |

| High current mode (3A)     | Low  | Low  |

#### Type-C Connector current mode setting in host mode

When PI5USB31213 is configured as a host, the current mode can only be set to Default Current Mode(current source Ip=80uA). I2C control is required to set current mode to 1.5A or 3A.

### **Audio Adapter Accessory Detection (OUT3)**

PI5USB31213 detects analog audio adapter attachment as per CC1/CC2 setting. This is reported by the OUT3 pin. OUT3 will be pulled low when an analog audio adapter attachment is detected. Otherwise, OUT3 will stay hi-z.

**Table 2C. Audio Adapter Accessory Detection**

| Audio Accessory | OUT3 |

|-----------------|------|

| Detected        | Low  |

| Not Detected    | Hi-Z |

### ADDR, ID, ENB, and Dead Battery Startup

Functionality of the ADDR, ID, and ENB pins are the same for pin control or I2C control modes. Dead Battery Startup operation is also the same for pin control and I2C control modes. Please refer to previous section for detail description.

Table 3. I<sup>2</sup>C Register

|         | I <sup>2</sup> C Register |                                                                                           | T = 0                       | ·                          |

|---------|---------------------------|-------------------------------------------------------------------------------------------|-----------------------------|----------------------------|

| Address | Name                      | Description                                                                               | Default Value               | Type                       |

| 0x01    | Device ID                 | Bits [7:3] = Version ID                                                                   | 08h                         | R                          |

|         |                           | 00001 = Product version                                                                   |                             |                            |

|         |                           | 00001 – Hoddet version                                                                    |                             |                            |

|         |                           | Bits [2:0] = Vendor ID(Pericom)                                                           |                             |                            |

|         |                           |                                                                                           |                             |                            |

|         |                           | 000 = Pericom                                                                             |                             |                            |

| 0x02    | Control                   | Bit 7 = Powersaving                                                                       | 00h                         | R/W                        |

|         |                           | O. Frankla / Antion retate                                                                | Upon power-up,              |                            |

|         |                           | 0 = Enable/Active state<br>1 = Disable and low power state                                | Bits [2:1] are initialized  |                            |

|         |                           | In Disable and low power state, all outputs of PI5USB31213, with the                      | according to PORT           |                            |

|         |                           | exception of CC1 and CC2 pins, are in High-Z State. CC1 and CC2 pins                      | pin setting as              |                            |

|         |                           | are pulled low with resistor Rd.                                                          | follows:                    |                            |

|         |                           |                                                                                           |                             |                            |

|         |                           | Bits [6] = Dual role 2 Try.SRC or Try.SNK setting                                         | PORT Bits                   |                            |

|         |                           |                                                                                           | pin [2:1]                   |                            |

|         |                           | 0 = Enable Try.SRC supported                                                              | initial                     |                            |

|         |                           | 1 = Enable Try.SNC supported                                                              | settins                     |                            |

|         |                           | Dita [5] - Accessory Detection in Device Mode                                             | GND 00                      |                            |

|         |                           | Bits [5] = Accessory Detection in Device Mode                                             | VDD   01<br>  Float   10    |                            |

|         |                           | 0 = Disable                                                                               | Float 10                    |                            |

|         |                           | 1 = Enable                                                                                | Note: This                  |                            |

|         |                           |                                                                                           | initialization only         |                            |

|         |                           | Bits [4:3] = Charging current mode                                                        | happens once when           |                            |

|         |                           | System can set the charging current mode when port is a host or dual role                 | PI5USB31213 is              |                            |

|         |                           | acting as host. These bits are ignored when port is a device or dual role                 | powered up. Bits            |                            |

|         |                           | acting as device.                                                                         | [2:1] can be                |                            |

|         |                           | 00 = Default current mode                                                                 | changed by I <sup>2</sup> C |                            |

|         |                           | 01 = Medium current mode (1.5A)                                                           | command                     |                            |

|         |                           | 10 = High current mode (3A)                                                               | afterwards.                 |                            |

|         |                           |                                                                                           |                             |                            |

|         |                           | Bits [2:1] = Port setting                                                                 |                             |                            |

|         |                           | System can set the role of the port.                                                      |                             |                            |

|         |                           | 00 - Davies (CNIV)                                                                        |                             |                            |

|         |                           | 00 = Device (SNK)<br>01 = Host (SRC)                                                      |                             |                            |

|         |                           | 10 = Dual Role (DRP)                                                                      |                             |                            |

|         |                           | 11 = Dual Role 2 (DRP) where Try.SRC or Try.SNC is supported                              |                             |                            |

|         |                           | , , , , , , , , , , , , , , , , , , ,                                                     |                             |                            |

|         |                           | Bit 0 = Interrupt Mask                                                                    |                             |                            |

|         |                           | INTB pin is used to acknowledge system if there is any interrupt events                   |                             |                            |

|         |                           | triggered. When this bit is set to 0, INTB pin is pulled low when an interrupt            |                             |                            |

|         |                           | event occur. When this bit is set to 1, INTB pin ignores all interrupt and remain High-Z. |                             |                            |

|         |                           | Tomani riigii-Z.                                                                          |                             |                            |

|         |                           | 0 = Do not mask interrupt                                                                 |                             |                            |

|         |                           | 1 = Mask interrupt                                                                        |                             |                            |

| 0x03    | Interrupt                 | Bit 7 = Fault condition recovery                                                          | 00h                         | Clearable read             |

|         |                           | This bit indicates if VCONN recover from fault conditions including OCP,                  |                             | only.                      |

|         |                           | OVP, OTP                                                                                  |                             | Bits[7:0] are cleared when |

|         |                           | 0 = Fault event not recovered                                                             |                             | Byte 3 is read.            |

|         |                           | 1 = Fault event recovered                                                                 |                             | Dyw 5 is iteau.            |

|         |                           |                                                                                           |                             |                            |

|         |                           | Bit 6 = OCP event                                                                         |                             |                            |

|         |                           | VCONN over-current protection indicator                                                   |                             |                            |

|         |                           | a N ogp                                                                                   |                             |                            |

|         |                           | 0 = No OCP event<br>1 = OCP event detected                                                |                             |                            |

|         |                           | 1 = OCP event detected                                                                    |                             |                            |

|         |                           |                                                                                           |                             |                            |

|         |                           |                                                                                           | l .                         | l .                        |

| Address | Name      | Description                                                                                         | Default Value | Type |

|---------|-----------|-----------------------------------------------------------------------------------------------------|---------------|------|

| 0x03    | Interrupt | Bit 5 = OVP event                                                                                   |               |      |

|         |           | VCONN over-voltage protection indicator                                                             |               |      |

|         |           |                                                                                                     |               |      |

|         |           | 0 = No OVP event                                                                                    |               |      |

|         |           | 1 = OVP event detected                                                                              |               |      |

|         |           | Bit $4 = $ Reserved. Read 0's.                                                                      |               |      |

|         |           | Bit 7 - Reserved. Read 0 3.                                                                         |               |      |

|         |           | Bit 3 = OTP event                                                                                   |               |      |

|         |           | VCONN over-temperature protection indicator                                                         |               |      |

|         |           | a N off                                                                                             |               |      |

|         |           | 0 = No OTP event<br>1 = OTP event detected                                                          |               |      |

|         |           | 1 – OTF evenit detected                                                                             |               |      |

|         |           | Bit 2 = Fault Ocurring.                                                                             |               |      |

|         |           |                                                                                                     |               |      |

|         |           | 0 = No fault is occurring                                                                           |               |      |

|         |           | 1 = Fault(s) is occurring                                                                           |               |      |

|         |           | *This hit will be not an along man med times and dison. And went't be                               |               |      |

|         |           | *This bit will be set or clear per real time condition. And won't be                                |               |      |

|         |           | cleared by I2C reading. No interrupt will be reported by the change of this bit.                    |               |      |

|         |           | of this bit.                                                                                        |               |      |

|         |           | Bit 1 = Detach event                                                                                |               |      |

|         |           | When this bit is set to 1, it indicates the unplug action. The port changes                         |               |      |

|         |           | from attached state (Attached.SNK, Attached.SRC, AudioAccessory or                                  |               |      |

|         |           | DebugAccessory state) to unattached state.                                                          |               |      |

|         |           | D'(0 A() 1                                                                                          |               |      |

|         |           | Bit 0 = Attach event When this bit is set to 1, it indicates the plug action. The port changes from |               |      |

|         |           | unattached state to attached state.                                                                 |               |      |

| 0x04    | CC status | Bit 7 = VBUS detection                                                                              | 00h           | R    |

|         |           | This bit reports VBUS status when PI5USB31213 is in device mode, dual                               |               |      |

|         |           | role mode acting as device or accessory mode.                                                       |               |      |

|         |           | O VIDIO (1) (1)                                                                                     |               |      |

|         |           | 0 = VBUS not detected<br>1 = VBUS detected                                                          |               |      |

|         |           | 1 – VBOS detected                                                                                   |               |      |

|         |           | Bits [6:5] = Charging current detection                                                             |               |      |

|         |           | These bits report the detected host charging current status when port is a                          |               |      |

|         |           | device or dual role acting as device.                                                               |               |      |

|         |           | 00 - Standby                                                                                        |               |      |

|         |           | 00 = Standby<br>01 = Default current mode                                                           |               |      |

|         |           | 10 = Medium current mode (1.5A)                                                                     |               |      |

|         |           | 11 = High current mode (3A)                                                                         |               |      |

|         |           |                                                                                                     |               |      |

|         |           | Bits [4:2] = Attached port status                                                                   |               |      |

|         |           | 000 = Standby                                                                                       |               |      |

|         |           | 000 = Standay<br>001 = Device                                                                       |               |      |

|         |           | 010 = Host                                                                                          |               |      |

|         |           | 011 = Audio Adapter Accessory                                                                       |               |      |

|         |           | 100 = Debug Accessory                                                                               |               |      |

|         |           | Rite [1:0] - Plug polarity                                                                          |               |      |

|         |           | Bits [1:0] = Plug polarity                                                                          |               |      |

|         |           | 00 = Standby                                                                                        |               |      |

|         |           | 01 = CC1 makes connection                                                                           |               |      |

|         |           | 10 = CC2 makes connection                                                                           |               |      |

|         |           | 11 = Undetermined (e.g. AudioAccessory, DebugAccessory or other                                     |               |      |

|         |           | undetermined connections)                                                                           |               |      |

March 2018

# **Register Table**

| Address       | Register                           | Туре                         | Reset<br>Value                                   | Bit 7                                                 | Bit 6                                                | Bit 5                                    | Bit 4                                                                          | Bit 3                                                      | Bit 2                                                                     | Bit 1                                                      | Bit 0          |

|---------------|------------------------------------|------------------------------|--------------------------------------------------|-------------------------------------------------------|------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------|----------------|

| 01H           | Device<br>ID                       | Read                         | 00001000                                         |                                                       | Version ID: 00001                                    |                                          |                                                                                |                                                            | Vendor ID(Pericom): 000                                                   |                                                            |                |

|               |                                    | trol Read/<br>Write 00000000 |                                                  | Powersaving                                           | Dual-role 2                                          | Accessory<br>Detection in<br>Device Mode | Charging Current mode (Host/Dual-role)                                         |                                                            | Port setting                                                              |                                                            | Interrupt Mask |

| 02H           | Control                            |                              | 0: No<br>Powersaving<br>1:<br>Powersaving        | 0: Try.SRC<br>supported<br>1:<br>Try.SNK<br>supported | 0: Disable<br>1: Enable                              | 00: Default<br>01: Medium<br>10: High    |                                                                                | 00: Device<br>01: Host<br>10: Dual-role<br>11: Dual-role 2 |                                                                           | 0: Does not<br>Mask<br>Interrupts<br>1: Mask<br>Interrupts |                |

|               |                                    |                              |                                                  | Recovery                                              | OCP Event                                            | OVP Event                                |                                                                                | OTP Event                                                  | Fault Occurring*                                                          | Detach                                                     | Attach         |

| 03H Interrupt | pt Read/<br>Clear                  | ad/<br>ear 00000000          | 0: fault event<br>not recovered                  | 0: No OCP<br>event                                    | 0: No OVP<br>event                                   | reserved                                 | 0: No OTP<br>event                                                             | 0: No fault is occurring 0: No                             |                                                                           | Interrupt                                                  |                |

|               |                                    |                              |                                                  | 1: fault event recovered                              | 1: OCP<br>event                                      | 1: OVP event                             | reserved                                                                       | 1: OTP event                                               | 1: Fault(s) is occurring                                                  | 1: detached                                                | 1: attached    |

| 0.411         | Device or in<br>Accessory<br>Mode) |                              | Charging current detection<br>(Port is a Device) |                                                       | Attached Port Status                                 |                                          | Plug polarity                                                                  |                                                            |                                                                           |                                                            |                |

| 04H CC        | CC status                          | Kead                         | aa  00000000                                     | 0: Vbus not<br>detected<br>1: Vbus<br>detected        | 00: Standby<br>01: Default<br>10: Medium<br>11: High |                                          | 000: Standby<br>001: Device<br>010: Host<br>011: Audio<br>100: Debug Accessory |                                                            | 00: Standby<br>01: CC1 connected<br>10: CC2 connected<br>11: undetermined |                                                            |                |

<sup>\*</sup>This bit will be set or clear per real time condition. And won't be cleared by I2C reading. No interrupt will be reported by the change of this bit.

Upon power-up, Bit 1 and Bit 2 of register 02H are initialized according to the pin #3 PORT setting as follows:

| Pin #3 Port Initial Connection    | Bit 2 & Bit 1 of Register 02H initialization |

|-----------------------------------|----------------------------------------------|

| PORT pin is floating – Dual role; | 10                                           |

| PORT pin =VDD – Host;             | 01                                           |

| PORT pin =GND – Device            | 00                                           |

This initialization only happens once when PI5USB31213 is powered up. Bit 1 and Bit 2 of register 02H can be changed by I2C commands afterwards.

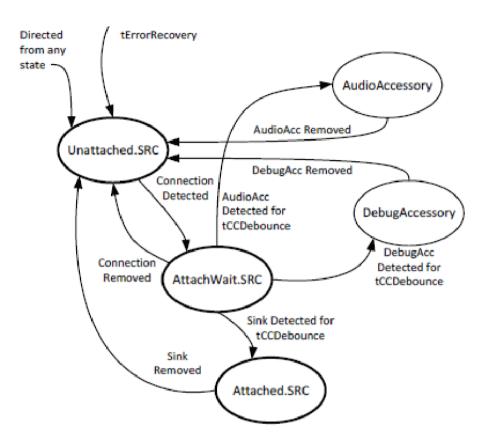

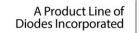

# **Connection State Diagram: SRC**

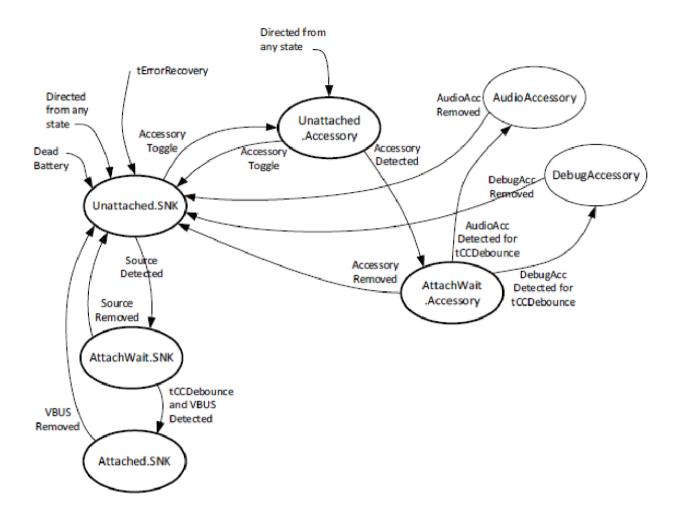

## **Connection State Diagram: SNK**

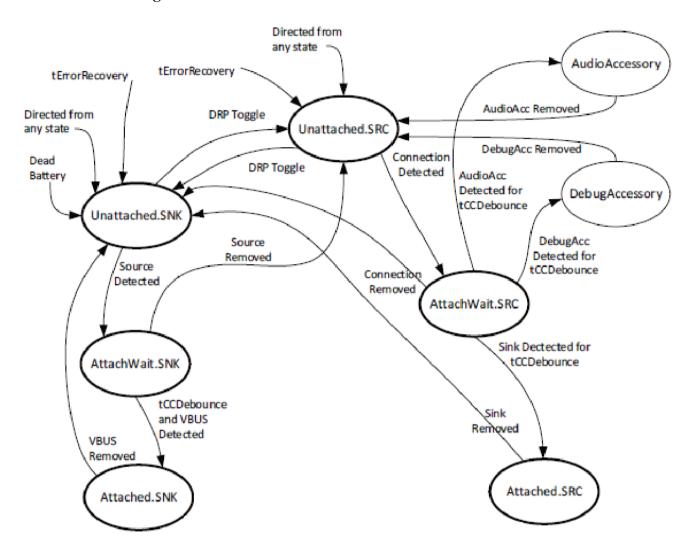

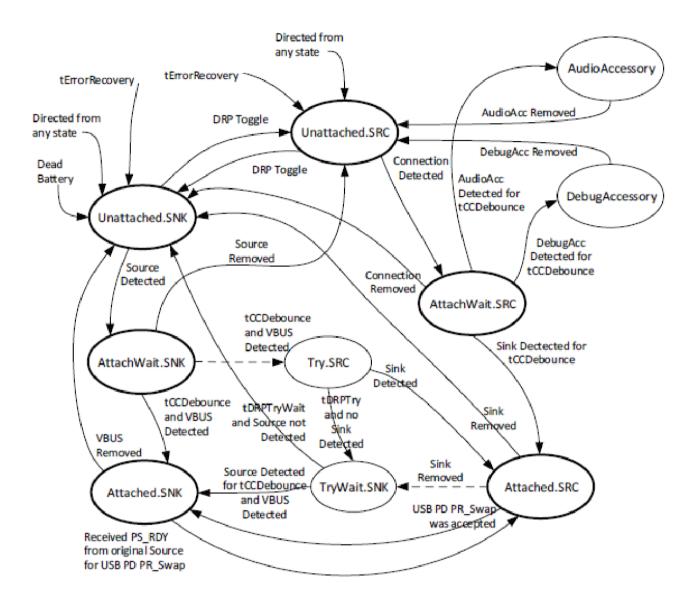

## **Connection State Diagram: DRP**

## Connection State Diagram: DRP with Try.SRC Supported

## Connection State Diagram: DRP with Try.SNK Supported

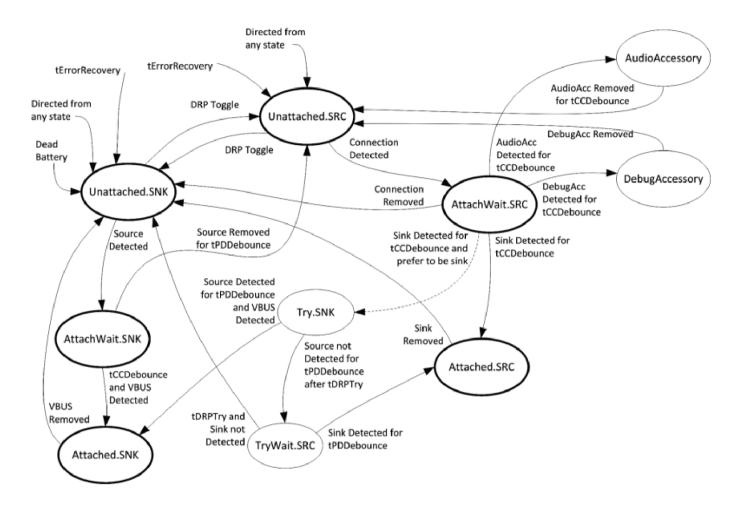

## **Packaging Mechanical**

### TQFN 2 X 4 -24 Contact (X1QFN)

### For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

## Ordering Information<sup>1,2,3</sup>

| Ordering Number Package Code |     | Package Description                           |  |  |

|------------------------------|-----|-----------------------------------------------|--|--|

| PI5USB31213XEAEX             | XEA | 24-contact, Extra Thin Fine Pitch QFN (X1QFN) |  |  |

### Notes:

- Thermal characteristics can be found on the company web site at www.diodes.com/design/support/packaging/

- E = Pb-free and Green

- X suffix = Tape/Reel

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated www.diodes.com