## **Dual Full-Bridge Motor Driver**

#### **Features**

- 750 mA Continuous Output Current

- Load Voltage Supply: 10V to 40V

- Full Bipolar Stepper Motor Drive Capability

- · Bidirectional DC Motor Capability

- Internal Fixed T<sub>OFF</sub> Time PWM Current Control

- · Internal Protection Diodes

- · Internal Thermal Shutdown

- · Under Voltage Lockout

- LS-TTL Compatible Logic Inputs with Pull-Up Resistors

- Low RON Output Resistance

- · Low Quiescent Current

- Operating Temperature Range: -20°C to +85°C

- Pin Compatible with Allegro 6219

#### **Applications**

- · Stepper Motor Actuators

- · DC Motor Actuators

- · Automotive HVAC Ventilation

- Automotive Power Seats

**Note:** The MTS62C19A device is formerly a product of Advanced Silicon.

#### **Description**

The MTS62C19A motor driver is a CMOS device capable of driving both windings of a bipolar stepper motor or bidirectionally control two DC motors. Each of the two independent H-bridge outputs is capable of sustaining 40V and delivering up to 750 mA of continuous current. The output current level is controlled by an internal PWM circuit that is configured using two logic inputs, a current sense resistor, and a selectable reference voltage. The H-bridge outputs have been optimized to provide a low output saturation voltage drop.

Full, half, and micro-stepping operations are possible with the PWM current control and logic inputs. The maximum output current is set by a sensing resistor and a user selectable reference voltage. The output current limit is selected using two logic level inputs. The selectable output current limits are 0%, 33%, 67%, or 100% of the maximum output current. Each bridge has a PHASE input signal which is used to control the direction of current flow through the H-bridge and the load.

The H-bridge power stage is controlled by non-overlapping signals which prevent current cross conduction when switching the direction of the current flow. Internal clamp diodes protect against inductive transients. Thermal protection circuitry disables the outputs when the junction temperature exceeds the safe operating limit. No special power-up sequencing is required. Undervoltage Lockout circuitry prevents the chip from operating when the load supply is applied prior to the logic supply.

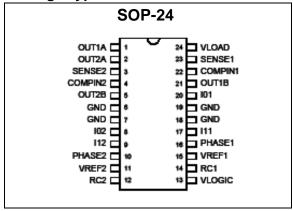

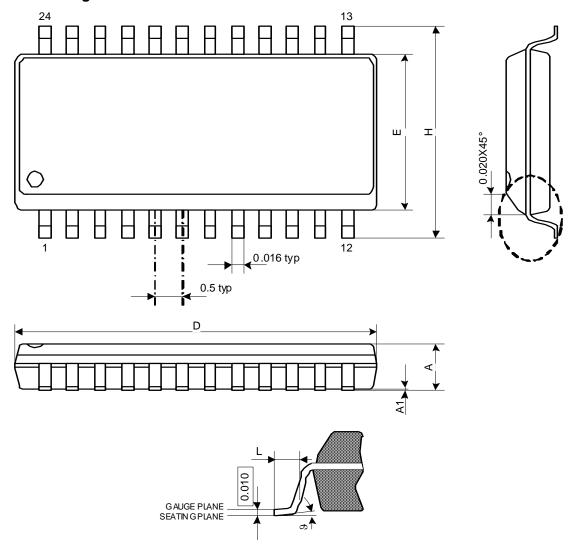

The device is supplied in a 24-pin SOP Package.

### **Package Types**

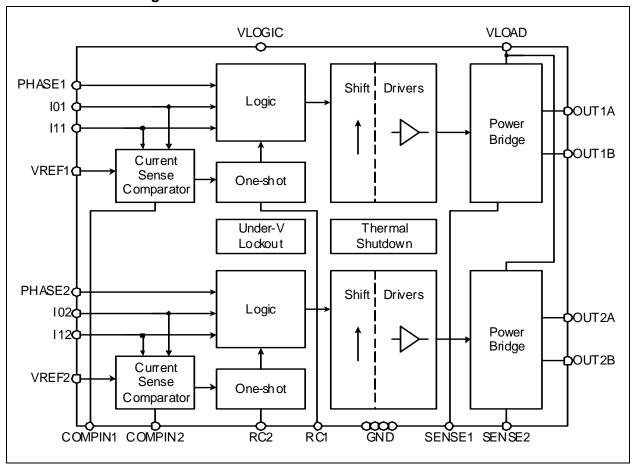

### **Functional Block Diagram**

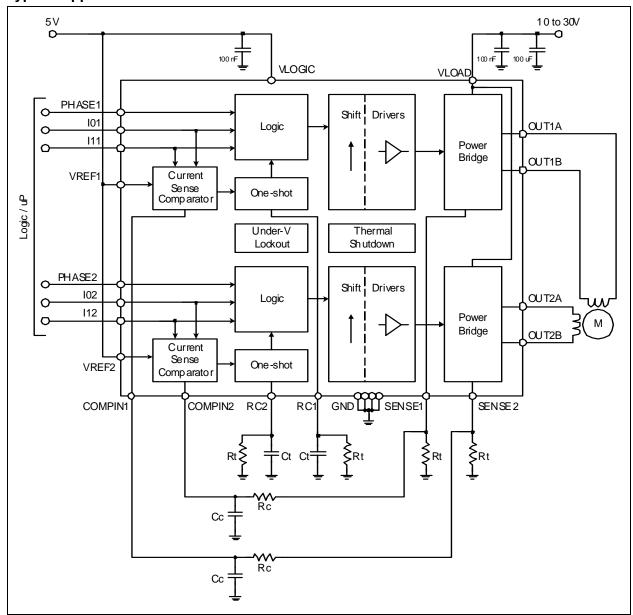

### **Typical Application**

## 1.0 ELECTRICAL CHARACTERISTICS

### **Absolute Maximum Ratings †**

$\label{eq:logic_supply_voltage} \begin{tabular}{llll} Logic Supply Voltage ($V_{LOGIC}$) & $-0.3$ to $+5.5$ V$ Load Supply Voltage ($V_{LOAD}$) & $-0.3$ to $+40.0$ V$ Logic Input Voltage Range ($V_{IN}$) & $-0.3$ to $VLOGIC $+0.3$ V$ V$ REF Voltage Range ($V_{REF}$) & $-0.3$ to $+10.0$ V$ Output Current (Peak) & $\pm 1A$ Output Current (Continuous) & $\pm 0.75A$ Sense Output Voltage & $-0.3$ V to $1.5$ V$ Junction Temperature ($T_{J}$) & $-20^{\circ}$C to $+150^{\circ}$C$ Operating Temperature Range ($T_{OPR}$) & $-20^{\circ}$C to $+85^{\circ}$C$ Storage Temperature Range ($T_{STG}$) & $-55^{\circ}$C to $+150^{\circ}$C} \end{tabular}$

† Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

Electrical Specifications: Unless otherwise specified, all limits are established for  $V_{LOGIC} = 4.5V$  to 5.5V,  $V_{LOAD} = 30V$ ,  $V_{REF} = 5V$ ,  ,  $V_{REF} =$

| Parameters                                               | Sym                            | Min  | Тур  | Max      | Units | Conditions                                                                    |

|----------------------------------------------------------|--------------------------------|------|------|----------|-------|-------------------------------------------------------------------------------|

| DC Characteristics                                       | 1                              |      | 1    | l .      |       |                                                                               |

| Logic Supply Voltage                                     | $V_{LOGIC}$                    | 4.5  | 5.0  | 5.5      | V     |                                                                               |

| Load Supply Voltage                                      | $V_{LOAD}$                     | 10   | 30   | 40       | V     |                                                                               |

| Logic Supply Current                                     | I <sub>VLOGIC</sub>            | _    | 0.8  | 1.0      | mA    |                                                                               |

| V <sub>REF</sub> Voltage Range                           | $V_{REF}$                      | 1.5  | 5.0  | 7.0      | V     |                                                                               |

| Driver Supply Current                                    | I <sub>VLOAD_ON</sub>          | _    | 0.55 | 1.0      | mA    | Both Bridges ON, No Load                                                      |

|                                                          | I <sub>VLOAD_OFF</sub>         | _    | 0.55 | 1.0      | mA    | Both Bridges Off                                                              |

| Control Logic Input Current (V <sub>IN</sub> = 0V)       | I <sub>IN</sub>                | _    | _    | -70      | μA    | I01,I11,I02,I12,PHASE1,PHASE2, (Note 1)                                       |

| Logic Low Input Voltage                                  | $V_{IL}$                       | _    | _    | 0.8      | V     | I01,I11,I02,I12,PHASE1,PHASE2                                                 |

| Logic High Input Voltage                                 | $V_{IH}$                       | 2.4  | _    | _        | V     | I01,I11,I02,I12,PHASE1,PHASE2                                                 |

| Current Limit Threshold                                  | $V_{REF}V_{SENS}$              | 9.5  | 10   | 10.5     | _     | I0=L,I1=L                                                                     |

| Ratio (V <sub>REF</sub> ÷ V <sub>SENSE</sub> )           | E                              | 13.5 | 15   | 16.5     | _     | I0=H,I1=L                                                                     |

|                                                          | -                              | 25.5 | 30   | 34.5     | _     | I0=L,I1=H                                                                     |

| Driver Output Saturation<br>Voltage V <sub>CE(SAT)</sub> | V <sub>ONN</sub><br>(Low Side) | _    | 0.55 | 0.65     | V     | (Sink) IOUT = +500 mA                                                         |

|                                                          |                                | _    | 0.90 | 1.00     | V     | (Sink) IOUT = +750 mA                                                         |

|                                                          | V <sub>ONP</sub>               | _    | 1.05 | 1.40     | V     | (Source) IOUT = -500 mA                                                       |

|                                                          | (High Side)                    | _    | 1.85 | 2.10     | V     | (Source) IOUT = -750 mA                                                       |

| Clamp Diode Forward Volt-                                | $V_{F\_NDIODE}$                | _    | 0.95 | 1.30     | V     | I <sub>F</sub> = 750 mA                                                       |

| age (Note 2)                                             | V <sub>F_PDIODE</sub>          | _    | 1.00 | 1.30     | V     | I <sub>F</sub> = 750 mA                                                       |

| Driver Output Leakage Cur-                               | I <sub>LEAK</sub>              | _    | _    | -50      | μA    | VOUT = 0V                                                                     |

| rent                                                     |                                | _    | _    | 50       | μΑ    | $V_{OUT} = V_{LOAD}$                                                          |

| Thermal Shutdown Temperature                             | $T_{J\_SHDN}$                  | _    | 170  | _        | °C    |                                                                               |

|                                                          |                                |      |      |          |       |                                                                               |

| AC Characteristics                                       |                                |      |      | <u> </u> |       |                                                                               |

| Cut-off Time (one-shot pulse)                            | T <sub>OFF</sub>               | _    | 50   | 58       | μs    | Rs= $1\Omega$ ,Rc= $1k\Omega$ ,Cc= $820pF$ ,<br>Rt= $56k\Omega$ , Ct= $820pF$ |

| Turn-off Delay                                           | $T_D$                          | _    | 1.5  | 10       | μs    |                                                                               |

|                                                          |                                |      | _    | _        |       |                                                                               |

**Note 1:**  $V_{IN} = 5.0V$  input current given by internal pull-up to Logic Supply.

2: Clamp/Freewheel diode is the intrinsic body-drain diode of the NMOS and PMOS transistors.

## **TEMPERATURE SPECIFICATIONS**

| Parameters                     | Sym               | Min | Тур | Max  | Units | Conditions          |

|--------------------------------|-------------------|-----|-----|------|-------|---------------------|

| Recommended Temperature Ranges |                   |     |     |      |       |                     |

| Junction Temperature Range     | T <sub>J</sub>    | -20 |     | +125 | °C    |                     |

| Operating Temperature Range    | T <sub>A</sub>    | -20 |     | +70  | °C    |                     |

| Thermal Package Resistance     |                   |     |     |      |       |                     |

| Thermal Resistance, SOP-24     | $\theta_{JA}$     | _   | 76  | _    | °C/W  | EIA/JEDEC JESD51-10 |

|                                | $\theta_{\sf JC}$ | _   | 16  | _    | C/VV  |                     |

#### 2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

TABLE 2-1: MTS62C19A PIN FUNCTION TABLE

| Pin No.<br>SOP-24 | Туре   | Name    | Function                                    |  |

|-------------------|--------|---------|---------------------------------------------|--|

| 1                 | Output | OUT1A   | Output 1 'A' Side of Motor Winding          |  |

| 2                 | Output | OUT2A   | Output 2 'A' Side of Motor Winding          |  |

| 3                 | Input  | SENSE2  | Current Sense for Output 2                  |  |

| 4                 | Input  | COMPIN2 | Current Sense Comparator Input for Output 2 |  |

| 5                 | Output | OUT2B   | Output 2 'B' Side of Motor Winding          |  |

| 6                 | Power  | GND     | Negative Logic Supply (Ground)              |  |

| 7                 | Power  | GND     | Negative Logic Supply (Ground)              |  |

| 8                 | Input  | 102     | Output 2 Current Selection Bit 0            |  |

| 9                 | Input  | l12     | Output 2 Current Selection Bit 1            |  |

| 10                | Input  | PHASE2  | Output 2 Phase                              |  |

| 11                | Input  | VREF2   | Output 2 Current Reference                  |  |

| 12                | Input  | RC2     | Output 2 RC Time Constant                   |  |

| 13                | Power  | VLOGIC  | Positive Logic Supply Voltage               |  |

| 14                | Input  | RC1     | Output 1 RC Time Constant                   |  |

| 15                | Input  | VREF1   | Output 1 Current Reference                  |  |

| 16                | Input  | PHASE1  | Output 1 Phase                              |  |

| 17                | Input  | l11     | Output 1 Current Selection Bit 1            |  |

| 18                | Power  | GND     | Negative Logic Supply (Ground)              |  |

| 19                | Power  | GND     | Negative Logic Supply (Ground)              |  |

| 20                | Input  | I01     | Output 1 Current Selection Bit 0            |  |

| 21                | Output | OUT1B   | Output 1 'B' Side of Motor Winding          |  |

| 22                | Input  | COMPIN1 | Current Sense Comparator Input for Output 1 |  |

| 23                | Input  | SENSE1  | Current Sense for Output 1                  |  |

| 24                | Power  | VLOAD   | Positive Load Supply Voltage                |  |

### 2.1 Ground Terminal (GND)

Logic supply ground. Only the driver current flows out of this pin; there is no high current. Minimize voltage drops between this pin and the logic inputs.

### 2.2 Logic Supply Voltage (VLOGIC)

Connect VLOGIC to the logic source voltage. Decouple the supply with a 0.1  $\mu\text{F}$  ceramic capacitor mounted close to the VLOGIC and GND terminals.

### 2.3 Load Supply Voltage (VLOAD)

Connect VLOAD to the motor positive voltage supply. The motor current is supplied through this pin and the selected output transistors.

# 2.4 Current Detection Selection (101, 102, 111, 112)

Comparator input for current threshold detection. The voltage across the sense resistor is fed back to this input through the low pass filter RcCc. The power transistors are disabled when the sense voltage exceeds the reference voltage of the selected comparator. When this occurs the current decays for a time set by RtCt (T<sub>OFF</sub> = 1.1 RtCt).

# 2.5 Current Flow Direction Selection (PHASE1, PHASE2)

Logic input to select the direction of current flow through the load. A "HIGH" logic signal level causes load current to flow from OUTxA to OUTxB. A "LOW" logic level causes load current to flow from OUTxB to OUTxA.

# 2.6 Current Sense Reference (VREF1, VREF2)

Reference voltage for current sense comparator. Determines the level of output current detection together with sensing resistor and inputs I0x, I1x.

# 2.7 Current Sense Input (SENSE1, SENSE2)

Connection to lower sources of output stage for insertion of current sense resistor.

## 2.8 Current Sense Comparator Input (COMPIN1, COMPIN2)

Current sense comparator input.

# 2.9 Output Stage OFF Time (RC1, RC2)

A parallel RtCt network connected to this pin sets the OFF time of the power transistors. The pulse generator is a monostable triggered by the output of the current sense comparator.

# 2.10 Output Stage (OUT1A, OUT2A, OUT1B, OUT2B)

Output connection to "A" side and "B" side of motor windings.

#### 3.0 FUNCTIONAL DESCRIPTION

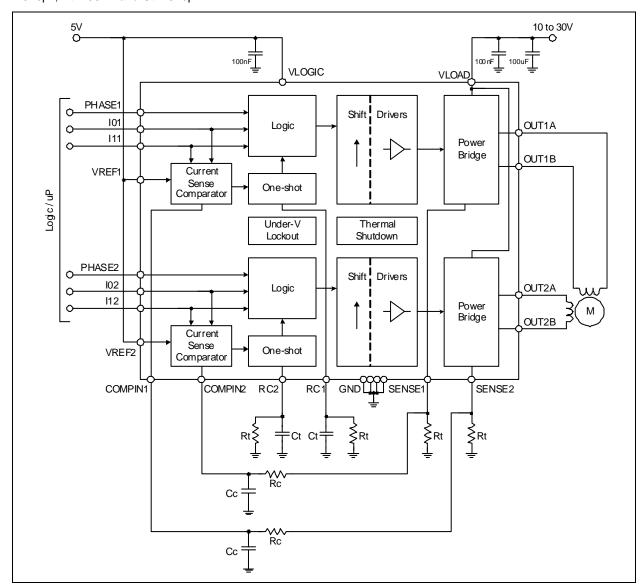

The circuit is designed to drive the two windings of a bipolar stepper motor and can be divided in two identical channels (channel 1 and channel 2) and protection circuitry for over temperature and undervoltage. The functionality of a channel and protection circuitry is presented on next sections.

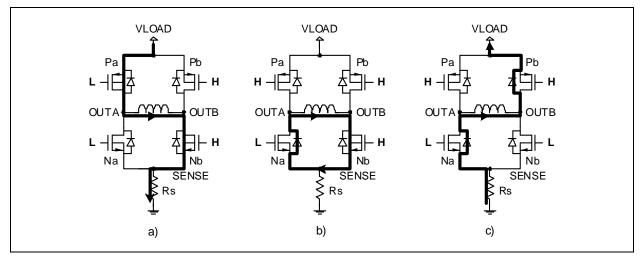

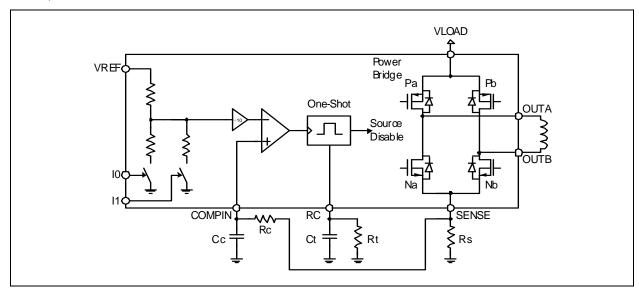

#### 3.1 Power Bridge Operation

Each motor winding is driven by an H-type bridge consisting of two N and two P transistors that allow the current to flow in both winding directions depending on the value of the PHASE signal (Table 3-1). The H-bridge can be set in 5 configurations that are related to the digital inputs PHASE, I0 and I1 and to the current sensed. These configurations are given in Table 3-2.

**FIGURE 3-1:** Power bridge control (PHASE = H / forward): (a) bridge ON, (b) source OFF, and (c) all OFF / coasting (for PHASE = L / reverse: invert A and B in drawings)

TABLE 3-1: CURRENT DIRECTION CONTROL

| Phase | Output Current                    |  |  |  |  |

|-------|-----------------------------------|--|--|--|--|

| L     | Current flows from OUTxB to OUTxA |  |  |  |  |

| Н     | Current flows from OUTxA to OUTxB |  |  |  |  |

TABLE 3-2: POWER BRIDGE GATE CONTROL TRUTH TABLE

| 1011     | PHASE | overi | T <sub>OFF</sub> | Case/Mode               | gna | gpa | gnb | gpb |

|----------|-------|-------|------------------|-------------------------|-----|-----|-----|-----|

| 00/01/10 | 1     | 0     | 0                | Forward ON              | L   | L   | Н   | Н   |

| 00/01/10 | 1     | Х     | 1                | Forward OFF             | L   | Н   | Н   | Н   |

| 00/01/10 | 0     | 0     | 0                | Reverse ON              | Н   | Н   | L   | L   |

| 00/01/10 | 0     | Х     | 1                | Reverse OFF             | Н   | Н   | L   | Н   |

| 11       | Х     | Х     | Х                | No Current/<br>Coasting | L   | Н   | L   | Н   |

**Legend:** Bold = Active MOS Transistors, Overi = Overcurrent flag, T<sub>OFF</sub> = Channel T<sub>OFF</sub> State Flag

#### 3.2 PWM Current Control

The current level in each motor winding is controlled by a PWM circuit with a fixed  $T_{OFF}$  time. The load current flowing in the winding is sensed through an external sensing resistor Rs connected between the power bridge's source pin SENSE (sources of transistors Na and Nb) and GND.

FIGURE 3-2: PWM Current Control Circuit Principle (Channel 1 Shown)

The voltage across Rs is compared to a fraction of the reference voltage VREF, chosen with the logic input bits I0 and I1 (Table 3-3). The power bridge and thus the load current can also be switched off completely when both logic inputs are high. Note that any logic input left unconnected will be treated as a high level (pull-up resistor).

The maximum trip current for regulation, given for I0 I1 = 00 is calculated in Equation 3-1.

#### **EQUATION 3-1:**

$$I_{MAX} = \frac{V_{REF}}{10 * R_S}$$

TABLE 3-3: CURRENT LEVEL CONTROL TRUTH TABLE

| 10 | I1 | Comp. Trip Voltage | Output Current       |

|----|----|--------------------|----------------------|

| 0  | 0  | Vtrip = 1/10*Vref  | Imax = Vref/10RS     |

| 1  | 0  | Vtrip = 1/15*Vref  | 2/3*Imax = Vref/15RS |

| 0  | 1  | Vtrip = 1/30*Vref  | 1/3*Imax = Vref/30RS |

| 1  | 1  | x                  | 0 (no current)       |

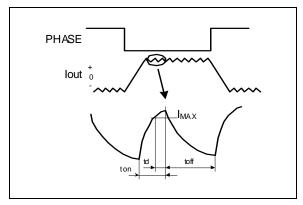

When the maximum allowed current is reached, the bridge source is turned off during a fixed period  $T_{OFF}$  (typically 50us) given by a non-retriggerable pulse generator and the external timing components Rt (20k-100 k $\Omega$  range) and Ct (100 pF-1000 pF range):

$$toff = 1.1*(Rt*Ct)$$

During  $T_{OFF}$  the winding current decreases. When the driver is re-enabled, the winding current increases again until it reaches the threshold, and the cycle repeats itself maintaining the load current at the desired level.

FIGURE 3-3: PWM Output Current Waveform

#### 3.3 Circuit Protection

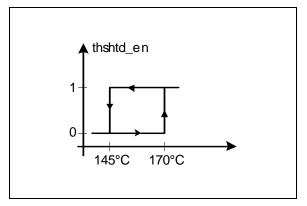

A thermal protection circuitry turns off all drivers when the junction temperature exceeds a safe operating limit of 170°C (typ.). This protects the devices from failure due to excessive heating. Despite this thermal protection, output short circuits are not permitted. The output drivers are re-enabled once junction temperature has dropped below 145°C (typ.).

**FIGURE 3-4:** Thermal Shutdown Output vs. Temperature Showing Hysteresis

An undervoltage lockout circuit protects the MTS62C19A from potential shoot-through currents when the load supply voltage is applied prior to the logic supply voltage. The power bridge and all outputs are disabled if VLOGIC is smaller than 4V.

With this protection feature, the circuit will withstand any order of turn-on or turn-off of the supply voltages VLOGIC and VLOAD. Normal dV/dt values are assumed.

# 4.0 APPLICATION CIRCUITS & ISSUES

### 4.1 Typical Application

The MTS62C19A circuit with external components for a typical application is shown in Figure 4-1. Typical passive component values are: Rs =  $1\Omega$ , Rc =  $1k\Omega$ , Cc = 820pF, Rt =  $56k\Omega$  and Ct = 820pF.

FIGURE 4-1: Typical Application Circuit

During PWM operation, when the output stage is turned-on, large voltage peaks might appear across Rs, which can wrongly trigger the input comparator. To avoid an unstable current control, an external RcCc filter should be used that delays the comparator action. Depending on load type many applications will not require this filter (SENSE connected to COMPIN).

### 4.2 Stepping Examples

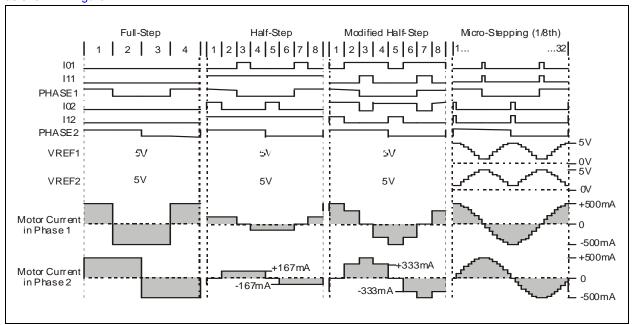

The MTS62C19A allows to control a motor in full-step, half-step, modified half-step and microstepping mode, as shown in Figure 4-2.

FIGURE 4-2: Examples of Stepping Modes Achievable with Typical Application Circuit

### 4.3 PCB Design Guidelines

Unused inputs should be connected to fixed voltage levels in order to get the highest noise immunity. Typical PCB layout guidelines for power application should be followed. These include separate power ground planes, supply decoupling capacitors close to the IC, short connections and use of maximized copper areas to improve thermal dissipation.

### 5.0 MECHANICAL DIMENSIONS

### **SOP 24L Package Outline**

| Symbol | Minimum        | Typical        | Maximum        | Unit      |

|--------|----------------|----------------|----------------|-----------|

| Α      | _              | _              | 2.642 (0.104)  | mm (inch) |

| A1     | 0.102 (0.004)  | _              | _              | mm (inch) |

| D      | 15.545 (0.612) | 15.697 (0.618) | 15.850 (0.624) | mm (inch) |

| E      | 7.417 (0.292)  | 7.518 (0.296)  | 7.595 (0.299)  | mm (inch) |

| Н      | 10.287 (0.405) | 10.464 (0.412) | 10.643 (0.419) | mm (inch) |

| L      | 0.533 (0.021)  | 0.787 (0.031)  | 1.041 (0.041)  | mm (inch) |

| J      | 0              | 4              | 8              | 0         |

Note 1: JEDEC outline: M0-119 AA

- 2: Dimensions "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusions and gate burrs should not exceed 0.25mm (0.010inch) per side.

- 3: Dimensions "E" does not include inter-lead flash, or protrusions. Inter-lead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

**NOTES:**

### **APPENDIX A: REVISION HISTORY**

## **Revision A (September 2010)**

• Original Release of this Document.

**NOTES:**

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-60932-535-0

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-792-7200

Fax: 480-792-7277

Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### **ASIA/PACIFIC**

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2401-1200

Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-6578-300 Fax: 886-3-6578-370

Taiwan - Kaohsiung Tel: 886-7-213-7830

Fax: 886-7-330-9305

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91 **UK - Wokingham**

Tel: 44-118-921-5869 Fax: 44-118-921-5820

08/04/10