# 产品手册

## ECK30-T13IA 核心板

**成都亿佰特电子科技有限公司**

Chengdu Ebyte Electronic Technology Co.,Ltd.

## 目录

|                       |    |

|-----------------------|----|

| 免责申明和版权公告 .....       | 1  |

| 1. 产品概述 .....         | 2  |

| 1.1. 产品介绍 .....       | 2  |

| 1.2. 产品特点 .....       | 2  |

| 1.3. 核心板功能框图 .....    | 5  |

| 1.4. 典型应用 .....       | 5  |

| 2. 产品选型 .....         | 5  |

| 2.1. 型号配置 .....       | 5  |

| 2.2. 型号编码 .....       | 6  |

| 3. 快速体验 .....         | 6  |

| 4. 功能和参数 .....        | 6  |

| 4.1. 产品功能 .....       | 6  |

| 4.2. 环境特性 .....       | 8  |

| 4.3. I/O 特性 .....     | 8  |

| 4.4. 电气特性 .....       | 12 |

| 5. 核心板硬件设计 .....      | 13 |

| 5.1. 处理器 .....        | 13 |

| 5.2. 内存 .....         | 14 |

| 5.3. 时钟 .....         | 15 |

| 5.4. 存储 .....         | 15 |

| 5.5. LED .....        | 16 |

| 5.6. 电源 .....         | 16 |

| 5.7. 在板 I/O 分配 .....  | 17 |

| 6. 底板硬件设计 .....       | 17 |

| 6.1. 电源接口 .....       | 18 |

| 6.2. 启动配置 .....       | 19 |

| 6.3. 复位按键 .....       | 19 |

| 6.4. 参考时钟和 NMI .....  | 20 |

| 6.5. 显示输出接口 .....     | 21 |

| 6.6. 数字摄像头接口 .....    | 23 |

| 6.7. SD/MMC 卡接口 ..... | 24 |

| 6.8. USB 接口 .....     | 25 |

| 6.9. 以太网接口 .....      | 26 |

| 6.10. CVBS 接口 .....   | 27 |

| 6.11. 模拟音频接口 .....    | 28 |

| 6.12. RTC .....       | 29 |

| 6.13. 数字音频接口 .....    | 30 |

| 6.14. UART 接口 .....   | 30 |

| 6.15. SPI 接口 .....    | 30 |

| 6.16. I2C 接口 .....    | 31 |

| 6.17. CAN 接口 .....    | 31 |

---

|                     |    |

|---------------------|----|

| 6.18. ADC 接口 .....  | 31 |

| 6.19. GPIO 接口 ..... | 32 |

| 6.20. 硬件设计检查项 ..... | 32 |

| 7. 软件资源 .....       | 32 |

| 7.1. 系统资源 .....     | 33 |

| 8. 结构尺寸 .....       | 34 |

| 9. 焊接指导 .....       | 34 |

| 9.1. 回流焊温度 .....    | 34 |

| 9.2. 回流焊曲线图 .....   | 35 |

| 10. 参考文档 .....      | 35 |

| 11. 修订说明 .....      | 35 |

| 12. 关于我们 .....      | 36 |

## 免责申明和版权公告

本文中的信息，如有变更，恕不另行通知。 文档“按现状”提供，不负任何担保责任，包括对适销性、适用于特定用途或非侵权性的任何担保，和任何提案、规格或样品在他处提到的任何担保。本文档不负任何责任，包括使用本文档内信息产生的侵犯任何专利权行为的责任。本文档在此未以禁止反言或其他方式授予任何知识产权使用许可，不管是明示许可还是暗示许可。

文中所得测试数据均为亿佰特实验室测试所得，实际结果可能略有差异。

文中提到的所有商标名称、商标和注册商标均属其各自所有者的财产，特此声明。

最终解释权归成都亿佰特电子科技有限公司所有。

### 注意：

由于产品版本升级或其他原因，本手册内容有可能变更。亿佰特电子科技有限公司保留在没有任何通知或者提示的情况下对本手册的内容进行修改的权利。本手册仅作为使用指导，成都亿佰特电子科技有限公司尽全力在本手册中提供准确的信息，但是成都亿佰特电子科技有限公司并不确保手册内容完全没有错误，本手册中的所有陈述、信息和建议也不构成任何明示或暗示的担保。

# 1. 产品概述

## 1.1. 产品介绍

亿佰特 ECK30-T13IA 系列核心板是基于全志公司的 T113-i 处理器精心设计的，采用邮票孔连接的低成本、低功耗、高性价比、高可靠性的全国产化工业级嵌入式核心板。可广泛应用于工业控制、HMI、IoT 等领域。

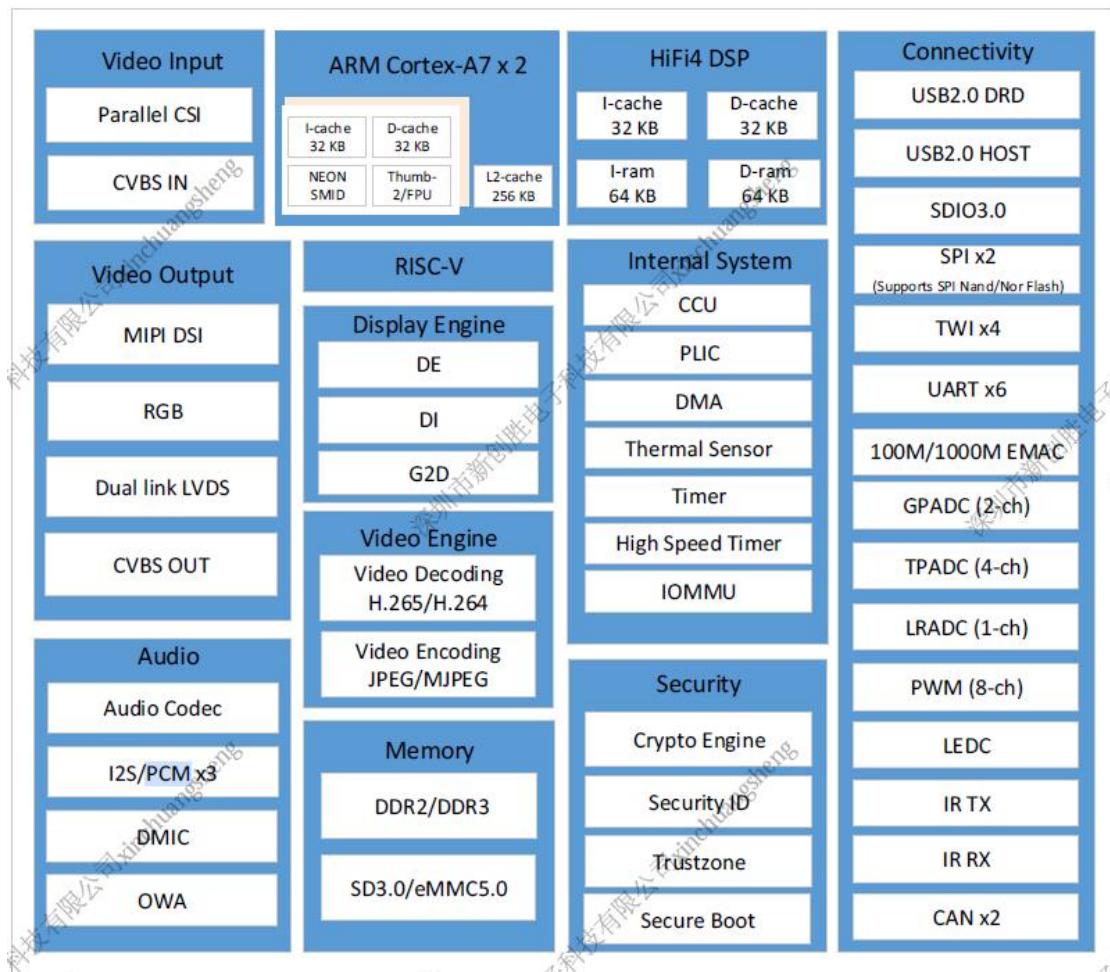

全志公司的 T113-i 处理器是由双核 ARM Cortex-A7、RISC-V 和 HiFi4 DSP 三种异构处理器所组成，能够为用户提供高效的计算能力。同时还提供 1 路显示、1 路数字摄像头、1 路千兆以太网、3 路 SDIO、2 路 USB、6 路 UART、2 路 CAN 等丰富的数字 I/O 功能，同时还提供了模拟视频、模拟音频、ADC 等丰富的模拟 I/O 功能。

ECK30-T13IA 系列核心板包含 3 种具体产品型号，均采用全国产化工业级器件设计。它们主要在内存容量、存储配置等方面有一些差异，客户可根据需求自行选择合适的型号。产品选型详见产品选型章节。

ECK30-T13IA 系列核心板实物图（产品底面无器件）如下：

实物图

## 1.2. 产品特点

1、处理器：全志 T113-i 处理器：

- ◆ 双核 ARM Cortex-A7，最高主频 1.2GHz；

- ◆ RISC-V；

- ◆ HiFi4 DSP；

2、在板贴装 DDR3 SDRAM，256MB/512MB/1GB 容量可选；

3、在板存储：8GB eMMC 或 256MB SPI NAND FLASH 可选；

4、视频输出：

- ◆ 2 路 LVDS 输出, 支持  $1920 \times 1080 @ 60\text{fps}$ ;

- ◆ 1 路数字 RGB 输出, 支持  $1920 \times 1080 @ 60\text{fps}$ ;

- ◆ 1 路 MIPI DSI, 支持 4Lane, 支持  $1920 \times 1200 @ 60\text{fps}$ ;

- ◆ 1 路 CVBS 输出, 支持 NTSC 和 PAL 制式;

- ◆ 1 路串行 RGB (DBI) 输出, 支持  $240 \times 320 @ 60\text{fps}$ ;

注: LVDS0、LVDS1 与数字 RGB 引脚复用, LVDS0 与 MIPI DSI 引脚复用, DBI 与 SPI1 引脚复用;

5、视频输入:

- ◆ 1 路 CSI, 8 位并行接口, 支持  $1920 \times 1080 @ 30\text{fps}$ ;

- ◆ 2 路 CVBS 输入, 支持 NTSC 和 PAL 制式;

6、音频接口:

- ◆ 集成 Audio Codec;

- ◆ 3 路单声道 MIC 输入;

- ◆ 1 路双声道 LINE IN;

- ◆ 1 路双声道 FM IN;

- ◆ 1 路差分 LINE OUT;

- ◆ 1 路双声道 Headphone 输出;

7、网络: 集成 1 个 10/100/1000 自适应以太网 MAC, 支持 RMII/RGMII 接口;

8、USB: 1 路 USB2.0 DRD, 1 路 USB2.0 HOST;

9、SMHC: 集成 3 个 SMHC 控制器, 引出 2 路到邮票孔;

10、4 路 TWI, 兼容 I2C 总线标准, 支持标准模式(100Kbps)和高速模式(400Kbps);

11、2 路 SPI, 引出 1 路到邮票孔;

12、6 路 UART, 最大波特率 4Mbps;

13、8 路 PWM, 最大输出频率 24/100MHz, 支持 PWM 输出、输入捕获;

14、2 路 GPADC, 12 位分辨率, 最大采样率 1MHz;

15、4 路 TPADC, 12 位分辨率, 最大采样率 1MHz, 支持 4 线电阻触摸屏;

16、1 路 LRADC, 6 位分辨率, 最大采样率 2KHz;

17、1 路 LEDC, 支持 1024 个 LED 串连, 最大数据传输速率 800Kbps;

18、3 路 I2S/PCM, 支持全双工, 采样率 8KHz~48KHz;

19、1 路 DMIC, 最高支持 8 通道, 采样率 8KHz~48KHz;

- 20、1路 OWA, 兼容 S/PDIF 协议;

- 21、2路 CIR, 1x CIR TX 接口, 1x CIR RX 接口;

- 22、2路 CAN(CAN0、CAN1), 支持 CAN 2.0A 和 CAN 2.0B 协议;

- 23、3路 JTAG, 包含 ARM、RISC-V 和 HiFi4 DSP JTAG;

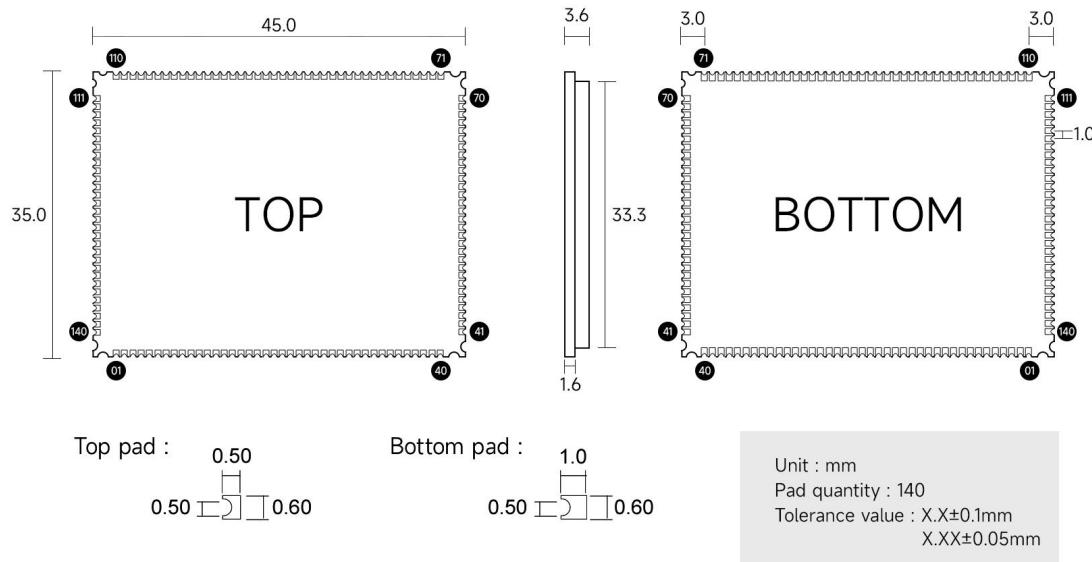

- 24、接口形式: 140 脚邮票孔, 间距 1.0mm;

- 25、电源: 单路 DC +5V±10%@0.5A 电源输入;

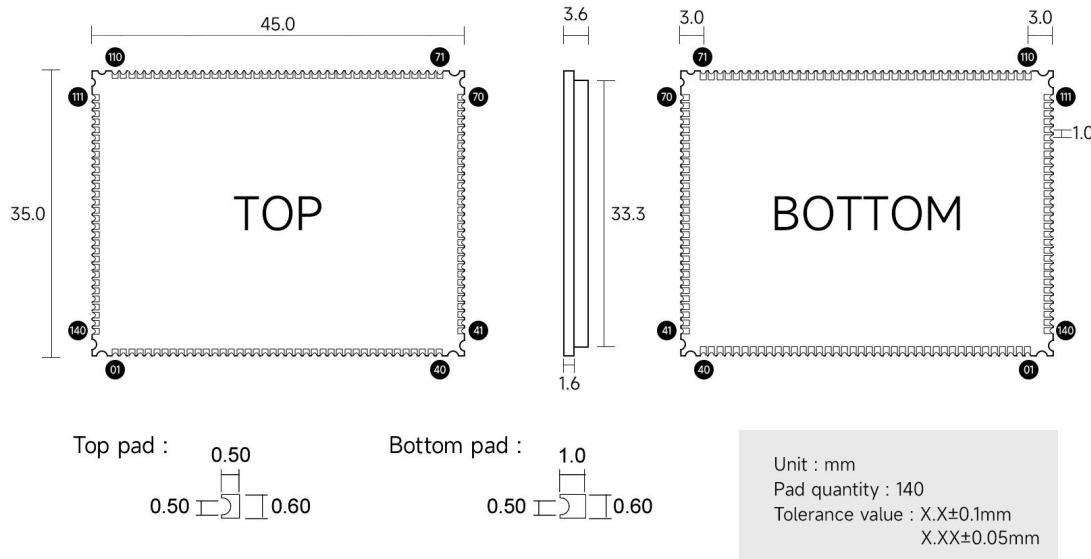

- 26、尺寸: 45×35×3.6mm, 尺寸如下图所示:

尺寸图

- 27、工作温度: 工业级: -40°C-85°C;

- 28、PCB 工艺: 8 层板设计, 沉金, 无铅工艺;

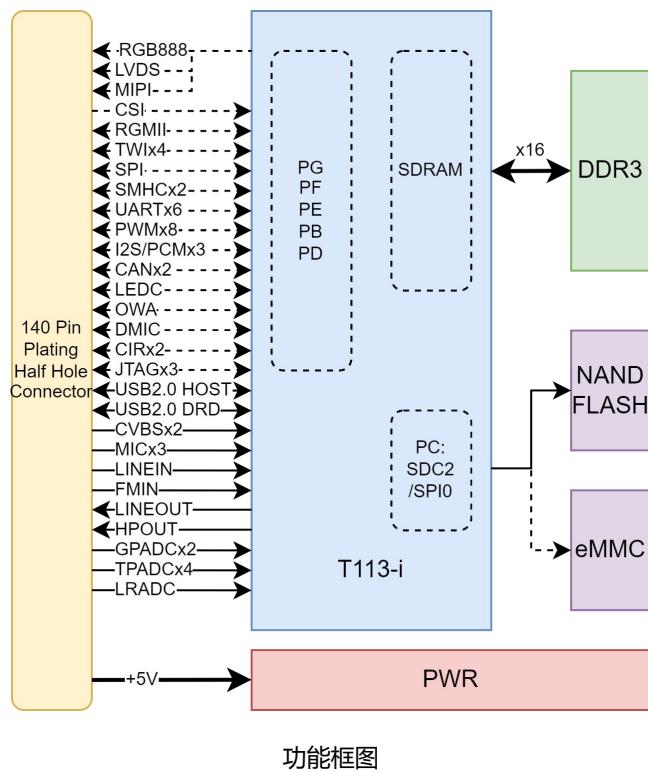

### 1.3.核心板功能框图

功能框图

### 1.4.典型应用

- 智能家居;

- 智能玩具;

- 智慧城市;

- 平板电脑;

- 物联网网关;

- 广告一体机;

- 工业一体机;

- 工业控制主板;

- 机器人、无人机。

## 2. 产品选型

### 2.1.型号配置

ECK30-T13IA 系列核心板选型配置表如下表:

产品选型和配置表

| 序号 | 产品型号 | 处理器型号 | 内存 | 存储 | 工作温度 |

|----|------|-------|----|----|------|

|----|------|-------|----|----|------|

|   |                    |        |               |               |                       |

|---|--------------------|--------|---------------|---------------|-----------------------|

| 1 | ECK30-T13IA2MN2M-I | T113-i | 256MB<br>DDR3 | 256MB<br>NAND | 国产工业级<br>-40°C ~ 85°C |

| 2 | ECK30-T13IA5ME8G-I | T113-i | 512MB<br>DDR3 | 8GB<br>eMMC   | 国产工业级<br>-40°C ~ 85°C |

| 3 | ECK30-T13IA1GE8G-I | T113-i | 1GB<br>DDR3   | 8GB<br>eMMC   | 国产工业级<br>-40°C ~ 85°C |

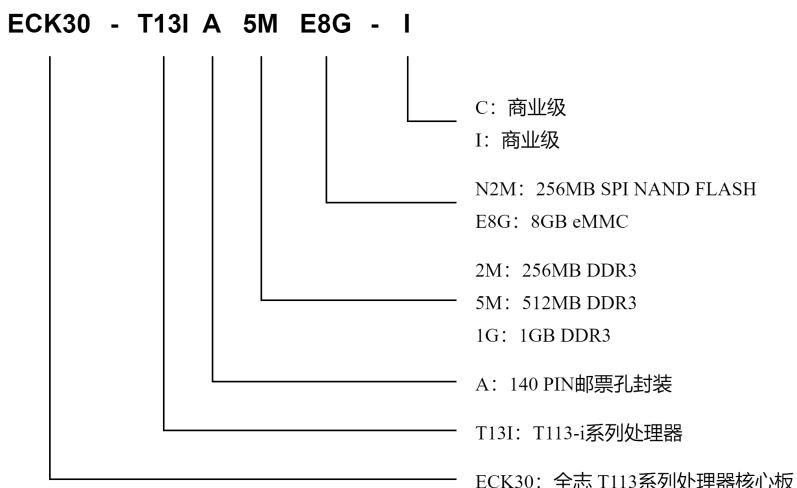

## 2.2.型号编码

产品型号编码说明如下图:

型号编码说明

## 3. 快速体验

选择亿佰特单板机产品，可快速体验 ECK30-T13IA 核心板产品典型应用功能，底板设计，软件开发等。

## 4. 功能和参数

### 4.1. 产品功能

ECK30-T13IA 系列核心板主要集成了处理器、内存、存储和电源系统，并引出了处理器上的所有 I/O 引脚。用户可以根据自己的需要，设计底板来应用核心板上 I/O 资源，将 I/O 复用成自己所需要的功能。

下表列举了 ECK30-T13IA 系列核心板在板集成的主要功能参数，和可复用 I/O 资源的功能参数。其中每项 I/O 功能的描述是，在不使用其他 I/O 功能的前提下，核心板所能使用该项 I/O 功能的最大指标（比如在使用 24 位色 RGB 接口功能和网络接口功能后，就不能实

现全部 UART 功能)。

产品功能表

| 功能          | 数量 | 功能描述                                                                                                                                                                                    |

|-------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU         | 1  | T113-i;<br>Dual-core ARM Cortex-A7@1.2GHz;<br>RISC-V CPU;<br>HiFi4 DSP;                                                                                                                 |

| MEM         | 1  | 在板 DDR3 SDRAM, 16 位宽, 256MB/512MB/1GB 可选;                                                                                                                                               |

| FLASH       | 1  | 在板 8GB eMMC / 在板 256MB SPI NAND FLASH 可选;                                                                                                                                               |

| DISPLAY     | 1  | 并行 RGB 24 位色输出, 最高支持 1920×1080@60fps;<br>双通道 LVDS 输出, 最高支持 1920×1080@60fps;<br>4-lane MIPI DSI, 最高支持 1920×1200@60fps;<br>注: 以上显示接口部分 I/O 为复用关系不能同时使用;<br>串行 RGB 输出, 最高支持 800×480@60fps; |

| CSI         | 1  | 8 位并行数字摄像头接口, 支持 1080P@30fps, 最大 148.5MHz 像素时钟;                                                                                                                                         |

| CVBS IN     | 2  | 1 个 CVBS decoder, 支持 NTSC 和 PAL 制式, 10-bit 视频 ADC;                                                                                                                                      |

| CVBS OUT    | 1  | 支持 NTSC 和 PAL 制式, 10-bit 视频 DAC;                                                                                                                                                        |

| Audio Codec | 1  | 2 通道 DAC, 采样率 8KHz~192KHz;<br>3 通道 ADC, 采样率 8KHz~48KHz;<br>3 路 MIC IN、1 路 LINE IN、1 路 FM IN;<br>1 路差分 LINE OUT、1 路 Headphone OUT;                                                       |

| EMAC        | 1  | 支持 RMII/RGMII 接口(10/100/1000Mbps);                                                                                                                                                      |

| SMHC        | 2  | 支持 SD3.0, SDIO3.0, MMC5.0 协议;<br>SDC0: 4 位数据总线 (推荐作为底板 Micro SD 功能);<br>SDC1: 4 位数据总线;<br>注: SDC2 未引出到邮票孔, 用于板上连接 eMMC 或 FLASH 存储芯片;                                                    |

| USB DRD     | 1  | 符合 USB2.0 标准, 支持 USB HOST 和 USB Device 功能;                                                                                                                                              |

| USB HOST    | 1  | 符合 USB2.0 标准, 支持 USB HOS 功能;                                                                                                                                                            |

| TWI(I2C)    | 4  | 支持标准模式(100Kbps)和高速模式(400Kbps);                                                                                                                                                          |

| SPI         | 1  | 支持 SPI 模式和 DBI(Display Bus Interface)模式;<br>支持 Master Mode、Slave Mode, 1 个片选信号;<br>最高支持 100MHz 工作频率;                                                                                    |

| UART        | 6  | 最大 4Mbps 波特率 (64MHz APB 时钟), 支持硬件或软件流控;                                                                                                                                                 |

| PWM         | 8  | 0~100%可调占空比, 支持输出、输入捕获, 输出频率为 0~24MHz 或 100MHz;                                                                                                                                         |

| GPADC       | 2  | 12 位 SAR 型 A/D 转换器, 采样频率高达 1MHz;                                                                                                                                                        |

| TPADC       | 4  | 12 位 SAR 型 A/D 转换器, 采样频率高达 1MHz, 支持 4 线电阻式触摸屏;                                                                                                                                          |

| LRADC       | 1  | 6 位 A/D 转换器, 采样频率高达 2KHz, 支持保持键和通用键;                                                                                                                                                    |

| LEDC        | 1  | 支持 1024 个 LED 串行连接, LED 数据传输速率高达 800Kbps;                                                                                                                                               |

| PCM/I2S     | 3  | 支持全双工, 采样率 8KHz~384KHz;                                                                                                                                                                 |

| DMIC        | 1  | 最高支持 8 通道, 采样率 8KHz~48KHz;                                                                                                                                                              |

| OWA         | 1  | One Wire Audio, 兼容 S/PDIF 协议;                                                                                                                                                           |

| CIR         | 2  | 包含 CIR TX、CIR RX, 可通过红外线进行远程控制;                                                                                                                                                         |

| CAN         | 2  | 支持 CAN 2.0A 和 CAN 2.0B 协议;                                                                                                                                                              |

|      |    |                                 |

|------|----|---------------------------------|

| JTAG | 3  | 包含 ARM、RISC-V 和 HiFi4 DSP JTAG; |

| GPIO | 79 | 软件配置 GPIO 功能，支持中断输入；            |

## 4.2. 环境特性

环境特性表

|      |     |                 |

|------|-----|-----------------|

| 工作温度 | 商业级 | 0°C ~ 70°C;     |

|      | 工业级 | -40°C ~ 85°C;   |

| 贮存温度 |     | -40°C ~ 85°C;   |

| 工作湿度 |     | 5~95%湿度，非凝结；    |

| 贮存湿度 |     | 60°C@95%湿度，非凝结； |

## 4.3. I/O 特性

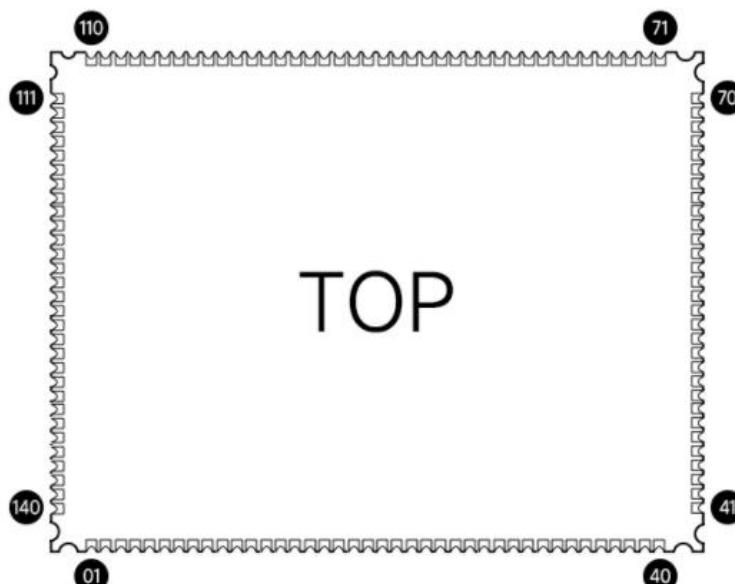

### 4.3.1. I/O 引脚定义

引脚编号图

引脚定义表

| Pin | Pin Name      | MPU Pin | Level/Rail | Type | Length(mil) | Comment       |

|-----|---------------|---------|------------|------|-------------|---------------|

| 1   | REFCLK_OUT_J2 | J2      | 1.8V       | AO   |             |               |

| 2   | FEL_A18       | A18     | 3.3V       | DI   |             | 1KΩ in series |

| 3   | NMI_N3        | N3      | 1.8V       | I/O  |             |               |

| 4   | RESET_M2      | M2      | 3.3V       | I/O  |             | 10KΩ pull up  |

| 5   | DGND          | -       | GND        | PWR  |             |               |

| 6   | PG17_E7       | E7      | 3.3V       | I/O  | 1075.42     |               |

| 7   | PG18_D7       | D7      | 3.3V       | I/O  | 1007.06     |               |

|    |         |    |      |     |         |               |

|----|---------|----|------|-----|---------|---------------|

| 8  | PG13_D6 | D6 | 3.3V | I/O | 891.26  |               |

| 9  | PG9_B6  | B6 | 3.3V | I/O | 914.82  |               |

| 10 | PG8_A6  | A6 | 3.3V | I/O | 919.43  |               |

| 11 | PG2_A3  | A3 | 3.3V | I/O | 902.69  |               |

| 12 | PG1_B3  | B3 | 3.3V | I/O | 907.56  |               |

| 13 | PG0_B2  | B2 | 3.3V | I/O | 916.6   |               |

| 14 | PG10_C6 | C6 | 3.3V | I/O | 904.65  |               |

| 15 | PG12_D5 | D5 | 3.3V | I/O | 895.1   |               |

| 16 | PG7_C5  | C5 | 3.3V | I/O | 902.43  |               |

| 17 | PG6_B5  | B5 | 3.3V | I/O | 904.28  |               |

| 18 | PG5_B4  | B4 | 3.3V | I/O | 901.95  |               |

| 19 | PG4_A4  | A4 | 3.3V | I/O | 901.03  |               |

| 20 | PG3_C3  | C3 | 3.3V | I/O | 898.23  |               |

| 21 | PG16_F7 | F7 | 3.3V | I/O | 899.31  |               |

| 22 | PG11_D4 | D4 | 3.3V | I/O | 782.01  |               |

| 23 | PG14_E6 | E6 | 3.3V | I/O | 753.47  |               |

| 24 | PG15_F6 | F6 | 3.3V | I/O | 752.68  |               |

| 25 | DGND    | -  | GND  | PWR |         |               |

| 26 | PF6_D3  | D3 | 3.3V | I/O | 1126.85 |               |

| 27 | PF0_C2  | C2 | 3.3V | I/O | 1122.36 |               |

| 28 | PF1_C1  | C1 | 3.3V | I/O | 1129.58 |               |

| 29 | PF2_D2  | D2 | 3.3V | I/O | 1129.74 | 33Ω in series |

| 30 | PF5_E2  | E2 | 3.3V | I/O | 1131.95 |               |

| 31 | PF3_D1  | D1 | 3.3V | I/O | 1130.76 |               |

| 32 | PF4_E3  | E3 | 3.3V | I/O | 1124.16 |               |

| 33 | DGND    | -  | GND  | PWR |         |               |

| 34 | PE12_R5 | R5 | 3.3V | I/O | 1117.23 |               |

| 35 | PE13_R4 | R4 | 3.3V | I/O | 1011.36 |               |

| 36 | PE4_T2  | T2 | 3.3V | I/O | 1010.35 |               |

| 37 | PE5_T3  | T3 | 3.3V | I/O | 1012.91 |               |

| 38 | PE6_R1  | R1 | 3.3V | I/O | 1010.38 |               |

| 39 | PE7_R2  | R2 | 3.3V | I/O | 1011.52 |               |

| 40 | PE8_R3  | R3 | 3.3V | I/O | 1010.62 |               |

| 41 | PE9_P2  | P2 | 3.3V | I/O | 1009.88 |               |

| 42 | PE10_P3 | P3 | 3.3V | I/O | 1007.44 |               |

| 43 | PE11_N1 | N1 | 3.3V | I/O | 1011.75 |               |

| 44 | PE14_N4 | N4 | 3.3V | I/O | 1009.9  |               |

| 45 | PE15_N5 | N5 | 3.3V | I/O | 1012.78 |               |

| 46 | PE16_N6 | N6 | 3.3V | I/O | 971.43  |               |

| 47 | PE17_M6 | M6 | 3.3V | I/O | 1002.44 |               |

| 48 | PE0_V1  | V1 | 3.3V | I/O | 1012.2  |               |

| 49 | PE1_U1  | U1 | 3.3V | I/O | 1012.06 |               |

| 50 | PE2_U2  | U2 | 3.3V | I/O | 1011.86 |               |

|    |           |     |      |     |         |  |

|----|-----------|-----|------|-----|---------|--|

| 51 | PE3_U3    | U3  | 3.3V | I/O | 1010.43 |  |

| 52 | DGND      | -   | GND  | PWR |         |  |

| 53 | PB8_G15   | G15 | 3.3V | I/O | 1535.4  |  |

| 54 | PB9_G16   | G16 | 3.3V | I/O | 1593.27 |  |

| 55 | PB10_F17  | F17 | 3.3V | I/O | 1592.89 |  |

| 56 | PB11_F15  | F15 | 3.3V | I/O | 1593.85 |  |

| 57 | PB12_F16  | F16 | 3.3V | I/O | 1511.52 |  |

| 58 | PB2_M16   | M16 | 3.3V | I/O | 1126.85 |  |

| 59 | PB3_M15   | M15 | 3.3V | I/O | 1082.91 |  |

| 60 | PB4_K16   | K16 | 3.3V | I/O | 1097.01 |  |

| 61 | PB5_K15   | K15 | 3.3V | I/O | 1125.02 |  |

| 62 | PB6_K17   | K17 | 3.3V | I/O | 1113.72 |  |

| 63 | PB7_J15   | J15 | 3.3V | I/O | 1038.85 |  |

| 64 | PB0_J16   | J16 | 3.3V | I/O | 1038.54 |  |

| 65 | PB1_J17   | J17 | 3.3V | I/O | 1032.1  |  |

| 66 | DGND      | -   | GND  | PWR |         |  |

| 67 | PD0_W19   | W19 | 3.3V | I/O | 1017.36 |  |

| 68 | PD1_V20   | V20 | 3.3V | I/O | 1016.69 |  |

| 69 | PD2_V19   | V19 | 3.3V | I/O | 1016.5  |  |

| 70 | PD3_U20   | U20 | 3.3V | I/O | 1016.65 |  |

| 71 | DGND      | -   | GND  | PWR |         |  |

| 72 | PD4_U19   | U19 | 3.3V | I/O | 1034.18 |  |

| 73 | PD5_U18   | U18 | 3.3V | I/O | 1037.15 |  |

| 74 | PD6_T19   | T19 | 3.3V | I/O | 1031.65 |  |

| 75 | PD7_T18   | T18 | 3.3V | I/O | 1031.69 |  |

| 76 | PD8_R20   | R20 | 3.3V | I/O | 1017.22 |  |

| 77 | PD9_R19   | R19 | 3.3V | I/O | 1019.47 |  |

| 78 | DGND      | -   | GND  | PWR |         |  |

| 79 | PD10_T17  | T17 | 3.3V | I/O | 1018.78 |  |

| 80 | PD11_R17  | R17 | 3.3V | I/O | 1018.77 |  |

| 81 | PD12_P19  | P19 | 3.3V | I/O | 1017.67 |  |

| 82 | PD13_P18  | P18 | 3.3V | I/O | 1018.78 |  |

| 83 | PD14_N17  | N17 | 3.3V | I/O | 1016.2  |  |

| 84 | PD15_N16  | N16 | 3.3V | I/O | 1019.47 |  |

| 85 | DGND      | -   | GND  | PWR |         |  |

| 86 | PD16_N20  | N20 | 3.3V | I/O | 1031.7  |  |

| 87 | PD17_N19  | N19 | 3.3V | I/O | 1034.48 |  |

| 88 | PD18_M19  | M19 | 3.3V | I/O | 1032.43 |  |

| 89 | PD19_M18  | M18 | 3.3V | I/O | 1034.74 |  |

| 90 | PD21_V18  | V18 | 3.3V | I/O | 1095.57 |  |

| 91 | PD20_W18  | W18 | 3.3V | I/O | 1126.38 |  |

| 92 | DGND      | -   | GND  | PWR |         |  |

| 93 | FMINR_C17 | C17 | -    | AI  |         |  |

|     |               |     |      |     |               |  |

|-----|---------------|-----|------|-----|---------------|--|

| 94  | FMINL_B17     | B17 | -    | AI  |               |  |

| 95  | LINEINR_C16   | C16 | -    | AI  |               |  |

| 96  | LINEINL_B16   | B16 | -    | AI  |               |  |

| 97  | AUGND         | -   | AGND | PWR |               |  |

| 98  | MBIAS_E16     | E16 | -    | AO  |               |  |

| 99  | MIC_DET_A17   | A17 | -    | AI  |               |  |

| 100 | MICIN1P_D20   | D20 | -    | AI  |               |  |

| 101 | MICIN1N_D19   | D19 | -    | AI  |               |  |

| 102 | MICIN2P_E15   | E15 | -    | AI  |               |  |

| 103 | MICIN2N_D15   | D15 | -    | AI  |               |  |

| 104 | MICIN3P_D17   | D17 | -    | AI  |               |  |

| 105 | MICIN3N_D16   | D16 | -    | AI  |               |  |

| 106 | AUGND         | -   | AGND | PWR |               |  |

| 107 | LINEOUTRP_B14 | B14 | -    | AO  |               |  |

| 108 | LINEOUTRN_C14 | C14 | -    | AO  |               |  |

| 109 | LINEOUTLP_B15 | B15 | -    | AO  |               |  |

| 110 | LINEOUTLN_C15 | C15 | -    | AO  |               |  |

| 111 | HBIAS_E17     | E17 | -    | AO  |               |  |

| 112 | HP_DET_A13    | A13 | -    | AI  |               |  |

| 113 | HPOUTR_D13    | D13 | -    | AO  |               |  |

| 114 | HPOUTFB_E13   | E13 | -    | AO  |               |  |

| 115 | HPOUTL_F13    | F13 | -    | AO  |               |  |

| 116 | DGND          | -   | GND  | PWR |               |  |

| 117 | TVOUT0_E19    | E19 | -    | AO  |               |  |

| 118 | TVIN1_C9      | C9  | -    | AI  |               |  |

| 119 | TVIN0_B9      | B9  | -    | AI  |               |  |

| 120 | DGND          | -   | GND  | PWR |               |  |

| 121 | LRADC_B12     | B12 | -    | AI  | 51KΩ pull up  |  |

| 122 | GPADC0_C13    | C13 | -    | AI  |               |  |

| 123 | GPADC1_B13    | B13 | -    | AI  |               |  |

| 124 | TP_X1_C12     | C12 | -    | AI  | 1nF pull down |  |

| 125 | TP_X2_A11     | A11 | -    | AI  | 1nF pull down |  |

| 126 | TP_Y1_B11     | B11 | -    | AI  | 1nF pull down |  |

| 127 | TP_Y2_C11     | C11 | -    | AI  | 1nF pull down |  |

| 128 | DGND          | -   | GND  | PWR |               |  |

| 129 | USB1_DP_A8    | A8  | -    | I/O | 960.34        |  |

| 130 | USB1_DM_B8    | B8  | -    | I/O | 962.55        |  |

| 131 | DGND          | -   | GND  | PWR |               |  |

| 132 | USB0_DP_B7    | B7  | -    | I/O | 957.89        |  |

| 133 | USB0_DM_C7    | C7  | -    | I/O | 959.18        |  |

| 134 | DGND          | -   | GND  | PWR |               |  |

| 135 | VDD_3V3_SOM   | -   | 3.3V | PWR |               |  |

| 136 | VDD_1V8_SOM   | -   | 1.8V | PWR |               |  |

|     |            |   |     |     |  |  |

|-----|------------|---|-----|-----|--|--|

| 137 | DGND       | - | GND | PWR |  |  |

| 138 | DGND       | - | GND | PWR |  |  |

| 139 | VDD_5V_SOM | - | 5V  | PWR |  |  |

| 140 | VDD_5V_SOM | - | 5V  | PWR |  |  |

注:

- ◆ AI: 模拟量输入;

- ◆ AO: 模拟量输出;

- ◆ DI: 数字量输入;

- ◆ DO: 数字量输出;

- ◆ I/O: 数字量输入输出;

- ◆ PWR: 电源;

- ◆ 走线长度单位为 mil;

- ◆ 详细邮票孔引脚复用功能可查看《ECK30-T13IA Pin List》文件。

### 4.3.2. I/O 阻抗控制

ECK30-T13IA 系列核心板所有高速信号在 PCB 设计时都做了阻抗控制和长度控制，核心板走线阻抗控制参数见下表。

走线阻抗控制表

| 序号 | 阻抗控制走线分类       | 阻抗控制                   | 典型型号网络名称                     |

|----|----------------|------------------------|------------------------------|

| 1  | USB 差分信号       | $90 \pm 10\% \Omega$   | USB1_DP_A8/USB1_DM_B8        |

| 2  | LVDS、MIPI 差分信号 | $100 \pm 10\% \Omega$  | PD0_W19/PD1_V20              |

| 3  | 模拟视频输入、输出信号    | $37.5 \pm 10\% \Omega$ | TVOUT0_E19、TVIN1_C9、TVIN0_B9 |

| 4  | 一般单端走线         | $50 \pm 10\% \Omega$   |                              |

## 4.4. 电气特性

### 4.4.1. 功耗

注: 以下参数是在常温环境下对 ECK30-T13IA5ME8G-I 核心板进行的测量, 测量功耗不包含底板功耗, 测量重载功耗时运行内存和 eMMC 测试程序, 无显示, 无底板 SDIO 访问, 无网络访问。测试方法、使用功能、环境温度等因素都会影响功耗, 以下功耗数据仅供参考。

电源功耗表

| 电源状态 | 测试环境 | 电源电压 | 电流 | 功耗 |

|------|------|------|----|----|

|------|------|------|----|----|

|       |               |      |        |        |

|-------|---------------|------|--------|--------|

| BOOT  | UBOOT 运行过程中   | 5.0V | 0.169A | 0.845W |

| PWRUP | 进入系统未运行应用     | 5.0V | 0.104A | 0.52W  |

| PWRUP | 软件重载测试        | 5.0V | 0.203A | 1.015W |

| SLEEP | freeze 模式休眠状态 | 5.0V | 0.087A | 0.435W |

| SLEEP | mem 模式休眠状态    | 5.0V | 0.056A | 0.28W  |

## 5. 核心板硬件设计

### 5.1. 处理器

ECK30-T13IA 系列核心板选用全志科技 T113 系列中的 T113-i 处理器为核心。T113-i 处理器是专为 RISC-V 多媒体解码平台设计的高级应用处理器。它集成了 RISC-V、双核 A RM Cortex-A7 和 HiFi4 DSP 三种异构处理器，能够提供高效的计算能力。T113-i 支持 H.265、H.264、MPEG-1/2/4、JPEG、VC1 等全格式解码。独立编码器可以编码 JPEG 或 MJPEG。集成 ADC/DAC 和 I2S/PCM/DMIC/OWA 音频接口可以与 CPU 无缝协作，加速多媒体算法应用，并改善用户体验。T113-i 支持 RGB/LVDS/MIPI DSI/CVBS OUT 多种显示输出接口，以满足不同屏幕和显示器连接的需求。T113-i 具有丰富的扩展接口，如 CAN、USB、SDIO、EMAC、TWI、UART、SPI、PWM、GPADC、LRADC、TPADC、IR TX&RX 等。此外，T113-i 可以通过 SDIO 和 UART 与 WiFi 和蓝牙等其他不同的外围设备连接。T113-i 处理器功能框图如下图所示。

T113-i 系统功能框图

### 5.1.1. 处理器架构

T113-i 处理器采用多核异构设计，集成了 RISC-V、双核 ARM Cortex-A7 和 HiFi4 DS P 三种异构处理器。相关参数见下表。

T113-i 处理器架构参数表

| 功能     | 功能参数                                                                                                             |

|--------|------------------------------------------------------------------------------------------------------------------|

| ARM    | Dual-core ARM CortexTM-A7, 1.2GHz;<br>32 KB I-cache + 32 KB D-cache + NEON SIMD + Thumb 2/FPU + 256 KB L2 cache; |

| RISC-V | RISC-V CPU, 1008MHz;<br>32 KB I-cache + 32 KB D-cache;                                                           |

| DSP    | HiFi4 DSP, 600MHz;<br>32 KB L1 I-cache and 32 KB L1 D-cache;<br>64 KB I-ram and 64 KB D-ram;                     |

### 5.2. 内存

ECK30-T13IA 系列核心板在板贴装 1 片 DDR3 SDRAM 内存芯片。设计为 16 位内存数

据位宽，256MB/512MB/1GB 三种容量可选。设计内存均采用国产工业级器件。内存芯片型号见下表。

内存芯片选型表

| 厂家               | 型号              | 单片容量  | 工作温度         |

|------------------|-----------------|-------|--------------|

| 江波龙（Longsys）     | F60C1A0002-M69W | 2Gbit | -40°C ~ 95°C |

| 兆易创新（GigaDevice） | GDP1BFLA-WB     | 2Gbit | -40°C ~ 95°C |

| 江波龙（Longsys）     | F60C1A0004-M79W | 4Gbit | -40°C ~ 95°C |

| 兆易创新（GigaDevice） | GDP2BFLM-WB     | 4Gbit | -40°C ~ 95°C |

| 兆易创新（GigaDevice） | GDP3BELM-WB     | 8Gbit | -40°C ~ 95°C |

注：具体贴装内存芯片型号以实物为准。

### 5.3.时钟

ECK30-T13IA 系列核心板在板提供 1 个 32.768KHz 晶体（无源）振荡电路和 1 个 24MHz 晶体（无源）振荡电路，作为处理器系统时钟源。

### 5.4.存储

ECK30-T13IA 系列核心板在板设计有两种存储方案，一种是 SPI FLASH 存储方案。这种存储方案选用 SLC NAND FLASH 芯片作为存储介质，具备低成本和高可靠性的特点。另一种是 eMMC 存储方案。这种存储方案选用 eMMC 芯片作为存储介质，具备存储容量大、单位存储成本低和使用方便的特点。因两种存储方案复用了相同的 I/O 资源，一种型号的核心板产品只支持一种存储方案。用户需要根据具体项目对存储的要求，选用对应型号的核心板产品。

SPI NAND FLASH 通过 SPI0 总线连接到处理器上。器件采用兆易创新（GigaDevice）公司的 GD5F2GM7UEYIGR（256MB）工业级 SPI NAND FLASH。

eMMC 存储器通过 SMHC（SDC2）总线连接到处理器上。器件采用国产工业级 eMMC 存储芯片，芯片型号见下表。

eMMC 芯片选型表

| 厂家           | 型号               | 容量  | 工作温度         |

|--------------|------------------|-----|--------------|

| 江波龙（Longsys） | FEMDRW008G-88A39 | 8GB | -40°C ~ 85°C |

| 得一微（YEESTOR） | SGM8000I-S27B8G  | 8GB | -40°C ~ 85°C |

注：具体贴装内存芯片型号以实物为准。

## 5.5.LED

核心板上贴装 2 个 LED，可用于无屏蔽罩板卡的状态和运行指示。2 个 LED 均为可编程指示 LED，分别对应 F2/PC0 和 F1/PC1 两个引脚，高电平点亮。

## 5.6.电源

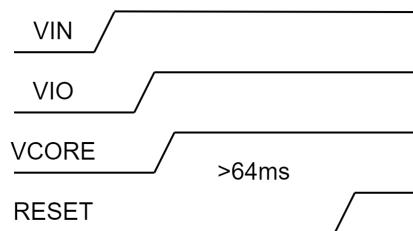

ECK30-T13IA 系列核心板采用分离电源方案，严格按照 T113-i 手册中的电压、功率和时序要求进行设计。ECK30-T13IA 系列核心板采用单路直流+5V 电源供电，外部只需要提供 VDD\_5V\_SOM 一路电源输入，其他电源都由核心板内部产生，无需额外供电。

ECK30-T13IA 系列核心板还提供两路电源输出，分别是 VDD\_3V3\_SOM 和 VDD\_1V8\_SOM，可用于底板小功率器件供电和底板 I/O 接口上电时序控制。两路输出电源相关参数见下表。

输出电源参数表

| 电源网络名       | 电源类型 | 电源域 | 典型电压 | 最大电流  |

|-------------|------|-----|------|-------|

| VDD_3V3_SOM | BUCK | VIO | 3.3V | 500mA |

| VDD_1V8_SOM | LDO  | VIO | 1.8V | 100mA |

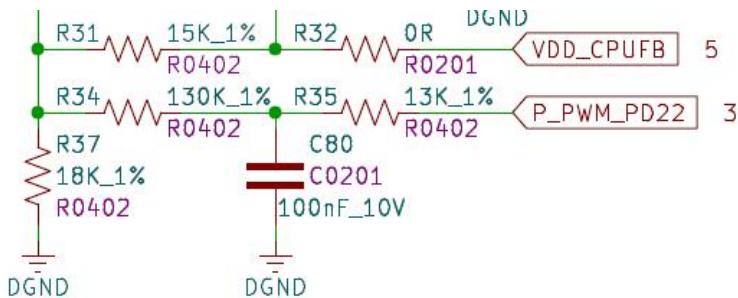

ECK30-T13IA 系列核心板 VDD-CPU 电源设计支持 DVFS 动态调频调压功能。硬件设计使用处理器 PD22 引脚的 PWM 功能作为 DVFS 动态调频调压的控制引脚。软件在 I/O 硬件配置和功能配置时应注意 PD22 引脚和 DVFS 功能的配置。相关硬件原理图如下。

DVFS 功能硬件原理图

ECK30-T13IA 系列核心板，在板未设计备用电池供电的 RTC 功能，所以核心板没有 RTC 电源接口。如果需要备用电池供电的 RTC 功能，可以通过 I2C 总线在底板扩展 RTC 芯片实现。

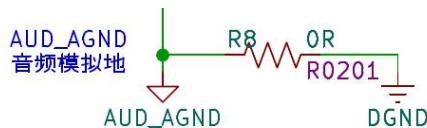

ECK30-T13IA 系列核心板提供两种电源地引脚，分别是数字信号地 DGND 和音频模拟信号地 AUGND。电源功率地和数字信号均参考 DGND，音频模拟信号参考 AUGND。两种

地在核心板上采用单点连接，原理如下图所示。

AUGND 单点接地原理图

ECK30-T13IA 系列核心板电源域和上电时序非常简单，主要电源域就只有 VIN, VIO 和 VCORE 三部分。其中 VCORE 只和处理器有关，和用户 I/O 接口无关，应用时可不关注。ECK30-T13IA 系列核心板上电时序如下图所示。

核心板上电时序图

ECK30-T13IA 系列核心板所有对外 I/O 接口都属于 VIO 电源域，底板可使用核心板输出的 VDD\_3V3\_SOM 或 VDD\_1V8\_SOM 电源作为底板 I/O 接口电源域的控制信号使用。

## 5.7. 在板 I/O 分配

ECK30-T13IA 系列核心板上部分功能占用了 T113-i 处理器的 I/O 功能，这些 I/O 功能未引出到邮票孔，用户在软件配置时应注意这些 I/O 的功能配置。具体占用的 I/O 如下表所示。

核心板在板复用 I/O 分配表

| MPU I/O 引脚 | 网络名称          | 核心板功能描述                |

|------------|---------------|------------------------|

| Y18        | P_PWM_PD22    | DVFS PWM               |

| F2         | LED1          | 在板用户 LED1              |

| F1         | LED2          | 在板用户 LED2              |

| G3         | PC2_eCLK_SCLK | eMMC CLK / SPI0 CLK    |

| G2         | PC3_eCMD_SCS  | eMMC CMD / SPI0 CS     |

| H3         | PC4_eD2_SMOSI | eMMC DATA2 / SPI0 MOSI |

| F5         | PC5_eD1_SMISO | eMMC DATA1 / SPI0 MISO |

| G6         | PC6_eD0_SWP   | eMMC DATA0 / SPI0 WP   |

| G5         | PC7_eD3_SHOLD | eMMC DATA3 / SPI0 HOLD |

## 6. 底板硬件设计

## 6.1. 电源接口

对于嵌入式产品设计，电源系统的设计至关重要，不但需要考虑电源本身的基本电气参数，还要考虑电源的稳定性设计、时序设计等多种因素。ECK30-T13IA 系列核心板采用了单电源供电方案，并提供电源时序管理信号，尽量简化用户底板电源设计。

### 6.1.1. 电源输入

ECK30-T13IA 系列核心板采用单路直流+5V 电源供电，对应邮票孔连接器的 139、140 引脚，供电电源引脚名为 VDD\_5V\_SOM。供电电压范围为 5.0V±10%。ECK30-T13IA 系列核心板正常功耗为 1W 左右。底板在对核心板供电电源设计时，要考虑 I/O 输出功耗和更多功能同时运行时增加的功耗，还要考虑高温下元器件功耗的增加，所以建议核心板供电电流设计不应小于 0.5A。

如果采用 DC-DC 电源对核心板供电，在电源设计时电源功率裕度也不应太大。如果电源设计功率太大，很多电源为保证转换效率，会工作在不连续 PWM 模式下，输出电源纹波会显著增大，不利于数字信号系统的工作稳定性。如果采用 LDO 对核心板供电，设计时应考虑 LDO 自身的功率损耗和工作温升，防止在高温环境或散热不好的环境中工作时，LDO 电源超温停止工作或烧毁。

### 6.1.2. 电源输出

ECK30-T13IA 系列核心板还提供两路电源输出，分别是 VDD\_3V3\_SOM 和 VDD\_1V8\_SOM，可用于底板小功率器件供电和底板 I/O 接口上电时序控制。

### 6.1.3. 电源控制

ECK30-T13IA 系列核心板所有对外 I/O 接口都属于 VIO 电源域，底板可使用核心板输出的 VDD\_3V3\_SOM 或 VDD\_1V8\_SOM 电源作为底板 I/O 接口电源域的控制信号使用。

### 6.1.4. 引脚定义

电源引脚定义表

| 引脚  | 网络名称        | MPU | 电平/电源轨     | 类型  | 走线长度 | 说明           |

|-----|-------------|-----|------------|-----|------|--------------|

| 97  | AUGND       |     | -          | PWR |      |              |

| 106 | AUGND       |     | -          | PWR |      |              |

| 135 | VDD_3V3_SOM |     | 3.3V / VIO | PWR |      | 最大供电电流 500mA |

| 136 | VDD_1V8_SOM |     | 1.8V / VIO | PWR |      | 最大供电电流 100mA |

| 139 | VDD_5V_SOM  |     | 5V / VIN   | PWR |      |              |

| 140 | VDD_5V_SOM  |     | 5V / VIN   | PWR |      |              |

## 6.2.启动配置

### 6.2.1. 启动顺序配置

ECK30-T13IA 系列核心板启动时，处理器会读取 BOOT\_Select 的状态，选择枚举介质的顺序。T113 处理器有 2 个 BOOT\_Select 引脚与 PC 引脚复用，默认内部上拉，启动配置关系如下表所示。

T113 Boot Select 配置表

| ECK30-T13IA<br>存储配置 | PC5<br>BOOT-SEL1 | PC4<br>BOOT-SEL0 | Boot Media                       |

|---------------------|------------------|------------------|----------------------------------|

| --                  | 0                | 0                | SPI NOR => SPI NAND              |

| --                  | 0                | 1                | SMHC0 => SPI NOR => Other media  |

| SPI NAND 存储         | 1                | 0                | SMHC0 => SPI NAND => Other media |

| eMMC 存储             | 1                | 1                | SMHC0 => eMMC2 => Other media    |

ECK30-T13IA 系列核心板 PC5 和 PC4 没有引出到邮票孔，核心板已经将启动顺序配置好了，无需用户底板配置。所有 ECK30-T13IA 系列核心板配置优先从 SMHC0 启动，后续枚举顺序根据在板存储方式不同而不同，如上表所示。

### 6.2.2. FEL 引脚

ECK30-T13IA 系列核心板支持固件强制烧录引脚 FEL。在 ECK30-T13IA 系列核心板未上电时，将 FEL 信号接地，上电后，将 FEL 释放，ECK30-T13IA 系列核心板将进入固件升级模式。用户可以在底板上设计按键或跳线将 FEL 信号接地，强制处理器进入固件升级模式。由于信号在核心板上已经设计了上拉电阻，底板设计只需要考虑接地和适当的 TVS 保护，不要在底板上为 FEL 信号随意设计上拉电阻。如果不使用 FEL 信号，该信号可以悬空处理，可以通过 SD 卡对固件进行升级。

### 6.2.3. 引脚定义

启动配置引脚定义表

| 引脚 | 网络名称    | MPU | 电平/电源轨 | 类型 | 走线长度 | 说明        |

|----|---------|-----|--------|----|------|-----------|

| 2  | FEL_A18 | A18 | 3.3V   | DI |      | 串联 1KΩ 电阻 |

## 6.3.复位按键

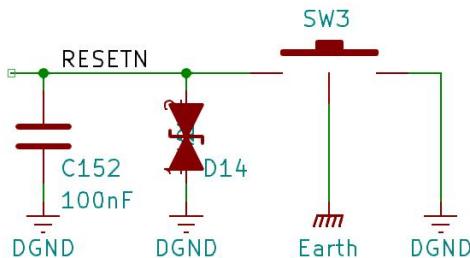

ECK30-T13IA 系列核心板引出的 RESET\_M2 信号可以连接外部按键，用于实现对处理

器的复位控制。RESET\_M2 信号为输入输出双向信号，可以作为外部复位输入，用于复位处理器，也是处理器内存电源复位信号输出。RESET\_M2 信号在核心板内提供了 10K 欧姆上拉电阻。因此在底板应用 RESET\_M2 信号作为手动复位输入时不要再连接上拉电阻，直接连接按键，或者通过 OD 门驱动。也不要通过推挽输出的接口驱动 RESET\_M2 信号。在连接手动输入按键时，可以放置小电容和 TVS 来减小干扰和提高 ESD 性能。按键参考原理图如下图所示。

### 6.3.1. 参考电路

按键参考原理图

注：复位和电源按键信号不要随意通过电阻上拉。如果上拉电源轨不正确，会导致在系统待机或关机的时候，引起不确定信号输入到按键信号接口。

### 6.3.2. 引脚定义

按键引脚定义表

| 引脚 | 网络名称     | MPU | 电平/电源轨 | 类型  | 走线长度 | 说明           |

|----|----------|-----|--------|-----|------|--------------|

| 4  | RESET_M2 | M2  | 3.3V   | I/O |      | 10KΩ pull up |

### 6.3.3. LAYOUT 建议

- ❖ 复位信号是敏感信号，可以包地处理或远离干扰较大的信号；

- ❖ 复位信号 TVS 管尽可能靠近按键摆放。

## 6.4. 参考时钟和 NMI

### 6.4.1. REFCLK\_OUT

处理器 DCXO 时钟模块可以通过 REFCLK\_OUT\_J2 引脚扇出与主时钟同频率的时钟信号。该时钟信号可以提供给底板上的器件做时钟输入，例如 WiFi 模块。在使用该时钟参考输出时要考虑该时钟电平、精度、上电顺序是否适合底板器件。如果不满足，建议不要使用

该时钟信号。

### 6.4.2. NMI

处理器非屏蔽中断信号，主要用于 PMIC 的管理。该引脚功能不建议用户使用。不使用时可悬空处理。

### 6.4.3. 引脚定义

按键引脚定义表

| 引脚 | 网络名称          | MPU | 电平/电源轨 | 类型  | 走线长度 | 说明 |

|----|---------------|-----|--------|-----|------|----|

| 1  | REFCLK_OUT_J2 | J2  | 1.8V   | AO  |      |    |

| 3  | NMI_N3        | N3  | 1.8V   | I/O |      |    |

## 6.5. 显示输出接口

ECK30-T13IA 系列核心板支持 RGB888 (RGB666)、双通道 LVDS (与 RGB 接口复用引脚)、MIPI DSI (与 RGB 接口复用引脚)、SPI (DBI) 显示接口。PD I/O 上如果只使用一组 LVDS，其他 PD 的 I/O 可以作为普通 I/O 使用。

- 双通道 LVDS 接口最高支持 1920×1080@60fps;

- 单通道 LVDS 接口最高支持 1366×768@60fps;

- 并行 RGB 接口最高支持 1920×1080@60fps;

- SPI 接口最高支持 240×320@60fps;

- 4-lane MIPI DSI 接口最高支持 1920×1200@60fps。

DBI 接口与 SPI1 的复用关系如下表所示。

DBI 与 SPI1 复用表

| DBI 功能              | SPI1 功能   |

|---------------------|-----------|

| DBI-CSX             | SPI1-CS   |

| DBI-SCLK            | SPI1-CLK  |

| DBI-SDO/SDA         | SPI1-MOSI |

| DBI-SDI(WRX)/TE/DCX | SPI1-MISO |

| DBI-DCX/WRX         | SPI1-HOLD |

| DBI-TE              | SPI1-WP   |

客户可以根据自己的需求配置显示分辨率和显示数据格式。屏幕应用中，可以使用 GPIO 控制屏幕电源和背光电源。可以使用 PWM 输出控制背光亮度。还可以使用 I2C 和 GPIO 外部中断功能连接触摸屏。可选用亿佰特的液晶触摸屏模块配合使用，相关模块信息详见

官网 <https://www.ebyte.com/>。

## 6.5.1. 接口定义

显示接口定义表

| 引脚 | 网络名称     | MPU | 电平/电源轨 | 类型  | 走线长度    | 说明                         |

|----|----------|-----|--------|-----|---------|----------------------------|

| 58 | PB2_M16  | M16 | 3.3V   | I/O | 1126.85 | LCD0_D0                    |

| 59 | PB3_M15  | M15 | 3.3V   | I/O | 1082.91 | LCD0_D1                    |

| 67 | PD0_W19  | W19 | 3.3V   | I/O | 1017.36 | LCD0_D2/LVDS0_V0P/DSI_D0P  |

| 68 | PD1_V20  | V20 | 3.3V   | I/O | 1016.69 | LCD0_D3/LVDS0_V0N/DSI_D0N  |

| 69 | PD2_V19  | V19 | 3.3V   | I/O | 1016.5  | LCD0_D4/LVDS0_V1P/DSI_D1P  |

| 70 | PD3_U20  | U20 | 3.3V   | I/O | 1016.65 | LCD0_D5/LVDS0_V1N/DSI_D1N  |

| 72 | PD4_U19  | U19 | 3.3V   | I/O | 1034.18 | LCD0_D6/LVDS0_V2P/DSI_CKP  |

| 73 | PD5_U18  | U18 | 3.3V   | I/O | 1037.15 | LCD0_D7/LVDS0_V2N/DSI_CKN  |

| 60 | PB4_K16  | K16 | 3.3V   | I/O | 1097.01 | LCD0_D8                    |

| 61 | PB5_K15  | K15 | 3.3V   | I/O | 1125.02 | LCD0_D9                    |

| 74 | PD6_T19  | T19 | 3.3V   | I/O | 1031.65 | LCD0_D10/LVDS0_CKP/DSI_D2P |

| 75 | PD7_T18  | T18 | 3.3V   | I/O | 1031.69 | LCD0_D11/LVDS0_CKN/DSI_D2N |

| 76 | PD8_R20  | R20 | 3.3V   | I/O | 1017.22 | LCD0_D12/LVDS0_V3P/DSI_D3P |

| 77 | PD9_R19  | R19 | 3.3V   | I/O | 1019.47 | LCD0_D13/LVDS0_V3N/DSI_D3N |

| 79 | PD10_T17 | T17 | 3.3V   | I/O | 1018.78 | LCD0_D14/LVDS1_V0P         |

| 80 | PD11_R17 | R17 | 3.3V   | I/O | 1018.77 | LCD0_D15/LVDS1_V0N         |

| 62 | PB6_K17  | K17 | 3.3V   | I/O | 1113.72 | LCD0_D16                   |

| 63 | PB7_J15  | J15 | 3.3V   | I/O | 1038.85 | LCD0_D17                   |

| 81 | PD12_P19 | P19 | 3.3V   | I/O | 1017.67 | LCD0_D18/LVDS1_V1P         |

| 82 | PD13_P18 | P18 | 3.3V   | I/O | 1018.78 | LCD0_D19/LVDS1_V1N         |

| 83 | PD14_N17 | N17 | 3.3V   | I/O | 1016.2  | LCD0_D20/LVDS1_V2P         |

| 84 | PD15_N16 | N16 | 3.3V   | I/O | 1019.47 | LCD0_D21/LVDS1_V2N         |

| 86 | PD16_N20 | N20 | 3.3V   | I/O | 1031.7  | LCD0_D22/LVDS1_CKP         |

| 87 | PD17_N19 | N19 | 3.3V   | I/O | 1034.48 | LCD0_D23/LVDS1_CKN         |

| 88 | PD18_M19 | M19 | 3.3V   | I/O | 1032.43 | LCD0_CLK/LVDS1_V3P         |

| 89 | PD19_M18 | M18 | 3.3V   | I/O | 1034.74 | LCD0_DE/LVDS1_V3N          |

| 90 | PD21_V18 | V18 | 3.3V   | I/O | 1095.57 | LCD0_VSYNC                 |

| 91 | PD20_W18 | W18 | 3.3V   | I/O | 1126.38 | LCD0_HSYNC                 |

## 6.5.2. LAYOUT 建议

- ❖ 数据及时钟差分对需遵循等长等距规则，差分对误差控制+-5mil，差分阻抗 100 欧；

- ❖ 差分走线少打过孔，保证差分对同时打过孔，并在差分对过孔旁放置地孔；

- ❖ 数据差分对需要以时钟差分对为参考做组间等长，等长+-50mil；

- ❖ 差分走线参考平面应完整，走线不要跨分割；

- ❖如果底板 RGB 信号设计有串联匹配电阻，建议靠近核心板邮票孔放置；

- ❖RGB 信号在核心板内已做等长处理，核心板内走线长度见引脚定义表；

- ❖核心板内 RGB 信号按照单端  $50\Omega \pm 10\%$  阻抗控制，底板阻抗控制建议保持一致；

- ❖建议底板 RGB 信号走线做等长控制，误差范围 $\pm 25\text{mil}$ ，信号线间距至少 2W。

## 6.6. 数字摄像头接口

ECK30-T13IA 系列核心板 CSI 接口支持 8bit DVP 接口、BT656 接口和 BT601 接口输入，并行 CSI 接口可支持最大像素时钟为 148.5MHz，BT656 接口在时钟双沿采样模式下，可支持 2\*1080p@30fps 输入。ECK30-T13IA 系列核心板 CSI 接口只支持 3.3V I/O 电平。

在实际底板应用中，并行 CSI 接口会占用大量 I/O 引脚，减少其他复用功能，可以考虑使用 USB 接口摄像头实现摄像头功能。

### 6.6.1. 接口定义

数字摄像头接口定义表

| 引脚 | 网络名称    | MPU | 电平/电源轨 | 类型  | 走线长度    | 说明            |

|----|---------|-----|--------|-----|---------|---------------|

| 48 | PE0_V1  | V1  | 3.3V   | I/O | 1012.2  | CSI 水平同步信号    |

| 49 | PE1_U1  | U1  | 3.3V   | I/O | 1012.06 | CSI 垂直同步信号    |

| 50 | PE2_U2  | U2  | 3.3V   | I/O | 1011.86 | CSI 像素时钟      |

| 51 | PE3_U3  | U3  | 3.3V   | I/O | 1010.43 | CSI 主时钟       |

| 36 | PE4_T2  | T2  | 3.3V   | I/O | 1010.35 | CSI Data Bit0 |

| 37 | PE5_T3  | T3  | 3.3V   | I/O | 1012.91 | CSI Data Bit1 |

| 38 | PE6_R1  | R1  | 3.3V   | I/O | 1010.38 | CSI Data Bit2 |

| 39 | PE7_R2  | R2  | 3.3V   | I/O | 1011.52 | CSI Data Bit3 |

| 40 | PE8_R3  | R3  | 3.3V   | I/O | 1010.62 | CSI Data Bit4 |

| 41 | PE9_P2  | P2  | 3.3V   | I/O | 1009.88 | CSI Data Bit5 |

| 42 | PE10_P3 | P3  | 3.3V   | I/O | 1007.44 | CSI Data Bit6 |

| 43 | PE11_N1 | N1  | 3.3V   | I/O | 1011.75 | CSI Data Bit7 |

### 6.6.2. LAYOUT 建议

- ❖CSI 信号在核心板内已做等长处理，核心板内走线长度见引脚定义表；

- ❖核心板内 CSI 信号按照单端  $50\Omega \pm 10\%$  阻抗控制，底板阻抗控制建议保持一致；

- ❖建议底板 CSI 信号走线做等长控制，误差范围 $\pm 25\text{mil}$ ，信号线间距至少 2W。

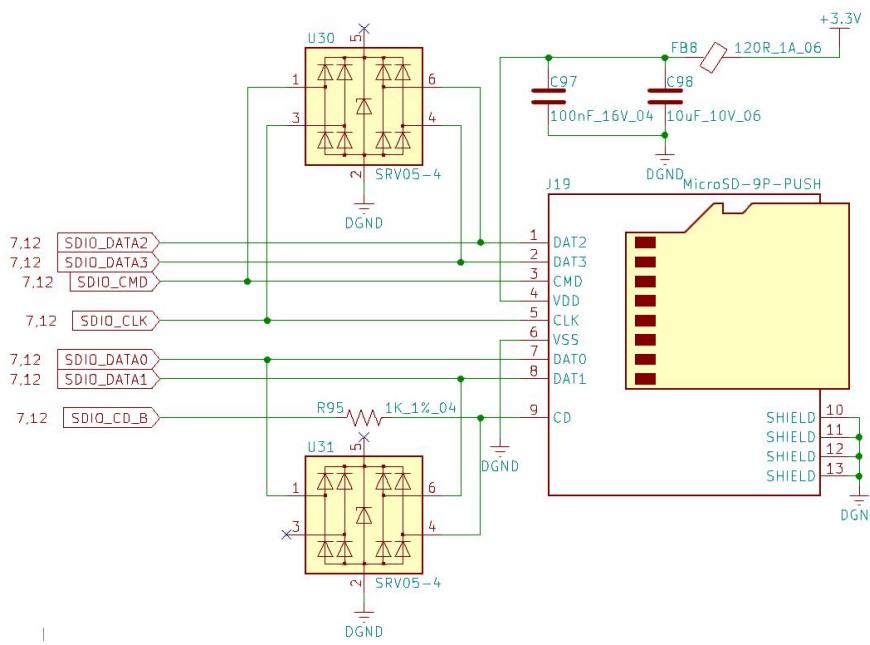

## 6.7.SD/MMC 卡接口

ECK30-T13IA 系列核心板搭载了 3 路 SMHC (SD/MM host controller) 控制器，包括 SMHC0、SMHC1、SMHC2。SMHC0 符合 Secure Digital Memory v3.0 协议，通常用于连接 SD 卡。SMHC1 符合 Secure Digital I/O v3.0 协议，通常用于连接扩展功能，例如 WiFi 模块。SMHC2 符合 Multimedia Card v5.0 协议，通常用于连接 eMMC 存储芯片。ECK30-T13 IA 系列核心采用 SMHC2 扩展了在板 eMMC 存储芯片。推荐底板使用 SMHC0 连接 SD 卡。SMHC1 推荐扩展其他设备或不使用。

处理器的 I/O 可以配置片内上拉电阻。这些上拉电阻可满足 SD 卡接口扩展时的上拉需求，用户设计无需外部上拉电阻。核心板在 PF2\_D2 的时钟信号上已经串联了 33 欧姆匹配电阻，用户设计也无需外部串联电阻。通过 SMHC0 接口扩展 Micro SD 卡，可参考以下原理图设计。

### 6.7.1. 参考电路

SD 卡参考电路图

### 6.7.2. 引脚定义

SMHC0 接口信号引脚定义

| 引脚 | 网络名称   | MPU | 电平/电源轨 | 类型  | 走线长度    | 说明      |

|----|--------|-----|--------|-----|---------|---------|

| 28 | PF1_C1 | C1  | 3.3V   | I/O | 1129.58 | SDC0_D0 |

| 27 | PF0_C2 | C2  | 3.3V   | I/O | 1122.36 | SDC0_D1 |

| 30 | PF5_E2 | E2  | 3.3V   | I/O | 1131.95 | SDC0_D2 |

| 32 | PF4_E3 | E3  | 3.3V   | I/O | 1124.16 | SDC0_D3 |

|    |        |    |      |     |         |          |

|----|--------|----|------|-----|---------|----------|

| 31 | PF3_D1 | D1 | 3.3V | I/O | 1130.76 | SDC0_CMD |

| 29 | PF2_D2 | D2 | 3.3V | I/O | 1129.74 | SDC0_CLK |

### 6.7.3. LAYOUT 建议

- ❖ 核心板内 SMHC 信号按照单端  $50\Omega \pm 10\%$  阻抗控制，底板阻抗控制建议保持一致；

- ❖ SMHC 信号在核心板内已做等长处理，核心板内走线长度见引脚定义表；

- ❖ 建议底板 SMHC 信号（不含插入检测信号）走线做等长控制，误差范围 $\pm 50\text{mil}$ ，信号线间距至少  $2W$ ；

- ❖ 插入检测信号串联  $1\text{K}$  欧姆电阻，提高 ESD 性能；

- ❖ 时钟信号与其他信号的距离遵循  $3W$  规则。

## 6.8. USB 接口

ECK30-T13IA 系列核心板支持 2 路 USB2.0 接口。USB0 支持 HOST 和 Device 模式，USB1 仅支持 HOST 模式。

如果用户使用 USB 的 OTG 功能，则 USB 接口推荐使用 MICRO USB 接口，因为该接口是 5 线接口，有 USB\_ID（可通过 GPIO 功能复用实现）信号，可以用来识别 HOST 和 DEVICE，从而实现 OTG 功能。如果用户不使用 USB 的 OTG 功能，只当做 USB HOST 使用，那么 USB 接口选择 4 线、5 线的接口都可以。

由于 T113 系列处理器的 USB 接口信号未提供单独的 VBUS 电源供电。USB 接口信号属于 VIO 电源域。当 USB 接口作为 DEVICE 使用时，应避免外部 HOST 设备先上电。如果外部 HOST 设备先上电，在 USB OTG 信号上可能会形成漏电，有影响处理器启动或损坏接口功能的风险。

### 6.8.1. 引脚定义

USB 接口信号引脚定义

| 引脚  | 网络名称       | MPU | 电平/电源轨 | 类型  | 走线长度   | 说明 |

|-----|------------|-----|--------|-----|--------|----|

| 129 | USB1_DP_A8 | A8  | -      | I/O | 960.34 |    |

| 130 | USB1_DM_B8 | B8  | -      | I/O | 962.55 |    |

| 132 | USB0_DP_B7 | B7  | -      | I/O | 957.89 |    |

| 133 | USB0_DM_C7 | C7  | -      | I/O | 959.18 |    |

## 6.8.2. LAYOUT 建议

- ❖ USB 信号走线做等长控制，差分对内误差±5mil，相邻差分对间距 3W 以上；

- ❖ USB 信号的差分阻抗按 90Ω控制；

- ❖ USB 信号线尽可能短。

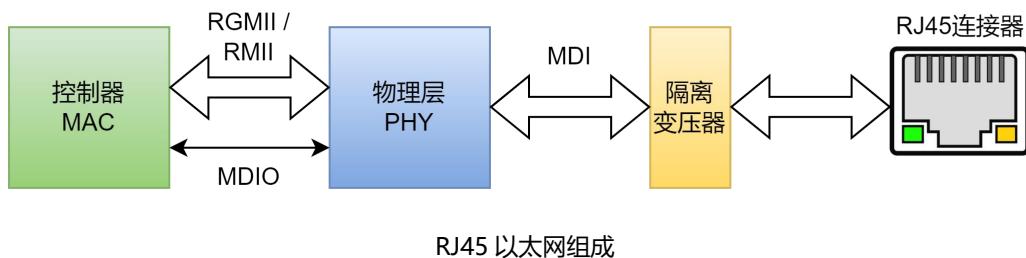

## 6.9. 以太网接口

ECK30-T13IA 系列核心板支持 1 路 10M/100M/1000M 自适应以太网控制器。以太网控制器支持 RGMII 与 RMII 接口。ECK30-T13IA 系列核心板 MII 接口复用于 PE/PG 引脚，只支持 3.3V 电平。

通常一个 RJ45 以太网接口主要由以太网控制器 MAC (Media Access Control)，以太网物理层接口 PHY (Physical Layer)，以太网变压器，RJ45 连接器几部分组成，如下图所示。

ECK30-T13IA 系列核心板板内没有设计以太网 PHY 电路，用户使用以太网功能，需要在底板上设计 PHY 接口芯片电路。底板 PHY 接口芯片电路设计可以参考亿佰特单板机产品图纸。

## 6.9.1. 引脚定义

以太网接口信号引脚定义

| 引脚 | 网络名称    | MPU | 电平/电源轨 | 类型  | 走线长度    | 说明           |

|----|---------|-----|--------|-----|---------|--------------|

| 36 | PE4_T2  | T2  | 3.3V   | I/O | 1010.35 | RGMII_TXD0   |

| 37 | PE5_T3  | T3  | 3.3V   | I/O | 1012.91 | RGMII_TXD1   |

| 43 | PE11_N1 | N1  | 3.3V   | I/O | 1011.75 | RGMII_TXD2   |

| 34 | PE12_R5 | R5  | 3.3V   | I/O | 1117.23 | RGMII_TXD3   |

| 38 | PE6_R1  | R1  | 3.3V   | I/O | 1010.38 | RGMII_TXCTRL |

| 51 | PE3_U3  | U3  | 3.3V   | I/O | 1010.43 | RGMII_TXCK   |

| 49 | PE1_U1  | U1  | 3.3V   | I/O | 1012.06 | RGMII_RXD0   |

| 50 | PE2_U2  | U2  | 3.3V   | I/O | 1011.86 | RGMII_RXD1   |

| 35 | PE13_R4 | R4  | 3.3V   | I/O | 1011.36 | RGMII_RXD2   |

|    |         |    |      |     |         |              |

|----|---------|----|------|-----|---------|--------------|

| 44 | PE14_N4 | N4 | 3.3V | I/O | 1009.9  | RGMII_RXD3   |

| 48 | PE0_V1  | V1 | 3.3V | I/O | 1012.2  | RGMII_RXCTRL |

| 45 | PE15_N5 | N5 | 3.3V | I/O | 1012.78 | RGMII_RXCK   |

| 40 | PE8_R3  | R3 | 3.3V | I/O | 1010.62 | MDC          |

| 41 | PE9_P2  | P2 | 3.3V | I/O | 1009.88 | MDIO         |

## 6.9.2. LAYOUT 建议

- ❖ RGMII 信号发送和接收分组做等长控制，误差±25mil，线间距 2W 以上；

- ❖ 网络差分信号做等长控制，差分对内误差±10mil，相邻差分对间距 3W 以上；

- ❖ 网口变压器靠近 PHY 芯片放置，距离建议不超过 20mm；

- ❖ PHY 芯片的电源引脚去耦电容靠近 PHY 芯片放置；

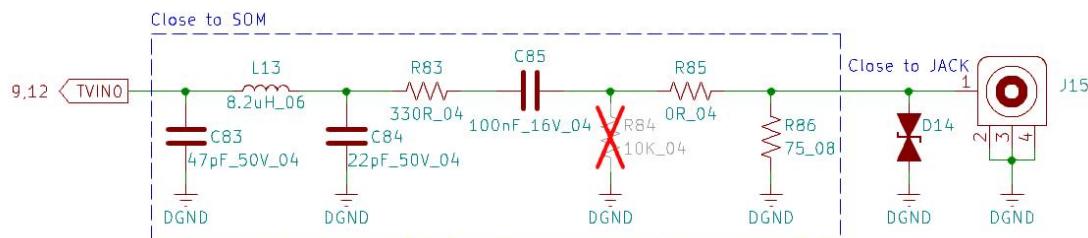

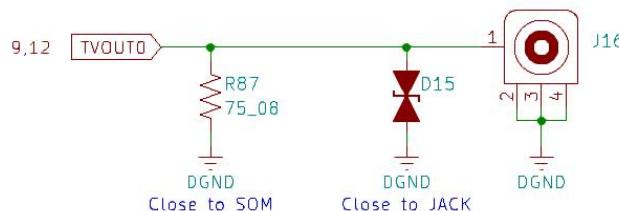

## 6.10.CVBS 接口

ECK30-T13IA 核心板提供 2 路 CVBS 模拟视频输入，1 路 CVBS 模拟视频输出。只需在底板放置少量滤波、匹配和保护电路就可以实现模拟视频输入、输出接口功能。

### 6.10.1. 参考电路

CVBS 输入接口电路图

CVBS 输出接口电路图

### 6.10.2. 引脚定义

模拟视频信号引脚定义

| 引脚  | 网络名称       | MPU | 电平/电源轨 | 类型 | 走线长度 | 说明 |

|-----|------------|-----|--------|----|------|----|

| 117 | TVOUT0_E19 | E19 | -      | AO |      |    |

| 118 | TVIN1_C9   | C9  | -      | AI |      |    |

|     |          |    |   |    |  |  |

|-----|----------|----|---|----|--|--|

| 119 | TVIN0_B9 | B9 | - | AI |  |  |

|-----|----------|----|---|----|--|--|

### 6.10.3. LAYOUT 建议

- ❖ 靠近接口放置 TVS;

- ❖ 匹配 75 欧姆电阻有功率要求，建议 0805 或以上尺寸封装；

- ❖ 走线阻抗控制为 37.5 欧姆；

- ❖ 模拟信号走线，应远离干扰，可包地处理。

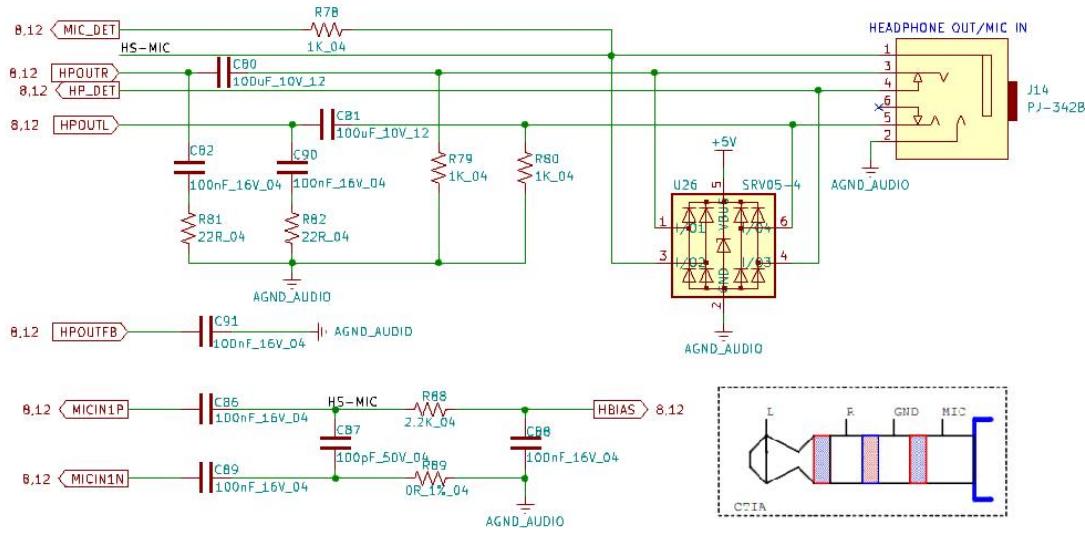

## 6.11. 模拟音频接口

T113-i 芯片内部集成了音频 codec 功能，可提供模拟音频接口。ECK30-T13IA 核心板引出了 2 路模拟音频输出接口（LINEOUT、HPOUT），5 路模拟音频输入接口（MICIN\*3、FMIN、LINEIN）。

### 6.11.1. 参考电路

模拟音频耳麦接口原理图

### 6.11.2. 引脚定义

模拟音频信号引脚定义

| 引脚 | 网络名称        | MPU | 电平/电源轨 | 类型  | 走线长度 | 说明      |

|----|-------------|-----|--------|-----|------|---------|

| 93 | FMINR_C17   | C17 | -      | AI  |      |         |

| 94 | FMINL_B17   | B17 | -      | AI  |      |         |

| 95 | LINEINR_C16 | C16 | -      | AI  |      |         |

| 96 | LINEINL_B16 | B16 | -      | AI  |      |         |

| 97 | AUGND       | -   | AGND   | PWR |      | 音频模拟信号地 |

|     |                |     |      |     |  |         |

|-----|----------------|-----|------|-----|--|---------|

| 98  | MBIAS_E16      | E16 | -    | AO  |  | 麦克风偏置电压 |

| 99  | MIC_DET_A17    | A17 | -    | AI  |  | 麦克风插入检测 |

| 100 | MICIN1P_D20    | D20 | -    | AI  |  |         |

| 101 | MICIN1N_D19    | D19 | -    | AI  |  |         |

| 102 | MICIN2P_E15    | E15 | -    | AI  |  |         |

| 103 | MICIN2N_D15    | D15 | -    | AI  |  |         |

| 104 | MICIN3P_D17    | D17 | -    | AI  |  |         |

| 105 | MICIN3N_D16    | D16 | -    | AI  |  |         |

| 106 | AUGND          | -   | AGND | PWR |  | 音频模拟信号地 |

| 107 | LINEOUTRP_B14  | B14 | -    | AO  |  |         |

| 108 | LINEOUTRNL_C14 | C14 | -    | AO  |  |         |

| 109 | LINEOUTLPL_B15 | B15 | -    | AO  |  |         |

| 110 | LINEOUTLNL_C15 | C15 | -    | AO  |  |         |

| 111 | HBIAS_E17      | E17 | -    | AO  |  | 耳机偏置电压  |

| 112 | HP_DET_A13     | A13 | -    | AI  |  | 耳机插入检测  |

| 113 | HPOUTR_D13     | D13 | -    | AO  |  |         |

| 114 | HPOUTFB_E13    | E13 | -    | AO  |  |         |

| 115 | HPOUTL_F13     | F13 | -    | AO  |  |         |

### 6.11.3. LAYOUT 建议

- ❖ 靠近接口放置 TVS;

- ❖ 模拟信号走线，应远离干扰，可包地处理。

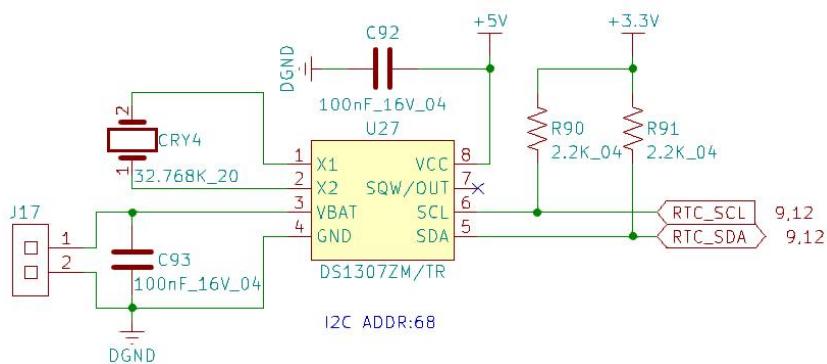

## 6.12.RTC

ECK30-T13IA 核心板上没有使用备用电池供电的 RTC，如果用户需要这种 RTC 功能，可以通过 I2C 总线在底板上扩展该功能。

### 6.12.1. 参考电路

RTC 参考电路图

## 6.13.数字音频接口

ECK30-T13IA 核心板最大支持 2 路数字音频接口（PCM/I2S）。在底板电路设计中，需要把数字音频接口信号接到音频编解码芯片上，通过音频编解码芯片实现耳机、麦克风、扬声器等音频接口功能。

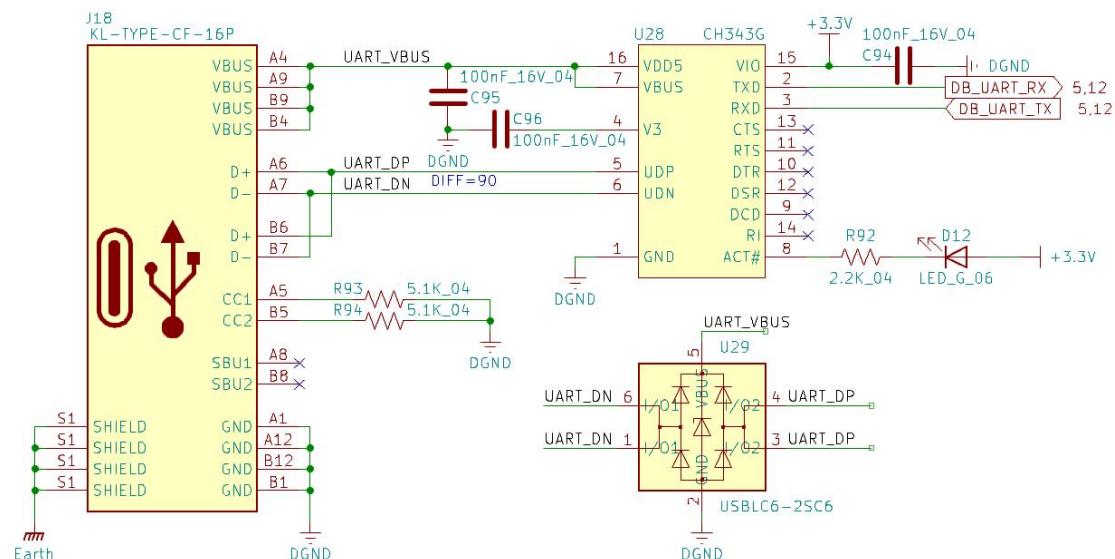

## 6.14.UART 接口

ECK30-T13IA 核心板最大支持 6 路的异步串口，最高支持 4Mbps 波特率。核心板默认使用 UART 0 作为调试串口。

### 6.14.1. 参考电路

为方便调试，底板上可以通过 USB 转串口芯片将调试串口引出为 USB 接口，USB 转串口电路原理图可参考下图。CH343G 芯片提供了 VIO 电源，可以有效的解决串口 I/O 电平兼容和电源域上电时序的问题。

USB 调试串口参考原理图

## 6.15.SPI 接口

ECK30-T13IA 系列核心板引出 1 路 SPI 接口，支持主/从模式。SPI 信号包括 SPI\_CLK、SPI\_SS、SPI\_MOSI 和 SPI\_MISO，设计时要先确认主从设备的关系，进而确认 MOSI 和 MISO 信号的方向。1 路 SPI 只提供 1 个片选信号。

## 6.16.I2C 接口

ECK30-T13IA 系列核心板支持 4 路 I2C 控制器，支持 2 种时钟频率模式，标准模式下的速率为 100Kbit/s，快速模式下的速率为 400Kbit/s。

同一 I2C 总线下可以挂载若干个设备，在原理图设计时需要注意以下几点：

- a) 检查同一总线下的设备地址是否冲突；

- b) 保证每条 I2C 总线上都有一对上拉电阻，阻值建议 2.2K~10K，但不要重复添加；

- c) 核心板内未提供 I2C 总线上拉电阻，需要用户在底板应用时上拉；

- d) 检查设备的 I2C 接口电平是否是 3.3V，如果不是，需要加电平转换电路；

- e) 检查 I2C 接口电源轨是否一致，不同时间域的 I2C 接口互联时，需要考虑总线开关电路；

- f) 同一总线下的设备数量不要过多，否则有可能超出 I2C 规范要求的 400pF 的负载电容限制，影响信号波形。

## 6.17.CAN 接口

ECK30-T13IA 系列核心板支持 2 路 CAN 控制器，支持 CAN 2.0A 和 CAN 2.0B 协议，只需要外接 CAN 收发器即可以进行 CAN 通讯。

## 6.18.ADC 接口

ECK30-T13IA 系列核心板提供 3 种 ADC 接口，分别是 1 路 LRADC (Low Rate ADC)，2 路 GPADC (General Purpose ADC)，4 路 TPADC (Touch Panel ADC)。

LRADC:

- ❖ 6bit 分辨率，应用于按键电压识别，最大采样率 2KHz，采样电压范围为：0~1.266V；

- ❖ LRADC 应用于按键识别时，如按键采用分压电阻方式时，推荐使用 1%精度电阻；

- ❖ LRADC 如不使用，核心板引脚可悬空，板内已提供 51K 上拉到 AVCC。

GPADC:

- ❖ 12bit 分辨率，最大采样率 1MHz，采样电压范围为：0~1.8V；

- ❖ GPADC 不建议应用于外部有浪涌或高压的 I/O 接口端电压识别，避免造成芯片接口损坏。

#### TPADC:

- ◆ 4 路 TPADC 接口，12bit 分辨率，8bit 采样精度，最大采样率 1MHz，可用于连接 4 线 RTP 屏或用作 AD\_KEY 功能。

## 6.19.GPIO 接口

ECK30-T13IA 系列核心板最大可提供 79 路 GPIO 接口，但大部分都存在复用功能。用户可根据自身需求对 GPIO 进行灵活配置。

## 6.20.硬件设计检查项

- ◆ 电源轨：检查 I/O 接口应用是否存在电源轨不一致的问题，例如 1.8V 的信号连接到 3.3V 的信号上。如果出现不同电源轨信号的连接需求，应采用电平转换电路处理。

- ◆ 上电时序：检查底板与核心板连接的信号是否存在底板信号先上电，或者两个板卡信号上电时间差异很大的情况。

- ◆ 上拉和下拉电阻：复用 I/O 接口在上电软件配置前存在输出状态不确定的情况，如果信号需要上电时保持确定电平，应在底板上设计上下拉电阻。部分功能信号也需要在底板上设计上拉或下拉电阻，如 I2C 信号。在设计上拉电阻时应注意上拉电源轨的设计。

- ◆ ESD 保护：对外接口信号应考虑相应的 ESD 保护设计，ESD 方案的选择应考虑信号速率、通讯协议和应用环境的要求。

- ◆ 高速信号等长：高速信号应考虑 PCB 的等长设计，包括 USB、以太网、SDIO、显示等。

- ◆ 阻抗控制：高速信号应考虑 PCB 阻抗控制，阻抗控制的关键是保持阻抗的连续性，底板应参考核心板信号的阻抗进行设计。

## 7. 软件资源

ECK30-T13IA 系列核心板搭载基于 Linux 5.4.61 版本内核的操作系统，开发板出厂附带嵌入式 Linux 系统开发所需要的交叉编译工具链，U-boot 源代码，Linux 内核和各驱动模块的源代码，以及适用于 Windows 桌面环境和 Linux 桌面环境的各种开发调试工具。

#### 操作系统：

Ubuntu 18.04 系统

系统源码:

u-boot 2018.07

Kernel 5.4.61

Buildroot 201902

Buildroot 202205

openwrt

开发环境及工具:

USB 烧录工具: PhoenixSuit

SD 卡烧录工具: PhoenixCard

## 7.1. 系统资源

系统软件资源表

| 类别            | 名称               | 描述                  | 源码                                          |

|---------------|------------------|---------------------|---------------------------------------------|

| SPL           | spl-pub          | Boot0, 引导 uboot     | <SDK>/brandy/brandy-2.0/spl-pub/            |

| BOOT          | u-boot 2018.07   | 引导程序                | <SDK>/brandy/brandy-2.0/u-boot-2018/        |

| Kernel        | Kernel 5.4.61    | Linux 内核            | <SDK>/kernel/linux-5.4/                     |

| Device Driver | Audio            | 内置音频驱动              | sound/soc/sunxi_v2/*                        |

|               | AWlink           | CAN 驱动              | drivers/net/can/sunxi_awlink.c              |

|               | GMAC             | 内置 MAC 驱动           | drivers/net/ethernet/allwinner/sunxi-gmac.c |

|               | GPADC            | GPADC 驱动            | drivers/input/sensor/sunxi_gpadc.c          |

|               | GPIO             | GPIO 驱动             | drivers/pinctrl/sunxi                       |

|               | LCD              | Disp2 显示驱动          | drivers/video/fbdev/sunxi/disp2/disp/lcd/   |

|               | LRADC            | 按键模块驱动              | drivers/input/keyboard/sunxi-keyboard.c     |

|               | SMHC             | MMC 驱动              | drivers/mmc/host/sunxi-mmc.c                |

|               | SPI              | SPI 驱动              | drivers/spi/spi-sunxi.c                     |

|               | SPI-NAND         | SPI-NAND 驱动         | drivers/mtd/awnand/spinand                  |

|               | TVD              | CVBS 输入             | drivers/media/platform/sunxi-tvd/           |

|               | TVE              | CVBS 输出             | drivers/video/fbdev/sunxi/disp2/tv/         |

|               | TWI              | I2C 驱动              | drivers/i2c/busses/i2c-sunxi.c              |

|               | UART             | 串口驱动                | drivers/tty/serial/sunxi-uart.c             |

|               | VIN              | CSI 驱动程序            | drivers/media/platform/sunxi-vin/           |

| 操作系统          | Buildroot 201902 | 201902 版本 Buildroot | <SDK>/buildroot/buildroot-201902            |

|               | Buildroot 202205 | 202205 版本 Buildroot | <SDK>/buildroot/buildroot-202205            |

|               | openwrt          | openwrt             | <SDK>/openwrt/openwrt                       |

| 开发工具          | PhoenixSuit      | USB 烧录工具            | /tools/PhoenixSuit                          |

|               | PhoenixCard      | SD 卡烧录工具            | /tools/PhoenixCard                          |

## 8. 结构尺寸

ECK30-T13IA 系列核心板采用 140 PIN, 1.0mm 间距邮票孔接口形式，可 STM 焊接，也可以手工焊接。核心板底层无器件，无裸露走线，底板设计简单。核心板结构尺寸见下图。

邮票孔核心板结构尺寸图

邮票孔尺寸图

## 9. 焊接指导

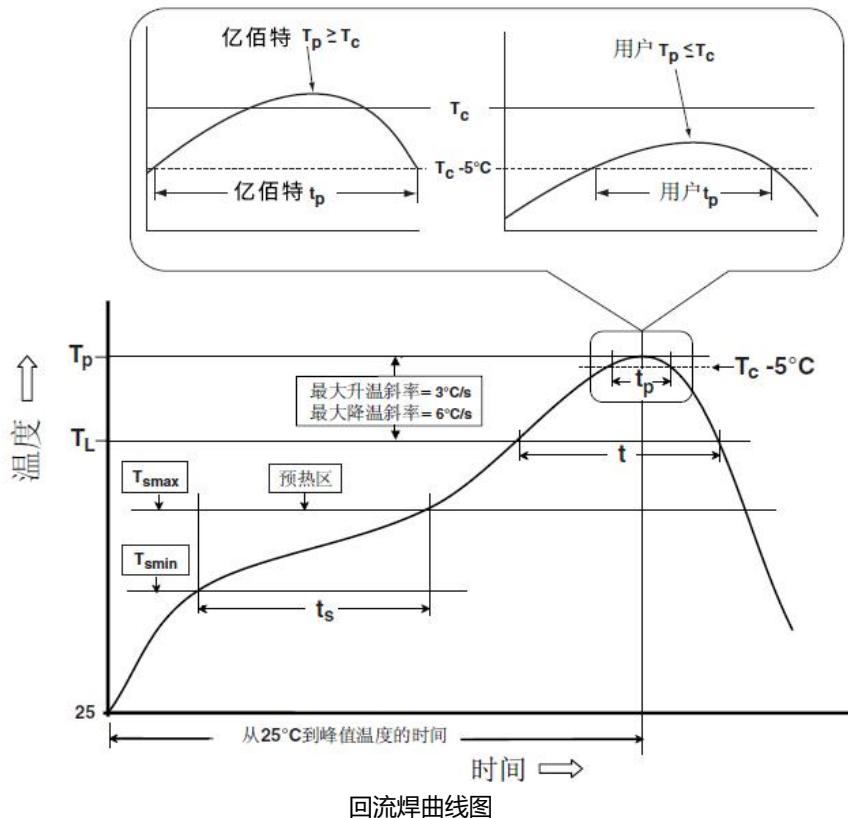

### 9.1. 回流焊温度

回流焊温度表

| 回流焊曲线特征      |                  | 有铅工艺组装         | 无铅工艺组装         |

|--------------|------------------|----------------|----------------|

| 预热/保温        | 最低温度 (Tsmin)     | 100°C          | 150°C          |

|              | 最高温度 (Tsmax)     | 150°C          | 200°C          |

|              | 时间 (Tsmin~Tsmax) | 60~120 秒       | 60~120 秒       |

| 升温斜率 (TL~Tp) |                  | 3°C/秒, 最大值     | 3°C/秒, 最大值     |

| 液相温度 (TL)    |                  | 183°C          | 217°C          |

| TL 以上保持时间    |                  | 60~90 秒        | 60~90 秒        |

| 封装体峰值温度 Tp   |                  | 用户不能超过产品“潮湿敏感” | 用户不能超过产品“潮湿敏感” |

|                                            |            |            |

|--------------------------------------------|------------|------------|

|                                            | 度”标签标注的温度。 | 度”标签标注的温度。 |

| 在指定分级温度 ( $T_c$ ) 5°C 以内的时间 ( $t_p$ ), 见下图 | 20 秒       | 30 秒       |

| 降温斜率 ( $T_p \sim T_L$ )                    | 6°C/秒, 最大值 | 6°C/秒, 最大值 |

| 室温到峰值温度的时间                                 | 6 分钟, 最长   | 8 分钟, 最长   |

| ※温度曲线的峰值温度 ( $T_p$ ) 容差定义是用户的上限            |            |            |

## 9.2. 回流焊曲线图

## 10. 参考文档

T113-i\_V1.9.pdf

## 11. 修订说明

修订说明表

| 版本   | 修改内容                   | 修改时间     | 编制  | 校对  | 审批  |

|------|------------------------|----------|-----|-----|-----|

| V1.0 | 初稿                     | 24-09-25 | WFX | WYQ | WFX |

| V1.1 | 更改 SMHC1 和 USB 部分描述错误。 | 24-11-25 | WFX | WYQ | WFX |

|      |                        |          |     |     |     |

## 12. 关于我们

销售热线: 4000-330-990

技术支持: [support@cdebyte.com](mailto:support@cdebyte.com) 官方网站: <https://www.ebyte.com>

公司地址: 四川省成都市高新区西区大道 199 号 B5 栋

((o))<sup>®</sup> **成都亿佰特电子科技有限公司**

**E BYTE** Chengdu Ebyte Electronic Technology Co.,Ltd.