# **Technical Product Description SMI130**

Inertial Sensor (6DoF) for Non-Safety Automotive Applications

Document revision 3.0

Release date September-2020

Part number 0273 141 181 (SMI130)

Issued by AE/PAS1.3

This Technical Product Description is for customer information purposes only.

Bosch does not guarantee any parameters or information given within this document.

Parameters may be subject to change at any time without notice.

Please refer to the Technical Customer Documentation for specified values.

# **Table of Contents**

| Ta | able c | of Co | ntents                                                     | 2  |

|----|--------|-------|------------------------------------------------------------|----|

| 1  | Р      | rodu  | ct Identification                                          | 4  |

|    | 1.1    | Mai   | n Functions and Properties                                 | 4  |

|    | 1.2    | Key   | Features                                                   | 4  |

| 2  | G      | ener  | al Product Description                                     | 5  |

|    | 2.1    |       | chanical Design                                            |    |

|    | 2.2    | Sen   | sor Data                                                   | 5  |

|    | 2.3    | Bloc  | ck Diagram                                                 | 6  |

|    | 2.4    | Sigr  | nal Path                                                   | 7  |

|    | 2.     | .4.1  | Accelerometer                                              | 7  |

|    | 2.     | .4.2  | Gyroscope                                                  | 7  |

|    | 2.5    | Orie  | entation of the Sensing Axes                               | 9  |

| 3  | Н      | ardw  | are Interface Description and Packaging                    | 10 |

|    | 3.1    | Pac   | kage Parameters                                            | 10 |

|    | 3.2    | Trar  | nsport Package                                             | 11 |

|    | 3.     | .2.1  | Tape on Reel Specification                                 | 11 |

|    | 3.     | .2.2  | Tape Dimensions                                            | 11 |

|    | 3.     | .2.3  | Reel Dimensions                                            | 11 |

|    | 3.     | .2.4  | Orientation within the Reel                                | 12 |

|    | 3.3    |       | eling of the Product                                       |    |

|    | 3.4    |       | ning                                                       |    |

|    | 3.5    |       | dering                                                     |    |

|    |        | .5.1  | Reflow Soldering Recommendation for Sensors in LGA Package |    |

|    |        | .5.2  | Classification Reflow Profile                              |    |

|    |        | .5.3  | Multiple Reflow Soldering Cycles                           |    |

|    | 3.6    |       | unting Recommendations                                     |    |

|    |        |       | ommendations for PCB Layout                                |    |

| 4  |        |       | nment Specification                                        |    |

|    | 4.1    |       | olut Maximum Ratings                                       |    |

|    | 4.2    | •     | erating Conditions                                         |    |

|    | 4.3    |       | time Conditions                                            |    |

|    | 4.4    |       | ironmental Safety                                          |    |

| 5  |        |       | eter Specification                                         |    |

|    | 5.1    |       | ver Supply                                                 |    |

|    | 5.2    |       | hnical data                                                |    |

|    |        | .2.1  | Accelerometer                                              |    |

|    |        | .2.2  | Gyroscope                                                  |    |

| 6  |        |       | are Interface Description                                  |    |

|    | 6.1    |       | al Peripheral Interface (SPI)                              |    |

|    | 6.     | .1.1  | SPI Connection                                             | 23 |

|    | 6.1.2     | SPI Timing                                | 24 |  |  |  |  |  |

|----|-----------|-------------------------------------------|----|--|--|--|--|--|

|    | 6.2 Two   | -wire Interface (TWI)                     | 26 |  |  |  |  |  |

|    | 6.2.1     | TWI Connection                            | 26 |  |  |  |  |  |

|    | 6.2.2     | TWI Timing                                | 27 |  |  |  |  |  |

|    | 6.3 Acce  | ess Restrictions (SPI and TWI)            | 30 |  |  |  |  |  |

| 7  | Applica   | ation Details                             | 31 |  |  |  |  |  |

|    | 7.1 Sens  | sor Setup                                 | 31 |  |  |  |  |  |

|    | 7.1.1     | Accelerometer                             | 31 |  |  |  |  |  |

|    | 7.1.2     | Gyroscope                                 | 32 |  |  |  |  |  |

|    | 7.2 Self- | -Test                                     | 33 |  |  |  |  |  |

|    | 7.2.1     | Accelerometer                             | 33 |  |  |  |  |  |

|    | 7.2.2     | Gyroscope                                 | 34 |  |  |  |  |  |

|    | 7.3 Inter | rrupt Engine                              | 34 |  |  |  |  |  |

|    | 7.3.1     | New Data Interrupt                        | 34 |  |  |  |  |  |

|    | 7.4 Rea   | ding Data                                 | 35 |  |  |  |  |  |

|    | 7.4.1     | Accelerometer                             | 35 |  |  |  |  |  |

|    | 7.4.2     | Gyroscope                                 | 36 |  |  |  |  |  |

|    | 7.4.3     | Temperature Sensor                        | 36 |  |  |  |  |  |

|    | 7.5 Soft  | Reset                                     | 37 |  |  |  |  |  |

|    | 7.5.1     | Accelerometer                             | 37 |  |  |  |  |  |

|    | 7.5.2     | Gyroscope                                 | 37 |  |  |  |  |  |

|    | 7.6 Reg   | ister Map                                 | 38 |  |  |  |  |  |

|    | 7.6.1     | Register Map Accelerometer                | 38 |  |  |  |  |  |

|    | 7.6.2     | Register Map Gyroscope                    | 45 |  |  |  |  |  |

| 8  | Safety    | Concept                                   | 52 |  |  |  |  |  |

| 9  | Function  | onal and Lifetime Qualification Test Plan | 53 |  |  |  |  |  |

| 10 | ) Disclai | imer                                      | 54 |  |  |  |  |  |

| 11 | Chang     | es                                        | 56 |  |  |  |  |  |

| 12 | •         | Table of Figures 57                       |    |  |  |  |  |  |

# 1 Product Identification

Product Designation: SMI130

Type Designation: Inertial sensor

Product Part Number: 0273 141 181

► This Product is intended for use in: Non-Safety Automotive Applications

## 1.1 Main Functions and Properties

The SMI130 is a combined triaxial accelerometer (ACC) and triaxial gyroscope (GYR) for non-safety related applications, e.g. for in-dash navigation in the passenger compartment. Within one package, the SMI130 offers the detection of acceleration and angular rate for the x-, y-, and z-axis. The digital standard serial peripheral interface (SPI) of the SMI130 allows for bi-directional data transmission.

| Sensor | Bosch Part Nr. | Туре          | Range             | Resolution |

|--------|----------------|---------------|-------------------|------------|

| SMI130 | 0273 141 181   | Accelerometer | ±2, ±4, ±8, ±16 g | 12 bit     |

|        |                | Gyroscope     | ±125 ±2000 °/s    | 16 bit     |

## 1.2 Key Features

| Key Feature                     | Description                                                                                                                                        |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Inertial sensor                 | Advanced triaxial 16 bit gyroscope and a versatile, leading edge triaxial 12 bit accelerometer for reduced PCB space and simplified signal routing |

| Small package                   | LGA, 16 pins, footprint 3.0 x 4.5 mm², height 0.95 mm                                                                                              |

| Common voltage supplies         | VDD voltage range: 2.4 3.6 V                                                                                                                       |

| Digital interface               | SPI, TWI (compatible with I <sup>2</sup> C)                                                                                                        |

| Smart operation and integration | Gyroscope and accelerometer can be operated individually                                                                                           |

| Consumer electronics suite      | MSL1, RoHS compliant, halogen-free                                                                                                                 |

| Operating temperature           | -40 +85 °C                                                                                                                                         |

| Extended operating temperature  | -40 +105 °C (details see chapter 4)                                                                                                                |

| Programmable functionality      | Acceleration and rate ranges selectable Low-pass filter bandwidths selectable                                                                      |

| On-chip temperature sensor      | Factory trimmed, 8 bit, typical                                                                                                                    |

# 2 General Product Description

## 2.1 Mechanical Design

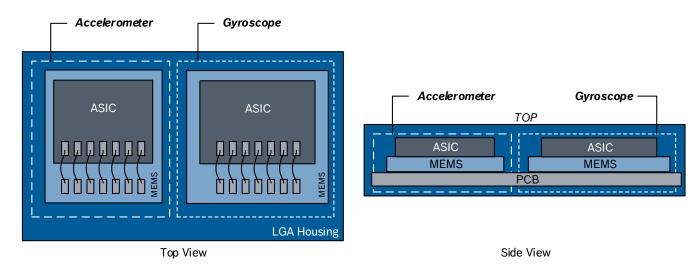

The inertial sensor SMI130 is based upon a combined two-chip stacked concept. The accelerometer and gyroscope sensing parts consist of sensitive micro-mechanical sensing elements (MEMS) mounted side-by-side on the PCB. The read out ASICs are stacked on top of the respective sensing elements. All of these elements are packed in one LGA package.

Figure 1 Schematics of the SMI130 mechanical design (left: top view; right: side view)

## 2.2 Sensor Data

The settings for the accelerometer and gyroscope can be set individually. The detailed description can be found in section 7.1. How to read and evaluate the sensor data is described in section 7.4

For both sensing elements it is recommended to actively set an appropriate, application specific bandwidth. For the accelerometer, the bandwidth can be set between 7.81 Hz and 1000 Hz. For the gyroscope, the bandwidth can be set between 32 Hz and 523 Hz.

Similar to the bandwidth, the measurement range can be selected by a specific register setting. The measurement range for the accelerometer is from  $\pm 2$  g to  $\pm 16$  g. For the gyroscope, the measurement range can be selected from  $\pm 125$  °/s to  $\pm 2000$  °/s.

The data representation of the SMI130 follows two's complement representation. For each axis, the acceleration and gyroscope data is split into a MSB upper part and a LSB lower part. It is recommended to always start with reading the LSB register.

In order to ensure data integrity, a **shadowing procedure** can be enabled. When this is enabled, the content of the MSB register is locked when reading the corresponding LSB register, until the MSB register is read. This means that the MSB register always has to be read in order to remove the data lock. Shadowing can be disabled or enabled for each sensing part separately. For disabled shadowing, the content of both MSB and LSB registers is updated immediately.

Two different streams of acceleration and gyroscope data are available, **unfiltered** and **filtered** data. The unfiltered data is sampled with 2 kHz. The sampling rate (output data rate ODR) of the filtered data depends on the selected filter bandwidth (*BW*). Based on the specific register settings (*data\_high\_bw*), either the filtered or unfiltered data is stored in the registers.

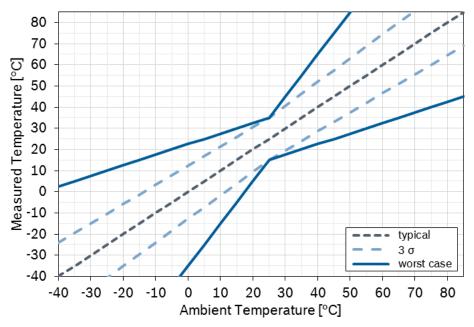

The ASICs for accelerometer and gyroscope have a built-in temperature sensor. The corresponding data can be read from registers ACC 0x08 (*TEMP*) and GYR 0x08 (*TEMP*). The temperature sensor data of the SMI130 has a width of 8 bits, which covers a temperature range of 128 K. The slope is typically 0.5 K/LSB.

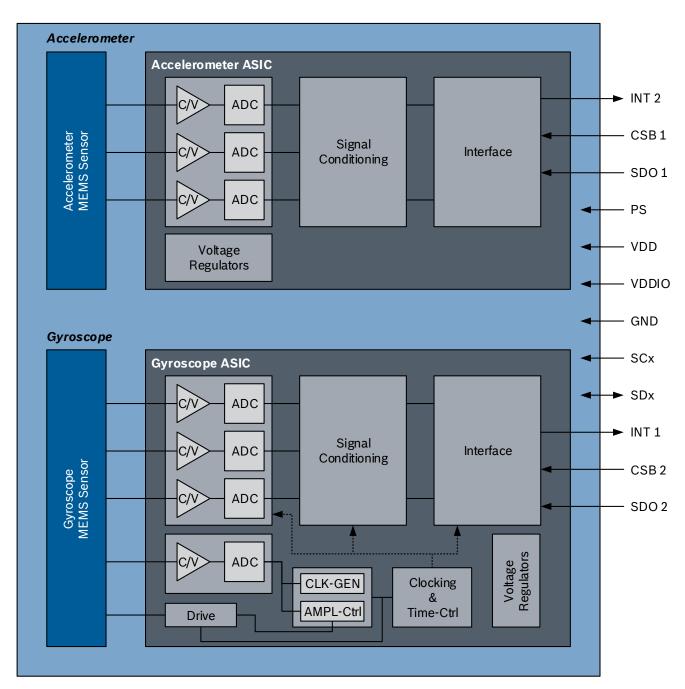

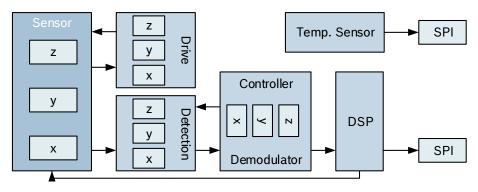

# 2.3 Block Diagram

Figure 2 shows the basic building blocks of the SMI130. As stated in section 2.1, the accelerometer and the gyroscope MEMS elements are each evaluated by their own ASIC. Both sensing elements detect voltage (V) variations, feeding into the analog-digital converter (ADC). The digital signals are further processed and accessible via SPI or TWI.

Figure 2 Simplified block diagram of the SMI130

# 2.4 Signal Path

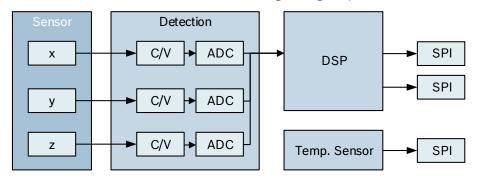

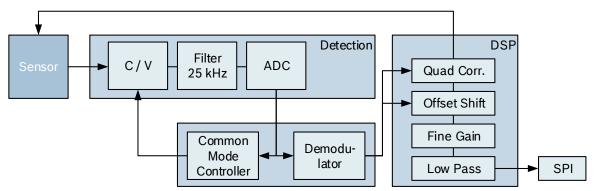

#### 2.4.1 Accelerometer

The accelerometer offers temperature and acceleration data for all three spatial dimensions. For the latter, the differential capacitance change (C) of the corresponding sensing element is detected. These signals correspond to the voltage (V) entering the hybrid algorithmic analog-digital-converter (ADC), translating the formerly analog signals into digital serial bit streams at a rate of 400 kHz. Then, the detected signal is translated into a data word of max. 16 bits and enters the digital signal processor (DSP).

Figure 3 Simplified signal path of the accelerometer

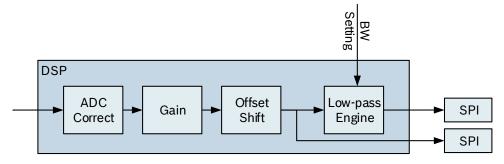

Within the DSP (see Figure 4), the data is corrected for the analog-digital conversion, the gain and offset corrected. A low-pass filter provides an adjustable data bandwidth. Here, the sampling rate is directly connected with the selected bandwidth.

The low-pass filter can be bypassed so that unfiltered data is accessible.

Figure 4 Simplified DSP element (accelerometer)

#### 2.4.2 Gyroscope

The signal path of the gyroscope is sketched in Figure 5. For proper data acquisition, five blocks are necessary for each rate axis, i.e., the drive, the (MEMS) sensor, the detection, the controller & demodulator, and the digital signal processor (DSP). In addition, a temperature signal is provided by the temperature sensor.

The drive is a closed-loop system that actively moves each sensor element at ~25 kHz.

Figure 5 Simplified signal path of the gyroscope

Data acquisition is independent from the drive and the temperature sensor. A more detailed sketch of the signal path of one axis is given in Figure 6.

The block 'Detection' corresponds to the analog part of the SMI130. The differential capacitance change (C) of each sensing element corresponds to the rate data of the respective sensing axis. The latter corresponds to the voltage (V) entering the 25 kHz filter which is equal to the drive frequency. The 1-bit  $\Sigma/\Delta$ -converter (ADC) translates the signal into a digital serial bit stream at a rate of 400 kHz.

This bit stream is fed into both the common mode controller and the demodulator. The first back-couples to 'C/V' in order to negate mass deviation of the sensor element. The latter demodulates the 25 kHz data signal which then enters the DSP.

In the DSP, the signal is both fed into the quadrature correction and the offset is shifted. Afterwards, it passes a fine gain block and low pass filter before being accessible via e.g. SPI.

The block 'Quad. Corr.' back-couples onto distinctive pads on the sensing element to compensate for possible deviations from the oscillation axis.

Figure 6 Path of the detection signal for one axis (gyroscope)

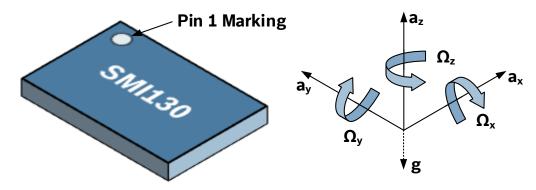

# 2.5 Orientation of the Sensing Axes

If the sensor is accelerated and/or rotated in the indicated directions, the corresponding channels of the device will deliver a positive acceleration and/or yaw rate signal (dynamic acceleration). If the sensor is at rest without any rotation, and the force of gravity is acting contrary to the indicated directions, the output of the corresponding acceleration channel will be positive and the output of the corresponding gyroscope channel will be 'zero' (static acceleration).

Figure 7 Sensing axis orientation

#### **Example:**

According to Figure 7, if the sensor is at rest, or at uniform motion in a gravity field, the output signals are:

$\pm$ 0 for the ACC x-channel  $\pm$ 0 for the GYR  $\Omega$ x-channel  $\pm$ 0 for the GYR  $\Omega$ y-channel  $\pm$ 1 g for the ACC z-channel  $\pm$ 0 for the GYR  $\Omega$ z-channel

The table below lists all corresponding output signals of x, y, and z, and  $\Omega_x$ ,  $\Omega_y$ , and  $\Omega_z$ , while the sensor is at rest, or at uniform motion in a gravity field. This assumes a  $\pm 2$  g accelerometer range setting and a top down gravity vector as shown above.

| Sensor<br>Orientation    | SM1130    | SMI130    | SMI130    | 0ETIWS  Earth | Earth     | Earth     |

|--------------------------|-----------|-----------|-----------|---------------|-----------|-----------|

| Output                   | 0         | +1 g      | 0         | -1 g          | 0         | 0         |

| Signal x                 | 0         | +1024 LSB | 0         | -1024 LSB     | 0         | 0         |

| Output                   | -1 g      | 0         | +1 g      | 0             | 0         | 0         |

| Signal y                 | -1024 LSB |           | +1024 LSB | 0             | 0         | 0         |

| Output                   | 0         | 0         | 0         | 0             | +1 g      | -1 g      |

| Signal z                 | 0         | 0         | 0         | 0             | +1024 LSB | -1024 LSB |

| Output Signal $\Omega_x$ | 0         | 0         | 0         | 0             | 0         | 0         |

|                          | 0         | 0         | 0         | 0             | 0         | 0         |

| Output Signal $\Omega_Y$ | 0         | 0         | 0         | 0             | 0         | 0         |

|                          | 0         | 0         | 0         | 0             | 0         | 0         |

| Output Signal $\Omega_z$ | 0         | 0         | 0         | 0             | 0         | 0         |

|                          | 0         | 0         | 0         | 0             | 0         | 0         |

# 3 Hardware Interface Description and Packaging

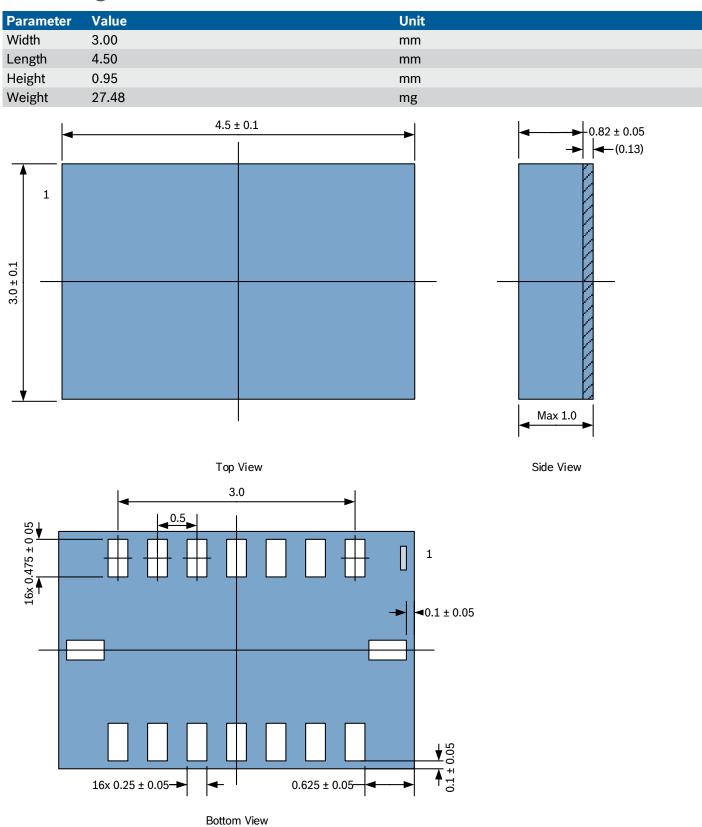

# 3.1 Package Parameters

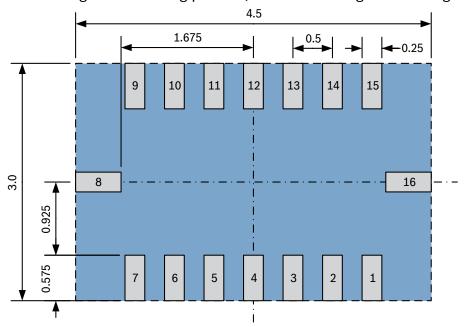

Figure 8 SMI130 package outline drawing

The dimensions are given in mm. Note: Unless otherwise specified, the tolerance is  $\pm$  0.05 mm.

The sensor housing is a standard LGA package.

# 3.2 Transport Package

## 3.2.1 Tape on Reel Specification

The SMI130 is shipped in a standard cardboard box.

The box dimensions for one reel are  $L \times W \times H = 35 \text{ cm} \times 35 \text{ cm} \times 6 \text{ cm}$ .

SMI130 quantity: 5000 pcs per reel. Please handle with care.

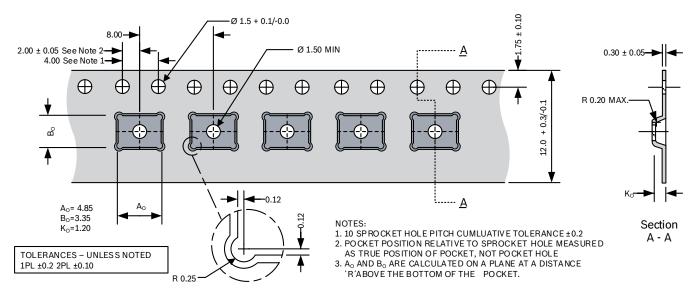

## 3.2.2 Tape Dimensions

Figure 9 Tape dimensions in mm

#### 3.2.3 Reel Dimensions

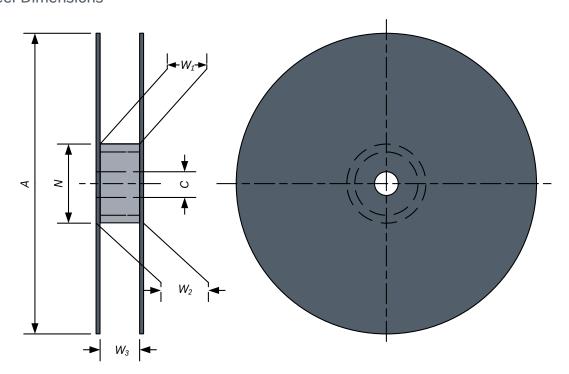

Figure 10 Reel dimensions

| Parameter            | Meaning                      | Dimensions [mm] |

|----------------------|------------------------------|-----------------|

| W (not depicted)     | tape width                   | 12              |

| Α                    | reel diameter                | 330             |

| N                    | hub diameter                 | 100             |

| $W_1$                | inner width of reel          | 12.4 +2         |

| $W_2$                | total width of reel          | 18.4            |

| W <sub>3</sub> , min | inner width of reel, minimum | 11.9            |

| W <sub>3</sub> , max | inner width of reel, maximum | 15.4            |

Figure 11 Details on hub hole dimension C in mm

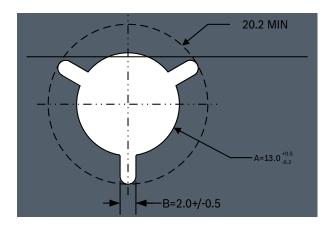

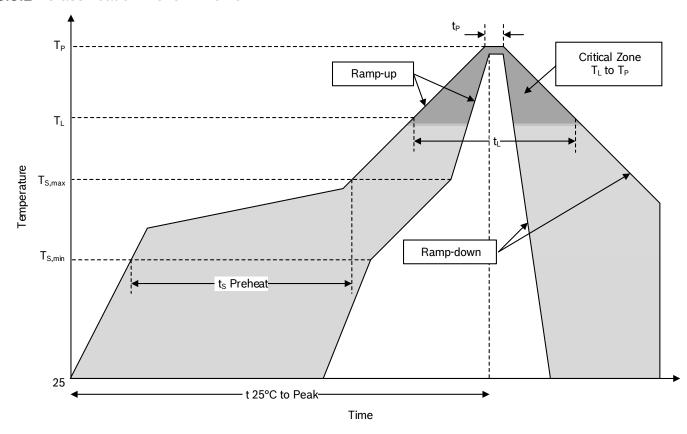

## 3.2.4 Orientation within the Reel

Figure 12 Orientation of the SMI130 devices relative to the tape

# 3.3 Labeling of the Product

| Labeling     | Name             | Symbol | Remark                                                             |

|--------------|------------------|--------|--------------------------------------------------------------------|

|              | Product number   | XXX    | 3 numeric digits, fixed to identify product type                   |

| • XXX        | Subcon ID        | Α      | 1 alphanumeric digit, variable to identify sub-con                 |

| AYYWW<br>CCC | Date code        | YYWW   | 4 numeric digits, fixed to identify YY: "year", WW: "working week" |

|              | Counter ID       | CCC    | 3 numeric digits, variable to generate trace-code                  |

|              | Pin 1 identifier | •      |                                                                    |

# 3.4 Pinning

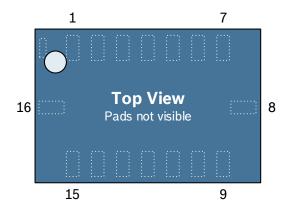

Figure 13 Pin-out top (left) and bottom (right) view

| Pin | Name  | I/O Type    | Description                                  | Connect to<br>- SPI - | Connect to<br>- TWI - |

|-----|-------|-------------|----------------------------------------------|-----------------------|-----------------------|

| 1   | INT2  | Digital out | Interrupt pin (ACC)                          | INT2 / DNC            | INT2 / DNC            |

| 2   | NC    |             |                                              | GND                   | GND                   |

| 3   | VDD   | Supply      | Power supply analog & digital domain         | VDD                   | VDD                   |

| 4   | GNDA  | Ground      | Ground for analog domain                     | GND                   | GND                   |

| 5   | CSB2  | Digital in  | SPI chip select GYR                          | CSB2                  | DNC (float)           |

| 6   | GNDIO | Ground      | Ground for I/O                               | GND                   | GND                   |

| 7   | PS    | Digital in  | Protocol select                              | GND                   | VDDIO                 |

| 8   | SCx   | Digital in  | Serial clock                                 | SCK                   | SCL                   |

| 9   | SDx   | Digital I/O | SPI: serial data in; TWI: serial data in/out | SDI                   | SDA                   |

| 10  | SDO2  | Digital out | SPI: serial data out GYR                     | SDO2                  | SDO2                  |

| 11  | VDDIO | Supply      | Digital I/O supply voltage                   | VDDIO                 | VDDIO                 |

| 12  | INT1  | Digital out | Interrupt pin (GYR)                          | INT1 / DNC            | INT1 / DNC            |

| 13  | NF    |             |                                              | DNC                   | DNC                   |

| 14  | CSB1  | Digital in  | SPI chip select ACC                          | CSB1                  | DNC (float)           |

| 15  | SDO1  | Digital out | SPI: serial data out ACC                     | SDO1                  | SDO1                  |

| 16  | NF    |             |                                              | DNC                   | DNC                   |

DNC: Do not connect INTx: If not needed, DNC

# 3.5 Soldering

The moisture sensitivity level (MSL) of BOSCH SMI130 corresponds to JEDEC Level 1, see also

- ► IPC/JEDEC J-STD-020C "Joint Industry Standard: Moisture/Reflow Sensitivity Classification for non-hermetic Solid State Surface Mount Devices"

- ► IPC/JEDEC J-STD-033A "Joint Industry Standard: Handling, Packing, Shipping and Use of Moisture/Reflow Sensitivity Surface Mount Devices"

The sensor IC fulfills the lead-free soldering requirements of the above-mentioned IPC/JEDEC standard, i.e. reflow soldering with a peak temperature up to 260°C.

Repair and manual soldering of the sensor is not permitted.

## 3.5.1 Reflow Soldering Recommendation for Sensors in LGA Package

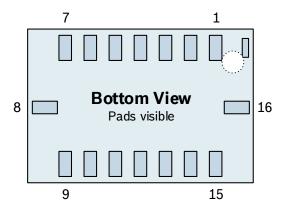

Please make sure that the edges of the LGA substrate of the sensor are free of solder material. Avoid solder material forming a high meniscus covering the edge of the LGA substrate (see Figure 14).

Figure 14 Reflow soldering recommendation

## 3.5.2 Classification Reflow Profile

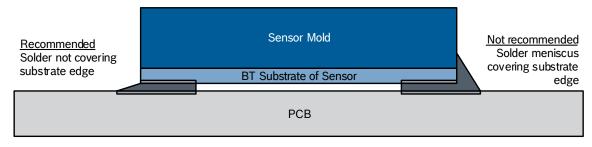

Figure 15 Soldering profile

| Profile Feature                                                                                                                  | Pb-Free Assembly               |

|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Average ramp-up rate (T <sub>Smax</sub> to T <sub>p</sub> )                                                                      | 3 °C/s max.                    |

| Preheat Temperature min (T <sub>Smin</sub> ) Temperature max (T <sub>Smax</sub> ) Time (t <sub>Smin</sub> to t <sub>Smax</sub> ) | 150 °C<br>200 °C<br>60 – 180 s |

| Time maintained above: Temperature $(T_L)$ Time $(t_L)$                                                                          | 217 °C<br>60 s – 150 s         |

| Peak classification temperature (T <sub>P</sub> )                                                                                | 260 °C                         |

| Time within 5 °C of actual peak temperature (tp)                                                                                 | 20 s – 40 s                    |

| Ramp-down rate                                                                                                                   | 6 °C/s max.                    |

| Time 25 °C to peak temperature                                                                                                   | 8 min max.                     |

Note: All temperatures refer to the topside of package, measured on the package body surface.

## 3.5.3 Multiple Reflow Soldering Cycles

The product can withstand up to 3 reflow soldering cycles in total. This could be a situation where a PCB is mounted with devices from both sides (i.e. 2 reflow cycles necessary) or where, in the next step, an additional re-work cycle could be required (1 reflow).

# 3.6 Mounting Recommendations

In general, MEMS sensors are high-precision measurement devices that consist of electronic as well as mechanical structures. BOSCH sensor devices are designed for precision, efficiency, and mechanical robustness.

However, in order to achieve best possible results of your design, the following recommendations should be taken into consideration when mounting the sensor on a printed circuit board (PCB).

In order to evaluate and optimize the considered placement position of the sensor on the PCB, it is recommended to use additional tools during the design in phase. For example:

- Regarding thermal aspects: infrared camera

- ▶ Regarding mechanical stress: warpage measurements and/or FEM-simulations

- Regarding shock robustness: drop test of the devices after soldering on the target application PCB

#### **Recommendations in Detail**

- ▶ It is recommended to keep a reasonable distance between the sensor mounting location on the PCB and the critical points described in the following examples. The exact value for a "reasonable distance" depends on many customer specific variables and therefore must be determined case by case.

- lt is generally recommended to minimize the PCB thickness (recommended: ≤0.8 mm) since a thin PCB shows less intrinsic stress.

- lt is not recommended to place the sensor directly under or next to push-button contacts as this can result in mechanical stress.

- lt is not recommended to place the sensor in the direct vicinity of extremely high temperature spots (e.g. a μController or a graphic chip) as this can result in the PCB heating up and consequently the sensor as well.

- ▶ It is not recommended to place the sensor in the direct vicinity of a mechanical stress maximum (e.g. in the center of a diagonal crossover). Mechanical stress can lead to bending of the PCB and the sensor.

- ▶ Do not mount the sensor too closely to a PCB anchor point, where the PCB is attached to a shelf (or similar), as this could also result in mechanical stress. To reduce potential mechanical stress, minimize redundant anchor points and/or loosen respective screws.

- Avoid mounting the sensor in areas where resonant amplitudes (vibrations) of the PCB are likely or expected.

- Please avoid partial coverage of the sensor by any kind of (epoxy) resin, as this can result in mechanical stress.

- Avoid mounting (and operation) of the sensor in the vicinity of strong magnetic, strong electric, and/or strong infrared radiation fields (IR).

- Avoid electrostatic charging of the sensor and of the device in which the sensor is mounted.

If the above mentioned recommendations cannot be realized appropriately, a specific in-line offsetcalibration after placement of the device onto your PCB may help to minimize the potentially remaining effects.

The SMI130 is designed to sense angular rates and accelerations with high accuracy even at low amplitudes and contains highly sensitive structures inside the sensor element. The MEMS sensor can

tolerate mechanical shocks up to several thousand g's. However, these limits might be exceeded in conditions with extreme shock loads such as a hammer blow on or next to the sensor, dropping the sensor onto hard surfaces, etc.

It is strongly recommended to avoid any g forces beyond the limits specified in the data sheet during transport, handling, and mounting of the sensors. A defined and qualified installation process on customer side is required.

This device has built-in protections against high electrostatic discharges or electric fields (2 kV HBM). However, anti-static precautions should be taken as with any other CMOS component.

Unless otherwise specified, proper operation can only occur when all terminal voltages are kept within the supply voltage range. Unused inputs must always be connected to a defined logic voltage level.

## 3.7 Recommendations for PCB Layout

For the design of the landing patterns, the dimensioning shown in Figure 16 is recommended.

Figure 16 SMI130 footprint. Dimensions given in mm.

# 4 **Environment Specification**

# 4.1 Absolut Maximum Ratings

Any values outside of the given ratings may seriously damage the device. The sensor must be discarded after exceeding these limits.

| Parameter                | Condition                 | Min  | Max        | Unit |

|--------------------------|---------------------------|------|------------|------|

| Voltage at supply pin    | VDD pin                   | -0.3 | 4.27       | V    |

| Voltage at supply pin    | VDDIO pin                 | -0.3 | 3.6        | V    |

| Voltage at any logic pin | non-supply pin            | -0.3 | VDDIO +0.3 | V    |

| Mechanical shock         | free fall onto hard surfa | ces  | 1.2        | m    |

| Mechanical shock         | duration <1 ms            |      | 2000       | g    |

| ESD                      | HBM, any pin              |      | 2          | kV   |

| ESD                      | CDM                       |      | 500        | V    |

| ESD                      | MM                        |      | 200        | V    |

# 4.2 Operating Conditions

| Parameter                                                | Symbol                | Min | Typical | Max | Unit |

|----------------------------------------------------------|-----------------------|-----|---------|-----|------|

| Operating temperature                                    | T                     | -40 | -       | 85  | °C   |

| Extended operating temperature (details see section 5.2) | T <sub>extended</sub> | -40 | -       | 105 | °C   |

## 4.3 Lifetime Conditions

| Parameter | Condition                                  |

|-----------|--------------------------------------------|

| Lifetime  | according to AEC-Q100 grade 3 requirements |

# 4.4 Environmental Safety

#### **RoHS**

The SMI130 sensor meets the requirements of the *Restriction of Hazardous Substances* (RoHS) directive 2002/95/EC of the European Parliament and of the Council of 27 January 2003 (on the *Restriction of the use of certain Hazardous Substances in electrical and electronic equipment*).

The sensor module is recyclable according to the norm WEEE - 2012/19/EU.

#### Halogen content

The SMI130 is halogen-free. For more details on the analysis results, please contact your Bosch representative.

# 5 Parameter Specification

## **5.1** Power Supply

The SMI130 has two distinct power supply pins:

- VDD is the main power supply for the internal blocks.

- ▶ VDDIO is a separate power supply pin mainly used for the supply of the interface.

| Parameter                       | Symbol   | Condition               | Min       | Typical | Max        | Unit |

|---------------------------------|----------|-------------------------|-----------|---------|------------|------|

| Supply voltage internal domains | VDD      |                         | 2.4       | 3.3     | 3.6        | V    |

| Supply voltage I/O domain       | VDDIO    |                         | 1.2       | 3.3     | 3.6        | V    |

| Voltage input low level         | $V_{IL}$ |                         |           |         | 0.3 VDDIO  | -    |

| Voltage input high level        | $V_{IH}$ |                         | 0.7 VDDIO |         |            | -    |

| Voltage output low level        | $V_{OL}$ | $I_{OL} = 3 \text{ mA}$ |           |         | 0.23 VDDIO | -    |

| Voltage output high level       | Vон      | I <sub>OH</sub> = 3 mA  | 0.8 VDDIO |         |            | -    |

#### Switching sequence of power supply VDD and VDDIO

If VDD and VDDIO are not powered on simultaneously (via directly connecting both pins), VDD has to be powered on first and set to a specified level. Thereafter, VDDIO can be powered on.

Not following this sequence might result in voltage levels of both pins which are not limited. This also applies if both are operated within their corresponding operating range.

In the case that the VDDIO supply is off, all interface pins (CSB, SDI, SCK, PS) must be kept close to GNDIO potential.

The SMI130 provides a **power-on reset (POR)** generator. It resets the logic part and the register values after powering on VDD and VDDIO.

After POR, all settings are reset to the default values.

In the case that VDD < 1.8 V or VDDIO < 1V for longer than 1 ms, a safe POR (see below) is required. Else, the device may end up in an undefined state.

#### Safe POR options:

- A. Ramp down VDD to a level  $\leq 0.35$  V monotonically and keep it below this level for  $\geq 2$  µs. There is no constraint on the VDDIO level. Ramp up VDD and VDDIO to operating range.

- **B.** Ramp down VDDIO to a level  $\leq$  0.35 V monotonically and keep it below for  $\geq$  2  $\mu$ s while keeping VDD  $\geq$  1.8 V. Ramp up VDD and VDDIO to operating range.

#### **SPI protocol requirements:**

The PS pin must be directly connected to GNDIO.

#### 5.2 Technical data

The data in the following section, unless otherwise noted, apply for the valid operation conditions given in section 4.2 and 5.1. All following figures include voltage, temperature, and lifetime effects if not noted otherwise. All figures, except sensitivity, are only valid without an external stimulus applied. All figures, except for the noise itself, exclude noise effects.

The sensor was validated and qualified in the temperature range from -40 °C to 85 °C according to Bosch standard release process. The specified values within this temperature range are given in the TPD section 5.2.1.1 and 5.2.2.1.

For elevated temperatures between 85 °C and 105 °C a characterization over the full range [-40 °C; 105 °C] was performed without consideration of lifetime effects. However the sensor will not be destroyed through

thermal event in this temperature range. Within this temperature range, the typical values are given in section 5.2.1.2 and 5.2.2.2. It is the customers' responsibility to assess the impact on system level.

#### 5.2.1 Accelerometer

The SMI130 allows for selection of range and bandwidth:

| Parameter                            | Symbol      | Comment    | Range (typical)       | Unit           | Resolution (typ.)         | Unit  |

|--------------------------------------|-------------|------------|-----------------------|----------------|---------------------------|-------|

| Measurement<br>Range  <br>Resolution | <b>g</b> FS | selectable | ±2<br>±4<br>±8<br>±16 | g              | 1024<br>512<br>256<br>128 | LSB/g |

| Bandwidth                            | BW          | selectable | 8, 16, 31, 63, 125, 2 | 250, 500, 1000 |                           | Hz    |

## 5.2.1.1 Values in the Temperature Range -40 °C to 85 °C

Unless otherwise specified, the sensor is configured with the default settings. The measurement range is set to 2 g and the bandwidth is set to 1000 Hz.

| Parameter                                                    | Symbol     | Condition / Comment                                           | Typic     | al  | Max | Unit     |

|--------------------------------------------------------------|------------|---------------------------------------------------------------|-----------|-----|-----|----------|

| Supply current                                               | $I_{DD}$   | w/o SPI communication                                         | 0.15      |     |     | mA       |

| Start-up time                                                | $t_{s,up}$ | POR                                                           |           |     | 0.2 | S        |

| Sensitivity tolerance                                        |            | including temperature and lifetime effects                    |           |     | ±5  | %        |

| Sensitivity tolerance                                        |            | T = 25 °C,<br>over lifetime                                   |           |     | ±4  | %        |

| Temperature Coefficient<br>Sensitivity                       | TCS        | nominal VDD supply,<br>temperature range -40 °C to 85 °C      | ±0.02     | 5   |     | % / K    |

| Zero-g offset*                                               |            | Including lifetime and temperature                            | X         | ±35 |     | mg       |

| reset to zero at end of                                      |            | effects                                                       | у         | ±40 |     |          |

| customer line -                                              |            |                                                               | Z         | ±90 |     |          |

| Zero-g offset                                                |            | T = 25 °C,<br>over lifetime                                   | ±70       |     |     | mg       |

| Temperature Coefficient Offset (zero-g)                      | TCO        | nominal VDD supply,<br>temperature range -40 °C to 85 °C      | ±1        |     |     | mg/K     |

| Nonlinearity<br>BW: 62.5 Hz, range: ± 2g                     | NLIN       | best fit straight line,<br>no life-time                       | ±25       |     |     | mg       |

| Noise rms                                                    |            | T = 25 °C,<br>nominal VDD supply,<br>no lifetime              | 6         |     |     | mg       |

| Temperature sensor slope                                     |            |                                                               | 0.5       |     |     | K/LSB    |

| Temperature sensor offset                                    |            | T = 25 °C                                                     | ±5        |     |     | K        |

| Cross axis sensitivity                                       |            | including temperature and lifetime                            | ±3        |     |     | %        |

| Noise rms Temperature sensor slope Temperature sensor offset |            | T = 25 °C,<br>nominal VDD supply,<br>no lifetime<br>T = 25 °C | 0.5<br>±5 |     |     | K/L<br>K |

<sup>\*</sup> Assumption: ACC is offset corrected at end of customer production line on system level

## 5.2.1.2 Values in the Temperature Range 85 °C to 105 °C

| Parameter                               | Symbol            | Condition / Comment                                                         | 7        | ГурісаІ | Unit  |

|-----------------------------------------|-------------------|-----------------------------------------------------------------------------|----------|---------|-------|

| Supply current                          | $I_{DD}$          | w/o SPI communication                                                       | C        | ).2     | mA    |

| Start-up time                           | t <sub>s,up</sub> | POR                                                                         | (        | ).2     | S     |

| Sensitivity tolerance                   |                   | over full temperature range,<br>w/o lifetime effects                        | ±        | ±1.4    | %     |

| Temperature Coefficient<br>Sensitivity  | TCS               | nominal VDD supply,<br>over full temperature range,<br>w/o lifetime effects | <u> </u> | ±0.025  | % / K |

| Zero-g offset*                          |                   | over full temperature range,                                                | ×        | t ±35   | mg    |

| - reset to zero at end of               |                   | w/o lifetime effects                                                        | У        | / ±65   |       |

| customer line                           |                   |                                                                             | Z        | ±90     |       |

| Temperature Coefficient Offset (zero-g) | TCO               | nominal VDD supply,<br>over full temperature range,<br>w/o lifetime effects | 4        | ±1      | mg/K  |

| Nonlinearity                            | NLIN              | over full temperature range,<br>w/o lifetime effects                        | ±        | ±25     | mg    |

| Noise rms                               |                   | nominal VDD supply,<br>over full temperature range<br>w/o lifetime effects  | 3        | 3       | mg    |

<sup>\*</sup> Assumption: ACC is offset corrected at end of customer production line on system level

## 5.2.2 Gyroscope

The SMI130 allows for selection of range and bandwidth:

| Parameter                            | Symbol          | Comment    | Range (typical)                        | Unit                   | Resolution (typ.)                           | Unit    |

|--------------------------------------|-----------------|------------|----------------------------------------|------------------------|---------------------------------------------|---------|

| Measurement<br>Range  <br>Resolution | R <sub>FS</sub> | selectable | ±125<br>±250<br>±500<br>±1000<br>±2000 | °/s                    | 262.14<br>131.07<br>65.54<br>32.77<br>16.38 | LSB/°/s |

| Bandwidth                            | BW              | selectable | 12, 23, 32, 47, 64,                    | 116, 230, 523 (unfilte | red)                                        | Hz      |

## 5.2.2.1 Values in the Temperature Range -40 °C to 85 °C

Unless otherwise specified, the sensor is configured with default settings. The measurement range is set to 2000 °/s and the bandwidth is set to 47 Hz.

| Parameter                                                   | Symbol            | Condition / Comment                                      | Typical | Max  | Unit    |

|-------------------------------------------------------------|-------------------|----------------------------------------------------------|---------|------|---------|

| Supply current                                              | $I_{DD}$          | w/o SPI communication                                    |         | 6.5  | mA      |

| Start-up time                                               | t <sub>s,up</sub> | POR                                                      |         | 0.2  | S       |

| Sensitivity tolerance                                       |                   | including temperature and lifetime effects               |         | ±5.5 | %       |

| Sensitivity tolerance                                       |                   | T = 25 °C,<br>over lifetime                              | ±1      |      | %       |

| Temperature Coefficient<br>Sensitivity                      | TCS               | nominal VDD supply,<br>temperature range -40 °C to 85 °C | ±0.03   |      | % / K   |

| Zero-rate offset* - reset to zero at end of customer line - |                   | Including lifetime and temperature effects               | ±0.5    |      | °/s     |

| Zero-rate offset                                            |                   | T = 25 °C,<br>over lifetime                              |         | ±1   | °/s     |

| Temperature Coefficient Offset (zero-g)                     | TCO               | nominal VDD supply,<br>temperature range -40 °C to 85 °C | ±0.015  |      | °/s / K |

| Nonlinearity<br>BW: 23 Hz; range: ±125 °/s                  | NLIN              | best fit straight line,<br>no life-time                  |         | ±1   | °/s     |

| Noise rms                                                   |                   | T = 25 °C,<br>nominal VDD supply,<br>no lifetime         | 0.1     |      | °/s     |

| Temperature sensor measurement range                        |                   |                                                          |         | 85   | °C      |

| Temperature sensor slope                                    |                   |                                                          | 0.5     |      | K/LSB   |

| Temperature sensor offset                                   |                   | T = 25 °C                                                | ±5      |      | K       |

| Cross axis sensitivity                                      |                   | including temperature and lifetime effects               | ±2      |      | %       |

|                                                             |                   |                                                          |         |      |         |

<sup>\*</sup> Assumption: GYR is offset corrected at end of customer production line on system level

## 5.2.2.2 Values in the Temperature Range 85 °C to 105 °C

| Parameter                                                 | Symbol     | Condition / Comment                                                         | Typical | Unit    |

|-----------------------------------------------------------|------------|-----------------------------------------------------------------------------|---------|---------|

| Supply current                                            | $I_{DD}$   | w/o SPI communication                                                       | 5.4     | mA      |

| Start-up time                                             | $t_{s,up}$ | POR                                                                         | 0.2     | S       |

| Sensitivity tolerance                                     |            | over full temperature range,<br>w/o lifetime effects                        | ±1.5    | %       |

| Temperature Coefficient<br>Sensitivity                    | TCS        | nominal VDD supply,<br>over full temperature range,<br>w/o lifetime effects | ±0.03   | % / K   |

| Zero-rate offset* - reset to zero at end of customer line |            | over full temperature range,<br>w/o lifetime effects                        | ±0.5    | °/s     |

|                                                           | TCO        | nominal VDD supply,<br>over full temperature range,<br>w/o lifetime effects | ±0.015  | °/s / K |

| Nonlinearity                                              | NLIN       | over full temperature range,<br>w/o lifetime effects                        | 0.1     | °/s     |

| Noise rms                                                 |            | nominal VDD supply,<br>over temperature range,<br>w/o lifetime effects      | 0.16    | °/s     |

<sup>\*</sup> Assumption: GYR is offset corrected at end of customer production line on system level

# **6 Software Interface Description**

# 6.1 Serial Peripheral Interface (SPI)

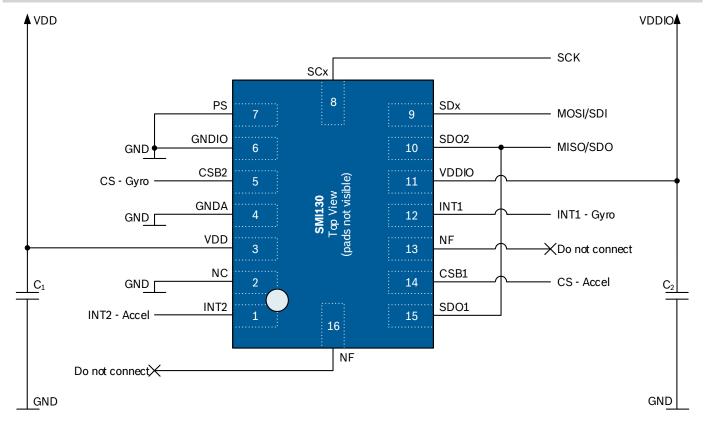

#### 6.1.1 SPI Connection

For communication, the SMI130 supports the SPI 4-wire protocol as a slave with a host device. The connection diagram is shown in Figure 17. The mapping for the interface of both accelerometer and gyroscope is given in the table below:

| Pin | Name | Description              |  |

|-----|------|--------------------------|--|

| 15  | SDO1 | ACC data output          |  |

| 10  | SDO2 | GYR data output          |  |

| 9   | SDx  | SDI serial data in       |  |

| 14  | CSB1 | ACC chip select (enable) |  |

| 5   | CSB2 | GYR chip select (enable) |  |

| 8   | SCx  | SCK serial clock         |  |

Figure 17 SPI connection diagram

C<sub>1</sub>, C<sub>2</sub>: 100 nF

INT1: see registers GYR 0x18, GYR 0x16 INT2: see registers ACC 0x1A, ACC 0x20

#### Note:

For a proper functionality defined voltage levels at SDI, SDO and SCK are required. In case this cannot be guaranteed by the SPI controller, additional pull-up or pull-down resistors are required.

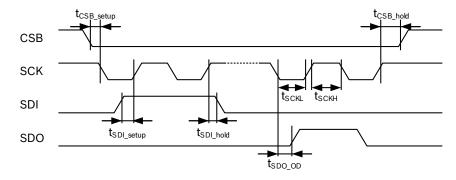

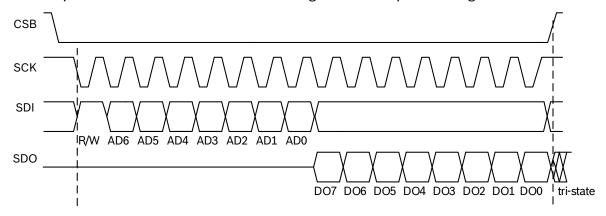

#### 6.1.2 SPI Timing

The SPI timing specification of the SMI130 is given in the following table:

| Parameter                        | Symbol                 | Condition                       | Min | Max | Units |

|----------------------------------|------------------------|---------------------------------|-----|-----|-------|

| Clock frequency                  | f <sub>SPI</sub>       | max. load on SDI or SDO = 25 pF |     | 10  | MHz   |

| SCK low pulse                    | <b>t</b> sckl          |                                 | 20  |     | ns    |

| SCK high pulse                   | <b>t</b> sckH          |                                 | 48  |     | ns    |

| SDI setup time                   | t <sub>SDI_setup</sub> |                                 | 20  |     | ns    |

| SDI hold time                    | tsDI_hold              |                                 | 20  |     | ns    |

| SDO output delay                 | tsdo_od                | load = 25 pF                    |     | 40  | ns    |

|                                  |                        | load = 250 pF, VDDIO = 2.4 V    |     | 40  | ns    |

| CSB setup time                   | tcsB_setup             |                                 | 20  |     | ns    |

| CSB hold time                    | tcsB_hold              |                                 | 40  |     | ns    |

| Idle time between write accesses | tIDLE_wacc_nm          |                                 | 2   |     | μs    |

Figure 18 shows the definition of the SPI timing.

Figure 18 SPI timing diagram

The SPI interface of the SMI130 is compatible with two modes: 00 and 11. The automatic selection between [CPOL = 0 and CPHA = 0] and [CPOL = 1 and CPHA = 1] is controlled based on the value of SCK after a falling edge of CSB (1 or 2). For single byte read as well as write operations, 16 bit protocols are used. The SMI130 also supports multiple-byte read operations.

For standard SPI configuration, CSB (1 or 2 - chip select low active), SCK (serial clock), SDI (serial data input), and SDO (1 or 2 - serial data output) pins are used. The communication starts when CSB (1 or 2) is pulled low by the SPI master and stops when CSB (1 or 2) is pulled high. SCK is also controlled by the SPI master. SDI and SDO (1 or 2) are driven at the falling edge of SCK and should be captured at the rising edge of SCK.

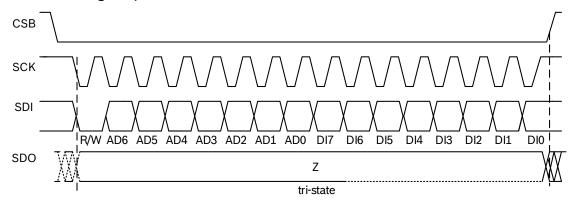

The basic write operation waveform for the 4-wire configuration is depicted in Figure 19. During the full write cycle, SDO remains in high-impedance state.

Figure 19 4-wire basic SPI write sequence (mode 11)

The basic read operation waveform for the 4-wire configuration is depicted in Figure 20.

Figure 20 4-wire basic SPI read sequence (mode 11)

The data bits are used as follows:

Bit <15>: Read/write bit. When 0, the data SDI is written into the chip. When 1, the data SDO from the

chip is read.

Bits <14:8>: Address AD (6:0)

Bits <7:0>: When in write mode, these bits are the data SDI which will be written into the address. When

in read mode, these bits are the data SDO which are read from the address.

Multiple read operations are possible by keeping CSB low and continuing the data transfer. Only the first register address has to be written. Addresses are automatically incremented after each read access as long as CSB stays active low.

The principle of multiple read is shown in Figure 21.

|         |    |   | Co  | nt   | rol  | By  | yte   | )     |   |   |      | D    | ata  | Ву   | te   |      |   |   |      | D    | ata | Ву   | rte  |      |   |   |      | D    | ata  | Ву   | rte  |      |   |         |

|---------|----|---|-----|------|------|-----|-------|-------|---|---|------|------|------|------|------|------|---|---|------|------|-----|------|------|------|---|---|------|------|------|------|------|------|---|---------|

| Start   | R۷ | ٧ | Reg | iste | r ad | dre | ess ( | (02 h | ) | [ | Data | regi | ster | – ad | dres | s 02 | h |   | Data | regi | ter | – ad | dres | s 03 | h |   | Data | regi | ster | – ad | dres | s 04 | h | Stop    |

| CSB = 0 | 1  | 0 | 0   | 0    | 0    | o   | 0     | 1     | 0 | Х | Х    | Х    | Х    | Х    | Х    | Х    | Х | Х | Х    | Х    | Χ   | Х    | Х    | Х    | Х | Х | Х    | Х    | Х    | Х    | Х    | Х    | Х | CSB = 1 |

Figure 21 SPI multiple read

# 6.2 Two-wire Interface (TWI)

With some exceptions, the TWI interface of the SMI130 is compatible to the I<sup>2</sup>C specification UM10204 Rev. 03 (19 June 2007), available at <a href="http://www.nxp.com">http://www.nxp.com</a>.

- ► The SMI130 supports the I<sup>2</sup>C standard and fast mode, but only the 7-bit address mode.

- ► For VDDIO = 1.2 ... 1.8 V the granted voltage output levels are slightly relaxed compared to the specification.

- The internal data hold time (t<sub>HDDAT</sub>) of 300 ns is not met under all operation conditions. The device achieves a minimum value of 120 ns across process corners and temperature.

- The minimum data fall time  $(t_F)$  of 20 ns cannot be met.

- Only single byte write is supported.

- ▶ Detection of a stop condition is not supported. All data transfer protocols are fully operational by means of detecting the start condition only.

- ▶ The device does not support the high-impedance mode while VDDIO is tied to GND.

- ► The device does not perform clock stretching, i.e. clock frequencies may not exceed the one specified in the parameter section and wait times between subsequent write accesses (as specified in section 6.2.2) have to be ensured by the bus master.

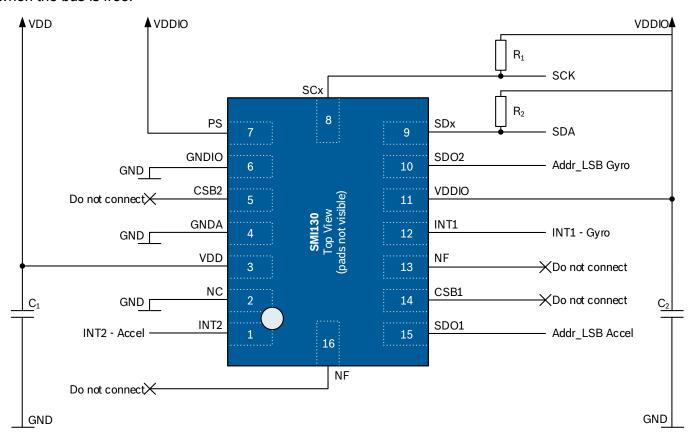

#### 6.2.1 TWI Connection

The TWI interface uses SCL (= SCx pin, serial clock) and SDA (= SDx pin, serial data input and output) signal lines. Both lines are connected to VDDIO externally via pull-up resistors so that they are pulled high when the bus is free.

Figure 22 TWI connection diagram

$C_1$ ,  $C_2$ : 100 nF  $R_1$ ,  $R_2$ : pull-up resistors

INT1: see registers GYR 0x18, GYR 0x16 INT2: see registers ACC 0x1A, ACC 0x20

SDO1 and SDO2 are used to define the TWI address of accelerometer and gyroscope. The default TWI address of the SMI130 accelerometer is 0x18 and the one of the gyroscope is 0x68. It is used if both SDO pins are pulled to GND. The alternative address is selected by pulling the corresponding SDO pin to VDDIO.

|                           | Accelerometer address | Gyroscope address   |

|---------------------------|-----------------------|---------------------|

| SDO1 and SDO2 to GND      | 0x18 (ACC: 0011000)   | 0x68 (GYR: 1101000) |

| SDO1 and/or SDO2 to VDDIO | 0x19 (ACC: 0011001)   | 0x69 (GYR: 1101001) |

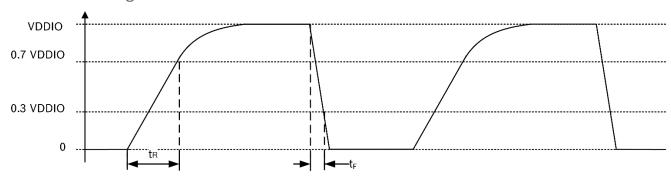

#### 6.2.2 TWI Timing

Figure 23 Definition of the rise and fall time of TWI signals

The TWI timing specification of the SMI130 is given in the table below.

| Parameter                                             | Symbol                  | Min  | Max | Units |

|-------------------------------------------------------|-------------------------|------|-----|-------|

| Clock frequency                                       | f <sub>SCL</sub>        | 0    | 400 | kHz   |

| SCL low period                                        | <b>t</b> LOW            | 1.3  |     | μs    |

| SCL high period                                       | <b>t</b> HIGH           | 0.6  |     |       |

| SDA setup time                                        | <b>t</b> sudat          | 0.1  |     |       |

| SDA hold time                                         | <b>t</b> hddat          | 0.12 |     |       |

| Setup time for a repeated start condition             | <b>t</b> susta          | 0.6  |     |       |

| Hold time for a start condition                       | <b>t</b> hdsta          | 0.6  |     |       |

| Setup time for a stop condition                       | <b>t</b> susto          | 0.6  |     |       |

| Time before a new transmission can start              | <b>t</b> <sub>BUF</sub> | 1.3  |     |       |

| Idle time between write accesses normal mode          | tIDLE wacc nm           | 2    |     |       |

| Fall time                                             | t <sub>F</sub>          | 0    | 300 | ns    |

| Rise time (determined by external pull-up resistance) | <b>t</b> R              | 20   | 300 | ns    |

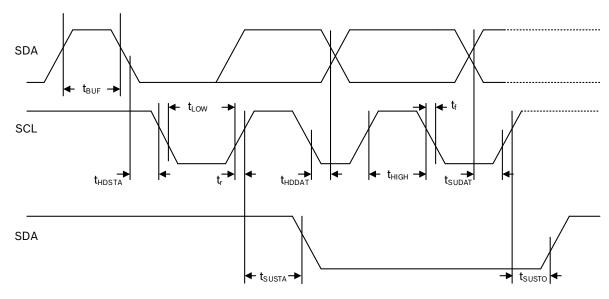

Figure 24 shows the definition of the TWI timing given in the table above.

Figure 24 SMI130 TWI timing specification

The TWI protocol works as follows:

| Mode   | Description                                                                                                                                                                                                                                                                                                                                   |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START: | Data transmission on the bus begins with a high to low transition on the SDA line while SCL is held high (start condition (S) indicated by the TWI bus master). Once the start signal is transferred by the master, the bus is considered busy.                                                                                               |

| STOP:  | Each data transfer should be terminated by a stop signal (P) generated by the master. The stop condition is a low to high transition on the SDA line while SCL is held high.                                                                                                                                                                  |

| ACK:   | Each byte of data transferred must be acknowledged. It is indicated by an acknowledge bit sent by the receiver. The transmitter must release the SDA line (no pull down) during the acknowledge pulse while the receiver must then pull the SDA line low so that it remains stable low during the high period of the acknowledge clock cycle. |

In the following diagrams these abbreviations are used:

| S     | Start                     | Р    | Stop                  |

|-------|---------------------------|------|-----------------------|

| ACKS  | Acknowledge by slave      | ACKM | Acknowledge by master |

| NACKM | Not acknowledge by master | RW   | Read / Write          |

A start (S) immediately followed by a stop (P) (without SCL toggling from VDDIO to GND) is not supported and not recognized by the SMI130.

**TWI write access** can be used to write a data byte in one sequence.

The sequence begins with a start condition generated by the master, followed by 7 bits of the slave address and a write bit (RW = 0). The slave sends an acknowledge bit (ACK = 0) and releases the bus. Then the master sends the one-byte register address. The slave again acknowledges the transmission and waits for the 8 bits of data, which shall be written to the specified register address. After the slave acknowledges the data byte, the master generates a stop signal and terminates the writing protocol. Figure 25 shows an example of a TWI write access to the accelerometer.

| _ |       |   |   |      |       |      |   |   |    |      | Control Byte            |   |   |      |   |   |   |      |        | Data | Byte |   |      |      |   |   |   |  |   |

|---|-------|---|---|------|-------|------|---|---|----|------|-------------------------|---|---|------|---|---|---|------|--------|------|------|---|------|------|---|---|---|--|---|

|   | Start |   |   | Slav | e Ado | ress |   |   | RW | ACKS | Register Address (0x10) |   |   | ACKS |   |   |   | Data | (0x09) | )    |      |   | ACKS | Stop |   |   |   |  |   |

| Γ | S     | 0 | 0 | 1    | 1     | 0    | 0 | 0 | 0  |      | 0                       | 0 | 0 | 1    | 0 | 0 | 0 | 0    |        | Х    | Х    | Х | Х    | Х    | Х | Х | Х |  | Р |

Figure 25 Example of a TWI write access to the accelerometer

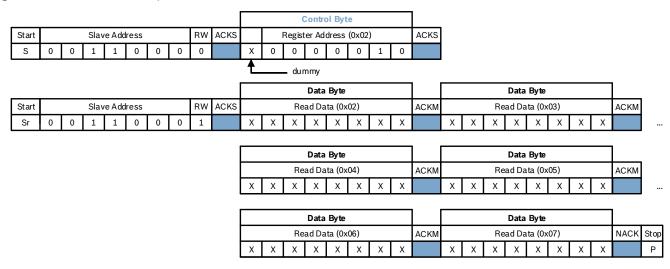

**TWI read access** can be used to read one or multiple data bytes in one sequence.

A read sequence consists of a one-byte TWI write phase followed by the TWI read phase. Both parts of the transmission must be separated by a repeated start condition (Sr). The TWI write phase addresses the slave and sends the register address to be read. After the slave acknowledges the transmission, the master again generates a start condition and sends the slave address together with a read bit (RW = 1). Then the master releases the bus and waits for the data bytes to be read out from the slave. After each data byte, the master has to generate an acknowledge bit (ACK = 0) to enable further data transfer. A NACKM (ACK = 1) from the master stops the data being transferred from the slave. The slave releases the bus so that the master can generate a stop condition and terminate the transmission.

The register address is automatically incremented. Hence, more than one byte can be sequentially read out. Once a new data read transmission starts, the start address will be set to the register address specified in the latest TWI write command. By default, the start address is set as 0x00. In this way, repetitive multibyte reads from the same starting address are possible.

In order to prevent the TWI slave from locking the TWI bus, a watchdog timer (WDT) is implemented. The WDT observes internal TWI signals and resets the TWI interface if the bus is locked up. The activity and timer period of the WDT can be configured via bits 2 (*i2c\_wdt\_en*) and 1 (*i2c\_wdt\_sel*) in registers ACC 0x34 (*BGW\_SPI3\_WDT*) and GYR 0x34 (*BGW\_SPI3\_WDT*).

- ▶ Writing 1 (0) to *i2c\_wdt\_en* activates (de-activates) the WDT.

- ▶ Writing 0 (1) to *i2c\_wdt\_se* sets a timer period of 1 ms (50 ms).

Figure 26 shows an example of a TWI read access to the accelerometer.

Figure 26 Example of a TWI read access to the accelerometer

#### **Note (Gyroscope Soft Reset):**

The SMI130 shows a specific behavior after performing a soft reset of the gyroscope. After carrying out the soft reset, the TWI slave is reset. This releases the bus before completing the command and a NACK is sent instead of an ACK. The user may ignore the first NACK after a soft reset of the gyroscope.

# **6.3 Access Restrictions (SPI and TWI)**

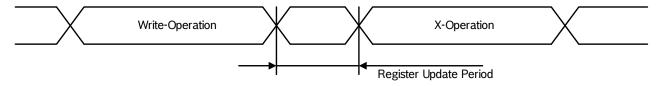

In order to allow for the correct internal synchronization of data written to the SMI130, certain access restrictions apply for consecutive write accesses or a write/read sequence through the SPI and TWI interface.

As illustrated in Figure 27, an interface idle time of at least 2  $\mu$ s is required following a write operation when the device operates.

Figure 27 Post-write access timing constraints

# 7 Application Details

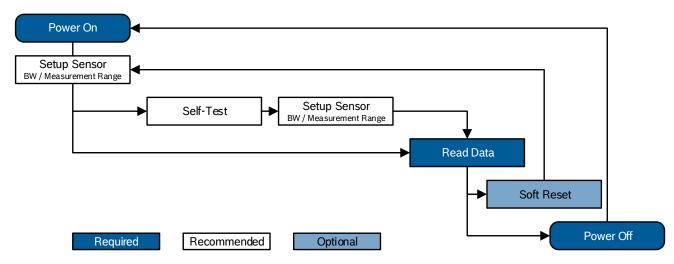

In Figure 28 the basic flow chart for the sensor application is shown. Three different categories of functional elements are shown:

Required: these blocks are mandatory for a proper sensor functionality and

retrieving data (e.g. read data)

Recommended: these blocks are useful to detect potential sensor failure and to allow

further configuration of the sensor (e.g. self-test, sensor setup)

Optional: depending on the customer specific application, these blocks might be

required (e.g. interrupt configuration)

The functional elements are described in the following sections.

Figure 28 Basic flow chart for SMI130 application with key functional elements

# 7.1 Sensor Setup

The basic sensor setup includes selection of the bandwidth and measurement range for accelerometer and gyroscope.

#### 7.1.1 Accelerometer

The **bandwidth** of filtered acceleration data is determined by setting bits <4:0> (*bw*) in register ACC 0x10 (*PMU\_BW*) as shown in the following table. It is recommended to actively set an appropriate, application specific bandwidth and to use the *bw* range from 01000 to 01111.

| bw <4:0> | Bandwidth | Update Time |

|----------|-----------|-------------|

| 00xxx    | reserved  | -           |

| 01000    | 7.81 Hz   | 64 ms       |

| 01001    | 15.63 Hz  | 32 ms       |

| 01010    | 31.25 Hz  | 16 ms       |

| 01011    | 62.5 Hz   | 8 ms        |

| 01100    | 125 Hz    | 4 ms        |

| 01101    | 250 Hz    | 2 ms        |

| 01110    | 500 Hz    | 1 ms        |

| 01111    | 1000 Hz   | 0.5 ms      |

| 1xxxx    | reserved  | -           |

The acceleration measurement **range** can be selected via bits <3:0> (*range*) in register ACC 0x0F (*PMU\_RANGE*) according to the table below.

| range <3:0> | Measurement Range | Resolution |

|-------------|-------------------|------------|

| 0011        | ±2 g              | 1024 LSB/g |

| 0101        | ±4 g              | 512 LSB/g  |

| 1000        | ±8 g              | 256 LSB/g  |

| 1100        | ±16 g             | 128 LSB/g  |

| others      | reserved          | -          |

## 7.1.2 Gyroscope

The **bandwidth** of filtered rate data is determined by setting bits <3:0> (*bw*) in register GYR 0x10 (*BW*) as shown in the following table.

| bw <3:0> | Filter Bandwidth [Hz] | ODR [Hz] | Decimation Factor |

|----------|-----------------------|----------|-------------------|

| 0111     | 32                    | 100      | 20                |

| 0110     | 64                    | 200      | 10                |

| 0101     | 12                    | 100      | 20                |

| 0100     | 23                    | 200      | 10                |

| 0011     | 47                    | 400      | 5                 |

| 0010     | 116                   | 1000     | 2                 |

| 0001     | 230                   | 2000     | 0                 |

| 0000     | 523 (unfiltered)      | 2000     | 0                 |

| 1xxx     | reserved              | reserved | reserved          |

The rate measurement **range** can be selected via bits <2:0> (*range*) in register GYR 0x0F (*RANGE*) according to the table below.

| range <2:0> | Measurement Range | Resolution     |

|-------------|-------------------|----------------|

| 000         | ±2000 °/s         | 16.38 LSB/°/s  |

| 001         | ±1000 °/s         | 32.77 LSB/°/s  |

| 010         | ±500 °/s          | 65.54 LSB/°/s  |

| 011         | ±250 °/s          | 131.07 LSB/°/s |

| 100         | ±125 °/s          | 262.14 LSB/°/s |

| others      | reserved          | -              |

## 7.2 Self-Test

#### 7.2.1 Accelerometer

The self-test feature allows for checking the sensor functionality by applying electrostatic forces to the sensor core instead of external accelerations. By physically deflecting the seismic mass, the entire signal path of the sensor is tested. Activation of the self-test results in a static offset in the acceleration data. Any external acceleration or gravitational force that is applied to the sensor during a self-test will be observed in the sensor output as a superposition of the acceleration and the self-test signal.

Before enabling the self-test, the acceleration measurement range should be set to **8 g**. The bandwidth should be set to **1000 Hz**.

The self-test is activated with the register ACC 0x32 (*PMU\_SELF\_TEST*). For details please refer to section 0. All three axes are tested for a complete self-test. For a proper interpretation of the self-test signals, it is recommended to perform the self-test for both the positive and the negative direction and to then calculate the difference of the resulting acceleration values.

The self-test of **each axis** is triggered **separately** by setting bits <1:0> (self\_test\_axis) according to the following table.

| self_test_axis <1:0> | 00                   | 01     | 10     | 11     |

|----------------------|----------------------|--------|--------|--------|

| self-test            | deactivate self-test | x-axis | y-axis | z-axis |

The **direction of the deflection** is controlled via bit 2 (*self\_test\_sign*). The deflection is negative (positive) when setting *self\_test\_sign* to 0 (1). The amplitude of the deflection has to be set high by setting bit 4 (*self\_test\_amp*) to 1. When a self-test is performed, only the acceleration data readout value of the selected axis is valid.

For each axis and direction, a waiting time of 50 ms is mandatory after enabling the self-test.

The minimum difference for each axis is shown in the table below. The measured signal differences can be significantly larger.

|                           | x-axis | y-axis | z-axis |  |

|---------------------------|--------|--------|--------|--|

| minimum difference signal | 800 mg | 800 mg | 400 mg |  |

After performing a self-test, a reset of the device is recommended. If the reset cannot be performed, the following sequence must be kept to prevent unwanted interrupt generation:

- **A.** Disable interrupts

- **B.** Change parameters of interrupts

- C. Wait for at least 50 ms

- D. Enable desired interrupts

Note:

An external stimulus during the self-test procedure might lead to wrong sensor reading for the specific axis. This might result in a failure of the self-test. A repetition of the self-test is recommended in this case.

## 7.2.2 Gyroscope

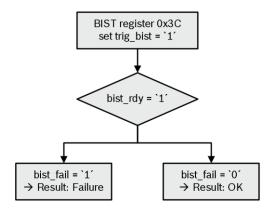

A built-in self-test (BIST) has been implemented, which provides a quick way to determine if the gyroscope is operational within the specifications.

The BIST uses three parameters for the evaluation of proper device operation:

- Drive voltage regulator

- Sense frontend offset regulator of x-, y- and z-channel

- Quad regulator for x-, y- and z-channel

Figure 29 SMI130 BIST sequence

If any of the three parameters is not within the limits, the BIST results in a 'fail'.

To trigger the BIST, set bit 0 (trig\_bist) in register GYR 0x3C (BIST) to 1.

Two bits (read-only) have to be checked in register GYR 0x3C (BIST):

- ▶ bit 1(bist rdy)

- bit 2 (bist fail)

bist\_rdy = 1 indicates that a test was performed. bist\_fail contains the result of the BIST. bist\_fail = 1 corresponds to a 'fail'.

A simple option to check for the sensor status is to read out bit 4 (*rate\_ok*) in register GYR 0x3C (*BIST*). No trigger is needed for this, and proper sensor function is indicated by a 1.

A waiting time of 50 ms is mandatory after enabling the self-test.

Note:

In contrast to the self-test of the accelerometer, the BIST of the gyroscope is fully decoupled from the sensing element. This means that the MEMS element is not deflected, and the current state of the MEMS element (e.g. its orientation) has no influence on the result of the BIST.

# 7.3 Interrupt Engine

## 7.3.1 New Data Interrupt

#### 7.3.1.1 Acceleration

The new\_data flag of each LSB register indicates whether the data for this specific channel has been updated. In addition, the acceleration part of SMI130 provides a new data interrupt. The new data interrupt allows for synchronous reading of acceleration data. It is generated after a new value of z-axis acceleration data has been stored in the data register.

The interrupt status flag *data\_int* of the new data interrupt is stored in register ACC 0x0A (*INT\_STATUS\_1*). It is active (inactive) if the bit is set to 1 (0). The interrupt is cleared automatically when the next data acquisition cycle starts. The interrupt status is 0 for a minimum of 50 µs. It is fixed to the non-latched mode.

The interrupt function associated with a specific status flag can be enabled (disabled) via setting bit 4  $(data_en)$  in register ACC 0x17  $(INT_EN_1)$  to 1 (0).

In addition, the new data interrupt can be mapped to an external INT2 pin. This feature can be enabled (disabled) via setting bit 7 (int2\_data) in register ACC 0x1A (INT\_MAP\_1) to 1 (0).

#### 7.3.1.2 Gyroscope

Comparable to the acceleration part, the SMI130 provides a new data interrupt for the gyroscope. The new data interrupt allows for synchronous reading of angular rate data. It is generated after storing a new z-axis angular rate value in the data register.

The interrupt status flag  $data_int$  of the new data interrupt is stored in register GYR 0x0A ( $INT_STATUS_1$ ). It is active (inactive) if the bit is set to 1 (0). The interrupt clears automatically after 280 – 400  $\mu$ s depending on settings. The interrupt mode of the new data interrupt is non-latched.

The interrupt function associated with the status flag can be enabled (disabled) via setting bit 7 (*data\_en*) in register GYR 0x15 (*INT\_EN\_0*) to 1 (0).

In addition, the new data interrupt can be mapped to an external INT1 pin. This feature can be enabled (disabled) via setting bit 0 (*int1 data*) in register GYR 0x18 (*INT MAP 1*) to 1 (0).

# 7.4 Reading Data

#### 7.4.1 Accelerometer

For each axis, the 12 bits of acceleration data are split into a MSB upper part (bits <11:4> of acceleration data) and a LSB lower part (bits <3:0> of acceleration data). Registers ACC 0x02 (*ACCD\_X\_LSB*) and ACC 0x03 (*ACCD\_X\_MSB*) contain the acceleration data for the x-channel, ACC 0x04 (*ACCD\_Y\_LSB*) and ACC 0x05 (*ACCD\_Y\_MSB*) for the y-channel, and ACC 0x06 (ACCD\_Z\_LSB) and ACC 0x07 (*ACCD\_Z\_MSB*) for the z-channel. The LSB part (all axes) also contains the *new\_data* flag. It is recommended to always start reading out the LSB register first followed by the corresponding MSB register. Acceleration data may be read from register LSB and/or MSB at any time except during power-up.

An example for the range setting of ±2 g is shown in the table below.

| LSB                | 1111 xxxx      | 0000 xxxx      | <   | 0000 xxxx      |

|--------------------|----------------|----------------|-----|----------------|

| MSB                | 0111 1111      | 0000 0000      |     | 1000 0000      |

| LSB + MSB [bin]    | 0111 1111 1111 | 0000 0000 0000 |     | 1000 0000 0000 |

| LSB + MSB [dec]    | +2047          | <br>0          | ••• | -2048          |

| Acceleration value | +2 g           | <br>0 g        |     | -2 g           |

In order to ensure data integrity, a **shadowing procedure** can be enabled. In this case, the content of the MSB register is locked by reading the corresponding LSB register until the MSB register is read. This means that the LSB register should be read first, followed by the MSB, register in order to remove the data lock. This condition is inherently fulfilled if a burst-mode read access is performed. Shadowing can be disabled (enabled) by writing 1 (0) to bit 6 (*shadow\_dis*) in the register ACC 0x13 (*ACCD\_HBW*). For disabled shadowing, the content of both MSB and LSB registers is updated immediately. Unused bits of the LSB registers may have any value and should be ignored.

**New data** can be identified by bit 0 (*new\_data* flag) of each LSB register. It is set after the data registers have been updated and reset if either the corresponding MSB or LSB part is read. In addition there is the opportunity to use the new data interrupt, which is described in section 7.3.1.1.

Two different streams of acceleration data are available, **unfiltered** and **filtered** data. The unfiltered data is sampled with 2 kHz. The sampling rate (output data rate ODR) of the filtered data depends on the selected filter bandwidth (*BW*) and is always twice the selected bandwidth (*BW* = ODR/2). The type of data is stored