# MSKSEMI 美森科

**ESD**

TVS

TSS

MOV

GDT

PIFD

# ESD3V3U4ULC-MS

Product specification

#### **Features**

- Solid-state silicon-avalanche technology

- Lowoperating and clamping voltage

- Up to four I/OLines of Protection

- Ultra low capacitance: 0.5pFtypical(I/O to I/O)

- Low Leakage

- Low operating voltage:3.3V

- Flow-Through design

#### **Mechanical Characteristics**

- TSLP-9-1 package (2.5×1.0×0.58mm)

- Molding compound flammability rating: UL 94V-0

- Packaging: Tape and Reel

- RoHS/WEEE Compliant

## **IEC COMPATIBILITY (EN61000-4)**

- IEC 61000-4-2 (ESD) ±15kV (air), ±8kV (contact)

- IEC 61000-4-4 (EFT) 40A (5/50ns)

- IEC 61000-4-5(Lightning) 5A(8/20μs)

# **Applications**

- Digital Visual Interface(DVI)

- MDDI Ports

- DisplayPortTM Interface

- PCI Express

- High Definition Multi-Media Interface(HDMI)

- eSATA Interfaces

#### **Reference News**

| PACKAGE OUTLINE | Circuit Diagram                                           | Marking |

|-----------------|-----------------------------------------------------------|---------|

|                 | NC NC GND NC NC 10 9 8 7 6 11 2 3 4 5 1/O 1/O GND 1/O 1/O | 117 **  |

| TSLP-9-1        |                                                           |         |

#### **Schematic & PIN Configuration**

| Pin       | Identificaion                            |

|-----------|------------------------------------------|

| 1,2,4,5   | Input Lines                              |

| 6,7,9, 10 | Output Lines<br>(No Internal Connection) |

| 3,8       | Ground                                   |

**Absolute Maximum Rating**

| Rating                                                    | Symbol            | Value          | Units |

|-----------------------------------------------------------|-------------------|----------------|-------|

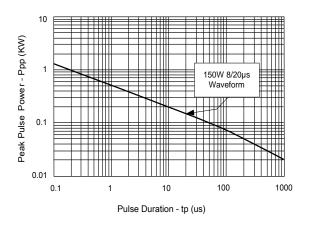

| Peak Pulse Power ( t <sub>p</sub> =8/20µs )               | P <sub>PP</sub>   | 80             | Watts |

| Peak Pulse Current ( t <sub>p</sub> =8/20μs )             | I <sub>pp</sub> 5 |                | А     |

| ESD per IEC 61000-4-2(Air) ESD per IEC 61000-4-2(contact) | Vesd              | +/-25<br>+/-25 | kV    |

| Operating Temperature                                     | TJ                | -55 to + 125   | °C    |

| Storage Temperature                                       | T <sub>STG</sub>  | -55 to +150    | °C    |

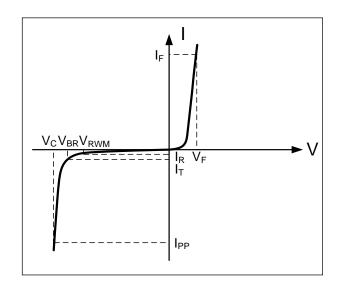

# **Electrical Parameters (T=25°C)**

| Symbol          | Parameter                              |  |  |  |

|-----------------|----------------------------------------|--|--|--|

| <b>I</b> PP     | Maximum Reverse Peak Pulse Current     |  |  |  |

| Vc              | Clamping Voltage @ IPP                 |  |  |  |

| VRWM            | Working Peak Reverse Voltage           |  |  |  |

| I <sub>R</sub>  | Maximum Reverse Leakage Current @ VRWM |  |  |  |

| V <sub>BR</sub> | Breakdown Voltage @ I⊤                 |  |  |  |

| lτ              | Test Current                           |  |  |  |

| lF              | Forward Current                        |  |  |  |

| VF              | Forward Voltage @ I <sub>F</sub>       |  |  |  |

## **Electrical Characteristics**

| Parameter                 | Symbol           | Conditions                                                             | Minimum | Typical | Maximum | Units |

|---------------------------|------------------|------------------------------------------------------------------------|---------|---------|---------|-------|

| Reverse Stand-Off Voltage | V <sub>RWM</sub> | Any I/O pin to ground                                                  |         |         | 3.3     | ٧     |

| Reverse Breakdown Voltage | $V_{BR}$         | l₁ = 1mA<br>Any I/O pin to ground                                      | 6.0     |         |         | V     |

| Reverse Leakage Current   | l <sub>R</sub>   | V <sub>RWM</sub> = 3V, T=25°C<br>Any I/O pin to ground                 |         |         | 1       | μΑ    |

| Clamping Voltage          | Vc               | I <sub>pp</sub> =5A, t <sub>p</sub> =8/20 µ s<br>Any I/O pin to ground |         |         | 15      | V     |

| Junction Capacitance      | Cj               | V <sub>R</sub> = 0V, f = 1MHz<br>I/O pin to GND                        |         |         | 0.8     | pF    |

|                           |                  | V <sub>R</sub> = 0V, f = 1MHz<br>Between I/O pins                      |         | 0.3     |         | pF    |

# **Typical Characteristics**

#### Non-Repetitive Peak Pulse Power vs. Pulse Time

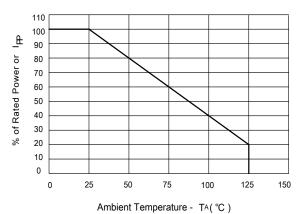

#### **Power Derating curve**

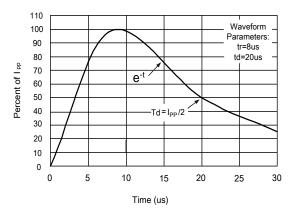

#### **Pulse Waveform**

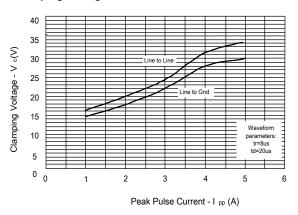

#### Clamping Voltage vs.Peak Pulse Current

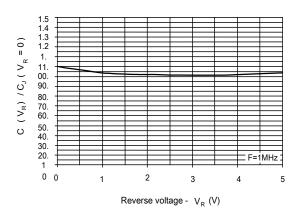

#### Normalized Capacitance vs. Reverse Voltage

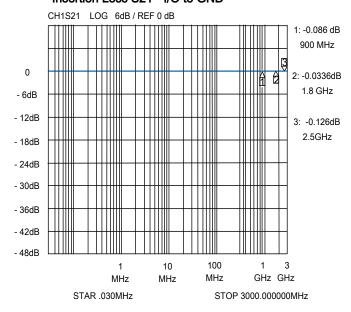

#### Insertion Loss S21 - I/O to GND

### **Design Recommendations for HDMI protection**

Adding external ESD protection to HDMI ports can be challenging. First, ESD protection devices have an inherent junction capacitance. Furthermore, adding even a small amount of capacitance will cause the impedance of the differential pair to drop. Second, large packages and land pattern requirements cause discontinuities that adversely affect signal integrity. The ESD3V3U4ULC-MS are specifically designed for protection of high-speed interfaces such as HDMI.

They present <0.4pF capacitance between the pairs while being rated to handle ±25kV ESDcontact discharges (±25kV air discharge) as outlined in IEC 61000-4-2. Each device is in a leadless SLP package that is less than 1.1mm wide. They are designed such that the traces flow straight through the device. The narrow package and flow-through design reduces discontinuities and minimizes impact on signal integrity. This becomes even more critical as signal speeds increase.

#### **Pin Configuration**

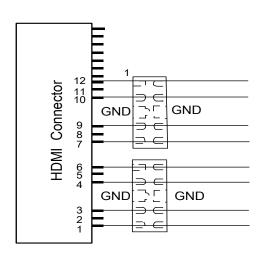

Figure 1 is an example of how to route the high speed differential traces through the ESD3V3U4ULC. The solid line represents the PCB trace. The PCB traces are used to connect the pin pairs for each line (pin 1 to pin 10, pin 2 to pin 9, pin 4 to pin 7, pin 5 to pin 6). For example, line 1 enters at pin 1 and exits at Pin 10 and the PCB trace connects pin 1 and 10 together. This is true for lines connected at pins 2, 4, and 5 also. Ground is connected at pins 3 and 8. One large ground pad should be used in lieu of two separate pads. The same layout rules apply for the ESD3V3U4ULC.

Figure 1.Flow though layout Using

## **Design Recommendations for HDMI Protection**

Good circuit board layout is critical not only for signal integrity, but also for effective suppression of ESD induced transients. For optimum ESD protection, the following guidelines are recommended:

- Place the device as close to the connector as possible. This practice restricts ESD coupling into adjacent traces and reduces parasitic inductance.

- The ESD transient return path to ground should be kept as short as possible.

Whenever possible, use multiple micro vias connected directly from the device ground pad to the ground plane.

- Avoid running critical signals near board edges.

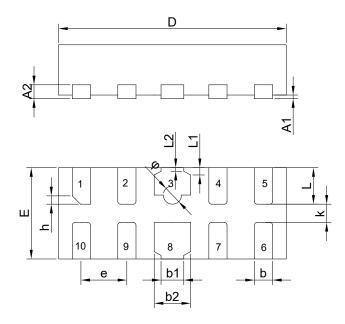

# Dimension (DFN2510)

| Dimensions in Millimeter |       |           |       |        |       |          |       |

|--------------------------|-------|-----------|-------|--------|-------|----------|-------|

| Symbol                   | Min.  | Nom.      | Max.  | Symbol | Min.  | Nom.     | Max.  |

| Α                        | 0.500 | 0.550     | 0.600 | D      | 2.450 | 2.500    | 2.550 |

| A1                       | 0.00  | 1         | 0.05  | Е      | 0.950 | 1.00     | 1.050 |

| A2                       | 0.122 | 0.152     | 0.200 | е      | 0.450 | 0.500    | 0.550 |

| b                        | 0.150 | 0.200     | 0.250 | h      | 0.080 | 0.120    | 0.150 |

| b1                       | 0.200 | 0.250     | 0.300 | k      | 0.150 | 0.200    | 0.250 |

| b2                       | 0.350 | 0.400     | 0.450 | L      | 0.350 | 0.400    | 0.450 |

| L1                       |       | 0.075 REF |       | L2     |       | 0.05 REF |       |

| φ                        | 0.150 | 0.200     | 0.250 |        |       |          |       |

# **REEL SPECIFICATION**

| P/N            | PKG      | QTY  |

|----------------|----------|------|

| ESD3V3U4ULC-MS | TSLP-9-1 | 3000 |

#### **Attention**

- Any and all MSKSEMI Semiconductor products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your MSKSEMI Semiconductor representative nearest you before using any MSKSEMI Semiconductor products described or contained herein in such applications.

- MSKSEMI Semiconductor assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all MSKSEMI Semiconductor products described or contained herein.

- Specifications of any and all MSKSEMI Semiconductor products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer'sproducts or equipment.

- MSKSEMI Semiconductor. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with someprobability. It is possiblethat these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents—or events cannot occur. Such measures include but are not limited to protective circuits anderror prevention circuitsfor safedesign, redundant design, and structural design.

- In the event that any or all MSKSEMI Semiconductor products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from theauthorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of MSKSEMI Semiconductor.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. MSKSEMI Semiconductor believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. Whendesigning equipment, refer to the "Delivery Specification" for the MSKSEMI Semiconductor productthat you intend to use.