**Circuits

from the Lab™**

Reference Circuits

*Circuits from the Lab™ reference circuits are engineered and tested for quick and easy system integration to help solve today's analog, mixed-signal, and RF design challenges. For more information and/or support, visit [www.analog.com/CN0188](http://www.analog.com/CN0188).*

**Devices Connected/Referenced**

|           |                                                                    |

|-----------|--------------------------------------------------------------------|

| ADA4051-2 | Micropower, Zero-Drift, Rail-to-Rail Input and Output, Dual Op Amp |

| AD7171    | Low Power, 16-Bit, Sigma-Delta ADC                                 |

| ADR381    | 2.5 V, Low Noise, High Accuracy, Band Gap Voltage Reference        |

| ADuM5402  | Quad-Channel Isolator with Integrated DC-to-DC Converter           |

## Low Cost, Level Shifted Low Side Current Monitor for Negative High Voltage Rails

### EVALUATION AND DESIGN SUPPORT

#### Circuit Evaluation Boards

[CN-0188 Circuit Evaluation Board \(EVAL-CN0188-SDPZ\)](#)

[System Demonstration Platform \(EVAL-SDP-CB1Z\)](#)

#### Design and Integration Files

[Schematics, Layout Files, Bill of Materials](#)

### CIRCUIT FUNCTION AND BENEFITS

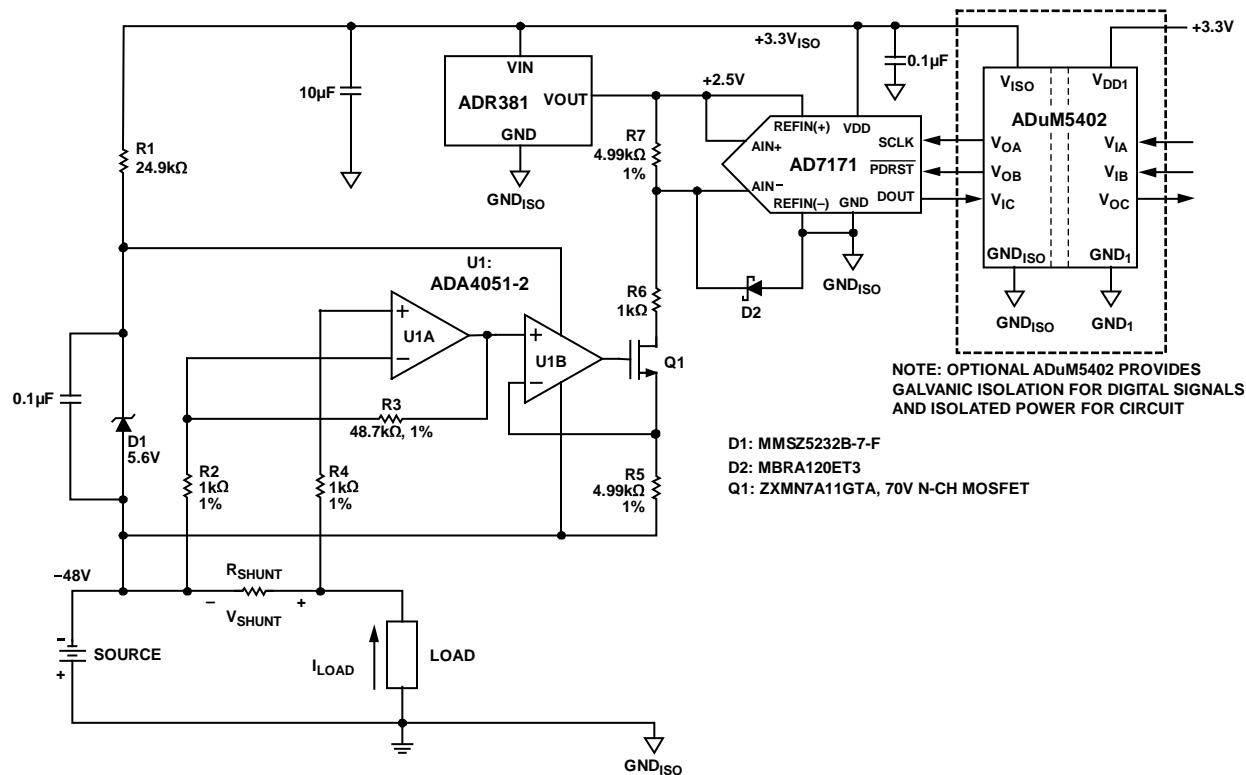

The circuit shown in Figure 1 monitors current in individual channels of  $-48\text{ V}$  to better than 1% accuracy. The load current passes through a shunt resistor, which is external to the circuit. The shunt resistor value is chosen so that the shunt voltage is approximately 50 mV at maximum load current.

09570-001

Figure 1. Low Side Current Monitor for Negative High Voltage Rails (All Connections and Decoupling Not Shown)

**Rev. B**

Circuits from the Lab™ circuits from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a lab environment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause whatsoever connected to the use of any Circuits from the Lab circuits. (Continued on last page)

The measurement result from the [AD7171](#) is provided as a digital code utilizing a simple 2-wire, SPI-compatible serial interface. The entire circuit operates on a single +3.3 V supply. Optional galvanic isolation is provided by the [ADuM5402](#) quad channel isolator. In addition to isolating the output data, the [ADuM5402](#) digital isolator can also supply isolated +3.3 V for the circuit. The [ADuM5402](#) is not required for normal circuit operation unless galvanic isolation is needed.

This combination of parts provides an accurate high voltage negative rail current sense solution with a small component count, low cost, and low power. The accuracy of the measurement is primarily determined by resistor tolerances and the accuracy of the band gap reference, and is typically better than 1%.

## CIRCUIT DESCRIPTION

The circuit is designed for a full-scale shunt voltage of 50 mV at maximum load current  $I_{MAX}$ . Therefore, the value of the shunt resistor is  $R_{SHUNT} = (50 \text{ mV})/(I_{MAX})$ .

The "ground" for the op amp stage is connected to the common-mode source voltage (-48 V). The voltage for the op amp stage is supplied by the "floating" 5.6 V zener diode, which is biased at a current of approximately 2 mA. This eliminates the need for a separate power supply. The circuit will operate with a source voltage from -60 V to -10 V with no modifications.

The shunt voltage is amplified by a factor of 49.7 using U1A, where  $G = 1 + R3/R2$ . The zero-drift [ADA4051-2](#) has a low offset voltage (15  $\mu\text{V}$  maximum) and does not contribute significant error to the measurement. A full-scale shunt voltage of 50 mV produces a full-scale output voltage from U1A of 2.485 V (referenced to the common-mode source voltage).

An N-channel MOSFET transistor with a large  $V_{DS}$  breakdown (70 V) inside the feedback loop of U1B applies the output voltage of U1A across resistor R5, and the resulting current flows through R6 and R7. The full-scale voltage from U1A of 2.485 V produces a full-scale current of 0.498 mA, which generates a full-scale voltage of 2.485 V across resistor R7. The voltage across R7 is applied to AIN- of the ADC. Resistor R6 and the Schottky diode D2 provide input protection for the [AD7171](#) in the event the MOSFET shorts out.

Notice that the power supply voltage for the [ADR381](#), the [AD7171](#), and the floating zener diode is supplied by the isolated power output (+3.3 V<sub>ISO</sub>) of the [ADuM5402](#) quad isolator.

The reference voltage for the [AD7171](#) is supplied by the [ADR381](#) precision band gap reference. The [ADR381](#) has an initial accuracy of  $\pm 0.24\%$  and a typical temperature coefficient of 5 ppm/ $^{\circ}\text{C}$ .

Although it is possible to operate both the [AD7171](#) VDD and REFIN(+) from the 3.3 V power supply, using a separate

reference provides better accuracy. A 2.5 V reference is chosen to provide sufficient headroom.

The input voltage to the [AD7171](#) ADC is converted into an offset binary code at the output of the ADC. The [ADuM5402](#) provides the isolation for the DOUT data output, the SCLK input, and the PDRST input.

The code is processed in the PC by using the SDP hardware board and LabVIEW software.

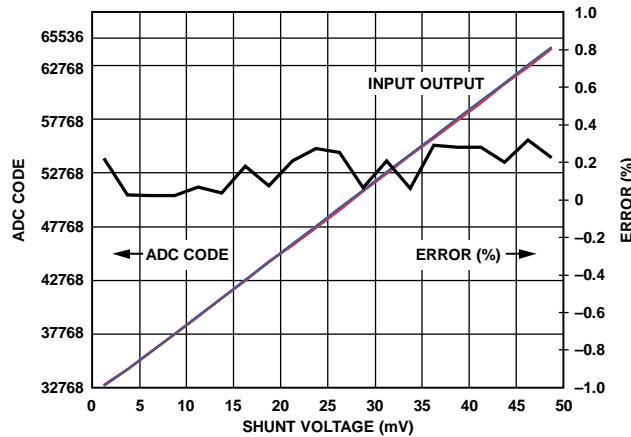

The graph in Figure 2 shows how the circuit tested achieves an error of 0.3% over the entire input voltage range (0 mV to 50 mV). A comparison is made between the code seen at the output of the ADC, recorded by LabVIEW, and an ideal code calculated based on a perfect system.

Figure 2. Plot of Output and Error vs. Shunt Voltage

In order to calculate this ideal code, there are several assumptions which must be made about the performance of the system. First, the op amp gain stage must multiply the input signal by exactly 49.7. Depending on resistor tolerances (1%), this value will vary by 2% worst case. Secondly, the current sink resistor (R5) and the ADC input resistor (R7) are assumed to be identical. In the circuit, these particular resistors have a tolerance of 1%. Since they are the same value, the matching will probably be better than 1%. Resistors with tighter tolerances can be used, which will increase the accuracy and the cost of the circuit.

Several items have been implemented on the PCB, which are not crucial to the function or performance of the circuit but are required to ensure user and hardware safety. As an example, if Q1 breaks down or shorts out, the ADC, SDP board, user, and user's PC are all at risk due to the large negative voltage potential. The safety items included are passive elements R6, D2, which protect the [AD7171](#), and the [ADuM5402](#) quad-channel digital isolator, which protects the circuits on the SDP board, as well as the user's PC.

### PCB Layout Considerations

In any circuit where accuracy is crucial, it is important to consider the power supply and ground return layout on the board. The PCB should isolate the digital and analog sections as much as possible. This PCB was constructed in a four layer stack up with large area ground plane layers and power plane polygons. See the [MT-031 Tutorial](#) for more discussion on layout and grounding and the [MT-101 Tutorial](#) for information on decoupling techniques.

The power supply to the **AD7171** and **ADuM5402** should be decoupled with  $10\ \mu\text{F}$  and  $0.1\ \mu\text{F}$  capacitors to properly suppress noise and reduce ripple. The capacitors should be placed as close to the device as possible with the  $0.1\ \mu\text{F}$  capacitor having a low ESR value. Ceramic capacitors are advised for all high frequency decoupling.

Care should be taken in considering the isolation gap between the primary and secondary sides of the **ADuM5402**. The EVAL-CN0188-SDPZ board maximizes this distance by pulling back any polygons or components on the top layer and aligning them with the pins on the **ADuM5402**.

Power supply lines should have as large a trace width as possible to provide low impedance paths and reduce glitch effects on the

supply line. Clocks and other fast switching digital signals should be shielded from other parts of the board by digital ground.

A complete design support package for this circuit note, including board layouts, can be found at <http://www.analog.com/CN0188-DesignSupport>.

### COMMON VARIATIONS

There are a number of solutions available for high-side sensing of positive sources. IC solutions using current sense amplifiers, difference amplifiers, or a combination of these are available.

["High-Side Current Sensing: Difference Amplifier vs. Current-Sense Amplifier," Analog Dialogue, January 2008](#), describes the use of current sense and difference amplifiers. The article is available at [www.analog.com/HighSide\\_CurrentSensing](http://www.analog.com/HighSide_CurrentSensing).

The following URLs link to Analog Devices products which are useful in solving the current sense problem:

Current sense amplifiers: [www.analog.com/CurrentSenseAmps](http://www.analog.com/CurrentSenseAmps)

Difference amplifiers: [www.analog.com/DifferenceAmps](http://www.analog.com/DifferenceAmps)

Instrumentation amplifiers: [www.analog.com/InstrumentationAmps](http://www.analog.com/InstrumentationAmps)

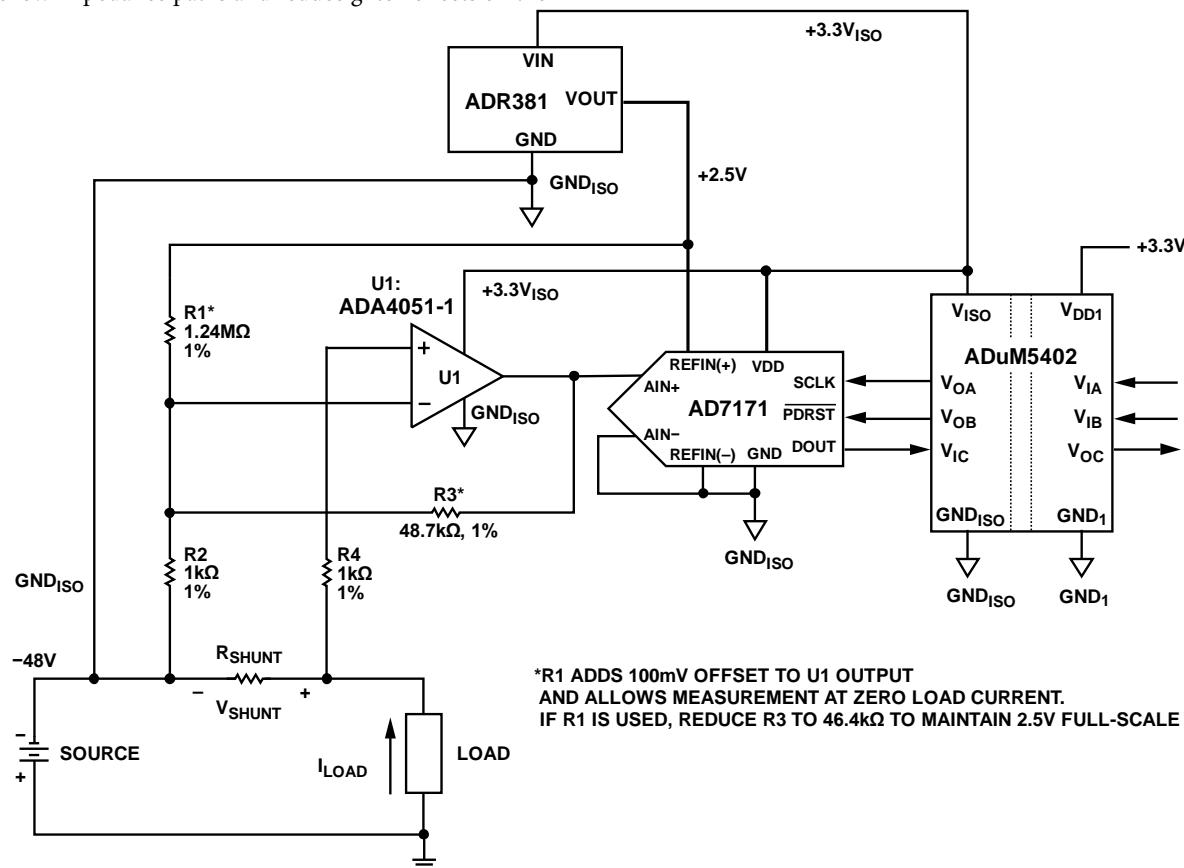

Figure 3. Alternate Galvanically Isolated Negative Rail Current Sense Circuit Powered Directly from  $-48\text{V}$  Source and ADuM5402 Isolator (All Connections and Decoupling Not Shown)

Figure 3 shows an alternate circuit which can be used when galvanic isolation is required. The "ground" for the entire circuit is connected to the  $-48$  V source. The isolated  $+3.3$  V from the **ADuM5402** is used to power the circuit. Note that this configuration does not require the op amp/MOSFET level shifter (see Figure 1) because the level shifting function is accomplished by the **ADuM5402** isolator which allows a new ground reference (GND1) to be established for the digital signals.

A single zero-drift **ADA4051-1** provides a gain of 49.7 to the shunt voltage. Resistor R1 provides a positive offset voltage of 100 mV at the op amp output that allows the circuit to operate down to zero load current. If this offset is added, then R3 should be reduced to  $46.4\text{ k}\Omega$  to maintain a full-scale ADC input voltage of 2.5 V for a 50 mV shunt voltage. Without the offset, the **ADA4051-1** output will become nonlinear for output voltages less than about 40 mV.

## CIRCUIT EVALUATION AND TEST

This circuit uses the EVAL-CN0188-SDPZ circuit board and the EVAL-SDP-CB1Z System Demonstration Platform (SDP) evaluation board. The two boards have 120-pin mating connectors, allowing for the quick setup and evaluation of the circuit's performance. The EVAL-CN0188-SDPZ board contains the circuit to be evaluated, as described in this note, and the SDP evaluation board is used with the CN0188 evaluation software to capture the data from the EVAL-CN0188-SDPZ circuit board.

### Equipment Needed

- PC with a USB port and Windows® XP or Windows Vista® (32-bit), or Windows® 7 (32-bit)

- EVAL-CN0188-SDPZ circuit evaluation board

- EVAL-SDP-CB1Z SDP evaluation board

- CN0188 evaluation software

- Power supply:  $+6$  V, or  $+6$  V "wall wart"

- Shunt resistor with maximum voltage of 50 mV at the maximum load current.

- Electronic load

### Getting Started

Load the evaluation software by placing the CN0188 evaluation software disc in the CD drive of the PC. Using "My Computer," locate the drive that contains the evaluation software disc and open the Readme file. Follow the instructions contained in the Readme file for installing and using the evaluation software.

### Functional Block Diagram

See Figure 1 of this circuit note for the circuit block diagram and the "EVAL-CN0188-SDPZ-SCH" pdf file for the circuit

schematics. This file is contained in the [CN0188 Design Support Package](#).

### Setup

Connect the 120-pin connector on the EVAL-CN0188-SDPZ circuit board to the connector marked "CON A" on the EVAL-SDP-CB1Z evaluation (SDP) board. Nylon hardware should be used to firmly secure the two boards, using the holes provided at the ends of the 120-pin connectors.

Connect a shunt resistor across the input terminals ( $R_{SHUNT}$ ) with a load to ground as indicated in Figure 1. With power to the supply off, connect a  $+6$  V power supply to the pins marked " $+6$  V" and "GND" on the board. If available, a  $+6$  V "wall wart" can be connected to the barrel connector on the board and used in place of the  $+6$  V power supply. Connect the USB cable supplied with the SDP board to the USB port on the PC. Note: Do not connect the USB cable to the mini USB connector on the SDP board at this time.

It is important to connect the system ground and the PCB isolated ground to guarantee correct voltage levels and operation. Test point 31 and test point 32 give access to the GND\_ISO required to properly make this connection.

### Test

Apply power to the  $+6$  V supply (or "wall wart") connected to the EVAL-CN0188-SDPZ circuit board. Launch the evaluation software and connect the USB cable from the PC to the USB mini-connector on the SDP board.

Once USB communications are established, the SDP board can be used to send, receive, and capture serial data from the EVAL-CN0188-SDPZ board. Data can be recorded for various values of load current as the electronic load is stepped.

Information and details regarding how to use the evaluation software for data capture can be found in the CN0188 evaluation software Readme file.

Information regarding the SDP board can be found in the [SDP User Guide](#).

## LEARN MORE

### CN0188 Design Support Package:

<http://www.analog.com/CN0188-DesignSupport>

Sino, Henri. "High-Side Current Sensing: Difference Amplifier vs. Current-Sense Amplifier," *Analog Dialogue* 42-01, January (2008).

Cantrell, Mark. *Application Note AN-0971, Recommendations for Control of Radiated Emissions with isoPower Devices.* Analog Devices.

Chen, Baoxing, John Wynne, and Ronn Kliger. *High Speed Digital Isolators Using Microscale On-Chip Transformers*, Analog Devices, 2003.

Chen, Baoxing. *iCoupler® Products with isoPower™ Technology: Signal and Power Transfer Across Isolation Barrier Using Microtransformers*, Analog Devices, 2006

Chen, Baoxing. "Microtransformer Isolation Benefits Digital Control." *Power Electronics Technology*. October 2008.

Ghiorse, Rich. Application Note AN-825, *Power Supply Considerations in iCoupler® Isolation Products*, Analog Devices.

Krakauer, David. "Digital Isolation Offers Compact, Low-Cost Solutions to Challenging Design Problems." *Analog Dialogue*. Volume 40, December 2006.

MT-022 Tutorial, *ADC Architectures III: Sigma-Delta ADC Basics*, Analog Devices.

MT-023 Tutorial, *ADC Architectures IV: Sigma-Delta ADC Advanced Concepts and Applications*, Analog Devices.

MT-031 Tutorial, *Grounding Data Converters and Solving the Mystery of "AGND" and "DGND,"* Analog Devices.

MT-101 Tutorial, *Decoupling Techniques*, Analog Devices.

Wayne, Scott. "iCoupler® Digital Isolators Protect RS-232, RS-485, and CAN Buses in Industrial, Instrumentation, and Computer Applications." *Analog Dialogue*. Volume 39, October 2005.

### **Data Sheets and Evaluation Boards**

[CN0188 Circuit Evaluation Board \(EVAL-CN0188-SDPZ\)](#)

[System Demonstration Platform \(EVAL-SDP-CB1Z\)](#)

[ADA4051-2 Data Sheet](#)

[ADA4051-2 Evaluation Board](#)

[ADA4051-1 Data Sheet](#)

[ADA4051-1 Evaluation Board](#)

[AD7171 Data Sheet](#)

[AD7171 Evaluation Board](#)

[ADR381 Data Sheet](#)

[ADuM5402 Data Sheet](#)

[ADuM5402 Evaluation Board](#)

### **REVISION HISTORY**

#### **11/11—Rev. A to Rev. B**

|                                                              |   |

|--------------------------------------------------------------|---|

| <a href="#">Change to Figure 3</a> .....                     | 3 |

| <a href="#">Changes to Circuit Evaluation and Test</a> ..... | 4 |

#### **6/11—Rev. 0 to Rev. A**

|                                                                |   |

|----------------------------------------------------------------|---|

| <a href="#">Changes to Circuit Note Title</a> .....            | 1 |

| <a href="#">Changes to Circuit Function and Benefits</a> ..... | 1 |

| <a href="#">Changes to Figure 1</a> .....                      | 1 |

| <a href="#">Changes to Circuit Description</a> .....           | 2 |

| <a href="#">Changes to Common Variations</a> .....             | 3 |

| <a href="#">Added Figure 3</a> .....                           | 3 |

#### **4/11—Revision 0: Initial Version**

(Continued from first page) Circuits from the Lab circuits are intended only for use with Analog Devices products and are the intellectual property of Analog Devices or its licensors. While you may use the Circuits from the Lab circuits in the design of your product, no other license is granted by implication or otherwise under any patents or other intellectual property by application or use of the Circuits from the Lab circuits. Information furnished by Analog Devices is believed to be accurate and reliable. However, "Circuits from the Lab" are supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability, noninfringement or fitness for a particular purpose and no responsibility is assumed by Analog Devices for their use, nor for any infringements of patents or other rights of third parties that may result from their use. Analog Devices reserves the right to change any Circuits from the Lab circuits at any time without notice but is under no obligation to do so.