# Remote16-BIT I<sup>2</sup>C AND SMBus I/O Expander with Interrupt Output

#### **Features**

- I<sup>2</sup>C to Parallel-Port Expander

- Open-Drain Interrupt Output

- Low Standby-Current Consumption of 10μA Max

- Compatible With Most Micro controllers

- 400-kHz Fast I<sup>2</sup>C Bus

- Address by Three Hardware Address Pins for Use of up to Eight Devices

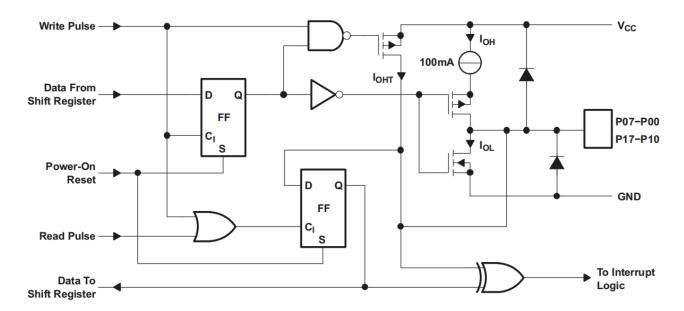

- Latched Outputs With High-Current Drive Capability for Directly Driving LEDs

- Current Source to Vcc for Actively Driving a High at the Output

- Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

- ESD Protection Exceeds JESD 22

- 2000-V Human-Body Model

- 200-V Machine Model

- 1000-V Charged-Device Model

# Ordering Information

| DEVICE       | Package Type    | MARKING | Packing | Packing Qty  |

|--------------|-----------------|---------|---------|--------------|

| PCF8575MS/TR | SSOP-24/QSOP-24 | PCF8575 | REEL    | 2500pcs/reel |

### **Description**

This 16-bit I/O expander for the two-line bidirectional bus (I<sup>2</sup>C) is designed for 2.5-V to 5.5-V VCC operation.

The PCF8575 device provides general-purpose remote I/O expansion for most microcontroller families by way of the I<sup>2</sup>C interface [serial clock (SCL), serial data (SDA)].

The device features a 16-bit quasi-bidirectional input/output (I/O) port (P07–P00, P17–P10), including latched outputs with high-current drive capability for directly driving LEDs. Each quasi-bidirectional I/O can be used as an input or output without the use of a data-direction control signal. At power on, the I/Os are high. In this mode, only a current source to VCC is active.

### **Applications**

- Telecom Shelters: Filter Units

- Servers

- Routers (Telecom Switching Equipment)

- Personal Computers

- Personal Electronics

- Industrial Automation

- Products with GPIO-Limited Processors

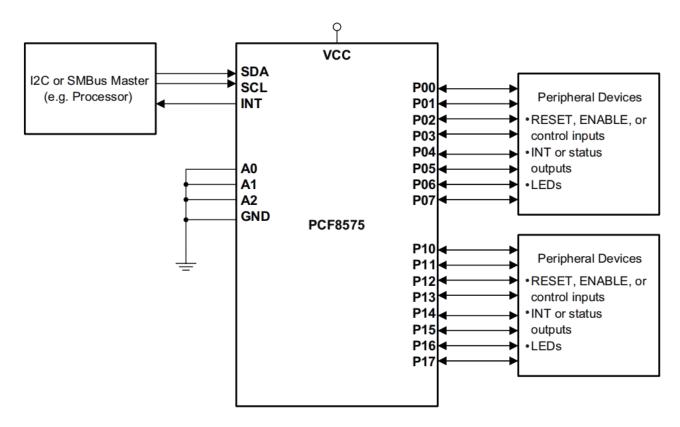

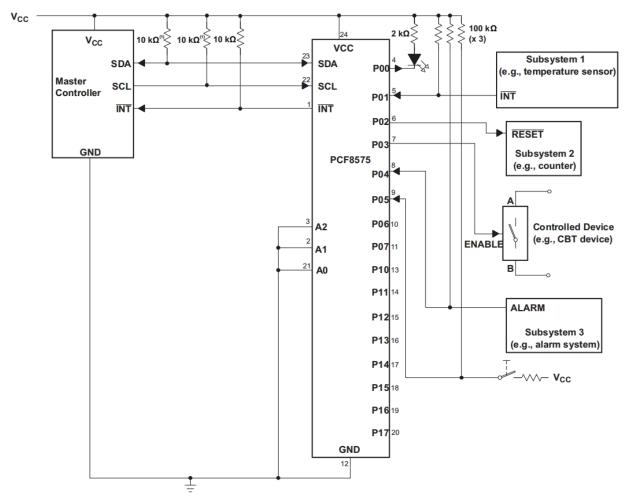

### **Simplified Schematic**

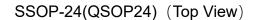

# **Pin Configuration and Functions**

# **Pin Functions**

| NAME | PIN | TYPE | DESCRIPTION                                                                           |  |

|------|-----|------|---------------------------------------------------------------------------------------|--|

| A0   | 21  | I    | Address input 0. Connect directly to VCC or ground. Pull-up resistors are not needed. |  |

| A1   | 2   | I    | Address input 1. Connect directly to VCC or ground. Pull-up resistors are not needed. |  |

| A2   | 3   | I    | Address input 2. Connect directly to VCC or ground. Pull-up resistors are not needed. |  |

| ĪNT  | 1   | 0    | Interrupt output. Connect to VCC through a pull-up resistor.                          |  |

| P00  | 4   | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P01  | 5   | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P02  | 6   | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P03  | 7   | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P04  | 8   | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P05  | 9   | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P06  | 10  | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P07  | 11  | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| GND  | 12  | _    | Ground                                                                                |  |

| P10  | 13  | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P11  | 14  | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P12  | 15  | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P13  | 16  | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P14  | 17  | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P15  | 18  | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P16  | 19  | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| P17  | 20  | I/O  | P-port input/output. Push-pull design structure.                                      |  |

| SCL  | 22  | I    | Serial clock line. Connect to VCC through a pull-up resistor                          |  |

| SDA  | 23  | I/O  | Serial data line. Connect to VCC through a pull-up resistor.                          |  |

| Vcc  | 24  | _    | Supply voltage                                                                        |  |

# **Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|      |                                          |                                   | MIN  | MAX                   | UNIT     |

|------|------------------------------------------|-----------------------------------|------|-----------------------|----------|

| VCC  | Supply voltage range                     |                                   | -0.5 | 6.5                   | ٧        |

| VI   | Input voltage range <sup>(2)</sup>       |                                   | -0.5 | $V_{CC} + 0.5$        | <b>V</b> |

| VO   | Output voltage range <sup>(2)</sup>      |                                   | -0.5 | V <sub>CC</sub> + 0.5 | V        |

| IIK  | Input clamp current                      | V <sub>1</sub> < 0                |      | -20                   | mA       |

| IOK  | Output clamp current                     | V <sub>0</sub> < 0                |      | -20                   | mA       |

| IOK  | Input/output clamp current               | $V_{O}$ < 0 or $V_{O}$ > $V_{CC}$ |      | -20                   | mA       |

| IOL  | Continuous output low current            | $V_{O} = 0$ to $V_{CC}$           |      | 50                    | mA       |

| IOH  | Continuous output high current           | $V_{O} = 0$ to $V_{CC}$           |      | -4                    | mA       |

|      | Continuous current through VCC or GND    |                                   |      | ±100                  | mA       |

| Tstg | Storage temperature range                |                                   |      | 150                   | °C       |

| T∟   | Lead Temperature (Soldering, 10 seconds) |                                   | -    | 260                   | ů        |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress

ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device

reliability.

# **ESD Ratings**

|        |                         |                                                              | VALUE | UNIT |

|--------|-------------------------|--------------------------------------------------------------|-------|------|

|        |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins | 2000  |      |

| V(ESD) | Electrostatic discharge | Charged device model (CDM), per JEDEC specification          | 1000  | V    |

|        |                         | JESD22- C101, all pins                                       | 1000  |      |

# **Recommended Operating Conditions**

|                 |                                  | MIN                   | MAX                   | UNIT |

|-----------------|----------------------------------|-----------------------|-----------------------|------|

| Vcc             | Supply voltage                   | 2.5                   | 5.5                   | ٧    |

| V <sub>IH</sub> | High-level input voltage         | 0.7 × V <sub>CC</sub> | V <sub>CC</sub> + 0.5 | ٧    |

| VIL             | Low-level input voltage          | -0.5                  | 0.3 × V <sub>CC</sub> | ٧    |

| I <sub>OH</sub> | P-port high-level output current |                       | -1                    | mA   |

| Іонт            | P-port transient pullup current  |                       | -10                   | mA   |

| I <sub>OL</sub> | P-port low-level output current  |                       | 25                    | mA   |

| T <sub>A</sub>  | Operating free-air temperature   | -40                   | 85                    | °C   |

#### **Thermal Information**

|      | THERMAL METRIC(1)                      | PCF8575MS | UNIT |

|------|----------------------------------------|-----------|------|

| Reja | Junction-to-ambient thermal resistance | 63        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>2.</sup> The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

### **Electrical Characteristics**

over recommended operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                      | TEST CONDITIONS                                                         | vcc            | MIN  | TYP(1) | MAX  | UNIT |

|------------------|--------------------------------|-------------------------------------------------------------------------|----------------|------|--------|------|------|

| V <sub>IK</sub>  | Input diode clamp voltage      | I <sub>I</sub> = -18mA                                                  | 2.5 V to 5.5 V | -1.2 |        |      | V    |

| V <sub>POR</sub> | Power-on reset voltage(2)      | $V_I = V_{CC}$ or GND, $I_O = 0$                                        | VPOR           |      | 1.2    | 1.8  | V    |

| I <sub>OH</sub>  | P port                         | V <sub>O</sub> = GND                                                    | 2.5 V to 5.5 V | -30  |        | -300 | μΑ   |

| Іонт             | P-port transient pullup curren | High during ACK, V <sub>OH</sub> = GND                                  | 2.5 V          | -0.5 | -1     |      | mA   |

|                  | SDA                            | V <sub>OL</sub> = 0.4 V                                                 |                | 3    |        |      |      |

|                  | Doort                          | V <sub>OL</sub> = 0.4 V                                                 | 2.5 V to 5.5 V | 5    | 15     |      | m A  |

| l <sub>OL</sub>  | P port                         | V <sub>OL</sub> = 1 V                                                   | 2.5 V to 5.5 V | 10   | 25     |      | mA . |

|                  | INT                            | V <sub>OL</sub> = 0.4 V                                                 |                | 1.3  |        |      |      |

|                  | SCL, SDA                       | V = V or CND                                                            | 251/40551      |      |        | ±5   |      |

| l <sub>ı</sub>   | A0, A1, A2                     | $V_1 = V_{CC}$ or GND                                                   | 2.5 V to 5.5 V |      |        | ±1   | μA   |

| lihl             | P port                         | V <sub>I</sub> ≥ V <sub>CC</sub> or VI ≤ GND                            | 2.5 V to 5.5 V | :    |        | ±400 | μΑ   |

|                  | Operating mode                 | V = V = 0 CND 10 = 0                                                    | 5.5 V          |      | 100    | 200  |      |

|                  |                                | $V_1 = V_{CC}$ or GND, IO = 0,<br>fscl = 400 kHz                        | 3.6 V          |      | 30     | 75   | - μA |

| 100              |                                | ISCI – 400 KHZ                                                          | 2.7 V          |      | 20     | 50   |      |

| ICC              |                                | V V ··· OND                                                             | 5.5 V          |      | 2.5    | 10   |      |

|                  | Standby mode                   | $V_1 = V_{CC}$ or GND,<br>$I_0 = 0$ , fscl = 0 kHz                      | 3.6 V          |      | 2.5    | 10   |      |

|                  |                                | 10 - 0, ISCI - 0 KMZ                                                    | 2.7 V          |      | 2.5    | 10   |      |

| ΔI <sub>CC</sub> | Supply current increase        | One input at $V_{CC} - 0.6 \text{ V}$ , Other inputs at $V_{CC}$ or GND | 2.5 V to 5.5 V |      |        | 200  | μΑ   |

| Cı               | SCL                            | V <sub>I</sub> = V <sub>CC</sub> or GND                                 | 2.5 V to 5.5 V |      | 3      | 7    | pF   |

| Cio              | SDA                            | - V <sub>IO</sub> = V <sub>CC</sub> or GND                              |                |      | 3      | 7    | nE   |

| CIO              | P port                         | VIO - VCC OI GIND                                                       | 2.5 V to 5.5 V |      | 4      | 10   | pF   |

<sup>(1)</sup> All typical values are at nominal supply voltage (2.5V, 3.3V, or 5V  $V_{CC}$ ) and  $T_A$  = 25°C.

<sup>(2)</sup> The power-on reset circuit resets the I2C bus logic with V<sub>CC</sub> < V<sub>POR</sub> and sets all I/Os to logic high (with current source to V<sub>CC</sub>).

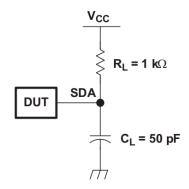

# **I2C Interface Timing Requirements**

over recommended operating free-air temperature range (unless otherwise noted) (see Figure 12)

|      |                                                          |                             | MIN                      | MAX | UNIT |

|------|----------------------------------------------------------|-----------------------------|--------------------------|-----|------|

| fscl | I <sup>2</sup> C clock frequency                         |                             |                          | 400 | kHz  |

| tsch | I <sup>2</sup> C clock high time                         |                             | 0.6                      |     | μs   |

| tscl | I <sup>2</sup> C clock low time                          |                             | 1.3                      |     | μs   |

| tsp  | I <sup>2</sup> C spike time                              |                             |                          | 50  | ns   |

| tsds | I <sup>2</sup> C serial data setup time                  |                             | 100                      |     | ns   |

| tsdh | I <sup>2</sup> C serial data hold time                   |                             | 0                        |     | ns   |

| ticr | I <sup>2</sup> C input rise time                         |                             | 20+0.1C <sub>b</sub> (1) | 300 | ns   |

| ticf | I <sup>2</sup> C input fall time                         |                             | 20+0.1C <sub>b</sub> (1) | 300 | ns   |

| tocf | I <sup>2</sup> C output fall time                        | 10-pF to 400-pF bus         |                          | 300 | ns   |

| tbuf | I <sup>2</sup> C bus free time between Stop and Start    |                             | 1.3                      |     | μs   |

| tsts | I <sup>2</sup> C start or repeated Start condition setup |                             | 0.6                      |     | μs   |

| tsth | I <sup>2</sup> C start or repeated Start condition hold  |                             | 0.6                      |     | μs   |

| tsps | I <sup>2</sup> C Stop condition setup                    |                             | 0.6                      |     | μs   |

| tvd  | Valid-data time                                          | SCL low to SDA output valid |                          | 1.2 | μs   |

| Cb   | I <sup>2</sup> C bus capacitive load                     |                             |                          | 400 | pF   |

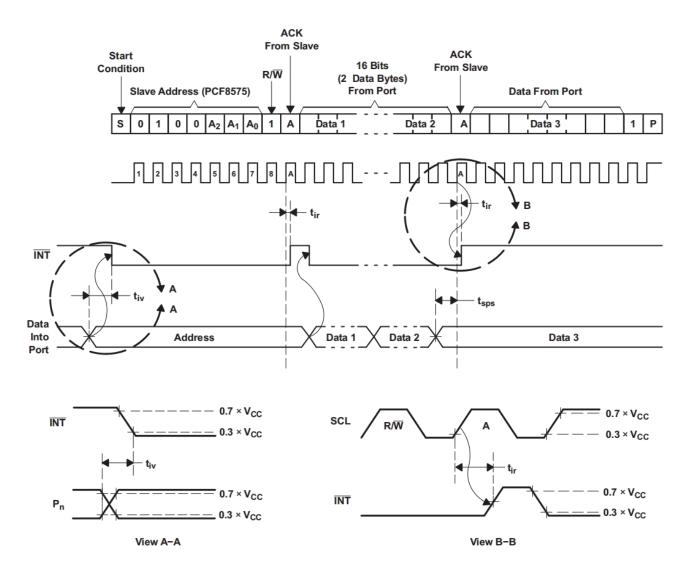

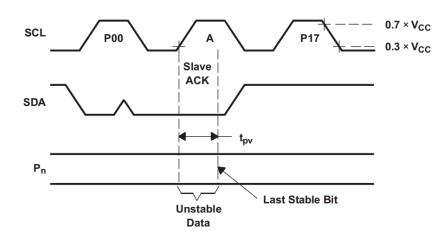

# **Switching Characteristics**

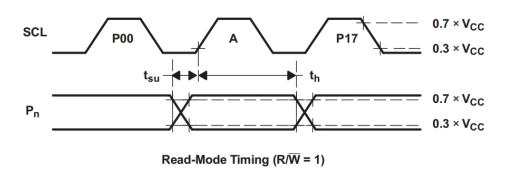

over recommended operating free-air temperature range,  $CL \le 100 \text{ pF}$  (unless otherwise noted) (see Figure 13 and Figure 14)

|     | PARAMETER                  | FROM (INPUT) | TO (OUTPUT) | MIN | MAX | UNIT |

|-----|----------------------------|--------------|-------------|-----|-----|------|

| tiv | Interrupt valid time       | P port       | INT         |     | 4   | μs   |

| tir | Interrupt reset delay time | SCL          | INT         |     | 4   | μs   |

| tpv | Output data valid          | SCL          | P port      |     | 4   | μs   |

| tsu | Input data setup time      | P port       | SCL         | 0   |     | μs   |

| th  | Input data hold time       | P port       | SCL         | 4   |     | μs   |

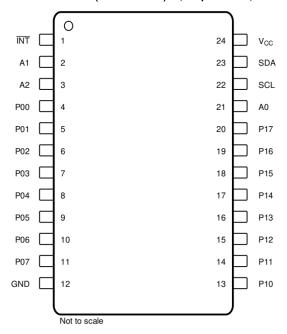

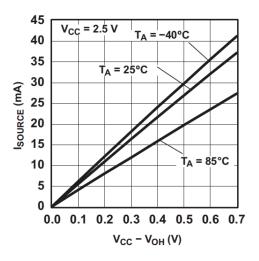

### **Typical Characteristics**

T<sub>A</sub> = 25°C (unless otherwise noted)

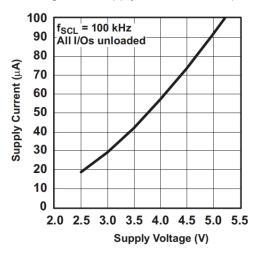

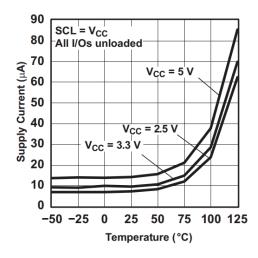

Figure 1. Supply Current vs Temperature

Figure 3. Supply Current vs Supply Voltage

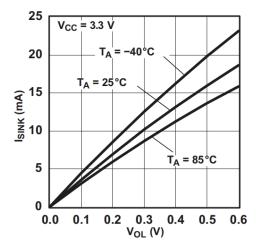

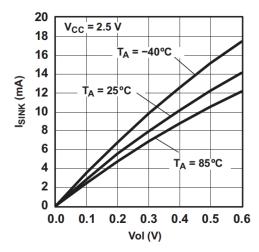

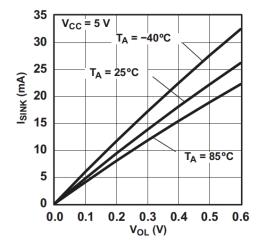

Figure 5. I/O Sink Current vs Output Low Voltage

Figure 2. Standby Supply Current vs Temperature

Figure 4. I/O Sink Current vs Output Low Voltage

Figure 6. I/O Sink Current vs Output Low Voltage

# Typical Characteristics(continued)

$T_A = 25$ °C (unless otherwise noted)

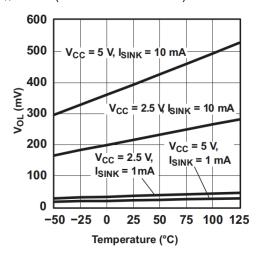

Figure 7. I/O Output Low Voltage vs Temperature

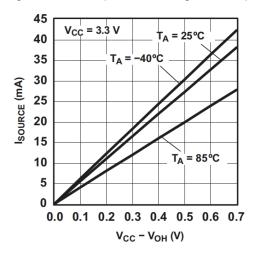

Figure 9. I/O Source Current vs Output High Voltage

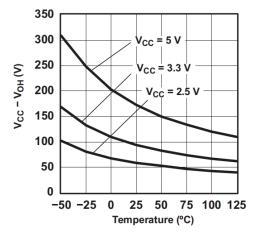

Figure 11. I/O High Voltage vs Temperature

Figure 8. I/O Source Current vs Output High Voltage

Figure 10. I/O Source Current vs Output High Voltage

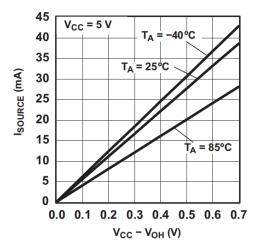

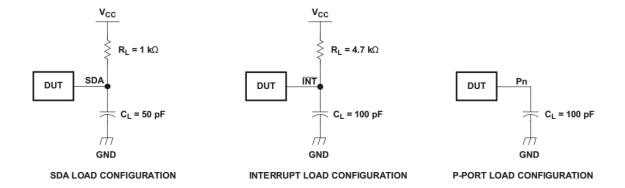

### **Parameter Measurement Information**

#### **SDA LOAD CONFIGURATION**

#### **VOLTAGE WAVEFORMS**

| BYTE | DESCRIPTION              |

|------|--------------------------|

| 1    | I <sup>2</sup> C address |

| 2, 3 | P-port data              |

Figure 12. I<sup>2</sup>C Interface Load Circuit and Voltage Waveforms

# **Parameter Measurement Information**(continued)

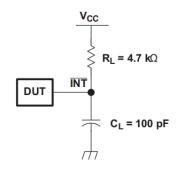

#### INTERRUPT LOAD CONFIGURATION

Figure 13. Interrupt Load Circuit and Voltage Waveforms

# **Parameter Measurement Information**(continued)

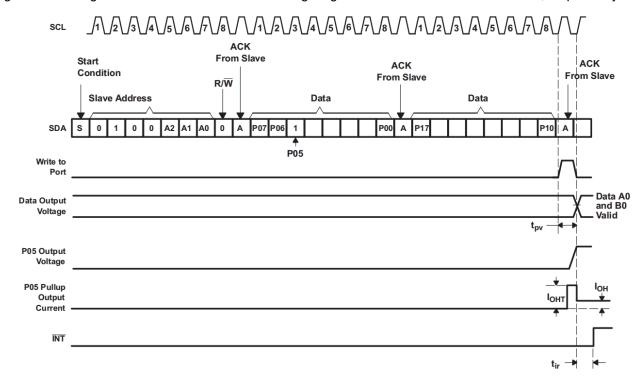

Write-Mode Timing  $(R/\overline{W} = 0)$

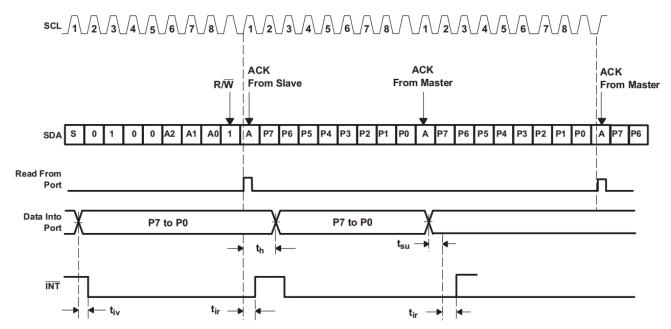

Figure 14. P-Port Load Circuits and Voltage Waveforms

### **Detailed Description**

#### Overview

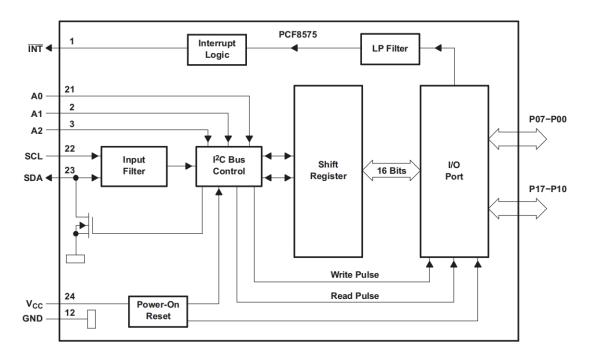

The PCF8575 provides general-purpose remote I/O expansion for most micro controller families via the I 2C interface serial clock (SCL) and serial data (SDA).

The device features a 16-bit quasi-bidirectional input/output (I/O) port (P07–P00, P17–P10), including latched outputs with high-current drive capability for directly driving LEDs. Each quasi-bidirectional I/O can be used as an input or output without the use of a data-direction control signal. At power on, the I/Os are high. In this mode, only a current source (IOH) to VCC is active. An additional strong pullup to VCC (IOHT) allows fast-rising edges into heavily loaded outputs. This device turns on when an output is written high and is switched off by the negative edge of SCL. The I/Os should be high before being used as inputs. After power on, as all the I/Os are set high, all of them can be used as inputs. Any change in setting of the I/Os as either input or outputs can be done with the write mode. If a high is applied externally to an I/O that has been written earlier to low, a large current (IOL) will flow to GND.

The PCF8575 provides an open-drain interrupt (INT) output, which can be connected to the interrupt input of a micro controller. An interrupt is generated by any rising or falling edge of the port inputs in the input mode. After time, tiv, the signal INT is valid. Resetting and reactivating the interrupt circuit is achieved when data on the port is changed to the original setting, or data is read from or written to the port that generated the interrupt. Resetting occurs in the read mode at the acknowledge (ACK) bit after the rising edge of the SCL signal or in the write mode at the ACK bit after the falling edge of the SCL signal. Interrupts that occur during the ACK clock pulse can be lost (or be very short), due to the resetting of the interrupt during this pulse. Each change of the I/Os after resetting is detected and is transmitted as INT. Reading from or writing to another device does not affect the interrupt circuit. This device does not have internal configuration or status registers. Instead, read or write to the device I/Os directly after sending the device address (see Figure 18 and Figure 19).

By sending an interrupt signal on this line, the remote I/O can inform the micro controller if there is incoming data on its ports, without having to communicate via the I 2C bus. Thus, the PCF8575 can remain a simple slave device.

Every data transmission to or from the PCF8575 must consist of an even number of bytes. The first data byte in every pair refers to port 0 (P07–P00), and the second data byte in every pair refers to port 1 (P17–P10). To write to the ports (output mode), the master first addresses the slave device, setting the last bit of the byte containing the slave address to logic 0. The PCF8575 acknowledges, and the master sends the first data byte for P07–P00.

After the first data byte is acknowledged by the PCF8575, the second data byte (P17-P10) is sent by the master.

Once again, the PCF8575 acknowledges the receipt of the data, after which this 16-bit data is presented on the port lines.

The number of data bytes that can be sent successively is not limited. After every two bytes, the previous data is overwritten. When the PCF8575 receives the pairs of data bytes, the first byte is referred to as P07–P00 and the second byte as P17–P10. The third byte is referred to as P07–P00, the fourth byte as P17–P10, and so on. Before reading from the PCF8575, all ports desired as input should be set to logic 1. To read from the ports (input mode), the master first addresses the slave device, setting the last bit of the byte containing the slave address to logic 1. The data bytes that follow on the SDA are the values on the ports. If the data on the input port changes faster than the master can read, this data may be lost.

When power is applied to VCC, an internal power-on reset holds the PCF8575 in a reset state until VCC has reached VPOR. At that time, the reset condition is released, and the device I 2C-bus state machine initializes the bus to its default state.

The hardware pins (A0, A1, and A2) are used to program and vary the fixed I 2C address and allow up to eight devices to share the same I 2C bus or SMBus. The fixed I 2C address of the PCF8575 is the same as the PCF8575C, PCF8574, PCA9535, and PCA9555, allowing up to eight of these devices, in any combination, to share the same I 2C bus or SMBus.

# **Functional Block Diagram**

# **Logic Diagram (Positive Logic)**

### Simplified Schematic Diagram of Each P-Port Input/Output

### **Feature Description**

#### I<sup>2</sup>C Interface

The bidirectional I<sup>2</sup>C bus consists of the serial clock (SCL) and serial data (SDA) lines. Both lines must be connected to a positive supply via a pullup resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

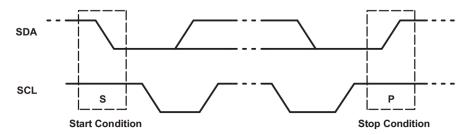

I<sup>2</sup>C communication with this device is initiated by a master sending a Start condition, a high-to-low transition on the SDA input/output while the SCL input is high (see Figure 15). After the Start condition, the device address byte is sent, most significant bit (MSB) first, including the data direction bit (R/W). This device does not respond to the general call address. After receiving the valid address byte, this device responds with an ACK, a low on the SDA input/output during the high of the ACK-related clock pulse. The address inputs (A2–A0) of the slave device must not be changed between the Start and Stop conditions.

The data byte follows the address ACK. If the R/W bit is high, the data from this device are the values read from the P port. If the R/W bit is low, the data are from the master, to be output to the P port. The data byte is followed by an ACK sent from this device. If other data bytes are sent from the master, following the ACK, they are ignored by this device. Data are output only if complete bytes are received and acknowledged. The output data is valid at time (tpv) after the low-to-high transition of SCL, during the clock cycle for the ACK.

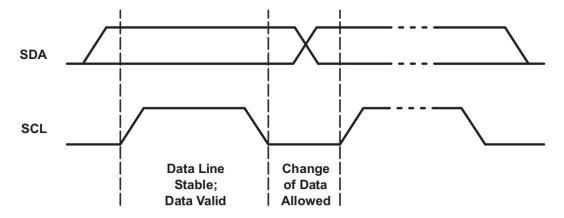

On the I 2C bus, only one data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the high pulse of the clock period, as changes in the data line at this time are interpreted as control commands (Start or Stop) (see Figure 16).

A Stop condition, a low-to-high transition on the SDA input/output while the SCL input is high, is sent by the master (see Figure 15).

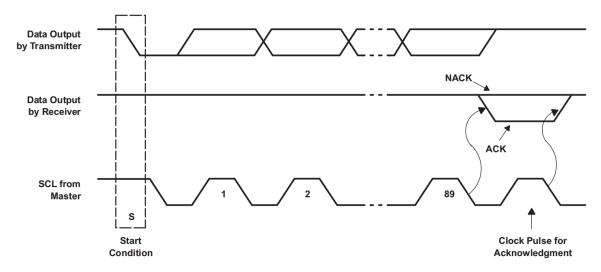

The number of data bytes transferred between the Start and Stop conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one ACK bit. The transmitter must release the SDA line before the receiver can send an ACK bit.

A slave receiver that is addressed must generate an ACK after the reception of each byte. Also, a master must generate an ACK after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the ACK clock pulse so that the SDA line is stable low during the high pulse of the ACK-related clock period (see Figure 17). Setup and hold times must be taken into account.

A master receiver must signal an end of data to the transmitter by not generating an acknowledge (NACK) after the last byte that has been clocked out of the slave. This is done by the master receiver by holding the SDA line high. In this event, the transmitter must release the data line to enable the master to generate a Stop condition.

Figure 15. Definition of Start and Stop Conditions

# **Feature Description (continued)**

Figure 16. Bit Transfer

Figure 17. Acknowledgment on I<sup>2</sup>C Bus

#### **Interface Definition**

| BYTE                           | BIT     |     |     |     |     |     |     |         |  |

|--------------------------------|---------|-----|-----|-----|-----|-----|-----|---------|--|

| DIIE                           | 7 (MSB) | 6   | 5   | 4   | 3   | 2   | 1   | 0 (LSB) |  |

| I <sup>2</sup> C slave address | L       | Н   | L   | L   | A2  | A1  | A0  | R/W     |  |

| P0x I/O data bus               | P07     | P06 | P05 | P04 | P03 | P02 | P01 | P00     |  |

| P1x I/O data bus               | P17     | P16 | P15 | P14 | P13 | P12 | P11 | P10     |  |

### **Address Reference**

| INPUTS |            |    | ISC DUC CLAVE O DIT DEAD ADDRESS | I2C BUS SLAVE 8- BIT WRITE     |

|--------|------------|----|----------------------------------|--------------------------------|

| A2     | <b>A</b> 1 | A0 | 12C BUS SLAVE 8-BIT READ ADDRESS | ADDRESS                        |

| L      | L          | L  | 65 (decimal), 41 (hexadecimal)   | 64 (decimal), 40 (hexadecimal) |

| L      | L          | Н  | 67 (decimal), 43 (hexadecimal)   | 66 (decimal), 42 (hexadecimal) |

| L      | Н          | L  | 69 (decimal), 45 (hexadecimal)   | 68 (decimal), 44 (hexadecimal) |

| L      | Н          | Н  | 71 (decimal), 47 (hexadecimal)   | 70 (decimal), 46 (hexadecimal) |

| Н      | L          | L  | 73 (decimal), 49 (hexadecimal)   | 72 (decimal), 48 (hexadecimal) |

| Н      | L          | Н  | 75 (decimal), 4B (hexadecimal)   | 74 (decimal), 4A (hexadecimal) |

| Н      | Н          | L  | 77 (decimal), 4D (hexadecimal)   | 76 (decimal), 4C (hexadecimal) |

| Н      | Н          | Н  | 79 (decimal), 4F (hexadecimal)   | 78 (decimal), 4E (hexadecimal) |

### **Device Functional Modes**

Figure 18 and Figure 19 show the address and timing diagrams for the write and read modes, respectively.

Figure 18. Write Mode (Output)

# **Device Functional Modes** (continued)

Figure 19. Read Mode (Input)

# **Typical Application**

The SCL and SDA pins must be tied directly to VCC because if SCL and SDA are tied to an auxiliary power supply that could be powered on while VCC is powered off, then the supply current, ICC, will increase as a result.

- A. Device address is configured as 0100000 for this example.

- B. P0, P2, and P3 are configured as outputs.

- C. P1, P4, and P5 are configured as inputs.

- D. P6 and P7 are not used and must be configured as outputs.

Figure 20. Application Schematic

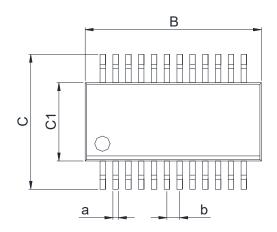

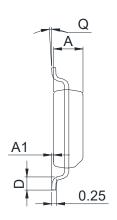

# **Physical Dimensions**

SSOP-24(QSOP-24)

| Dimensions In Millimeters(SSOP-24)(QSOP-24) |      |      |      |      |      |      |    |      |      |  |

|---------------------------------------------|------|------|------|------|------|------|----|------|------|--|

| Symbol:                                     | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b    |  |

| Min:                                        | 1.30 | 0.10 | 8.55 | 5.80 | 3.80 | 0.50 | 0° | 0.23 | 0.63 |  |

| Max:                                        | 1.50 | 0.25 | 8.75 | 6.20 | 4.00 | 0.80 | 8° | 0.31 | TYP  |  |

# **Revision History**

| DATE      | REVISION                  | PAGE |

|-----------|---------------------------|------|

| 2013-3-5  | New                       | 1-22 |

| 2023-7-24 | Update encapsulation type | 1    |

| 2024-11-7 | Update Lead Temperature   | 4    |

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: Select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields. All problems, responsibilities and losses arising from the user's use beyond the applicable area of the product shall be borne by the user and have nothing to do with Huaguan Semiconductor, and the user shall not claim any compensation liability against Huaguan Semiconductor by the terms of this Agreement.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.