#### ACPL-071L and ACPL-074L

# Single-Channel and Dual-Channel High-Speed 15-MBd CMOS Optocoupler

#### **Description**

The Broadcom<sup>®</sup> ACPL-071L (single-channel) and ACPL-074L (dual-channel) are 15-MBd CMOS optocouplers in SOIC-8 package. The optocouplers use the latest CMOS IC technology to achieve outstanding performance with very low power consumption. Basic building blocks of ACPL-071L and ACPL-074L are high speed LEDs and CMOS detector ICs. Each detector incorporates an integrated photodiode, a high-speed transimpedance amplifier, and a voltage comparator with an output driver.

#### **Applications**

- Digital field bus isolation:

- CANBus, RS485, USB

- Multiplexed data transmission

- Computer peripheral interface

- Microprocessor system interface

- DC/DC converter

#### **Features**

- +3.3V and +5 V CMOS compatibility

- 30 ns max. pulse width distortion

- 40 ns max. propagation delay (3.3V supply voltage)

- 30 ns max. propagation delay skew

- High speed: 15 MBd min.

- 10 kV/µs minimum common mode rejection

- -40°C to 105°C temperature range

- Safety and regulatory approvals:

- UL recognized: 3750 V rms for 1 min. per UL 1577

- CSA component acceptance Notice #5

- IEC/EN/DIN EN 60747-5-5

**CAUTION!** It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD. The components featured in this data sheet are not to be used in military or aerospace applications or environments.

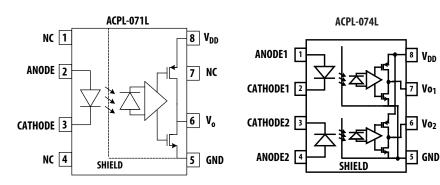

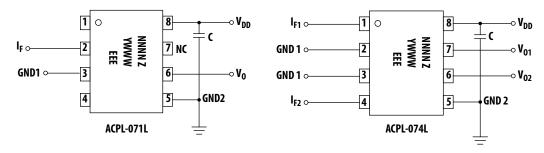

## **Functional Diagram**

NOTE: A 0.1-µF bypass capacitor must be connected as close as possible between pins VDD and GND.

| Truth Table                 |   |  |  |  |  |  |  |

|-----------------------------|---|--|--|--|--|--|--|

| LED V <sub>O</sub> , OUTPUT |   |  |  |  |  |  |  |

| OFF                         | Н |  |  |  |  |  |  |

| ON                          | L |  |  |  |  |  |  |

## **Ordering Information**

ACPL-071L/074L are UL Recognized with 3750 Vrms for 1 minute per UL1577.

|             | Option         |         |               |               | IEC/EN/DIN EN |               |

|-------------|----------------|---------|---------------|---------------|---------------|---------------|

| Part Number | RoHS Compliant | Package | Surface Mount | Tape and Reel | 60747-5-5     | Quantity      |

| ACPL-071L   | -000E          | SO-8    | X             |               |               | 100 per tube  |

|             | -500E          |         | X             | Х             |               | 1500 per reel |

|             | -060E          |         | Х             |               | X             | 100 per tube  |

|             | -560E          |         | X             | Х             | X             | 1500 per reel |

| ACPL-074L   | -000E          | SO-8    | X             |               |               | 100 per tube  |

|             | -500E          |         | X             | X             |               | 1500 per reel |

|             | -060E          |         | X             |               | X             | 100 per tube  |

|             | -560E          |         | X             | Х             | X             | 1500 per reel |

To order, choose a part number from the part number column and combine with the desired option from the option column to form an order entry.

#### Example 1:

ACPL-071L-500E to order product of Small Outline SO-8 package in Tape and Reel packaging in RoHS compliant.

#### Example 2:

ACPL-074L-000E to order product of Small Outline SO-8 package in tube packaging and RoHS compliant.

Option data sheets are available. Contact your Broadcom sales representative or authorized distributor for information.

## **Reflow Soldering Profile**

Recommended reflow condition as per JEDEC Standard, J-STD-020 (latest revision). Non-halide flux should be used.

## **Regulatory Information**

The ACPL-071L and ACPL-074L have been approved by the following organizations:

| UL                      | Recognized under UL 1577, component recognition program, File E55361. |

|-------------------------|-----------------------------------------------------------------------|

| CSA                     | Approved under CSA Component Acceptance Notice #5, File CA88324.      |

| IEC/EN/DIN EN 60747-5-5 |                                                                       |

AV02-0963EN Broadcom

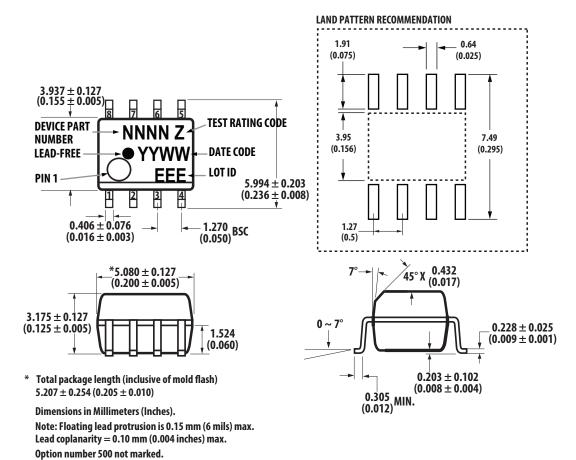

## **Package Dimensions**

ACPL-071L and ACPL-074L (Small Outline S0-8 Package)

# **Insulation and Safety Related Specifications**

| Parameter                                         | Symbol | Value | Units | Conditions                                                                                    |

|---------------------------------------------------|--------|-------|-------|-----------------------------------------------------------------------------------------------|

| Minimum External Air Gap (Clearance)              | L(I01) | 4.9   | mm    | Measured from input terminals to output terminals, shortest distance through air.             |

| Minimum External Tracking (Creepage)              | L(I02) | 4.8   | mm    | Measured from input terminals to output terminals, shortest distance path along body.         |

| Minimum Internal Plastic Gap (Internal Clearance) |        | 0.08  | mm    | Insulation thickness between emitter and detector; also known as distance through insulation. |

| Tracking Resistance (Comparative Tracking Index)  | СТІ    | 175   | Volts | DIN IEC 112/VDE 0303 Part 1                                                                   |

| Isolation Group                                   |        | Illa  |       | Material Group (DIN VDE 0110, 1/89, Table 1)                                                  |

#### **IEC/EN/DIN EN 60747-5-5 Insulation Characteristics**

| Description                                                                                        | Symbol                 | Option 060        | Unit  |

|----------------------------------------------------------------------------------------------------|------------------------|-------------------|-------|

| Installation classification per DIN VDE 0110, Table 1                                              |                        |                   |       |

| for rated mains voltage ≤ 150 Vrms                                                                 |                        | I – IV            |       |

| for rated mains voltage ≤ 300 Vrms                                                                 |                        | I – IV            |       |

| for rated mains voltage ≤ 600 Vrms                                                                 |                        | I – III           |       |

| Climatic Classification                                                                            |                        | 40/85/21          |       |

| Pollution Degree (DIN VDE 0110/39)                                                                 |                        | 2                 |       |

| Maximum Working Insulation Voltage                                                                 | $V_{IORM}$             | 567               | Vpeak |

| Input to Output Test Voltage, Method b                                                             | $V_{PR}$               | 1063              | Vpeak |

| $V_{IORM} \times 1.875 = V_{PR}$ , 100% Production Test with $t_m = 1s$ , Partial discharge < 5 pC |                        |                   |       |

| Input to Output Test Voltage, Method a                                                             | $V_{PR}$               | 907               | Vpeak |

| $V_{IORM} \times 1.6 = V_{PR}$ , Type and Sample Test, $t_{m}$ =10s, Partial discharge < 5 pC      |                        |                   |       |

| Highest Allowable Overvoltage (Transient Overvoltage t <sub>ini</sub> = 60s)                       | V <sub>IOTM</sub>      | 6000              | Vpeak |

| Safety-limiting values – maximum values allowed in the event of a failure.                         |                        |                   |       |

| Case Temperature                                                                                   | $T_S$                  | 150               | °C    |

| Input Current                                                                                      | I <sub>S, INPUT</sub>  | 150               | mA    |

| Output Power                                                                                       | P <sub>S, OUTPUT</sub> | 600               | mW    |

| Insulation Resistance at T <sub>S</sub> , VIO = 500 V                                              | R <sub>S</sub>         | ≥ 10 <sup>9</sup> | Ω     |

**NOTE:** These optocouplers are suitable for safe electrical isolation only within the safety limit data. Maintenance of the safety data shall be ensured by means of protective circuits.

## **Absolute Maximum Ratings**

| Parameter                         | Symbol                                     | Min.        | Max.                 | Units |  |  |

|-----------------------------------|--------------------------------------------|-------------|----------------------|-------|--|--|

| Storage Temperature               | T <sub>S</sub>                             | <b>–</b> 55 | +125                 | °C    |  |  |

| Ambient Operating Temperature     | T <sub>A</sub>                             | -40         | +105                 | °C    |  |  |

| Supply Voltages                   | V <sub>DD</sub>                            | 0           | 6.0                  | Volts |  |  |

| Output Voltage                    | Vo                                         | -0.5        | V <sub>DD</sub> +0.5 | Volts |  |  |

| Average Forward Input Current     | I <sub>F</sub>                             | _           | 20.0                 | mA    |  |  |

| Average Output Current            | Io                                         | _           | 10.0                 | mA    |  |  |

| Input Power Dissipation           | P <sub>I</sub>                             | _           | 35                   | mW    |  |  |

| Output Power Dissipation          | P <sub>O</sub>                             | _           | 100                  | mW    |  |  |

| Lead Solder Temperature           | 260°C for 10s., 1.6 mm below seating plane |             |                      |       |  |  |

| Solder Reflow Temperature Profile | See Reflow Soldering Profile               |             |                      |       |  |  |

## **Recommended Operating Conditions**

| Parameter                             | Symbol          | Min. | Max. | Units |

|---------------------------------------|-----------------|------|------|-------|

| Ambient Operating Temperature         | T <sub>A</sub>  | -40  | +105 | °C    |

| Supply Voltages                       | V <sub>DD</sub> | 4.5  | 5.5  | V     |

|                                       |                 | 3.0  | 3.6  | V     |

| Input Current (ON)                    | I <sub>F</sub>  | 12   | 18   | mA    |

| Supply Voltage Slew Rate <sup>a</sup> | S <sub>R</sub>  | 0.5  | 500  | V/ms  |

a. Slew rate of supply voltage ramping is recommended to ensure no glitch more than 1V to appear at the output pin.

## **Electrical Specifications**

Over recommended temperature (T<sub>A</sub> =  $-40^{\circ}$ C to  $+105^{\circ}$ C), 3.0V  $\leq$  V<sub>DD</sub>  $\leq$  3.6V and 4.5V  $\leq$  V<sub>DD</sub>  $\leq$  5.5V.

All typical specifications are at  $T_A$  = +25°C,  $V_{DD}$  = +3.3V.

| Parameter                       | Symbol           | Part<br>Number | Min.                | Тур.                  | Max. | Units | Test Conditions                                                        |

|---------------------------------|------------------|----------------|---------------------|-----------------------|------|-------|------------------------------------------------------------------------|

| Input Forward Voltage           | V <sub>F</sub>   |                | 1.3                 | 1.5                   | 1.8  | V     | I <sub>F</sub> = 14 mA                                                 |

| Input Reverse Breakdown Voltage | BV <sub>R</sub>  |                | 5.0                 | _                     | _    | V     | I <sub>R</sub> = 10 μA                                                 |

| Logic High Output Voltage       | V <sub>OH</sub>  |                | V <sub>DD</sub> – 1 | V <sub>DD</sub> – 0.3 | _    | V     | $I_F = 0$ , $I_O = -4$ mA, $V_{DD} = 3.3V$                             |

|                                 |                  |                | V <sub>DD</sub> – 1 | V <sub>DD</sub> – 0.2 | _    | V     | $I_F = 0$ , $I_O = -4$ mA, $V_{DD} = 5V$                               |

| Logic Low Output Voltage        | V <sub>OL</sub>  |                | _                   | 0.35                  | 0.8  | V     | I <sub>F</sub> = 14 mA, I <sub>O</sub> = 4 m A, V <sub>DD</sub> = 3.3V |

|                                 |                  |                | _                   | 0.2                   | 0.8  | V     | I <sub>F</sub> = 14 mA, I <sub>O</sub> = 4 mA, V <sub>DD</sub> = 5V    |

| Input Threshold Current         | I <sub>TH</sub>  |                | _                   | 4.5                   | 8.8  | mA    | I <sub>OL</sub> = 20 μA                                                |

| Logic Low Output Supply Current | I <sub>DDL</sub> | ACPL-071L      | _                   | 4.1                   | 6.0  | mA    | I <sub>F</sub> = 14 mA                                                 |

|                                 |                  | ACPL-074L      | _                   | 8.3                   | 12.0 | mA    | I <sub>F</sub> = 14 mA                                                 |

| Logic Low Output Supply Current | I <sub>DDH</sub> | ACPL-071L      | _                   | 3.8                   | 6.0  | mA    | I <sub>F</sub> = 0                                                     |

|                                 |                  | ACPL-074L      | _                   | 7.6                   | 12.0 | mA    | I <sub>F</sub> = 0                                                     |

## **Switching Specifications**

Over recommended temperature (T<sub>A</sub> = -40°C to +105°C), 3.0V  $\leq$  V<sub>DD</sub>  $\leq$  3.6V and 4.5V  $\leq$  V<sub>DD</sub>  $\leq$  5.5V.

All typical specifications are at  $T_A$  = +25°C,  $V_{DD}$  = +3.3V.

| Parameter                                                        | Symbol           | Min. | Тур. | Max. | Units | Test Conditions                                                                               |

|------------------------------------------------------------------|------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------|

| Propagation Delay Time to Logic<br>Low Output <sup>a</sup>       | t <sub>PHL</sub> | _    | 29   | 40   | ns    | I <sub>F</sub> = 14 mA, C <sub>L</sub> = 15 pF, V <sub>DD</sub> = 3.3V,<br>CMOS Signal Levels |

|                                                                  |                  | 1    | _    | 50   | ns    | $I_F$ = 14 mA, $C_L$ = 15 pF, $V_{DD}$ = 5V, CMOS Signal Levels                               |

| Propagation Delay Time to Logic High Output <sup>a</sup>         | t <sub>PLH</sub> | _    | 22   | 40   | ns    | $I_F$ = 14 mA, $C_L$ = 15 pF, $V_{DD}$ = 3.3V, CMOS Signal Levels                             |

|                                                                  |                  | _    | _    | 50   | ns    | I <sub>F</sub> = 14 mA, C <sub>L</sub> = 15 pF, V <sub>DD</sub> = 5V,<br>CMOS Signal Levels   |

| Pulse Width                                                      | $t_{PW}$         | 66.7 | _    | _    | ns    |                                                                                               |

| Pulse Width Distortion <sup>b</sup>                              | PWD              | 0    | 7    | 25   | ns    | I <sub>F</sub> = 14 mA, C <sub>L</sub> = 15 pF, V <sub>DD</sub> = 3.3V,<br>CMOS Signal Levels |

|                                                                  |                  | _    | _    | 30   | ns    | I <sub>F</sub> = 14 mA, C <sub>L</sub> = 15 pF, V <sub>DD</sub> = 5V,<br>CMOS Signal Levels   |

| Propagation Delay Skew <sup>c</sup>                              | t <sub>PSK</sub> |      | _    | 30   | ns    | $I_F$ = 14 mA, $C_L$ = 15 pF, CMOS Signal Levels                                              |

| Output Rise Time (10% – 90%)                                     | t <sub>R</sub>   | _    | 20   | _    | ns    | I <sub>F</sub> = 14 mA, C <sub>L</sub> = 15 pF, CMOS Signal Levels                            |

| Output Fall Time (90% - 10%)                                     | t <sub>F</sub>   | _    | 25   | _    | ns    | I <sub>F</sub> = 14 mA, C <sub>L</sub> = 15 pF, CMOS Signal Levels                            |

| Common Mode Transient Immunity at Logic High Output <sup>d</sup> | CM <sub>H</sub>  | 10   | 15   | _    | kV/µs | $V_{CM} = 1000 \text{ V}, T_A = 25^{\circ}\text{C}, I_F = 0 \text{ mA}$                       |

| Common Mode Transient Immunity at Logic Low Output <sup>e</sup>  | CM <sub>L</sub>  | 10   | 15   | _    | kV/µs | V <sub>CM</sub> = 1000 V, T <sub>A</sub> = 25°C, I <sub>F</sub> = 14 mA                       |

a. t<sub>PHL</sub> propagation delay is measured from the 50% level on the rising edge of the input pulse to the 50% level of the falling edge of the V<sub>O</sub> signal. tpLH propagation delay is measured from the 50% level on the falling edge of the input pulse to the 50% level of the rising edge of the V<sub>O</sub> signal.

- b. PWD is defined as  $|t_{PHL}-t_{PLH}|.$

- c. t<sub>PSK</sub> is equal to the magnitude of the worst case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that will be seen between units at any given temperature within the recommended operating conditions.

- d. CM<sub>H</sub> is the maximum tolerable rate of rise of the common mode voltage to assure that the output will remain in a high logic state.

- e. CM<sub>I</sub> is the maximum tolerable rate of fall of the common mode voltage to assure that the output will remain in a low logic state.

# **Package Characteristics**

All Typical at  $T_A = 25$ °C.

| Parameter                                | Symbol | Min. | Тур.             | Max. | Units | Test Conditions                                                   |

|------------------------------------------|--------|------|------------------|------|-------|-------------------------------------------------------------------|

| Input-Output Insulation                  | II-O   | _    | _                | 1.0  | μA    | 45% RH, t = 5s, V <sub>I-O</sub> = 3 kV DC, T <sub>A</sub> = 25°C |

| Input-Output Momentary Withstand Voltage | VISO   | 3750 | _                | _    | Vrms  | RH 50%, t = 1 min., T <sub>A</sub> = 25°C                         |

| Input-Output Resistance                  | R I-O  | _    | 10 <sup>12</sup> | _    | Ω     | V <sub>I-O</sub> = 500 V dc                                       |

| Input-Output Capacitance                 | C I-O  | _    | 0.6              | _    | pF    | f = 1 MHz, T <sub>A</sub> = 25°C                                  |

AV02-0963EN Broadcom

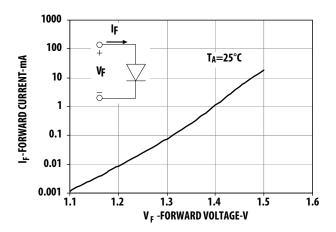

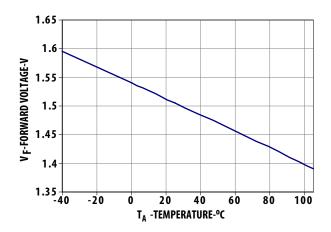

Figure 1: Typical Input Diode Forward Characteristic

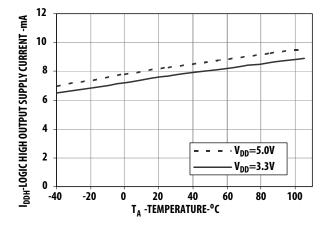

Figure 3: Typical Logic High O/P Supply Current vs. Temperature for ACPL-074L

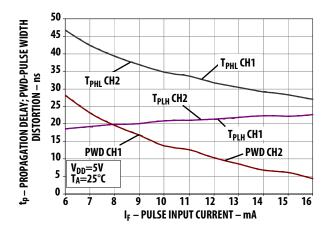

Figure 5: Typical Switching speed vs. Pulse Input Current at 5V Supply Voltage

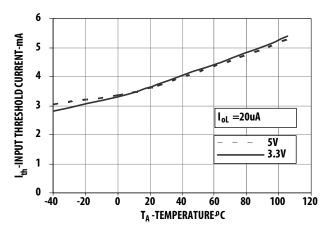

Figure 2: Typical Input Threshold Current vs. Temperature

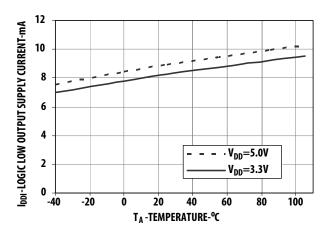

Figure 4: Typical Logic Low O/P Supply Current vs. Temperature for ACPL-074L

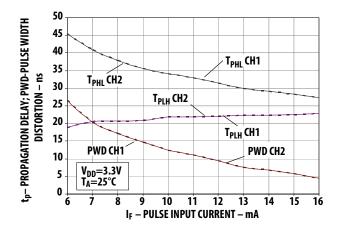

Figure 6: Typical Switching Speed vs. Pulse Input Current at 3.3V Supply Voltage

Figure 7: Typical V<sub>F</sub> vs. Temperature

#### **Application Information**

#### **Bypassing and PC Board Layout**

The ACPL-071L and ACPL-074L optocouplers are extremely easy to use. ACPL-071L and ACPL-074L provide CMOS logic output due to the high-speed CMOS IC technology used.

The external components required for proper operation are the input limiting resistor and the output bypass capacitor. Capacitor should be placed as close as possible to the optocoupler and values should be between 0.01  $\mu$ F and 0.1  $\mu$ F.

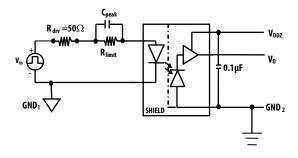

Figure 8: Recommended Printed Circuit Board Layout

#### **Powering Sequence**

V<sub>DD</sub> needs to achieve a minimum level of 3.0V before powering up the output connecting component.

## **Input Limiting Resistors**

ACPL-071L and ACPL-074L are direct current driven (Figure 8), and thus eliminate the need for input power supply. To limit the amount of current flowing through the LED, it is recommended that a 210 $\Omega$  resistor is connected in series with anode of LED (that is, Pin 2 for ACPL-071L and Pins 1 and 4 for ACPL-074L) at 5V input signal. At 3.3V input signal, it is recommended to connect a  $80\Omega$  resistor in series with anode of LED.

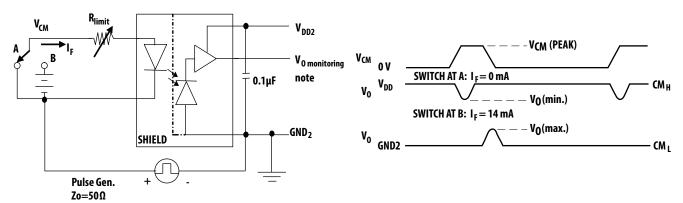

The recommended limiting resistors are based on the assumption that the driver output impedence is 50 (as shown in Figure 9).

Figure 9: Connection of Peaking capacitor (Cpeak) in Parallel of the Input Limiting Resistor (Rllimit) to Improve Speed Performance

#### **Speed Improvement**

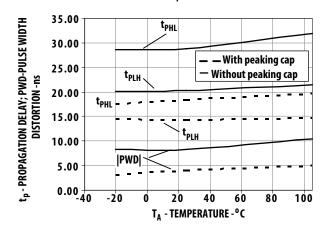

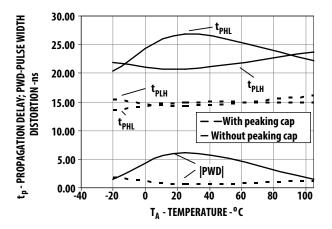

A peaking capacitor can be placed across the input current limit resistor (Figure 9) to achieve enhanced speed performance. The value of the peaking cap is dependent to the rise and fall time of the input signal and supply voltages and LED input driving current (If). Figure 10 shows significant improvement of propagation delay and pulse with distortion with added peak capacitor at driving current of 14 mA and 3.3V or 5V power supply.

Figure 10: Improvement of tp and PWD with Added 100 pF Peaking Capacitor in Parallel of Input Limiting Resistor

Figure 11: Test circuit for Common Mode Transient Immunity and Typical Waveforms.  $R_{total}$  is the total resistance of the driver output impedence (which is assumed to be  $50\Omega$ ) and the limiting resistor ( $R_{total} = R_{drv} + R_{limit}$ ).

Broadcom, the pulse logo, Connecting everything, Avago Technologies, Avago, and the A logo are among the trademarks of Broadcom and/or its affiliates in the United States, certain other countries, and/or the EU.

Copyright © 2014–2018 Broadcom. All Rights Reserved.

The term "Broadcom" refers to Broadcom Inc. and/or its subsidiaries. For more information, please visit www.broadcom.com.

Broadcom reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design. Information furnished by Broadcom is believed to be accurate and reliable. However, Broadcom does not assume any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.