## 6G UHD-SDI/3G/HD/SD Adaptive Cable Equalizer

#### **Gennum Products**

#### **Key Features**

- Supports data rates from 125Mb/s to 6.25Gb/s

- SMPTE ST 2081 (proposed), SMPTE ST 424,

SMPTE ST 292, and SMPTE ST 259 compliant

- Automatic cable equalization

- Typical equalized length of Belden 1694A cable:

- 80m at 5.94Gb/s

- 210m at 2.97Gb/s

- 300m at 1.485Gb/s

- 500m at 270Mb/s

- Supports DVB-ASI at 270Mb/s

- Supports MADI at 125Mb/s

- Manual bypass control

- Programmable carrier detect with squelch threshold adjustment

- Automatic power-down on loss of signal

- Differential output supports DC-coupling from +1.2V to +3.3V CML logic

- Optional 6dB flat band gain on input

- Selectable output de-emphasis: 2dB, 6dB, and 8dB

- Standard EIA/JEDEC logic for control/status signals

- Single +3.3V power supply operation

- 180mW power consumption (35mW in sleep)

- Operating temperature range: -40°C to +85°C

- Small footprint QFN package (4mm x 4mm)

- Footprint compatible with the GS2974A, GS2974B, GS2984, GS2994, and GS3440

- Pb-free and RoHS compliant

#### **Applications**

- SMPTE ST 2081 (proposed), SMPTE ST 424,

SMPTE ST 292, and SMPTE ST 259 coaxial cable serial digital interfaces

- Serialized 8b/10b encoded video streams up to 6.25Gb/s

#### Description

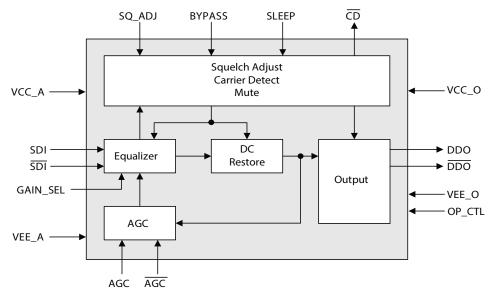

The GS6042 is a high-speed BiCMOS device designed to optimally equalize and restore signals received over  $75\Omega$  coaxial cable.

The device supports data rates up to 6.25Gb/s while being optimized for the proposed SMPTE ST 2081, as well as SMPTE ST 424, SMPTE ST 292, and SMPTE ST 259.

The GS6042 features DC restoration to compensate for the DC content of SMPTE pathological signals.

The Carrier Detect output pin  $\overline{(CD)}$  indicates whether an input signal has been detected. It can be connected directly to the SLEEP pin to enable automatic sleep on loss of input.

A CD threshold is set via the SQ\_ADJ pin, allowing the GS6042 to distinguish between small amplitude SDI signals and noise at the input of the device.

The equalizing and DC restore stages are disengaged and no equalization occurs when the BYPASS pin is HIGH. This is useful for signals launched at the signal source with low data rates and/or slow rise/fall times.

The GS6042 features a gain selection pin (GAIN\_SEL) which can be used to compensate for 6dB flat attenuation prior to the input of the device.

The differential output can be DC-coupled to Semtech's reclockers and cable drivers, as well as industry-standard CML logic by changing the voltage applied to the VCC\_O pin. In general, DC-coupling to any termination voltage between +1.2V and +3.3V is supported.

The GS6042 also features programmable output de-emphasis with three user-selectable operating levels to support long PCB traces at the output of the device.

Power consumption of the GS6042 is typically 180mW when its output is DC-coupled at +1.2V.

The GS6042 is Pb-free, and the encapsulation compound does not contain halogenated flame retardant. This component and all homogeneous subcomponents are RoHS compliant.

**GS6042 Functional Block Diagram**

#### **Revision History**

| Version | ECO    | PCN | Date              | Changes and/or Modifications                                                                                              |

|---------|--------|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------|

| 4       | 027667 | _   | September<br>2015 | Added tape and reel options to Table 6-2: Ordering Information.                                                           |

| 3       | 019547 | _   | May 2014          | Corrected the values for the de-emphasis levels                                                                           |

| 2       | 017789 | _   | February 2014     | Converted to Final Data Sheet. Modified Section 4.3. Included reference to 6G SMPTE standard.                             |

| 1       | 016407 | _   | November 2013     | Converted to Final Data Sheet. Included information on 6.25G support. Updated Jitter characteristics. Updates throughout. |

| 0       | 012658 | _   | June 2013         | New document                                                                                                              |

#### **Contents**

| Key Features                                       | 1  |

|----------------------------------------------------|----|

| Applications                                       | 1  |

| Description                                        | 1  |

| Revision History                                   | 2  |

| 1. Pin Out                                         | 4  |

| 1.1 GS6042 Pin Assignment                          | 4  |

| 1.2 GS6042 Pin Descriptions                        | 4  |

| 2. Electrical Characteristics                      | 6  |

| 2.1 Absolute Maximum Ratings                       | 6  |

| 2.2 DC Electrical Characteristics                  | 6  |

| 2.3 AC Electrical Characteristics                  | 8  |

| 3. Input/Output Circuits                           | 10 |

| 4. Detailed Description                            | 11 |

| 4.1 Serial Digital Inputs                          | 11 |

| 4.2 Automatic (Adaptive) Cable Equalization        | 11 |

| 4.3 Differential Digital Data Output               | 11 |

| 4.4 Programmable Squelch Adjust (SQ_ADJ)           | 12 |

| 4.5 Carrier Detect, Sleep, and Auto-Sleep          | 13 |

| 4.6 GAIN_SEL                                       | 13 |

| 4.7 Adjustable Output Swing, De-emphasis, and Mute | 14 |

| 5. Applications Information                        | 16 |

| 5.1 High-Gain Adaptive Cable Equalizers            | 16 |

| 5.2 PCB Layout                                     | 16 |

| 5.3 Typical Application Circuit                    | 17 |

| 6. Package & Ordering Information                  | 18 |

| 6.1 Package Dimensions                             | 18 |

| 6.2 Packaging Data                                 | 18 |

| 6.3 Recommended PCB Footprint                      | 19 |

| 6.4 Marking Diagram                                | 19 |

| 6.5 Solder Reflow Profiles                         | 20 |

| 6.6 Ordering Information                           | 20 |

# 1. Pin Out

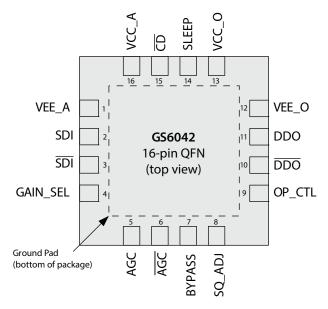

# 1.1 GS6042 Pin Assignment

Figure 1-1: GS6042 Pin Out

## 1.2 GS6042 Pin Descriptions

**Table 1-1: GS6042 Pin Descriptions**

| Pin Number | Name     | Туре  | Description                                                                                                                                                          |  |                                                                                                   |

|------------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---------------------------------------------------------------------------------------------------|

| 1          | VEE_A    | Power | Most negative power supply connection for the input buffer, core, and control circuits.                                                                              |  |                                                                                                   |

|            |          |       | Connect to ground.                                                                                                                                                   |  |                                                                                                   |

| 2, 3       | SDI, SDI | Input | Serial digital differential input.                                                                                                                                   |  |                                                                                                   |

|            |          |       | Flat Band Gain Control.                                                                                                                                              |  |                                                                                                   |

| 4          | GAIN_SEL | Input | Please refer to the DC Electrical Characteristics table for logic level threshold and compatibility. This pin is a $+2.5V$ input that is tolerant to $+3.3V$ levels. |  |                                                                                                   |

|            |          |       |                                                                                                                                                                      |  | When HIGH, the device compensates for an additional 6dB of loss across the entire operating band. |

|            |          |       | This pin has an internal pull-down resistor.                                                                                                                         |  |                                                                                                   |

| 5, 6       | AGC, AGC | _     | External AGC capacitor connection.                                                                                                                                   |  |                                                                                                   |

|            |          |       | EQ Bypass Control.                                                                                                                                                   |  |                                                                                                   |

| 7          | BYPASS   | Input | Please refer to the DC Electrical Characteristics table for logic level threshold and compatibility. This pin is a $+2.5V$ input that is tolerant to $+3.3V$ levels. |  |                                                                                                   |

|            |          | -     | Forces the equalizer and DC-restore stages into Bypass mode when HIGH. No equalization occurs in this mode.                                                          |  |                                                                                                   |

|            |          |       | This pin has an internal pull-down resistor.                                                                                                                         |  |                                                                                                   |

**Table 1-1: GS6042 Pin Descriptions (Continued)**

| Pin Number | Name          | Туре   | Description                                                                                                                                                                                                                                                                                                       |

|------------|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |               |        | Squelch Threshold Adjust.                                                                                                                                                                                                                                                                                         |

| 8          | SQ_ADJ        | Input  | Adjusts the input signal amplitude threshold of the carrier detect function. The serial data output of the device can be muted when the serial data input signal amplitude is too low by connecting the $\overline{\text{CD}}$ and OP_CTL pins using a suitable resistor network (see Figure 4-4 and Figure 4-5). |

|            |               |        | This pin has an internal pull-down resistor.                                                                                                                                                                                                                                                                      |

|            |               |        | <b>Note:</b> The SQ_ADJ function is only available when the device is not configured for auto-sleep mode. Reference Section 4.5 for more detail.                                                                                                                                                                  |

|            |               |        | Output Swing, De-emphasis and Mute Control.                                                                                                                                                                                                                                                                       |

|            |               |        | When this pin is connected to GND, the output swing is $850 \mathrm{mV}_{\mathrm{ppd}}$                                                                                                                                                                                                                           |

|            |               |        | with no de-emphasis applied to the output signal.                                                                                                                                                                                                                                                                 |

| 9          | OP_CTL        | Input  | With this pin connected to +2.5V, the output is muted.                                                                                                                                                                                                                                                            |

|            |               |        | Intermediate voltages and functions are shown in Table 4-5. These voltages can be achieved as shown in Figure 4-4 and Figure 4-5.                                                                                                                                                                                 |

|            |               |        | This pin has an internal pull-down resistor.                                                                                                                                                                                                                                                                      |

| 10, 11     | DDO, DDO      | Output | Serial digital differential output.                                                                                                                                                                                                                                                                               |

| 12         | VEE_O         | Power  | Most negative power supply connection for the output buffer. Connect to ground.                                                                                                                                                                                                                                   |

| 12         | VCC 0         | Davier | Most positive power supply connection for the output buffer.                                                                                                                                                                                                                                                      |

| 13         | VCC_O         | Power  | Connect to 1.2V - 3.3V DC.                                                                                                                                                                                                                                                                                        |

|            |               |        | SLEEP Control.                                                                                                                                                                                                                                                                                                    |

|            |               |        | Please refer to the DC Electrical Characteristics table for logic level threshold and compatibility. This pin is a +2.5V input that is tolerant to +3.3V levels.                                                                                                                                                  |

|            |               |        | When HIGH the part is powered-down except for the Carrier Detect function.                                                                                                                                                                                                                                        |

| 14         | SLEEP         | Input  | This pin can be connected directly to the $\overline{\text{CD}}$ pin to automatically put the device to sleep (low-power operation) on loss of carrier.                                                                                                                                                           |

|            |               |        | This pin has an internal pull-down resistor.                                                                                                                                                                                                                                                                      |

|            |               |        | <b>Note:</b> When SLEEP is connected to $\overline{\text{CD}}$ for automatic power reduction on loss of carrier, the SQ_ADJ pin will not modify the $\overline{\text{CD}}$ threshold. The $\overline{\text{CD}}$ threshold will revert to the default value used when SQ_ADJ is pulled LOW.                       |

|            |               |        | Carrier Detect Status Output.                                                                                                                                                                                                                                                                                     |

| 15         | <del>CD</del> | Output | Please refer to the DC Electrical Characteristics table for logic level threshold and compatibility. This pin is a +2.5V output.                                                                                                                                                                                  |

| 13         | CD            | σαιραί | Indicates presence of an input signal. When the $\overline{\text{CD}}$ pin is LOW, a signal has been detected at the input. When this pin is HIGH, this indicates loss of input signal.                                                                                                                           |

| 16         | VCC_A         | Power  | Most positive power supply connection for the input buffer, core and control circuits.  Connect to +3.3V DC.                                                                                                                                                                                                      |

|            | Center Pad    | Power  | Internally bonded to VEE_A.  Connect to GND with at least 5 vias.                                                                                                                                                                                                                                                 |

| -          |               |        |                                                                                                                                                                                                                                                                                                                   |

# 2. Electrical Characteristics

## 2.1 Absolute Maximum Ratings

**Table 2-1: Absolute Maximum Ratings**

| Parameter                                   | Value                             |

|---------------------------------------------|-----------------------------------|

| Supply Voltage - Core/Output Driver         | -0.5V to +3.6V DC                 |

| Input ESD Voltage (HBM)                     | 5kV                               |

| Storage Temperature Range (T <sub>s</sub> ) | -50°C to +125°C                   |

| Input Voltage Range (any input)             | -0.3 to (V <sub>CC_A</sub> +0.3)V |

| Operating Temperature Range                 | -40°C to +85°C                    |

| Solder Reflow Temperature                   | 260°C                             |

**Note:** Absolute Maximum Ratings are those values beyond which damage may occur. Functional operation outside of the ranges shown in the AC and DC Electrical Characteristics is not guaranteed.

#### 2.2 DC Electrical Characteristics

#### **Table 2-2: DC Electrical Characteristics**

$V_{CC\ A} = +3.3V \pm 5\%$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise shown.

| Parameter                      | Symbol      | Conditions | Min   | Тур | Max   | Units | Notes |

|--------------------------------|-------------|------------|-------|-----|-------|-------|-------|

| Supply Voltage - Core          | $V_{CC\_A}$ | _          | 3.135 | 3.3 | 3.465 | V     | _     |

|                                |             | _          | 1.14  | 1.2 | 1.26  | V     | 1     |

| Supply Voltage - Output Driver | $V_{CC\_O}$ | _          | 2.375 | 2.5 | 2.625 | V     | 1     |

|                                |             | _          | 3.135 | 3.3 | 3.465 | ٧     | 1     |

Rev.4

#### **Table 2-2: DC Electrical Characteristics (Continued)**

$V_{CC\_A}$  = +3.3V ±5%,  $T_A$  = -40°C to +85°C, unless otherwise shown.

| Parameter                         | Symbol              | Conditions                                                   | Min   | Тур          | Max | Units | Notes |

|-----------------------------------|---------------------|--------------------------------------------------------------|-------|--------------|-----|-------|-------|

|                                   |                     | $V_{CC\_O} = 1.2V$<br>$\Delta V_{DDO} = 425 \text{mV}_{ppd}$ | _     | 180          | _   | mW    | 2     |

|                                   |                     | $V_{CC\_O} = 1.2V$<br>$\Delta V_{DDO} = 850 \text{mV}_{ppd}$ | _     | 195          | _   | mW    | 2     |

|                                   |                     | $V_{CC\_O} = 2.5V$ $\Delta V_{DDO} = 425 \text{mV}_{ppd}$    | _     | 196          | _   | mW    | 2     |

| Power Consumption                 | $P_{D}$             | $V_{CC\_O} = 2.5V$ $\Delta V_{DDO} = 850 \text{mV}_{ppd}$    | _     | 221          | _   | mW    | 2     |

|                                   |                     | $V_{CC\_O} = 3.3V$<br>$\Delta V_{DDO} = 425 \text{mV}_{ppd}$ | _     | 202          | _   | mW    | 2     |

|                                   |                     | $V_{CC\_O} = 3.3V$ $\Delta V_{DDO} = 850 \text{mV}_{ppd}$    | _     | 240          | _   | mW    | 2     |

|                                   |                     | Sleep Mode<br>SLEEP = HIGH                                   | _     | 35           | _   | mW    | _     |

| Supply Current - Core             | I <sub>s</sub>      | _                                                            | _     | 55           | _   | mA    | 2,3   |

| Comple Compate Output Driver      |                     | $\Delta V_{DDO} = 850 \text{mV}_{ppd}$                       | _     | 20           | _   | mA    | 2     |

| Supply Current - Output Driver    | I <sub>Out</sub>    | $\Delta V_{DDO} = 425 \text{mV}_{ppd}$                       | _     | 10           | _   | mA    | 2     |

| Input Common Mode Voltage         | $V_{CMIN}$          | _                                                            | _     | 1.7          | _   | V     | _     |

| Output Common Mode Voltage        | V <sub>CMOUT</sub>  |                                                              | Refer | to Section 4 | 3   |       |       |

| CD Output Voltage<br>Logic Levels | V <sub>CD(OH)</sub> | Signal not present                                           | 2.0   | _            | _   | V     | _     |

|                                   | V <sub>CD(OL)</sub> | Signal present                                               | _     | _            | 0.4 | V     | _     |

| Input Voltage Logic Levels:       | V <sub>IH</sub>     | Minimum to assert                                            | 1.7   | _            | _   | V     | 4     |

| GAIN_SEL, BYPASS, SLEEP           | V <sub>IL</sub>     | Maximum to de-assert                                         | _     | _            | 0.7 | V     | 4     |

#### Notes:

- 1.  $V_{CC\_O}$  operates from +1.2V through +3.3V (+/-5%).

- 2. De-emphasis off.

- 3. An additional 3mA when de-emphasis is enabled.

Rev.4

September 2015

4. GAIN\_SEL, BYPASS, SLEEP pins are +2.5V, but +3.3V tolerant.

## 2.3 AC Electrical Characteristics

**Table 2-3: AC Electrical Characteristics**

$V_{CC\_A}$  = +3.3V ±5%,  $T_A$  = -40°C to +85°C, unless otherwise shown

| Parameter                       | Symbol            | Conditions                                              | Min | Тур  | Max  | Units             | Notes   |

|---------------------------------|-------------------|---------------------------------------------------------|-----|------|------|-------------------|---------|

| Serial input Data Rate          | DR <sub>DDO</sub> | _                                                       | 125 | _    | 6250 | Mb/s              | 1       |

| Input Voltage Swing             | $\Delta V_{SDI}$  | Differential,<br>270Mb/s and 1.485Gb/s                  | 720 | 800  | 950  | $mV_ppd$          | 2       |

| input voltage swing             | ∆. SDI            | Differential,<br>2.97Gb/s and 5.94Gb/s                  | 720 | 800  | 880  | ${\rm mV_{ppd}}$  | 2       |

| Output Voltage Swing            | $\Delta V_DDO$    | 100Ω differential load,<br>OP_CTL set for high<br>swing | 700 | 850  | 1000 | $mV_ppd$          | _       |

|                                 |                   | $100\Omega$ differential load, OP_CTL set for low swing | 350 | 425  | 500  | mV <sub>ppd</sub> | _       |

|                                 |                   | 6.25Gb/s<br>Belden 1694A: 0-50m                         | _   | 0.35 | _    | UI                | 4, 5    |

|                                 |                   | 5.94Gb/s<br>Belden 1694A: 0-80m                         | _   | 0.35 | 0.5  | UI                | 4, 5    |

|                                 |                   | 2.97Gb/s<br>Belden 1694A: 0-100m                        | _   | _    | 0.2  | UI                | 3, 4, 5 |

|                                 |                   | 2.97Gb/s<br>Belden 1694A: 100-150m                      | _   | _    | 0.3  | UI                | 3, 4, 5 |

|                                 |                   | 2.97Gb/s<br>Belden 1694A: 150-170m                      | _   | _    | 0.4  | UI                | 3, 4, 5 |

| Output Jitter at Various        |                   | 2.97Gb/s<br>Belden 1694A: 170-200m                      | _   | _    | 0.5  | UI                | 3, 4, 5 |

| Cable Lengths and Data<br>Rates |                   | 2.97Gb/s<br>Belden 1694A: 210m                          | _   | 0.5  |      | UI                | 4, 5    |

|                                 |                   | 1.485Gb/s<br>Belden 1694A: 0-200m                       | _   |      | 0.2  | UI                | 3, 4, 5 |

|                                 |                   | 1.485Gb/s<br>Belden 1694A: 200-260m                     | _   | _    | 0.3  | UI                | 3, 4, 5 |

|                                 |                   | 1.485Gb/s<br>Belden 1694A: 260-300m                     | _   | 0.3  | _    | UI                | 4, 5    |

|                                 |                   | 270Mb/s<br>Belden 1694A: 0-300m                         | _   | 0.1  | 0.15 | UI                | 3, 4, 5 |

|                                 |                   | 270Mb/s<br>Belden 1694A: 300-500m                       | _   | _    | 0.25 | UI                | 3, 4, 5 |

#### **Table 2-3: AC Electrical Characteristics (Continued)**

$V_{CC\_A}$  = +3.3V ±5%,  $T_A$  = -40°C to +85°C, unless otherwise shown

| Parameter                  | Symbol                          | Conditions                                        | Min | Тур | Max | Units | Notes |

|----------------------------|---------------------------------|---------------------------------------------------|-----|-----|-----|-------|-------|

| Output Rise/Fall time      | t <sub>r</sub> , t <sub>f</sub> | 5.94Gb/s, 2.97Gb/s, and<br>1.485Gb/s<br>20% - 80% | _   | 75  | _   | ps    | _     |

|                            |                                 | 270Mb/s<br>20% - 80%                              | _   | 150 | _   | ps    | _     |

| Mismatch in Rise/Fall time | $\Delta t_{r'} \Delta t_{f}$    | _                                                 | _   | _   | 30  | ps    | _     |

| Duty Cycle Distortion      |                                 | _                                                 | _   | _   | 30  | ps    | _     |

| Overshoot                  |                                 | _                                                 | _   | _   | 10  | %     | _     |

| Input Patura Loss          |                                 | 5MHz - 1.485GHz                                   | 15  | _   | _   | dB    | _     |

| Input Return Loss          |                                 | 1.485GHz - 2.97GHz                                | 10  | _   | _   | dB    | _     |

| Input Resistance           |                                 | single-ended                                      | _   | 1.9 | _   | kΩ    | _     |

| Input Capacitance          |                                 | single-ended                                      | _   | 1.3 | _   | pF    | _     |

| Output Resistance          |                                 | single-ended                                      | _   | 50  | _   | Ω     | _     |

#### **Notes:**

- $1. \ \ Device performance is optimized for standard data rates (SD = 270Mb/s, HD = 1.485Gb/s, 3G = 2.970Gb/s, 6G = 5.94Gb/s).$

- 2. 0m cable length.

- 3. All parts are production tested. In order to guarantee maximum jitter over the full range of specification ( $V_{CC\_A} = +3.3V \pm 5\%$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , and 720-880mV<sub>pp</sub> launch swing from the SDI cable driver), the recommended applications circuit must be used.

- 4. Based on validation data using the recommended applications circuit, with  $V_{CC\_A} = +3.3V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$  and  $800 \text{mV}_{pp}$  launch swing from the SDI cable driver.

- 5.  $GAIN\_SEL = 0$ .

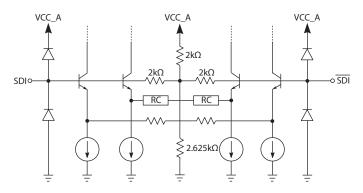

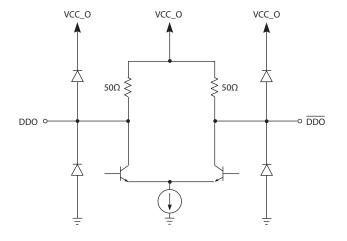

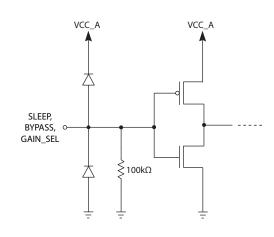

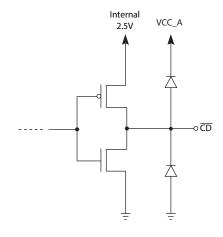

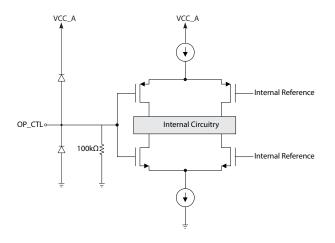

# 3. Input/Output Circuits

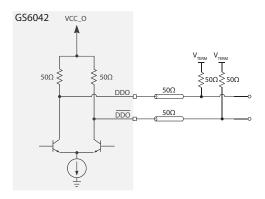

Figure 3-1: Input Circuit

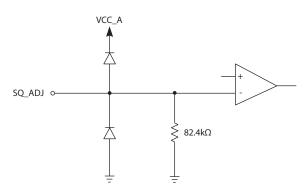

Figure 3-2: SQ\_ADJ Circuit

Figure 3-3: Output Circuit

Figure 3-4: SLEEP, BYPASS, and GAIN\_SEL Circuits

Figure 3-5: CD Circuit

Figure 3-6: OP\_CTL

# 4. Detailed Description

The GS6042 is a high-speed BiCMOS IC designed to automatically equalize high-bandwidth serial digital video signals.

The GS6042 can equalize data rates up to 6.25Gb/s including 6G UHD-SDI, 3G SDI, HD SDI, and SD SDI serial digital signals. The GS6042 is optimized to equalize up to 80m of Belden 1694A cable at 5.94Gb/s (UHD-SDI), 210m at 2.97Gb/s (3G-SDI), 300m at 1.485Gb/s (HD-SDI), and 500m at 270Mb/s (SD-SDI).

The GS6042 can be powered from a single +3.3V DC power supply, and is footprint-compatible with Semtech's GS2974A, GS2974B, GS2984, GS2994, and GS3440 equalizers.

## 4.1 Serial Digital Inputs

The received serial data signal is connected to the input pins (SDI/SDI) in either a differential or single-ended configuration. AC-coupling of the inputs is recommended because the SDI and SDI inputs are internally biased to approximately 1.71V.

See Figure 5-1 for the recommended input applications circuit when using a single-ended  $75\Omega$  coax cable.

## 4.2 Automatic (Adaptive) Cable Equalization

The input signal passes through a variable gain equalizing stage, whose frequency response closely matches the inverse of the Belden 1694A cable loss characteristic for any given attached cable length within the supported ranges.

The equalized signal is DC-restored, effectively restoring the logic threshold of the equalized signal to its correct level independent of shifts due to AC-coupling.

## 4.3 Differential Digital Data Output

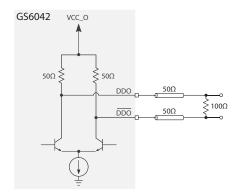

The digital data output signals (DDO/ $\overline{DDO}$ ) have a nominal output voltage swing of either 850mV<sub>ppd</sub> or 425mV<sub>ppd</sub> ( $\Delta$ V<sub>DDO</sub>), as set by the OP\_CTL pin. Table 4-1 shows the typical output common mode voltage levels (V<sub>CMOUT</sub>) related to the two output swing options and the type of output transmission termination as shown in Figure 4-1 and Figure 4-2.

Table 4-1: Typical Common Mode Output Voltage Levels (V<sub>CMOUT</sub>)

| Supply             | Termination Type 1 (       | See Figure 4-1) (See 1)    | Termination Type           | <b>2 (See</b> Figure 4-2)  |

|--------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| Voltage<br>(VCC_O) | 425mV <sub>ppd</sub> Swing | 850mV <sub>ppd</sub> Swing | 425mV <sub>ppd</sub> Swing | 850mV <sub>ppd</sub> Swing |

| 3.3V               | 3.19V                      | 3.09V                      | 3.09V                      | 2.88V                      |

| 2.5V               | 2.39V                      | 2.29V                      | 2.29V                      | 2.08V                      |

| 1.8V               | 1.69V                      | 1.59V                      | 1.59V                      | 1.38V                      |

| 1.2V               | 1.09V                      | 0.99V                      | 0.99V                      | 0.78V                      |

#### Note:

1. The values shown for termination type 1 only apply when  $V_{TERM} = VCC_O$ .

Figure 4-1:  $50\Omega$  Termination to  $V_{TFRM}$

Figure 4-2:  $100\Omega$  Parallel Output Termination

### 4.4 Programmable Squelch Adjust (SQ\_ADJ)

The GS6042 features a programmable Squelch Adjust (SQ\_ADJ) threshold.

This feature can be useful in applications where there are multiple input channels using the GS6042 and the maximum gain of each device must be limited to avoid crosstalk.

The SQ\_ADJ pin acts to change the threshold of the Carrier Detect  $(\overline{CD})$  pin. When the input signal level drops below the threshold set by SQ\_ADJ, the  $\overline{CD}$  pin will be driven HIGH, indicating that there is not a valid input signal.

This feature has been designed for use in applications such as routers, where signal crosstalk and circuit noise cause the equalizer to output erroneous data when no input signal is present. The use of a Carrier Detect function with a fixed internal reference does not solve this problem since the signal-to-noise ratio on the circuit board could be significantly less than the default signal detection level set by the on-chip reference.

In applications where programmable squelch adjust is not required, the SQ\_ADJ pin can be left unconnected.

**Note:** When using SQ\_ADJ to limit the maximum gain of the GS6042,  $\overline{\text{CD}}$  should not be connected to SLEEP.

## 4.5 Carrier Detect, Sleep, and Auto-Sleep

The Carrier Detect output pin  $\overline{(CD)}$  indicates the presence of a valid signal at the input of the GS6042. When  $\overline{CD}$  is LOW, the device has detected a valid input on SDI/ $\overline{SDI}$ . When  $\overline{CD}$  is HIGH, the device considers the input invalid.

**Note 1:** CD will only detect loss of signal for data rates greater than 19Mb/s.

**Note 2:** If SQ\_ADJ is being used to limit the maximum gain of the device, and the maximum cable length is exceeded, the  $\overline{\text{CD}}$  pin will be set to HIGH even if an input is present.

**Table 4-2: CD Output**

| CD | Input Status                |

|----|-----------------------------|

| 0  | Valid input on SDI/SDI pins |

| 1  | Input is not valid          |

The GS6042 also includes a SLEEP input pin, which can be used to put the device into a low-power sleep mode. In this mode, the outputs are high impedance and will be pulled high by the on-chip termination. Set the SLEEP pin HIGH to place the chip in this low-power state. In this mode, the Carrier Detect output will still function to facilitate the detection of a valid serial input data signal.

Auto-Sleep is enabled by connecting  $\overline{CD}$  to SLEEP. When connected, the GS6042 will automatically go into low-power sleep mode when there is a loss of input signal.

**Note 3:** If the  $\overline{CD}$  pin is connected to the SLEEP pin, SQ\_ADJ must be either left open, or connected to ground.

**Table 4-3: SLEEP Input**

| SLEEP | Function                                                          |

|-------|-------------------------------------------------------------------|

| 0     | Normal operation                                                  |

| 1     | Low-power sleep mode; $\overline{\text{CD}}$ output remains valid |

#### 4.6 GAIN SEL

The GS6042 provides the option of compensating for 6dB of flat attenuation prior to the equalizer.

Table 4-4: GAIN\_SEL Input Table

| GAIN_SEL | Function                                      |  |

|----------|-----------------------------------------------|--|

| 0        | No flat band gain is applied                  |  |

| 1        | 6dB of flat band gain applied to input signal |  |

## 4.7 Adjustable Output Swing, De-emphasis, and Mute

The OP\_CTL input pin determines the output swing and de-emphasis settings for DDO and DDO.

The OP\_CTL pin is an analog input, allowing different combinations of output swing, de-emphasis, and mute. The possible values are listed in Table 4-5.

Table 4-5: OP\_CTL Functions and Levels

| Level | Swing                | De-emphasis | Mute | Voltage (V)   |

|-------|----------------------|-------------|------|---------------|

| 0     | 850mV <sub>ppd</sub> | Off         | N    | 0.000 - 0.083 |

| 1     | 850mV <sub>ppd</sub> | 2dB         | N    | 0.234 - 0.394 |

| 2     | 850mV <sub>ppd</sub> | 6dB         | N    | 0.545 - 0.704 |

| 3     | 850mV <sub>ppd</sub> | 8dB         | N    | 0.856 - 1.015 |

| 4     | 425mV <sub>ppd</sub> | Off         | N    | 1.166 - 1.333 |

| 5     | 425mV <sub>ppd</sub> | 2dB         | N    | 1.484 - 1.644 |

| 6     | 425mV <sub>ppd</sub> | 6dB         | N    | 1.795 - 1.954 |

| 7     | 425mV <sub>ppd</sub> | 8dB         | N    | 2.106 - 2.265 |

| 8     | 425mV <sub>ppd</sub> | N/A         | Υ    | 2.416 - 2.500 |

When muted, the output swing is set to 425mV<sub>ppd</sub> and the outputs are latched.

Automatic muting of the output can be enabled by connecting the  $\overline{\text{CD}}$  pin to the OP\_CTL pin.

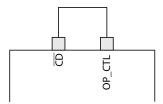

If the connection is made directly, as shown in Figure 4-3, the output would be in its default mode ( $850 \text{mV}_{ppd}$  swing with no de-emphasis) when there is signal present.

Figure 4-3: Direct Loopback

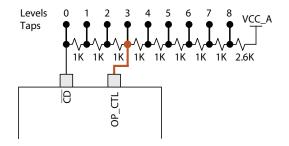

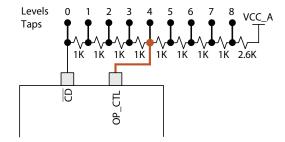

To enable automatic muting while the output is configured for other settings, a resistor network can be used between  $\overline{\text{CD}}$  and VCC\_A. The intermediate voltages of this resistor ladder can set the output to any one of the nine different settings as shown in the examples given in Figure 4-4 and Figure 4-5.

Figure 4-4: Resistor Divider Loopback Example #1 (Function Level 3 from Table 4-5)

Figure 4-5: Resistor Divider Loopback Example #2 (Function Level 4 from Table 4-5)

In Figure 4-4, the automatic muting of the output is established by connecting node 3 to the OP\_CTL pin. In this scenario, the output would be 850mV<sub>ppd</sub> with 8dB of de-emphasis when there is a signal present.

In Figure 4-5, the OP\_CTL pin is connected to node 4. In this scenario, the output would be  $425 \text{mV}_{ppd}$  with no de-emphasis when there is a signal present.

In both cases, the output would be muted when no carrier is detected.

Note: When the device is in SLEEP mode, automatic muting and SQ\_ADJ do not function. Asserting the SLEEP pin manually overrides all other functionality.

Rev.4

# 5. Applications Information

### 5.1 High-Gain Adaptive Cable Equalizers

The GS6042 is a multi-rate Adaptive Cable Equalizer. In order to extend the cable lengths that the device can support, it is necessary to have high-gain in the equalizer.

In particular, an SDI video cable equalizer must provide wide band gain over a range of frequencies in order to accommodate the range of data rates and signal patterns that are present in a SMPTE-compliant serial video stream.

Small levels of signal or noise present at the input pins of the equalizer may cause chatter at the output. In order to prevent this from happening, particular attention must be paid to board layout.

## 5.2 PCB Layout

Special attention must be paid to component layout when designing serial digital interfaces for HDTV and other high-speed video applications.

An FR-4 dielectric can be used, however, controlled impedance transmission lines are required for PCB traces longer than approximately 1cm. Note the following PCB artwork features used to optimize performance:

- PCB trace width for high data rate signals should be closely matched to SMT component width to minimize reflections due to changes in trace impedance

- High-speed traces should be curved to minimize impedance changes

- Cut-outs in the inner layers should be used under the GS6042 input and output components to minimize parasitic capacitance

Rev.4

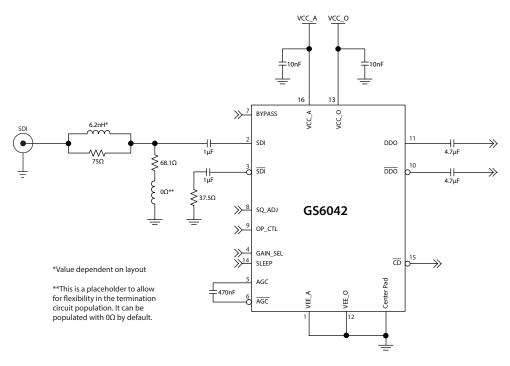

# **5.3 Typical Application Circuits**

Figure 5-1: GS6042 Typical Application Circuit Recommended for Extended Cable Reach Applications

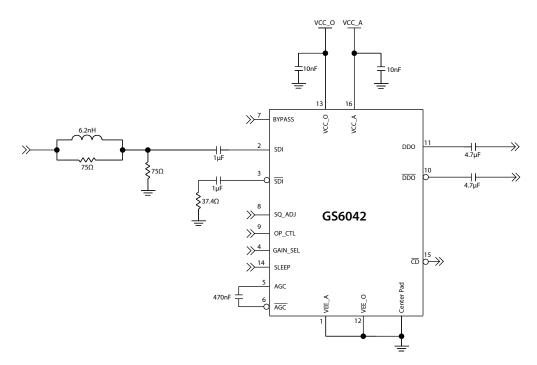

Figure 5-2: GS6042 Alternate Application Circuit Recommended for Drop-in Replacement Applications

# 6. Package & Ordering Information

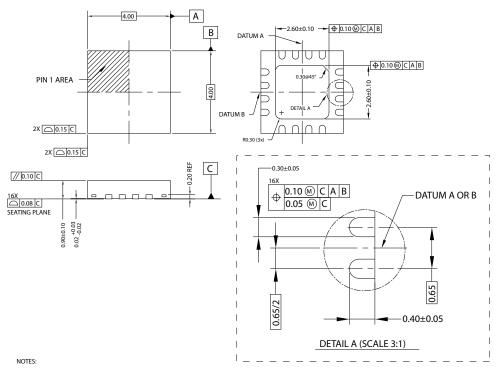

## **6.1 Package Dimensions**

- DIMENSIONING AND TOLERANCE IS IN CONFORMANCE TO ASME Y14.5-1994

ALL DIMENSIONS ARE IN MILLIMETERS \* IN DEGREES

DIMENSION OF LEAD WIDTH APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15mm AND 0.30mm FROM THE TERMINALT IR GOOTH ROWS, IF THE TERMINAL HAS OPTIONAL RADIUS ON THE END OF THE TERMINAL, THE LEAD WIDTH DIMENSION SHOULD NOT BE MEASURED IN THAT RADIUS AREA

Figure 6-1: Package Dimensions

## **6.2 Packaging Data**

Rev.4

Table 6-1: Packaging Data

| Parameter                                                            | Value                |

|----------------------------------------------------------------------|----------------------|

| Package Type                                                         | 4mm x 4mm 16-pin QFN |

| Package Drawing Reference                                            | JEDEC M0220          |

| Moisture Sensitivity Level                                           | 1                    |

| Junction to Case Thermal Resistance, $\theta_{j-c}$                  | 31.0°C/W             |

| Junction to Air Thermal Resistance, $\theta_{j-a}$ (at zero airflow) | 43.8°C/W             |

| Psi, ψ                                                               | 11.0°C/W             |

| Pb-free and RoHS compliant                                           | Yes                  |

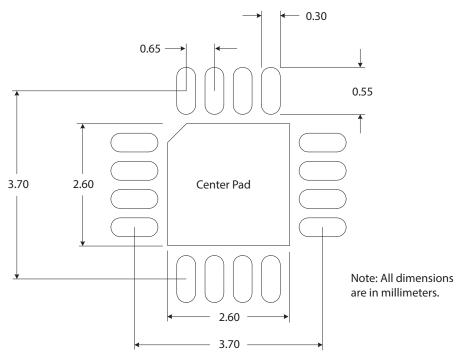

## **6.3 Recommended PCB Footprint**

Figure 6-2: Recommended PCB Footprint

The Center Pad should be connected to the most negative power supply plane for analog circuitry in the device (VEE\_A) by a minimum of 5 vias.

**Note:** Suggested dimensions only. Final dimensions should conform to customer design rules and process optimizations.

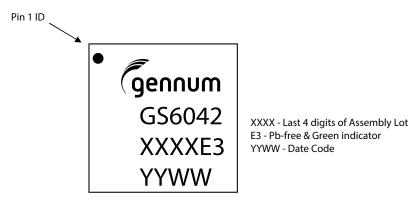

## 6.4 Marking Diagram

Figure 6-3: Marking Diagram

Rev.4

# **6.5 Solder Reflow Profiles**

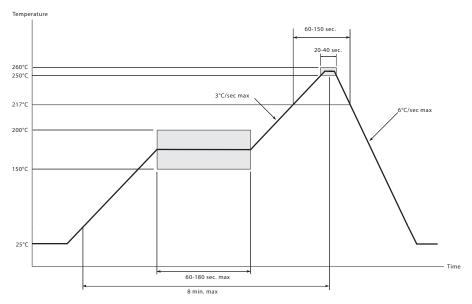

The GS6042 is available in a Pb-free package. It is recommended that the Pb-free package be soldered with Pb-free paste using the reflow profile shown in Figure 6-4.

Figure 6-4: Maximum Pb-free Solder Reflow Profile

## **6.6 Ordering Information**

**Table 6-2: Ordering Information**

| Part Number   | Package                                       | Temperature Range |

|---------------|-----------------------------------------------|-------------------|

| GS6042-INE3   | Pb-free 16-pin QFN                            | -40°C to +85°C    |

| GS6042-INTE3  | Pb-free 16-pin QFN<br>(250pc. tape and reel)  | -40°C to +85°C    |

| GS6042-INTE3Z | Pb-free 16-pin QFN<br>(2500pc. tape and reel) | -40°C to +85°C    |

#### **IMPORTANT NOTICE**

Information relating to this product and the application or design described herein is believed to be reliable, however such information is provided as a guide only and Semtech assumes no liability for any errors in this document, or for the application or design described herein. Semtech reserves the right to make changes to the product or this document at any time without notice. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. Semtech warrants performance of its products to the specifications applicable at the time of sale, and all sales are made in accordance with Semtech's standard terms and conditions of sale.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS, OR IN NUCLEAR APPLICATIONS IN WHICH THE FAILURE COULD BE REASONABLY EXPECTED TO RESULT IN PERSONAL INJURY, LOSS OF LIFE OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

The Semtech name and logo are registered trademarks of the Semtech Corporation. All other trademarks and trade names mentioned may be marks and names of Semtech or their respective companies. Semtech reserves the right to make changes to, or discontinue any products described in this document without further notice. Semtech makes no warranty, representation or guarantee, express or implied, regarding the suitability of its products for any particular purpose. All rights reserved.

© Semtech 2015

#### **Contact Information**

Semtech Corporation 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111, Fax: (805) 498-3804 www.semtech.com