## **Integrated Driver and MOSFET & Linear Regulator**

#### **General Description**

The DS9613 are high frequency integrated power stage optimized for synchronous buck applications to offer high current, high efficiency, and high power density performance with very low shutdown current. Packaged in QFN3x3-21L & QFN4x4-23L package, DS9613 enable voltage regulator designs to deliver up to 8 A continuous current per phase.

The DS9613 incorporates an advanced MOSFET gate driver IC that features high current driving capability, adaptive dead-time control, an integrated bootstrap switch.

The DS9613 offer operating temperature monitoring, protection features, and warning flags that improve system monitoring and reliability.

### **Applications**

• True Wireless Stereo

#### **Features**

- Capable of Average Currents up to 8A

- Capable of Switching at Frequencies up to 1 MHz

- Integrated High Voltage Linear Regulator

- Compatible with 2V ~ 5V PWM Input

- Support VCC to 2.5V ~ 5.5V Power

- Internal Bootstrap Diode

- Undervoltage Lockout

- The QFN3x3-21L & QFN4x4-23L Package Available

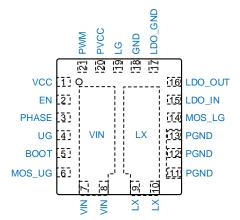

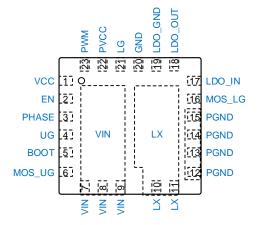

#### **Pin Configurations**

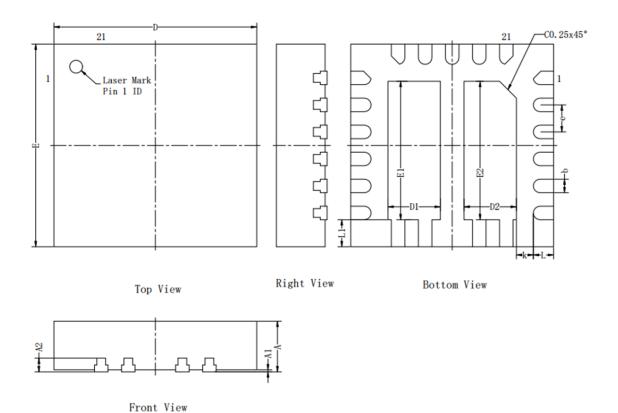

QFN3x3-21L

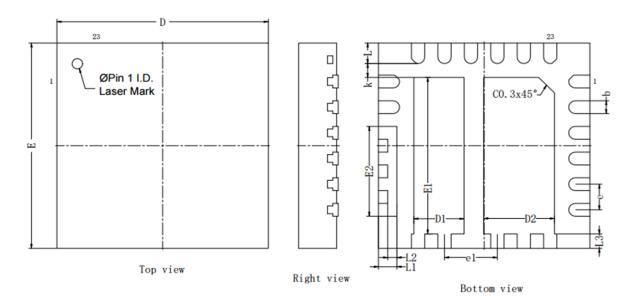

QFN4x4-23L

## **Ordering Information**

DS9613XX

| Designator | Description  | Symbol | Description |

|------------|--------------|--------|-------------|

| XX         | Package Type | Q33    | QFN3x3-21L  |

|            |              | Q44    | QFN4x4-23L  |

## **Description of Functional Pins**

| Pin No       |                   | Pin Name    | Pin Function                                                                                                                                                        |  |

|--------------|-------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| QFN3x3-21L   | QFN4x4-23L        | Pili Naille | Fill Fullction                                                                                                                                                      |  |

| 1            | 1                 | VCC         | Power supply of internal control logic. The required bias voltage for VCC is 2.5V ~ 5.5V. For avoiding noise disturbance, the supplied bias voltage must be stable. |  |

| 2            | 2                 | EN          | Enable Pin. When low, both UGATE and LGATE are driven low and the normal operation is disabled.                                                                     |  |

| 3            | 3                 | PHASE       | Bootstrap Capacitor Return , Must be connected to LX .                                                                                                              |  |

| 4            | 4                 | UG          | Driver for High Side MOSFET Gate Access .                                                                                                                           |  |

| 5            | 5                 | BOOT        | Bootstrap Supply for High Side Gate Drive.                                                                                                                          |  |

| 6            | 6                 | MOS_UG      | High Side MOSFET Gate Input .                                                                                                                                       |  |

| 7,8          | 7,8,9             | VIN         | Conversion Supply Power Input .                                                                                                                                     |  |

| 9 , 10       | 10 , 11           | LX          | Switch Node Output .                                                                                                                                                |  |

| 11 , 12 , 13 | 12 , 13 , 14 , 15 | PGND        | Power Ground .                                                                                                                                                      |  |

| 14           | 16                | MOS_LG      | Low Side MOSFET Gate Input .                                                                                                                                        |  |

| 15           | 17                | LDO_OUT     | Linear Regulator Output Pin.                                                                                                                                        |  |

| 16           | 18                | LDO_IN      | Linear Regulator Input Pin.                                                                                                                                         |  |

| 17           | 19                | GND         | Linear Regulator ( LDO ) ground.                                                                                                                                    |  |

| 18           | 20                | GND         | Analog ground.                                                                                                                                                      |  |

| 19           | 21                | LG          | Driver for Low Side MOSFET Gate Access .                                                                                                                            |  |

| 20           | 22                | PVCC        | Power supply of gate driver. The required bias voltage for PVCC is 2.5V ~ 5.5V. Connect a 1uF/X7R between PVCC and PGND.                                            |  |

| 21           | 23                | PWM         | PWM Signal Input. Connect this pin to the PWM output of the controller .                                                                                            |  |

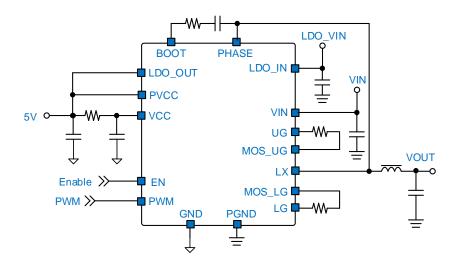

### **Typical Application Circuits**

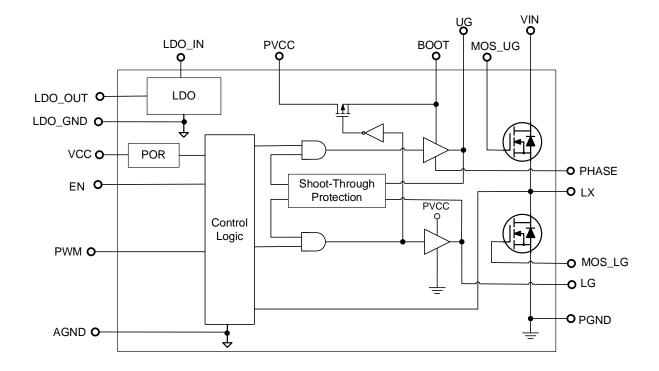

### **Function Block Diagram**

| VIN to GND                                    | 3U/V                   |

|-----------------------------------------------|------------------------|

| VCC & PVCC to GND                             |                        |

| BOOT to PHASE, VBOOT-PHASE                    |                        |

| DC                                            | 0.3V to 6.5V           |

| < 20ns                                        |                        |

| PHASE & LX to GND                             |                        |

| DC                                            | 0.3V to 30V            |

| < 20ns                                        |                        |

| GL to GND                                     |                        |

| DC                                            | −0.3V to 6.5V          |

| < 20ns                                        |                        |

| LDO_IN to GND                                 | 28V                    |

| Other Pins                                    | ( GND - 0.3V ) to 6.5V |

| Power Dissipation, PD @ T <sub>A</sub> = 25°C |                        |

| QFN3x3-21L                                    | 3.3W                   |

| QFN4x4-23L                                    | 5.8W                   |

| Package Thermal Resistance (Note 2)           |                        |

| QFN3x3-21L , θ <sub>JA</sub>                  | 35°C/W                 |

| QFN4x4-23L , θ <sub>JA</sub>                  | 19°C/W                 |

| Lead Temperature (Soldering, 10 sec.)         | 260°C                  |

| Junction Temperature                          | 150°C                  |

| Storage Temperature Range                     | −65°C to 150°C         |

| ESD Susceptibility (Note 3)                   |                        |

| HBM (Human Body Model)                        | 2KV                    |

|                                               |                        |

| Recommended Operating Conditions              |                        |

| Supply Input Voltage, VIN                     | 2.5V to 24V            |

| Supply LDO Input Voltage, LDO_IN              | 5.5V to 23V            |

| Control Input Voltage, VCC & PVCC             | 2.5V to 5.5V           |

| Junction Temperature Range                    | −10°C to 125°C         |

| Ambient Temperature Range                     | −10°C to 85°C          |

#### **Electrical Characteristics**

(  $V_{IN}$  =12V,  $V_{CC}$  =5V,  $T_A$ =25°C unless otherwise specified )

| Parame                    | ter        | Symbol               | Test Conditions                                                                              | Min | Тур | Max | Unit |  |

|---------------------------|------------|----------------------|----------------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| Supply Voltage Rang       | je         | VCC , PVCC           |                                                                                              | 2.5 | 5.0 | 5.5 | V    |  |

| Quiescent Current         |            | Iq_vcc               | PWM Input Floating                                                                           |     | 50  |     | μΑ   |  |

| Dawer On Danet            |            | V <sub>POR_R</sub>   | VCC & PVCC Rising                                                                            |     | 2.5 | 2.8 | V    |  |

| Power On Reset            |            | V <sub>POR_</sub> F  | VCC & PVCC Falling                                                                           | 2.1 | 2.3 |     | V    |  |

| Conversion Voltage        |            | VIN                  |                                                                                              | 2.5 | 12  | 24  | V    |  |

|                           |            |                      | F <sub>SW</sub> = 1 MHz,<br>VIN = 12 V, VOUT = 1.0 V,                                        |     |     | 5   |      |  |

| Continuous Output Current |            |                      | F <sub>SW</sub> = 300 KHz,<br>VIN = 12 V, VOUT = 1.0 V,                                      |     |     | 8   | А    |  |

|                           |            |                      | Duration = 5 S,<br>Period = 10 mS,                                                           |     |     | 12  |      |  |

| Peak Output Current       |            |                      | F <sub>SW</sub> = 300 KHz,<br>VIN = 12 V, VOUT = 1.0V,<br>Duration = 10 mS,<br>Period = 1 S, |     |     | 18  | А    |  |

| High & Low Side MOSFET    |            | R <sub>DS(ON)</sub>  | V <sub>GS</sub> = 4.5V                                                                       |     | 23  |     | mΩ   |  |

| PWM INPUT                 |            |                      |                                                                                              | 1   |     |     |      |  |

| Maximum Input Current     |            | I <sub>PWM</sub>     | PWM = 5V or 0V                                                                               |     |     | 100 | μΑ   |  |

| PWM Rising Threshold      |            | V <sub>PWM_Rth</sub> |                                                                                              | 1.8 |     |     | V    |  |

| PWM Falling Threshold     |            | V <sub>PWM_Fth</sub> |                                                                                              |     |     | 0.4 | V    |  |

| GATE DRIVER TIMI          | NGS        |                      |                                                                                              |     |     |     |      |  |

| LS to HS Gate Deadtime    |            | t <sub>PD HU</sub>   |                                                                                              |     | 20  |     | nS   |  |

| HS to LS Gate Deadtime    |            | t <sub>PD HL</sub>   |                                                                                              |     | 20  |     | nS   |  |

| EN# INPUT                 |            |                      |                                                                                              |     |     |     |      |  |

|                           | Logic-High | V <sub>EN_</sub> H   | VCC = 5V                                                                                     | 2   |     |     |      |  |

| EN Input Voltage          |            |                      |                                                                                              |     |     |     | V    |  |

| Parameter                                  | Symbol            | Test Conditions                                                               | Min | Тур  | Max | Unit |

|--------------------------------------------|-------------------|-------------------------------------------------------------------------------|-----|------|-----|------|

| Linear Regulator                           | Linear Regulator  |                                                                               |     |      |     |      |

| Supply Voltage                             | Vin               |                                                                               | 5.5 |      | 23  | V    |

| DC Output Voltage Accuracy                 |                   | I <sub>LOAD</sub> = 0.1mA                                                     | -1  |      | 1   | %    |

| Dropout Voltage (I <sub>LOAD</sub> =100mA) | V <sub>DROP</sub> | Vout = 5V                                                                     |     | 0.35 |     | V    |

| Ground Current (I <sub>LOAD</sub> = 0mA)   | lα                | V <sub>IN</sub> > 5.5V                                                        |     | 1.5  |     | μA   |

| Line Regulation                            | ΔLINE             | $I_{LOAD} = 1 \text{mA},$<br>$10 \text{V} \leq V_{IN} \leq 20 \text{V}$       |     | 0.5  |     | %    |

| Load Regulation                            | ΔLOAD             | 10mA≤ I <sub>LOAD</sub> ≤ 0.2A                                                |     | 0.3  |     | %    |

| Output Current Limit                       | I <sub>LIM</sub>  | V <sub>OUT</sub> = 0V                                                         | 501 | 700  |     | mA   |

| Power Supply Rejection Ratio               | PSRR              | Vout = 5V,<br>I <sub>LOAD</sub> = 30mA,<br>V <sub>IN</sub> = 12V,<br>f = 1KHz |     | 70   |     | dB   |

| Thermal Shutdown Temperature               | T <sub>SD</sub>   | lioad = 10mA                                                                  |     | 160  |     | °C   |

| Thermal Shutdown Hysteresis                | ΔT <sub>SD</sub>  | - ILOAD = TOTTIA                                                              |     | 15   |     | °C   |

- Note 1. Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta$ JA is measured at  $T_A = 25^{\circ}$ C on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta$ <sub>JC</sub> is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

#### **Application Guideline**

#### Theory of Operation

The DS9613 is an integrated driver and MOSFET module designed for use in a synchronous buck converter topology. A PWM input signal is required to control the drive signals to the high-side and low-side integrated MOSFETs.

#### POR ( Power On Reset )

POR block detects the voltage of the VCC pin. When the VCC pin voltage is higher than POR rising hreshold, POR block output is high. POR output is low when VCC is not higher than POR rising threshold. When the POR block output is high, UGATE and LGATE can be controlled by PWM input voltage. If the POR block output is low, both UGATE and LGATE will be pulled to low.

#### **Bootstrap Control**

Bootstrap control block controls the integrated bootstrap switch. When LGATE is high ( low side MOSFET is turned on ), the bootstrap switch is turned on to charge the bootstrap capacitor connected to BOOT pin. When LGATE is low ( low side MOSFET is turned off ), the bootstrap switch is turned off to disconnect VCC pin and BOOT pin.

#### **Power Supply Decoupling**

The DS9613 sources relatively large currents into the MOSFET gates. In order to maintain a constant and stable supply voltage ( PVCC ) a low–ESR capacitor should be placed near the power and ground pins. A multi–layer ceramic capacitor ( MLCC ) between 1uF and 4.7uF is typically used.

A separate supply pin ( VCC ) is used to power the analog and digital circuits within the driver. A 1uF ceramic capacitor should be placed on this pin in close proximity to the DS9613. It is good practice to separate the VCC and PVCC decoupling capacitors with a resistor ( 10 typical ) to avoid coupling driver noise to the analog and digital circuits that control the driver function .

# Safety Timer and Overlap Protection Circuit

It is important to avoid cross-conduction of the two MOSFETS which could result in a decrease in the power conversion efficiency or damage to the device.

The DS9613 and applying the appropriate amount of non-overlap time (the time between the turn-off of one MOSFET and the turn-on of the other MOSFET). When the PWM input pin is driven high, the gate of the low-side MOSFET goes low after a propagation delay. The time it takes for the low-side MOSFET to turn off is dependent on the total charge on the low-side MOSFET gate.

The DS9613 monitors the gate voltage of both MOSFETs and the switch node voltage to determine the conduction status of the MOSFETs. Once the low-side MOSFET is turned off an internal timer delays the turn-on of the high-side MOSFET. When the PWM input pin goes low, the gate of the high-side MOSFET goes low after the propagation delay . The time to turn off the high-side MOSFET is dependent on the total gate charge of the high-side MOSFET. A timer is triggered once the high-side MOSFET stops conducting, to delay the turn-on of the low-side MOSFET.

#### Enable and Disable

The DS9613 includes an EN pin for sequence control. When the EN pin rises above the VEN\_H trip point, the DS9613 begins a new initialization and follows the PWM command to control the UGATE and LGATE. When the EN pin falls below the VEN\_L trip point, the DS9613 shuts down and keeps UGATE and LGATE low.

| UVLO | EN#  | Driver State             |

|------|------|--------------------------|

| L    | Х    | Disabled ( UG = LG = 0 ) |

| Н    | L    | Disabled ( UG = LG = 0 ) |

| Н    | Н    | Enabled                  |

| Н    | Open | Enabled                  |

# Linear Regulator (LDO) Input and Output Capacitor Requirements

The external input and output capacitors of LDO must be properly selected for stability and performance. Use a  $1\mu F$  or larger input capacitor and place it close to the IC's LDO\_IN and GND pins. Any output capacitor meeting the minimum  $1m\Omega$  ESR ( Equivalent Series Resistance ) and effective capacitance between  $1\mu F$  and  $22\mu F$  requirement may be used. Place the output capacitor close to the IC's LDO\_OUT and GND pins. Increasing capacitance and decreasing ESR can improve the circuit's PSRR and line transient response.

#### Linear Regulator Current Limit

The LDO contain the current limiter of output power transistor, which monitors and controls the transistor, limiting the output current to 700mA (typical).

The output can be shorted to ground indefinitely without damaging the part.

#### Linear Regulator Dropout Voltage

The LDO use a PMOS pass transistor to achieve low dropout. When ( LDO\_IN – LDO\_OUT ) is less than the dropout voltage (  $V_{DROP}$  ), the PMOS pass device is in the linear region of operation and the input-to-output resistance is the RDS<sub>(ON)</sub> of the PMOS pass element.  $V_{DROP}$  scales approximately with the output current because the PMOS device behaves as a resistor in dropout condition.

As any linear regulator, PSRR and transient response are degraded as ( LDO\_IN - LDO\_OUT ) approaches dropout condition.

# Linear Regulator OTP ( Over Temperature Protection )

The over temperature protection function of LDO will turn off the P-MOSFET when the junction temperature exceeds 160°C (typ.). Once the junction temperature cools down by approximately 15°C, the regulator will automatically resume operation.

#### **PCB Layout Guidelines**

DS9613 is a high current module rated for operation up to 1MHz. This requires high switching speed to keep the switching losses and device temperatures within limits. An integrated gate driver within the package eliminates driver-to-MOSFET gate pad parasitic of the package or on PCB.

To achieve high switching speeds, high levels of slew rate (dv/dt and di/dt) will be present throughout the power train which requires careful attention to PCB layout to minimize voltage spikes and other transients. As with any synchronous buck converter layout, the critical requirement is to minimize the path of the primary switching current loop formed by the High-Side MOSFET, Low-Side MOSFET, and the input bypass capacitor CIN. The PCB design is greatly simplified by the optimization of the DS9613 pin out. The power inputs of VIN and PGND are located adjacent to each other and the input bypass capacitors CIN should be placed as close as possible to these pins. The area of the secondary switching loop is formed by Low-Side MOSFET, output inductor, and output capacitor COUT is the next critical requirement.

While DS9613 is a highly efficient module, it still dissipates a significant amount of heat under high power conditions. Special attention is required for thermal design. MOSFETs in the package are directly attached to individual exposed pads (VIN and PGND) to simplify thermal management. Both VIN and LX pads should be attached to large areas of PCB copper. Thermal relief pads should be placed to ensure proper heat dissipation to the board. An inner power plane layer dedicated to VIN, typically the high voltage system input, is desirable and VIAs should be provided near the device to connect the VIN pads to the power plane. Significant amount of heat can also be dissipated through multiple PGND pins.

A large copper area connected to the PGND pins in addition to the system ground plane through VIAs will further improve thermal dissipation.

As shown on Figure , the top most layer of the PCB should comprise of wide and exposed copper area for the primary AC current loop which runs along VIN pad originating from the input capacitors hat are mounted to a large PGND pad. They serve as thermal relief as heat flows down to the VIN exposed pad that fan out to a wider area.

Adding VIAs will only help transfer heat to cooler regions of the PCB board through the other layers beneath but serve no purpose to AC activity as all the AC current sees the lowest impedance on the top layer only.

As the primary and secondary (complimentary) AC current loops move through VIN to LX and through PGND to LX, large positive and negative voltage spikes appear at the LX terminal which are caused by the large internal di/dt produced by the package parasitic.

To minimize the effects of this interference at the LX terminal, at which the main inductor is mounted, size just enough for the inductor to physically fit. The goal is to employ the least amount of copper area for this LX terminal, only enough so the inductor can be securely mounted.

## **Package Information:**

| SYMBOL | MIN        | NOM        | MAX   |  |  |

|--------|------------|------------|-------|--|--|

| A      | 0.70       | 0.75       | 0.80  |  |  |

| A1     | 0.00       | /          | 0.05  |  |  |

| A2     |            | 0. 203 REF | ,     |  |  |

| b      | 0.15       | 0.20       | 0. 25 |  |  |

| D      | 2.90       | 3.00       | 3. 10 |  |  |

| D1     | 0.675      | 0.775      | 0.875 |  |  |

| D2     | 0.675      | 0.775      | 0.875 |  |  |

| Е      | 2.90       | 3.00       | 3. 10 |  |  |

| E1     | 1. 95      | 2.05       | 2. 15 |  |  |

| E2     | 1. 95      | 2.05       | 2. 15 |  |  |

| е      | 0. 40 BSC  |            |       |  |  |

| k      | 0. 25 REF. |            |       |  |  |

| L      | 0. 20      | 0.30       | 0.40  |  |  |

| L1     | 0.30       | 0.40       | 0. 50 |  |  |

QFN3x3-21L

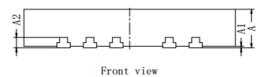

| SYMBOL | MIN        | NOM        | MAX   |  |

|--------|------------|------------|-------|--|

| A      | 0.70       | 0.75       | 0.80  |  |

| A1     | 0.00       | /          | 0.05  |  |

| A2     | 110        | 0. 203 REF |       |  |

| b      | 0.20       | 0. 25      | 0.30  |  |

| D      | 3.90       | 4.00       | 4. 10 |  |

| D1     | 0.85       | 0.95       | 1.05  |  |

| D2     | 1.24       | 1.34       | 1.44  |  |

| E      | 3.90       | 4.00       | 4. 10 |  |

| E1     | 2. 35      | 3.05       | 2. 55 |  |

| E2     | 1.65       | 1.75       | 1.85  |  |

| е      | 0. 50 BSC  |            |       |  |

| e1     | 1.00 BSC   |            |       |  |

| k      | 0. 27 REF. |            |       |  |

| L      | 0.30       | 0.40       | 0.50  |  |

| L1     | 0.25       | 0.35       | 0.45  |  |

| L2     | 0.075      | 0.175      | 0.275 |  |

| L3     | 0.18       | 0.28       | 0.38  |  |

QFN4x4-23L