# 30V, 0.3A, High-Frequency Transformer Driver for Automotive Applications, AEC-Q100

#### DESCRIPTION

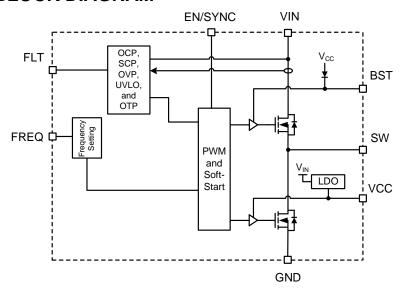

The MPQ18913 is a high-frequency half-bridge transformer driver. It is ideal for use as the primary-side MOSFET in isolated power supplies for biasing silicon carbide (SiC) field-effect transistors (FETs), silicon FETs, and insulated gate bipolar transistors (IGBTs). The MPQ18913 simplifies an isolated biased supply's design by integrating the control, switching power stage, and protection circuitry in one device. This typology supports designs with a high isolation voltage and small interwinding capacitance.

The MPQ18913 features soft switching and an optional frequency spread spectrum (FSS) to optimize EMI performance. It supports a wide 5V to 30V input voltage ( $V_{IN}$ ) range, and can survive surges of up to 50V. It also integrates two switching MOSFETs that are rated for 300mA of average input current ( $I_{IN}$ ).

The device has a wide 400kHz to 5MHz configurable switching frequency ( $f_{SW}$ ) range, which reduces the solution size and optimizes efficiency in resonant topologies (e.g. LLC converters).

Full safety and protection features include input over-voltage protection (OVP), over-current protection (OCP), and fault indication. The device's built-in soft start (SS) controls the inrush current during start-up.

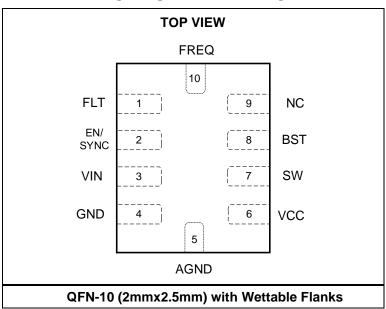

The MPQ18913 is available in QFN-10 (2mmx2.5mm) package with wettable flanks.

#### **FEATURES**

- Advanced Protection Features:

- Over-Current Protection (OCP)

- Short-Circuit Protection (SCP)

- Over-Voltage Protection (OVP)

- Over-Temperature Protection (OTP)

- Fault Reporting

- Under-Voltage Lockout (UVLO)

- Supports Up to 5kV Isolation Voltage

- Low EMI:

- o Soft Switching

- Flip-Chip Package

- Frequency Spread Spectrum (FSS)Option

- Low Interwinding Capacitance

- Small Solution Size:

- 400kHz to 5MHz Configurable Switching Frequency (f<sub>SW</sub>)

- Available in a Tiny QFN-10 (2mmx2.5mm) Package with Wettable Flanks

#### **APPLICATIONS**

- Silicon Carbide (SiC) Transformer Driver Biased Supplies

- Automotive Traction Inverters and Onboard Charging (OBC)

- DC Fast-Charging Stations

- Uninterrupted Power Supplies (UPSs) and Solar Inverters

- Isolated Power Supplies

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

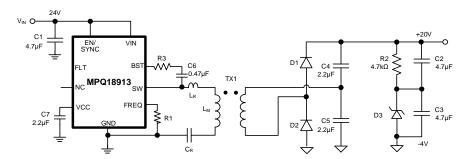

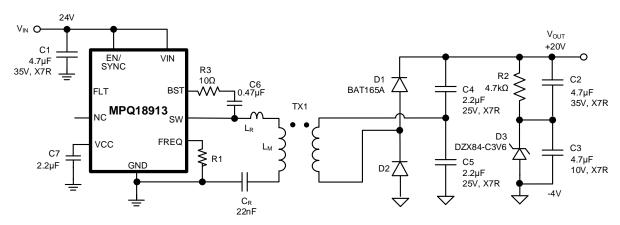

#### TYPICAL APPLICATION

#### **SELECTION GUIDE**

| Part Number           | Soft-Start Time | Hiccup Time |

|-----------------------|-----------------|-------------|

| MPQ18913GRPE-AEC1-Z   | 2ms             | 12ms        |

| MPQ18913GRPE-A-AEC1-Z | 20ms            | 120ms       |

#### ORDERING INFORMATION

| Part Number           | Package                  | Top Marking | MSL Rating |

|-----------------------|--------------------------|-------------|------------|

| MPQ18913GRPE-AEC1*    | QFN-10 (2mmx2.5mm)       | See Below   | 1          |

| MPQ18913GRPE-A-AEC1** | QFN-10 (ZIIIIIXZ.SIIIII) | See Delow   | l          |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MPQ18913GRPE-AEC1-Z).

**TOP MARKING** (MPQ18913GRPE-AEC1)

**TOP MARKING** (MPQ18913GRPE-A-AEC1)

MLY

**MMY**

LLL

LLL

ML: Product code of MPQ18913GRPE-AEC1

MM: Product code of MPQ18913GRPE-A-AEC1-Z

Y: Year code LLL: Lot number Y: Year code LLL: Lot number

#### PACKAGE REFERENCE

© 2024 MPS. All Rights Reserved.

<sup>\*\*</sup> For Tape & Reel, add suffix -Z (e.g. MPQ18913GRPE-A-AEC1-Z).

## **PIN FUNCTIONS**

| Pin# | Name    | Description                                                                                                                                                                           |

|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | FLT     | Fault indicator. The FLT pin is an open-drain output.                                                                                                                                 |

| 2    | EN/SYNC | <b>Enable and external clock.</b> Pull the EN/SYNC pin high to turn the device on; pull EN/SYNC low to turn it off. Apply an external clock to synchronous switching frequency (fsw). |

| 3    | VIN     | Input voltage. Bypass the VIN pin to GND using a $1\mu F$ ceramic capacitor, placed as close to the IC as possible.                                                                   |

| 4    | GND     | Ground.                                                                                                                                                                               |

| 5    | AGND    | Analog ground. Connect AGND to power ground using a single-point connection.                                                                                                          |

| 6    | VCC     | <b>Biased supply.</b> Decouple the VCC pins using a $\ge 1\mu F$ ceramic capacitor referred to GND. Place this capacitor as close to VCC as possible.                                 |

| 7    | SW      | Switching node.                                                                                                                                                                       |

| 8    | BST     | HS-FET driver voltage. Connect a ceramic capacitor between the BST and SW pins.                                                                                                       |

| 9    | NC      | Not connected. For internal test use only. Leave the NC pin floating.                                                                                                                 |

| 10   | FREQ    | <b>Switching frequency setting.</b> Connect a resistor between the FREQ and GND pins to set fsw. Place this resistor as close to FREQ as possible.                                    |

#### ABSOLUTE MAXIMUM RATINGS (1)

| V <sub>IN</sub> , V <sub>EN</sub>             | 0.3V to +35V                   |

|-----------------------------------------------|--------------------------------|

| V <sub>SW</sub>                               | $-0.3V$ to $(V_{IN} + 0.3V)$   |

| BST to SW                                     | 0.3V to +6.5V                  |

| $V_{CC}$ , $V_{DET}$ , $V_{FLT}$ , $V_{FREQ}$ | 0.3V to +6.5V                  |

| V <sub>IN</sub> , V <sub>EN</sub> (surge)     | 0.3V to +50V                   |

| Junction temperature (T <sub>J</sub> )        | 150°C                          |

| Lead temperature                              | 260°C                          |

| Storage temperature                           | 65°C to +150°C                 |

| Continuous power dissipati                    | on $(T_A = 25^{\circ}C)^{(2)}$ |

| QFN-10 (2mmx2.5mm)                            | 2.5W                           |

#### ESD Ratings

| Human body model (HBN   | Л)±2000V  |

|-------------------------|-----------|

| Charged device model (C | DM)±2000V |

## Recommended Operating Conditions (3)

| Input voltage (V <sub>IN</sub> ) | 5V to 30V         |

|----------------------------------|-------------------|

| External VCC bias                | 4.86V to 5.5V     |

| Operating junction temp (7       | (i)40°C to +150°C |

#### Thermal Resistance $\theta_{JA}$ $\theta_{JC}$

| EVQ-189  | 13-D-00A <sup>(4)</sup> | 45.3                | 7   | °C/W |

|----------|-------------------------|---------------------|-----|------|

| QFN-10 ( | (2mmx2.5mm)             | ) <sup>(5)</sup> 70 | 2.3 | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) T<sub>A</sub>) / θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation can cause excessive die temperature, which may cause the device to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on the EVQ18913-D-00A, 6-layer PCB.

- 5) Measured on a JESD51-7, 4-layer PCB. The value of θ<sub>JA</sub> given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

3

## **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 24V$ ,  $T_J = -40$ °C to +150°C, typical values are tested at  $T_J = 25$ °C, unless otherwise noted.

| Parameter                                            | Symbol                           | Condition                                                                               | Min  | Тур  | Max  | Units |

|------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------|------|------|------|-------|

| Power Supply Transformer Driver                      |                                  |                                                                                         |      | •    |      |       |

| VCC regulator voltage                                | Vcc                              | $I_{CC}$ = 0mA to 20mA, $V_{EN}$ = 1.5V                                                 | 4.55 | 4.7  | 4.85 | V     |

| Vcc under-voltage lockout rising (UVLO) threshold    | Vcc_uvlo_<br>RISING              | V <sub>CC</sub> rising                                                                  | 4.1  | 4.25 | 4.4  | V     |

| Vcc UVLO falling threshold                           | V <sub>CC_UVLO_</sub><br>FALLING | Vcc falling                                                                             | 3.95 | 4.1  | 4.25 | V     |

| Vcc UVLO hysteresis                                  | Vcc_uvlo_hys                     |                                                                                         |      | 150  |      | mV    |

| V <sub>IN</sub> UVLO rising threshold                | V <sub>IN_UVLO_</sub>            | V <sub>IN</sub> rising                                                                  | 4.35 | 4.65 | 4.9  | V     |

| V <sub>IN</sub> UVLO falling threshold               | VIN_UVLO_<br>FALLING             | V <sub>IN</sub> falling                                                                 | 4    | 4.25 | 4.5  | V     |

| V <sub>IN</sub> UVLO hysteresis                      | V <sub>IN_UVLO_HYS</sub>         |                                                                                         |      | 400  |      | mV    |

| Shutdown current                                     | I <sub>SD</sub>                  | V <sub>EN</sub> = 0V                                                                    |      | 4    | 12   | μΑ    |

| Quiescent current                                    | ΙQ                               | $V_{EN}$ =1.5V, $f_{SW}$ = 1MHz (set by the FREQ resistor, $R_{FREQ}$ ), SW is floating |      | 9.5  |      | mA    |

| Input over-voltage protection (OVP) rising threshold | Vovp_rising                      | Rising                                                                                  | 31   | 33   | 35   | V     |

| Input OVP falling threshold                          | Vovp_falling                     | Falling                                                                                 | 28.5 | 30.5 | 32.5 | V     |

| Input OVP hysteresis                                 | Vovp_hys                         |                                                                                         |      | 2.5  |      | V     |

| EN start-up threshold                                | V <sub>EN_ON</sub>               | V <sub>EN</sub> rising                                                                  | 1    | 1.1  | 1.2  | V     |

| EN shutdown threshold                                | V <sub>EN_OFF</sub>              | V <sub>EN</sub> falling                                                                 | 0.8  | 0.9  | 1    | V     |

| EN hysteresis                                        | V <sub>EN_HYS</sub>              |                                                                                         |      | 0.2  |      | V     |

| EN pull-down resistance                              | Ren                              |                                                                                         |      | 2    |      | МΩ    |

| EN shutdown blanking time (6)                        | ten_sd_blk                       | EN off to stop switching                                                                |      | 6    |      | μs    |

| Synchronous (SYNC) input rising threshold            | V <sub>SYNC_RISING</sub>         | Rising                                                                                  |      | 1.7  |      | V     |

| SYNC input falling threshold                         | VSYNC_FALLING                    | Falling                                                                                 |      | 0.9  |      | V     |

| SYNC input hysteresis                                | V <sub>SYNC_HYS</sub>            |                                                                                         |      | 0.8  |      | V     |

| High-side MOSFET (HS-FET) on resistance              | Rds(on)_hs                       | I <sub>DS</sub> = 0.1A                                                                  |      | 180  |      | mΩ    |

| Low-side MOSFET (LS-FET) on resistance               | R <sub>DS(ON)_LS</sub>           | I <sub>DS</sub> =0.1A                                                                   |      | 180  |      | mΩ    |

|                                                      |                                  | V <sub>EN</sub> = 0V, V <sub>SW</sub> = 24V, T <sub>J</sub> = 25°C                      |      |      | 1    | μΑ    |

| Switch leakage                                       | Isw_LkG                          | V <sub>EN</sub> = 0V, V <sub>SW</sub> = 24V,<br>T <sub>J</sub> = -40°C to 150°C         |      |      | 6    | μΑ    |

| Average SW capacitance                               | Csw                              | V <sub>EN</sub> = 0V, SW ramps up from 0V to 24V                                        | 100  | 125  | 150  | pF    |

| FLT output low voltage                               | V <sub>OL</sub>                  |                                                                                         |      | 0.2  | 0.3  | V     |

| Contable of free                                     | t.                               | $R_{FREQ} = 33k\Omega$                                                                  | -3%  | 3    | +3%  | MHz   |

| Switching frequency                                  | fsw                              | $R_{FREQ} = 100k\Omega$                                                                 | -3%  | 1    | +3%  | MHz   |

## **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN} = 24V$ ,  $T_J = -40$ °C to +150°C, typical values are tested at  $T_J = 25$ °C, unless otherwise noted.

| Parameter                                | Symbol          | Condition                            | Min  | Тур | Max  | Units |

|------------------------------------------|-----------------|--------------------------------------|------|-----|------|-------|

| FREQ resistor                            | RFREQ           |                                      | 20   |     | 250  | kΩ    |

| SYNC frequency                           | fsync           |                                      | 0.4  |     | 5    | MHz   |

| Over-current protection (OCP) threshold  | Іоср            |                                      | -15% | 1.2 | +15% | А     |

| Over-current protection                  |                 | MPQ18913, $R_{FREQ} = 100k\Omega$    | -20% | 1   | +20% | ms    |

| (OCP) blanking time (6)                  | tocp            | MPQ18913-A, R <sub>FREQ</sub> =100kΩ | -20% | 20  | +20% | ms    |

| Short circuit protection (SCP) threshold | I <sub>SC</sub> | Fast off limit                       |      | 6   |      | А     |

| Licoup time (6)                          |                 | MPQ18913                             | -20% | 12  | +20% |       |

| Hiccup time (6)                          | tHICCUP         | MPQ18913-A                           | -20% | 120 | +20% | ms    |

| Dead time (DT) (6)                       |                 |                                      | -20% | 25  | +20% | ns    |

| 0 (1 1 1 1 1 (6)                         |                 | MPQ18913, $R_{FREQ} = 100$ kΩ        |      | 2   |      | ms    |

| Soft-start time (6)                      | tss             | MPQ18913-A, $R_{FREQ} = 100k\Omega$  |      | 20  |      | ms    |

| Thermal shutdown                         | T <sub>SD</sub> |                                      |      | 170 |      | °C    |

| Thermal shutdown hysteresis              | $\DeltaT_{SD}$  |                                      |      | 20  |      | °C    |

#### Note:

<sup>6)</sup> Derived from bench characterization. Not tested in production.

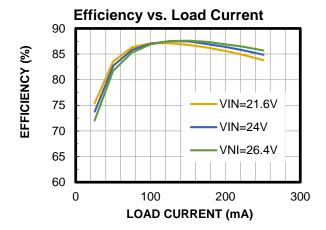

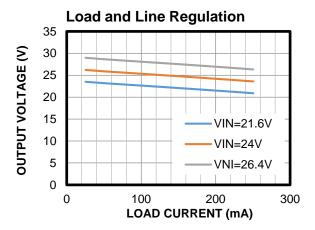

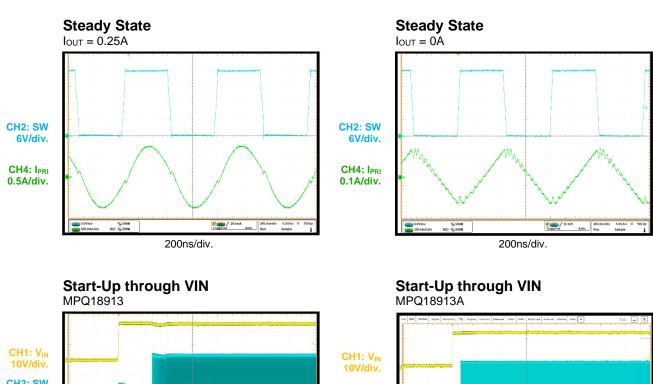

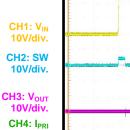

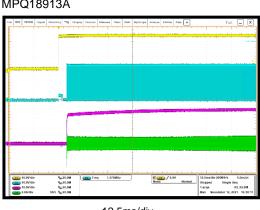

## **TYPICAL CHARACTERISTICS**

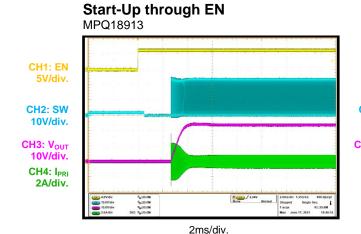

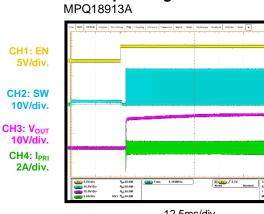

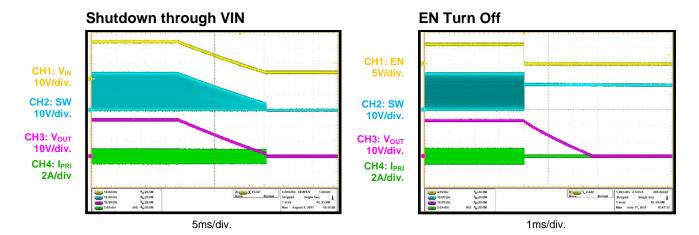

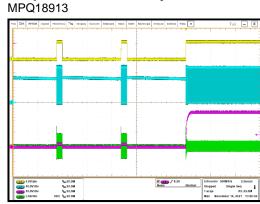

Performance curves and waveforms are tested on the evaluation board,  $V_{IN}$  = 24V,  $V_{OUT}$  = 24V,  $T_A$  = 25°C, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = 24V$ ,  $I_{OUT} = 0.25A$ ,  $T_A = 25$ °C, unless otherwise noted.

2A/div.

Start-Up through EN

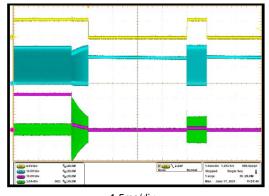

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 24V$ ,  $I_{OUT} = 0.25A$ ,  $T_A = 25$ °C, unless otherwise noted.

CH1:FLT

CH2: SW

10V/div.

CH3: Vout

10V/div.

CH4: I<sub>PRI</sub>

3A/div.

4V/div.

CH2: SW

10V/div.

CH3: V<sub>OUT</sub>

10V/div.

CH4: I<sub>PRI</sub>

3A/div.

## **Output Short Recovery**

## **FUNCTIONAL BLOCK DIAGRAM**

**Figure 1: Functional Block Diagram**

#### **OPERATION**

#### **Enable Control (EN/SYNC)**

The EN pin enables and disables the MPQ18913 power converter. Pull the EN voltage ( $V_{EN}$ ) above the start-up threshold to enable the MPQ18913. The device starts switching after a delay time. The device is disabled when  $V_{EN}$  falls below the shutdown threshold. The EN/SYNC pin can support up to 30V. For automatic start-up, connect EN/SYNC directly to the VIN pin.

Then EN/SYNC pin can also be used for external clock synchronization. Connect a clock with a 400kHz to 1.67MHz frequency to the EN/SYNC pin. The internal clock frequency scales to be 1x or 3x the external clock frequency while continuing to operate at a 50% duty cycle. The scale factor is set by the FREQ resistor (R<sub>FREQ</sub>).

| Scale Factor | f <sub>SW</sub> (MHz) | R <sub>FREQ</sub> (kΩ) |

|--------------|-----------------------|------------------------|

| 1            | 0.4 to 1.5            | 100                    |

| 3            | 1.5 to 5              | 33.2                   |

#### **Under-Voltage Lockout (UVLO)**

The MPQ18913 implements separate undervoltage lockout (UVLO) protection for the input VIN and VCC pins. The maximum input voltage ( $V_{IN}$ ) UVLO rising threshold can be as low as 4.9V to allow for start-up across the entire  $V_{IN}$  range. The FLT pin is always low during  $V_{IN}$  or  $V_{CC}$  UVLO.

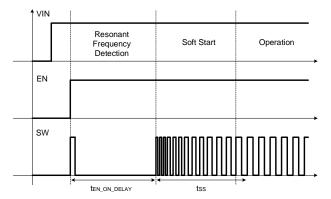

#### **Power Converter Soft Start (SS)**

During start-up, the switching frequency ( $f_{SW}$ ) is 2x the set frequency to limit the inrush current, and then gradually decreases to the set value.

Figure 2: Timing Diagram during Start-Up

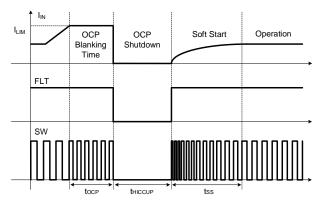

## Over-Current Protection (OCP) and Short-Circuit Protection (SCP)

Over-Current protection (OCP) is implemented by measuring the instantaneous current (I<sub>INSTANTANEOUS</sub>) on the low-side MOSFET (LS-FET). When the current exceeds the OCP threshold, f<sub>SW</sub> increases to limit the input current (I<sub>IN</sub>). If the over-current (OC) fault persists for longer than 1ms, the device stops switching, and automatically attempts to resume switching after a hiccup period (thiccup). The FLT pin is also pulled low. The FLT pin is released once the part attempts to start switching again.

Figure 3: Timing Diagram during an OC Fault

Short-circuit protection (SCP) is implemented by sensing I<sub>INSTANTANEOUS</sub> on high-side MOSFET (HS-FET). SCP protects the device from dead shorts between SW and GND.

#### Over-Voltage Protection (OVP)

When  $V_{\text{IN}}$  exceeds the over-voltage protection (OVP) rising threshold, the converter immediately stops switching, and FLT pulls low. Once  $V_{\text{IN}}$  falls below the OVP falling threshold with hysteresis, the part starts switching and FLT releases.

#### **Over-Temperature Protection (OTP)**

The MPQ18913 consistently monitors the die temperature to implement over-temperature protection (OTP). When the die temperature exceeds the thermal shutdown threshold, the part stops switching and pulls FLT low. Once the temperature falls below thermal shutdown threshold with hysteresis, the part starts up again and FLT releases.

#### **Fault Reporting (FLT)**

The FLT pin is an open-drain output that is pulled low if one of the following occur: V<sub>IN</sub> UVLO, V<sub>CC</sub> UVLO, OCP (in hiccup or latch-off mode), SCP (in hiccup or latch-off mode), OVP, and OTP.

Table 1: Fault Reporting Functions (7)

| EN   | V <sub>IN</sub>      | V <sub>cc</sub>          | FLT  |

|------|----------------------|--------------------------|------|

| -    | Powered              | Powered                  | High |

| -    | Not powered,<br>UVLO | Not powered,<br>UVLO     | Low  |

| Low  | Powered              | Not powered              | Low  |

| Low  | Not powered,<br>UVLO | Powered (8)              | Low  |

| High | Powered              | Not powered,<br>UVLO (8) | Low  |

| High | Not powered,<br>UVLO | Powered (8)              | Low  |

#### Note:

- 7) "Powered" means that the device is no longer in  $V_{\text{IN}}$  or  $V_{\text{CC}}$  UVLO, and an internal or external supply is applied. "Not powered" means the pin is in UVLO.

- 8) This operation can only occur when an external  $V_{\text{CC}}$  bias is applied. It is not recommended to power  $V_{\text{CC}}$  while  $V_{\text{IN}}$  is not powered, or to pull EN high while  $V_{\text{IN}}$  is powered and  $V_{\text{CC}}$  is not powered.

#### APPLICATION INFORMATION

#### **COMPONENT SELECTION**

#### **Selecting the Rectification Diodes**

It is recommended to use Schottky diodes, due to their low forward voltage drop and fast recovery, to minimize power loss and achieve zero voltage switching (ZVS).

The diodes' peak current (IPEAK) can be calculated with Equation (1):

$$I_{PEAK} \approx \Pi \times I_{LOAD}$$

(1)

## Selecting the Output Capacitor (Cout)

The output voltage ripple ( $\Delta V_{OUT}$ ) is determined by the powered device's capacitance and gate charge (e.g. SiC FET or IGBT). To maintain an acceptable  $\Delta V_{OUT}$ , choose a proper output capacitance (C<sub>OUT</sub>). C<sub>OUT</sub> for the two V<sub>OUT</sub> rails can be estimated with Equation (2):

$$C_{OUT\_POS\_RAIL} = C_{OUT\_NEG\_RAIL} \ge (QG / \Delta V_{OUT})$$

(2)

If each rail's capacitance should exceed 22µF, then the MPQ18913A should be selected due to its longer soft-start time (tss).

#### Selecting the Switching Frequency (f<sub>SW</sub>)

A higher f<sub>SW</sub> reduces the size of transformer, requires a larger transformer winding AC resistance, which limits the output power (Pout). Table 2 shows the recommended fsw.

Table 2: Recommended fsw

| P <sub>OUT</sub> (W) | f <sub>SW</sub> (MHz) |

|----------------------|-----------------------|

| ≤6                   | 0.4 to 0.75           |

| ≤3                   | 0.75 to 2             |

| ≤2                   | 1.5 to 5              |

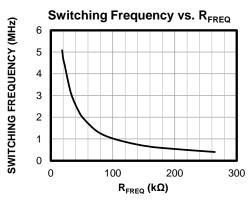

The resistor between FREQ and GND (R<sub>FREQ</sub>) sets f<sub>SW</sub> (see Figure 4).

Figure 4: Switching Frequency vs. RFREQ

#### Selecting the Transformer's Magnetizing Inductance

The magnetizing inductance (L<sub>M</sub>) target design value is based on achieving ZVS. L<sub>M</sub> can be calculated with Equation (3).

$$L_{M} = \frac{DT}{8 \times C_{SW} \times f_{SW}} = \frac{25ns}{8 \times 0.15nF \times f_{SW}}$$

(3)

If L<sub>M</sub> exceeds the target value, then there is not enough magnetizing current to achieve full ZVS. With a low input voltage and small parasitic capacitance on the converter, partial ZVS may not cause excessive thermal or electrical stress. If L<sub>M</sub> is below the design target value, there is more magnetizing current than required, which caused additional conduction loss in the FET and copper loss in the transformer. Given the small on resistance of the integrated FET and reasonable AC resistance of the transformer, the additional loss can be manageable.

L<sub>M</sub> should exceed 10x the leakage inductance to reduce V<sub>OUT</sub>'s sensitivity to the inductance and resonant capacitance variation.

#### Selecting the Resonant Capacitor (C<sub>R</sub>)

The resonant capacitance  $(C_R)$  can be calculated with Equation (4):

$$C_{R} = \frac{1}{4 \times \pi^{2} \times L_{R} \times f_{SW}^{2}}$$

(4)

Where  $L_R$  is the transformer leakage inductance, reflected to the primary side.

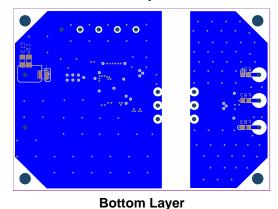

## PCB Layout Guidelines (9)

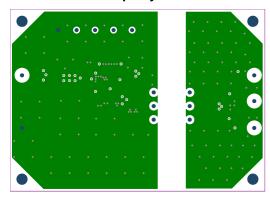

Efficient PCB layout is critical for stable operation. For the best results, refer to Figure 5 and follow the guidelines below:

- 1. Place the input capacitor, VCC capacitor, and BST capacitor as close to the corresponding pins as possible.

- 2. Place the R<sub>FREQ</sub> as close to the FREQ pin as possible.

- Connect R<sub>FREQ</sub> using short and direct traces. The other R<sub>FREQ</sub> terminal should be connected to AGND.

- 4. Connect AGND to power ground through a single-point connection.

- 5. Minimize the switching node areas on both the primary and secondary sides to reduce EMI.

- 6. Place the input filter on the bottom layer to reduce EMI.

#### Note:

9) The recommended layout is based on Figure 6 on page 14.

**Top Layer**

Mid-Layer 1

Mid-Layer 2

Figure 5: Recommended PCB Layout

## TYPICAL APPLICATION CIRCUIT

Figure 6: Typical Application Circuit (V<sub>IN</sub> = 24V, V<sub>OUT</sub> = +20V/-4V, 6W LLC, Start Up through VIN)

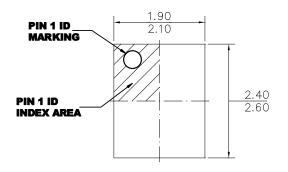

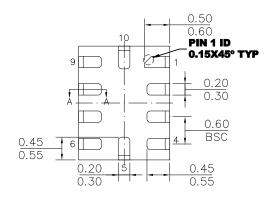

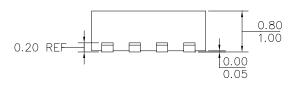

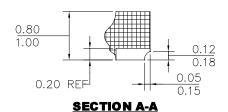

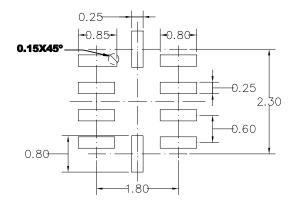

## **PACKAGE INFORMATION**

## QFN-10 (2mmx2.5mm)

**TOP VIEW**

**BOTTOM VIEW**

**SIDE VIEW**

RECOMMENDED LAND PATTERN

#### NOTE:

- 1) THE LEAD SIDE IS WETTABLE.

- 2) ALL DIMENSIONS ARE IN MILLIMETERS.

- 3) LEAD COPLANARITY SHALL BE 0.08 MILLIMETERS MAX.

- 4) JEDEC REFERENCE IS MO-220.

- 5) DRAWING IS NOT TO SCALE.

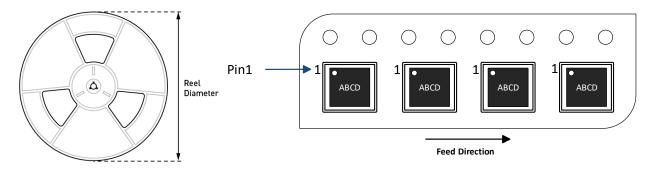

## **CARRIER INFORMATION**

| Part Number                                          | Package<br>Description | Quantity/<br>Reel | Quantity/<br>Tube | Quantity/<br>Tray | Reel<br>Diameter | Carrier<br>Tape<br>Width | Carrier<br>Tape<br>Pitch |

|------------------------------------------------------|------------------------|-------------------|-------------------|-------------------|------------------|--------------------------|--------------------------|

| MPQ18913GRPE-<br>AEC1-Z<br>MPQ18913GRPE-<br>A-AEC1-Z | QFN-10<br>(2mmx2.5mm)  | 5000              | N/A               | N/A               | 13in             | 12mm                     | 8mm                      |

## **REVISION HISTORY**

| Revision # | Revision Date | Description                                                                                                                                                                                                                                  | Pages Updated |  |

|------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|

| 1.0        | 5/24/2023     | Initial Release                                                                                                                                                                                                                              | -             |  |

| 1.01       | 7/18/2024     | Updated R3 and C6 to be in series in Typical Application circuit diagram                                                                                                                                                                     | 1, 14         |  |

|            |               | <ul> <li>Updated formatting for Equation (1)</li> <li>Updated "28" to "8" and "0.17nF" to "0.15nF" in Equation (3)</li> <li>Fixed formatting in Table 2, Figure 4, and Selecting the Transformer's Magnetizing Inductance section</li> </ul> | 12            |  |

**Notice:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.