## SD8568 内置晶振、高精度的的实时时钟芯片

### 1. 概述

SD8568 是一种具有标准 IIC 接口的实时时钟芯片, CPU 可使用该接口通过四位地址寻址来读写片内 16 字节寄存器的数据(包括时间寄存器、报警寄存器、控制寄存器等)。

SD8568 内置单路定时/报警中断输出, 报警中断时间最长可设置为一周。

SD8568 具有独立的频率脉冲输出脚。

### 2. 特性

- 低功耗: 0.4  $\mu$ A 典型值( $V_{DD}=3.0V$ ,  $T_a=25^{\circ}C$ )。

- 工作电压: 1.5V~5.5V; 计时电压: 1.0V~5.5V ; 工作温度: -40°C~+105°C。

- 标准 IIC 总线接口方式, 最高速度 400KHz (4.5V~5.5V)。

- 年、月、日、星期、时、分、秒的 BCD 码输入/输出, 并可通过独立的地址访问各时间寄存器。

- 闰年自动调整功能(从 2000 年~2099 年); 世纪位标识。

- 24 小时制式

- 内置星期、时、分、秒共 4 字节的报警数据寄存器, 每个报警寄存器的最高位为报警允许位。

- 三种中断均可选择从 INT 脚输出, 并具有两个中断标志位.

- 内置晶振, 常温高精度: 25°C< $\pm$ 5ppm(出厂精度)。

- 内置星期、日、时、分共 4 字节的报警数据寄存器, 每个报警寄存器的最高位为报警允许位; 报警中断功能时间范围最长设至 1 个月, 星期、日、时、分报警共有 16 种组合方式。

- 周期性频率中断输出脚 FREQ: 32768Hz、1024Hz、64Hz、1Hz 共四种方波脉冲。

- 自动重置的 8 位倒计时定时器, 可选的 4 种时钟源 (4096Hz、64Hz、1Hz、1/60Hz)。

- 内置 IIC 总线 0.5 秒自动复位功能(从 Start 命令开始计时), 保证时钟数据的有效性及可靠性, 避免 IIC 总线挂死问题。

- 内置时钟数据写保护功能, 避免对数据的误写操作, 可更好地保护时钟数据。

- 内置上电复位电路, 具上电和停振标志位 OSF。

- 内置电源稳压, 内部计时电压可低至 1.0V。

- 芯片管脚抗静电 (ESD)>4KV

- 芯片在兴威帆的评估板上可通过 4KV 的群脉冲(EFT) 干扰

- CMOS 工艺

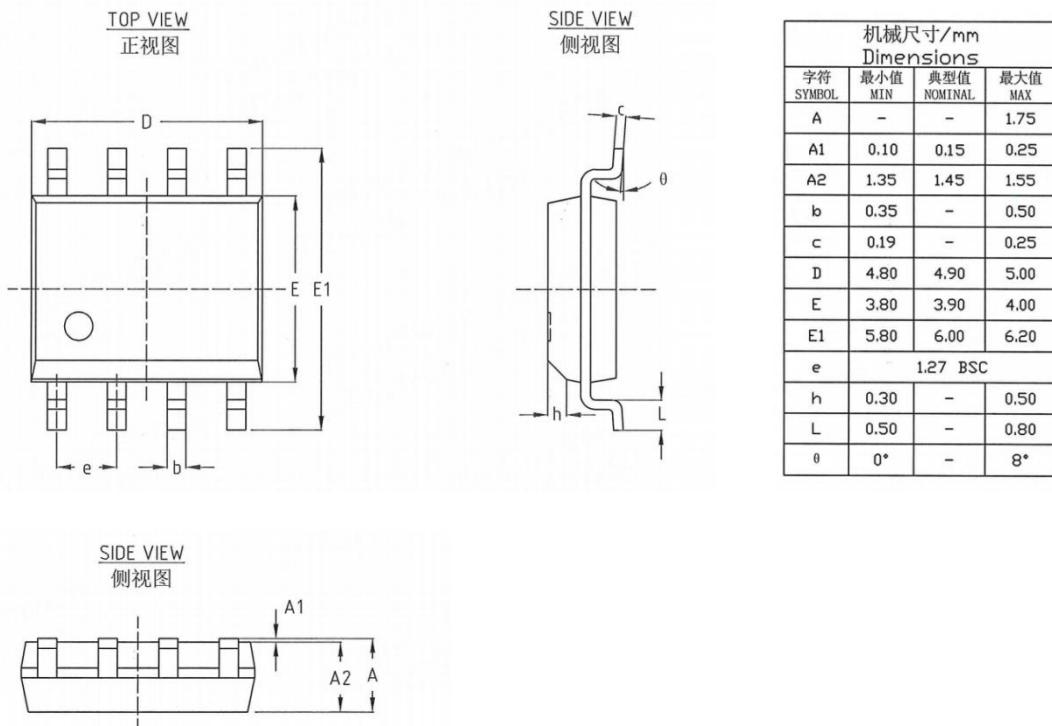

- 封装形式:SOP8 (150mil)

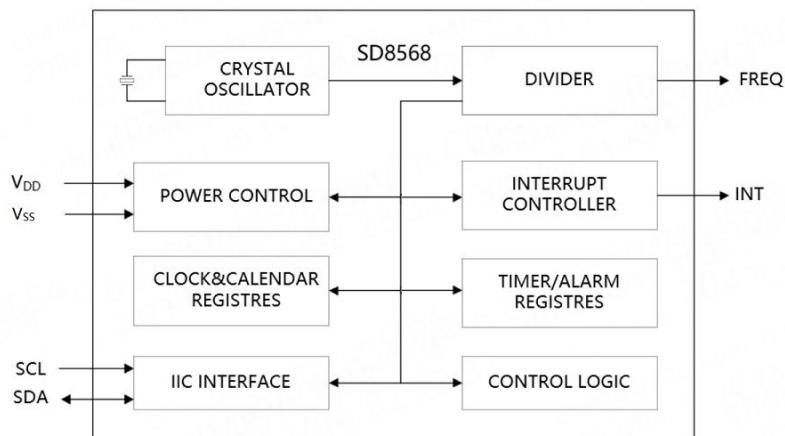

### 3. 原理框图

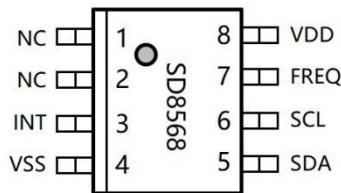

### 4. 管脚定义

封装形式:SOP8

表 1 SD8568 管脚功能表

| 脚号 | 名称              | 功能                                                                                            | 特征                 |

|----|-----------------|-----------------------------------------------------------------------------------------------|--------------------|

| 1  | NC              | 不与内部相连                                                                                        |                    |

| 2  | NC              | 不与内部相连                                                                                        |                    |

| 3  | INT             | 报警中断输出脚, 根据控制寄存器来设置其工作的模式, 它可通过重写控制寄存器来禁止.                                                    | N-沟道开路输出           |

| 4  | V <sub>SS</sub> | 负电源 (GND)                                                                                     |                    |

| 5  | SDA             | 串行数据输入/输出脚, 此管脚通常用一电阻上拉至 V <sub>DD</sub> , 并与其它漏极开路或集电器开路输出的器件通过线与方式连接.                       | N 沟道开路输出, CMOS 输入. |

| 6  | SCL             | 串行时钟输入脚, 由于在 SCL 上升/下降沿处理信号, 要特别注意 SCL 信号的上升/下降升降时间, 应严格遵守说明书, 与 SCL 相连的 MCU 端口最好设置为 CMOS 输出。 | CMOS 输入            |

| 7  | FREQ            | 频率输出脚                                                                                         | N-沟道开路输出           |

| 8  | V <sub>DD</sub> | 正电源                                                                                           | 1.5V~5.5V          |

## 5. 寄存器

### 5.1 寄存器列表

| 地址  | 寄存器段    | 寄存器名称  | BIT  |       |       |        |       |       |       |       | 数值范围<br>(十进制) | 复位值<br>(二进制) |

|-----|---------|--------|------|-------|-------|--------|-------|-------|-------|-------|---------------|--------------|

|     |         |        | D7   | D6    | D5    | D4     | D3    | D2    | D1    | D0    |               |              |

| 00H | 控制寄存器   | CTR1   | TEST | WRTC  | -     | ENTEST | TESTC | 0     | T1    | T0    | N/A           | 0000-1000    |

| 01H |         | CTR2   | 0    | 0     | 0     | IM     | INTAF | INTDF | INTAE | INTDE | N/A           | 0000-0000    |

| 02H | 时间寄存器   | 秒      | OSF  | S40   | S20   | S10    | S8    | S4    | S2    | S1    | 0-59          | 1XXX-XXXX    |

| 03H |         | 分钟     | -    | MN40  | MN20  | MN10   | MN8   | MN4   | MN2   | MN1   | 0-59          | XXXX-XXXX    |

| 04H |         | 小时     | -    | -     | H20   | H10    | H8    | H4    | H2    | H1    | 0-23          | XXXX-XXXX    |

| 05H |         | 日      | -    | -     | D20   | D10    | D8    | D4    | D2    | D1    | 1-31          | XXXX-XXXX    |

| 06H |         | 星期     | -    | -     | -     | -      | -     | W4    | W2    | W1    | 0-6           | XXXX-XXXX    |

| 07H |         | 月      | C    | -     | -     | M010   | M08   | M04   | M02   | M01   | 1-12          | 0XXX-XXXX    |

| 08H |         | 年      | Y80  | Y40   | Y20   | Y10    | Y8    | Y4    | Y2    | Y1    | 0-99          | XXXX-XXXX    |

| 09H | 时间报警寄存器 | 分钟报警   | EAMN | AMN40 | AMN20 | AMN10  | AMN8  | AMN4  | AMN2  | AMN1  | 0-59          | 1000-0000    |

| 0AH |         | 小时报警   | EAH  | -     | AH20  | AH10   | AH8   | AH4   | AH2   | AH1   | 0-23          | 1000-0000    |

| 0BH |         | 日报警    | EAD  | -     | AD20  | AD10   | AD8   | AD4   | AD2   | AD1   | 1-31          | 1000-0000    |

| 0CH |         | 星期报警   | EAW  | -     | -     | -      | -     | AW4   | AW2   | AW1   | 0-6           | 1000-0000    |

| 0DH | 控制寄存器   | CTR3   | FE   | -     | -     | -      | -     | -     | FS1   | FS0   | N/A           | 1000-0000    |

| 0EH |         | CTR4   | DE   | -     | -     | -      | -     | -     | TDS1  | TDS0  | N/A           | 0XXX-XX11    |

| 0FH |         | 倒计时定时器 | TD7  | TD6   | TD5   | TD4    | TD3   | TD2   | TD1   | TD0   | N/A           | 0000-0000    |

### 5.2 实时时钟数据寄存器(02H~08H)

实时时钟数据寄存器是 7 字节的存储器，它以 BCD 码方式存贮包括年、月、日、星期、时、分、秒的数据。

**年数据[08H 地址] (00~99)**：设置千年（20XX）的后两位数字（00~99），通过自动日历功能计至 2099 年。（注意：2000 年为闰年）

**月数据[07H 地址] (01~12)**：每月包含的天数通过自动日历功能来更改。

1,3,5,7,8,10,12: 1~31

4,6,9,11: 1~30

2(闰年): 1~29

2(普通): 1~28

其中月数据的最高位 C 为世纪位：C=0 指定世纪数为 20XX，C=1 指定世纪数为 19XX，“XX”为年数据 08H 中的值。当年寄存器中的值由 99 变为 00 时，世纪位 C 会从 1 变为 0。

**注意：**如 C=1，当读取月数据时，要屏蔽掉月的最高位。

**星期数据[06H 地址] (00~06)**：七进制计数器，00 对应星期天，01 对应星期一，依次类推。

**日数据[05H 地址] (01~31)**

**小时数据[04H 地址] (00~23)**：二十四小时制

**分数据[03H 地址] (00~59)**

**秒数据[02H 地址] (00~59)**

例如:

设置时间为 2006 年 12 月 20 日星期三 18 点 19 分 20 秒,则寄存器 03H~08H 的赋值应分别为 20H、19H、18H、20H、03H、12H、06H。

注:

1. 在上电复位时, 芯片内部不对实时时钟数据寄存器作清零或置位处理。

2. 当写实时时钟数据时(03H~08H),不可以单独对 7 个时间数据中的某一位进行写操作,否则可能会引起时间数据的错误进位,所以要修改其中某一个数据, 应一次性写入全部 7 个实时时钟数据。

3. 当芯片收到读实时时钟数据命令,则所有实时时钟数据被锁存(时钟走时并不受影响), 此功能可以避免时间数据的错读现象。

### 5.3 中断(01H、09H~FH 地址)

SD8568 有报警中断、频率中断和倒计时中断等 3 种不同的中断, 它们由控制寄存器 CTR1、CTR2、CTR3、CTR4 中的相关位来使能:

中断允许位、标志位及输出端口列表

| 序号 | 中断名   | 中断允许位            | 中断模式控制位<br>(0:单次; 1=周期性) | 中断标志位<br>(1=有中断,0=无中断) | 中断输出控制位<br>及输出脚<br>(1=允许,0=禁止) |

|----|-------|------------------|--------------------------|------------------------|--------------------------------|

| 1  | 报警中断  | EAW/EAD/EAH/EAMN | -                        | INTAF                  | INTAE, INT 脚                   |

| 2  | 频率中断  | FE               | -                        | 无                      | 无, FREQ 脚                      |

| 3  | 倒计时中断 | DE               | IM                       | INTDF                  | INTDE, INT 脚                   |

当报警中断发生时,置报警中断标志位 INTAF 为 1;当倒计时中断产生时, 置倒计时中断标志位 INTDF 为 1;频率中断没有标志位。标志位被置 1 后,需要手动清除。

报警中断和倒计时中断是以 INT 脚为输出脚,频率中断是以 FREQ 位输出脚。当报警中断和倒计时中断均被允许输出时, INT 脚输出的是两种中断的电平或脉冲。

#### (1) 报警中断

当 INTAE=1 时报警中断被允许输出, 报警中断何时发生由时间报警寄存器(09H~0CH)来确定。这其中 09H~0CH 依次用于存放报警时间的分钟、小时、日、星期数据, 除报警数据寄存器的最高位为该时间数据报警中断允许位以外, 报警寄存器的格式与实时时钟寄存器相同。

以分钟报警寄存器 09H 为例说明如下(其它小时、日、星期报警寄存器类同):

| BIT   | D7   | D6    | D5    | D4    | D3   | D2   | D1   | D0   |

|-------|------|-------|-------|-------|------|------|------|------|

| 位名(值) | EAMN | AMN40 | AMN20 | AMN10 | AMN8 | AMN4 | AMN2 | AMN1 |

EAMN 为分钟报警允许使能位: EAMN=0,分钟报警中断允许,EAMN=1, 分钟报警中断禁止。

时间报警允许的使能位是用于确定哪些时间报警寄存器(分钟、小时、日和星期等)需要与实时时钟寄存器之间作比较。当实时时钟运行时,一旦被允许的报警寄存器均与对应的实时时钟寄存器相匹配, 就会触发一次报警中断,同时报警中断标志位 INTAF 位被置“1”。

为清除报警中断,可通过写操作将控制寄存器 CTRL1 的 INTAF 位置“0”即可.

## (2) 频率中断

当 **FE=1** 时频率中断被允许; **FE=0** 时频率中断被禁止。

**FREQ** 为频率中断输出脚。频率中断没有标志位。

**FREQ** 脚输出频率中断由控制寄存器 **CTRL3** 中的 **FS1**、**FS0** 位来选择确定:

| 频率(Hz) | FS1 | FS0 |

|--------|-----|-----|

| 32768  | 0   | 0   |

| 1024   | 0   | 1   |

| 32     | 1   | 0   |

| 1      | 1   | 1   |

## (3) 倒计时中断

与倒计时中断相关的寄存器是 8 位的倒计时定时器, 当控制寄存器 **CTRL4** 中的位 **DE=1** 时倒计时中断被允许。

倒计时定时器的频率源由控制寄存器 **CTRL4** 中的位 **TDS1**、**TDS0** 来选定

| TDS1 | TDS0 | 定时器频率源(HZ) |

|------|------|------------|

| 0    | 0    | 4096       |

| 0    | 1    | 64         |

| 1    | 0    | 1          |

| 1    | 1    | 1/60       |

当 **DE=1** 且倒计时定时器写入一个八位自动重置的二进制数后, 倒计时定时器会按照 **TDS1**、**TDS0** 选定的频率时间来减一。每次当倒计时定时器为零时, 会置倒计时中断的标志位 (**控制寄存器 CTRL2** 中的位 **INTDF**) 为 1; 倒计时最长周期为 256 分钟。特别的, 当不使用倒计时定时器时, 为了降低功耗, 请将 **TD1**、**TDO** 均设置为 1。

当 **INTDE=1** 即允许倒计时中断从 **INT** 脚输出。该倒计时中断有两种模式, 即单事件中断和周期性中断, 模式的选定由控制寄存器 **CTRL2** 中的倒计时中断模式位 **IM** 的值来定:

| IM 位 | 倒计时中断模式 | INT 脚                              |

|------|---------|------------------------------------|

| 0    | 单事件中断   | 输出低电平直至 <b>INTDF</b> 位清零           |

| 1    | 周期性中断   | 输出周期性脉冲直至中断允许位清零<br>(脉冲低电平时间请参见下表) |

倒计时中断周期性脉冲低电平时间(S) (DE=1, INTDE=1, IM=1)

| 定时器频率源(HZ) | n=1    | n>1    |

|------------|--------|--------|

| 4096       | 1/8192 | 1/4096 |

| 64         | 1/128  | 1/64   |

| 1          | 1/64   | 1/64   |

| 1/60       | 1/64   | 1/64   |

注: n 为倒计时寄存器 **OFH** 所赋初值。

当设置 **DE=1**、**INTDE=1**、**IM=0** 时, 即允许倒计时中断的低电平从 **INT** 脚输出; 置 **INTDF=0** 时 **INT** 脚输出变为高电平直到下一次倒计时中断 **INT** 脚再次变为低电平; 当设置 **DE=1**、**INTDE=1**、**IM=1** 时, 则从 **INT** 脚输出低电平时间如上表的连续脉冲。

当设置 **INTDE=0** 时倒计时中断被禁止或复位。

**特别的:**当重新配置倒计时中断时,需要复位倒计时计数器,即置 **INTDE=0**,然后再置 **INTDE=1**,才可以启用新的倒计时中断。

## 5.4 其它控制/状态位

- (1) TEST、TESTC、ENTEST、T1、T0 位：为 RTC 内部测试位，除 TESTC=1 其它位默认值均为 0。

- (2) OSF：上电和停振标志位，为读/写位。当初次上电或发生停振，该标志置 1。该位置 1 时，并不复位内部寄存器，用户可以通过程序清除该标志位为 0。

- (3) WRTC 位：为 RTC 寄存器写保护状态指示位，为只读位。读 WRTC 位可以判断当前 RTC 芯片写保护处于何种状态：WRTC=1 写保护打开，WRTC=0 写保护关闭。上电该位默为 0，RTC 处于写保护关闭状态，用户可以对 RTC 任意寄存器进行写操作。

写保护打开时，除了 0EH 寄存器的 Bit6~Bit2 以外，0H~0FH 寄存器均不能被写入。

通过以下步骤 a 打开写保护位功能，步骤 b 关闭写保护位功能。

- a、向 0EH 寄存器的 Bit6~Bit2 依次写入 b00000、b10101、b01010、b10111；

- b、向 0EH 寄存器的 Bit6~Bit2 依次写入 b00000、b11100、b00011、b01110。

注意以上数据均需要单字节写入 0EH 寄存器。

## 6.串行 IIC 接口

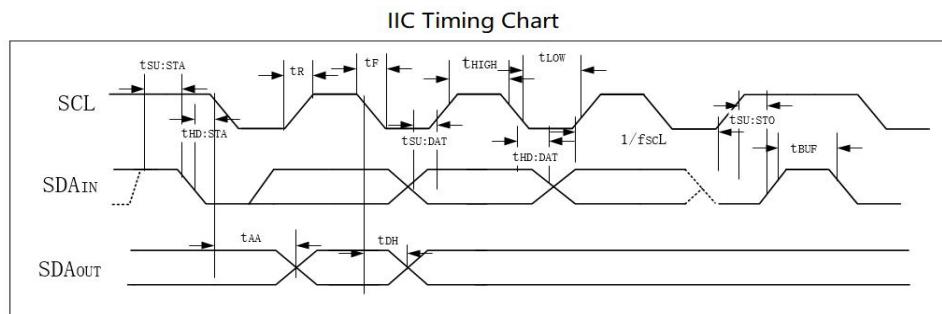

6.1 SD8568 通过两线式 IIC 串行接口方式接收各种命令并读写数据。两线式串行 IIC 接口方式描述如下：

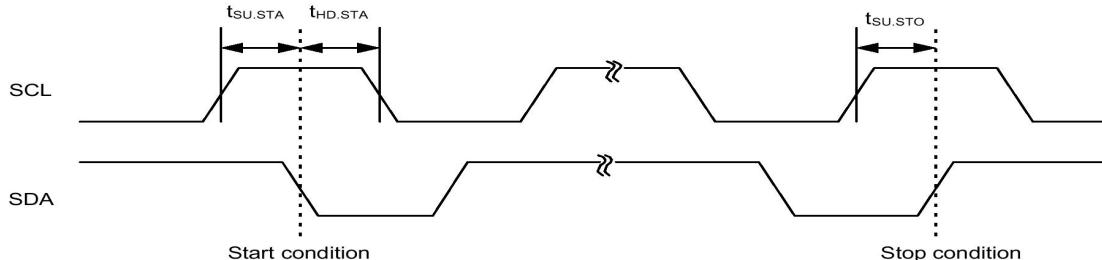

(1) 开始条件

当 SCL 处于高电平时，SDA 由高电平变成低电平时构成一个开始条件，对 SD8568 的所有操作均必须由开始条件开始。

(2) 停止条件

当 SCL 处于高电平时，SDA 由低电平变成高电平时构成一个停止条件，此时 SD8568 的所有操作均停止，系统进入待机状态。

实时时钟的串行接口

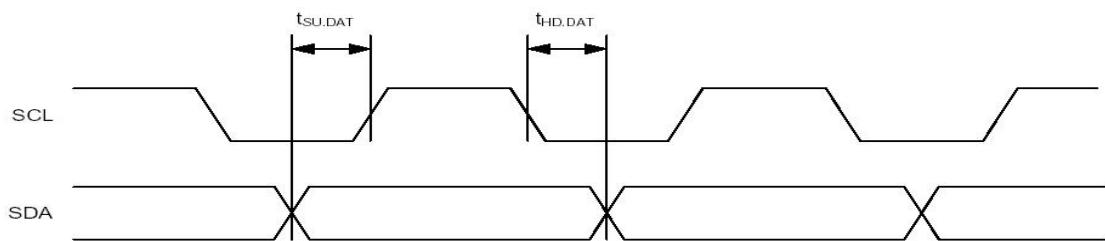

(3) 数据传输

当 SCL 为低电平，且 SDA 线电平变化时，则数据由 CPU 传输给 SD8568(高位在前、低位在后,下同)；当 SCL 为高电平，且 SDA 线电平不变时，则 CPU 读取 SD8568 发送来的数据；当 SCL 为高电平，且 SDA 电平变化时，SD8568 收到一个开始或停止条件。

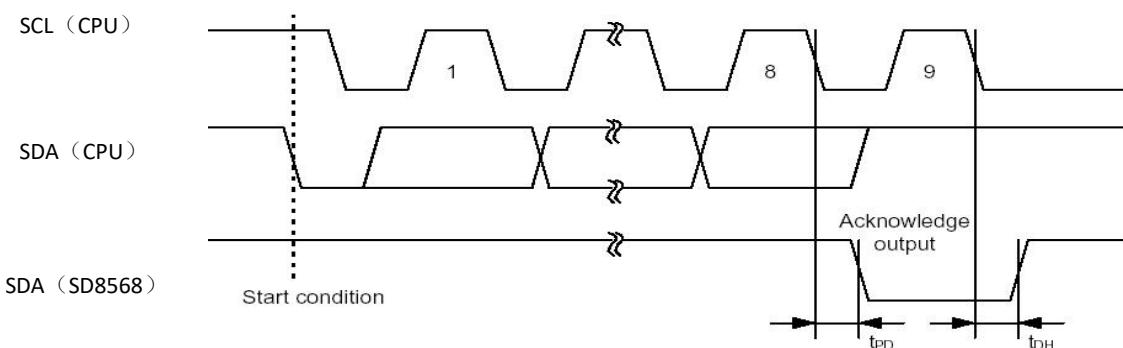

实时时钟数据传输时序

## (4) 确认

数据传输以 8 位序列进行。SD8568 在第九个时钟周期时将 SDA 置位为低电平，即送出一个确认信号（Acknowledge bit, 以下简称“ACK”），表明数据已经被其收到。

图 5 实时时钟确认信号

## 6.2 数据/指令传输格式

当 CPU 发出开始条件与实时时钟建立连接后，CPU 首先通过 SDA 总线连续输出 7 位器件地址和 1 位读/写指令来唤醒 SD8568.

## (1) 器件代码:

| BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|------|------|------|------|------|------|------|------|

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | R/W  |

其中高 7 位 BIT7~BIT1 称“器件代码”，它代表实时时钟的器件地址，固定为“1010001”；BIT0 为读/写位，“1”为读操作，“0”为写操作。

## (2) 数据传输格式:

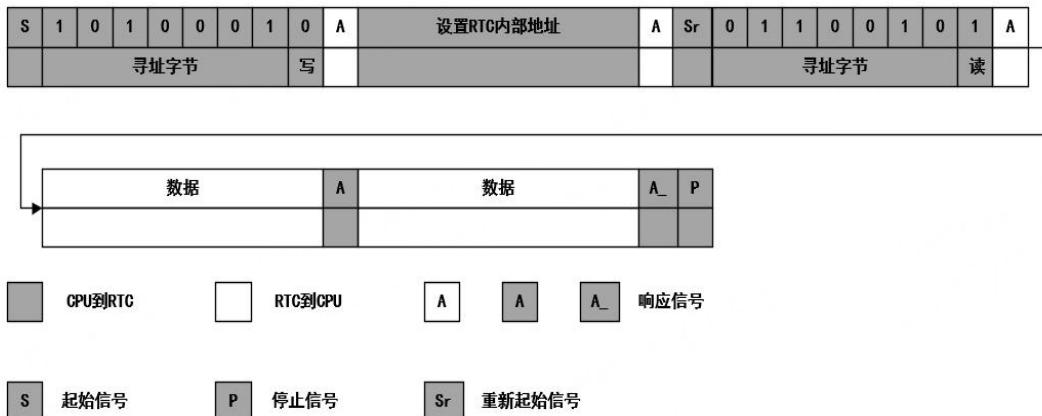

在数据发送/接收时停止信号到来时，将结束其数据传输。如果只有开始信号，而没有结束信号，接着重新产生起始信号，则还要重新设置器件代码(在传输方向需要改变时，就用这种传输方式，如下面的读数据方式 1)。

主设备向从设备写入数据过程图

|   |   |   |   |   |   |   |   |   |   |           |   |    |   |   |

|---|---|---|---|---|---|---|---|---|---|-----------|---|----|---|---|

| S | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | A | 设置RTC内部地址 | A | 数据 | A | P |

|   |   |   |   |   |   |   |   |   |   | 寻址字节      | 写 |    |   |   |

主设备向从设备直接读取数据过程图

|   |   |   |   |   |   |   |   |   |   |      |   |    |   |   |

|---|---|---|---|---|---|---|---|---|---|------|---|----|---|---|

| S | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | A | 数据   | A | 数据 | A | P |

|   |   |   |   |   |   |   |   |   |   | 寻址字节 | 读 |    |   |   |

数据传输时改变其传输方向过程图

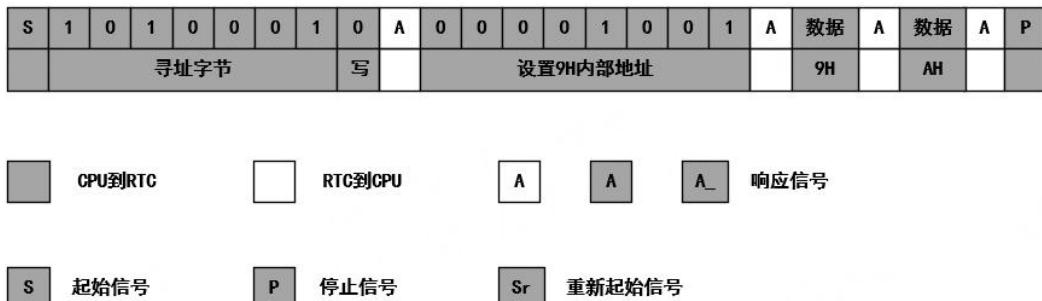

## (3)SD8568 数据传输的写模式

- . 先送 7 位器件地址(1010001),第 8 位送入写命令("0"), 第 9 位是 SD8568 的响应位(ACK),SD8568 进入写状态;

- . 接下来一个字节确定为 SD8568 的内部地址(0H~FH), 第 9 位是 SD8568 的响应位;

- . 开始写数据,每写完 1 个字节的数据之后,都经过 1 位的响应信号才能写下 1 字节的数据;如果要结束写数据过程,则在 ACK 后送出停止命令即可.

SD8568 写数据示例(向 9H,AH 地址写数据):

- 特别注意:**

1. 除了 5 个写允许位, 对寄存器(0H~FH)的写操作必须确认芯片处于写允状态,否则写无效.

2. 写时间同步: 每次对实时时间秒寄存器的写操作时, 当秒数据的 8 个 bit 完全写入并收到 ACK 信号后, 就会对秒以下的内部计数器清零, 使时间同步。

3. 从当前地址开始,每次读写完一个字节地址自动加 1 直到 FH,读写完 FH 后地址自动加 1 后为 0H.

4. 为了提高数据的可靠性, 当写完成后, 应将芯片置于写禁止状态。

5. 有关写实时时间数据的位数的特别要求请参见(5.2.注 2)

## (4)SD8568 数据传输的读模式

SD8568 有两种读数据方法:

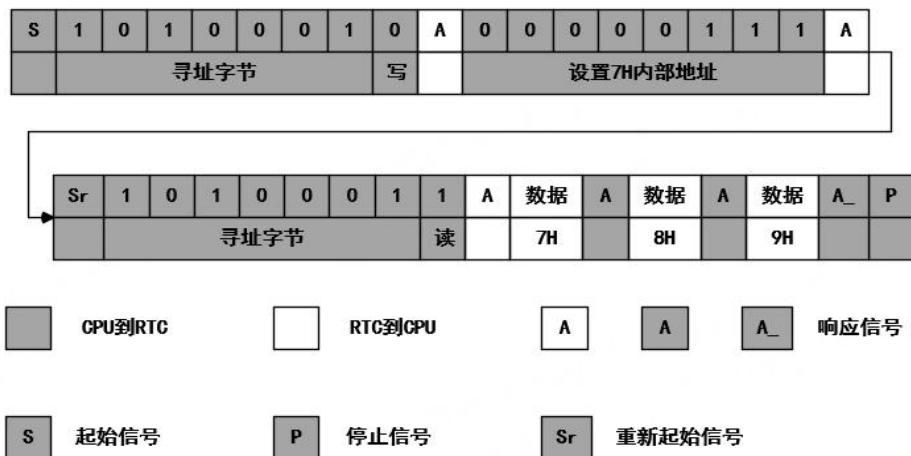

I)读方法 1:从指定的内部地址中读取数据

- . 与写模式的前两步一样;

- . 重新发出开始命令以改变两线接口数据传输方向;

- . 再送 7 位器件地址(1010001),第 8 位送入读命令("1"), 第 9 位是 SD8568 的响应位(ACK),SD8568 进入读状态;

- . 开始读数据,每读完 1 个字节的数据之后,CPU 都要送出 1 位的响应信号(ACK,低电平)才能读下 1 字节的数据;如果想要结束读数据过程,则 CPU 要送出 1 位的响应信号(ACK\_,高电平), ACK\_后送出停止命令即可.

SD8568 读数据方法 1 示例(从 7H~9H 地址读取数据):

## II) 读方法 2:直接读取数据(从当前内部地址开始)

- . 开始信号后,先送 7 位器件地址(1010001),第 8 位送入读命令("1"), 第 9 位是 SD8568 的响应位(ACK),SD8568 进入读状态;

- . 每读完 1 个字节的数据之后,CPU 都要送出 1 位的响应信号(ACK,低电平)才能读下 1 字节的数据;如果想要结束读数据过程,则 CPU 要送出 1 位的响应信号(ACK\_,高电平), ACK\_后送出停止命令即可. (同样的,每次读写完一个字节地址自动加 1 直到 FH,读写完 FH 后地址自动加 1 后为 OH.)

SD8568 读数据方法 2 示例(从当前内部地址开始读取数据):

## (5) SD8568 在特殊条件下的数据传输

为了保证读写数据的有效性,SD8568 的两线通信开始到结束仅在此 0.5S 秒之内,如此可避免总线挂死的现象。

因此在 SD8568 中, IIC 通信方式会在第一个开始信号 (START)到来之后的 0.5 秒之内自动终止本次通信。所以,要注意: 从开始信号进行读/写数据,直到停止信号, 读/写操作过程必须在 0.5 秒之内完成。

## 7. 上电复位

芯片内部具有上电复位电路：当芯片第一次加上电源时，芯片内部复位。复位操作对内部部分寄存器进行置初值但不包括实时时钟数据寄存器。

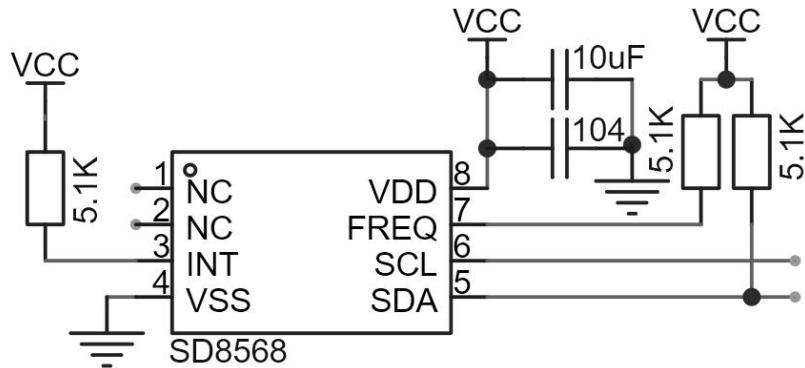

## 8. 应用参考电路

特别注意：在 PCB 排版时，SD8568 的周围及背面不要排布大电流、强干扰线路。

## 9. 极限参数

$V_{DD}$  、 SCL、 SDA 和 INT 引脚上的电压（相对于地） ..... -0.5V 至 7.0V

贮存温度 ..... -65°C 至 +150°C

引线温度（焊接，10 秒） ..... 260°C

注：强度超出所列的极限参数可能导致器件的永久性损坏。这些仅仅是极限参数，并不意味着在极限条件下或在任何其它超出推荐工作条件所示参数的情况下器件能有效地工作。延长在极限参数条件上的工作时间会影响器件的可靠性。

## 10. 直流特性

| SYMBOL       | PARAMETER                     | CONDITIONS                  | MIN | TYP | MAX | UNITS   | NOTES |

|--------------|-------------------------------|-----------------------------|-----|-----|-----|---------|-------|

| $V_{DD}$     | Main Power Supply             |                             | 1.5 |     | 5.5 | V       |       |

| $I_{DD1}$    | Supply Current                | $V_{DD}=5V$                 |     | 0.6 | 1.0 | $\mu A$ |       |

|              |                               | $V_{DD}=3V$                 |     | 0.4 | 0.8 | $\mu A$ |       |

| $I_{DD2}$    | Supply Current win IIC Active | $V_{DD}=5V$                 |     | 40  | 120 | $\mu A$ |       |

| $I_{L1}$     | Input Leakage Current On SCL  |                             |     | 100 |     | nA      |       |

| $I_{LO}$     | I/O Leakage Current On SDA    |                             |     | 100 |     | nA      |       |

| INT $V_{OL}$ | Output Low Voltage            | $V_{DD}=5V$<br>$I_{OL}=2mA$ |     | 0.4 |     | V       |       |

| $T_{ri}$     | $V_{DD}$ rise time            | 0V rise to $V_{DD}$         |     |     | 3   | s       |       |

## 11. 交流特性

| PARAMETER                                                                         | CONDITIONS                                                                                                                             | Standard Mode<br>(f <sub>SCL</sub> =100kHz) |     |                      | Fast Mode<br>(f <sub>SCL</sub> =400kHz) |     |                      | UNITS |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----|----------------------|-----------------------------------------|-----|----------------------|-------|

|                                                                                   |                                                                                                                                        | MIN                                         | TYP | MAX                  | MIN                                     | TYP | MAX                  |       |

| f <sub>SCL</sub> SCL frequency                                                    |                                                                                                                                        |                                             |     | 100                  |                                         |     | 400                  | kHz   |

| V <sub>L</sub> SDA and SCL input buffer LOW voltage                               |                                                                                                                                        | -0.3                                        |     | 0.2×V <sub>DD</sub>  | -0.3                                    |     | 0.2×V <sub>DD</sub>  | V     |

| V <sub>H</sub> SDA and SCL input buffer HIGH voltage                              |                                                                                                                                        | 0.8×V <sub>DD</sub>                         |     | V <sub>DD</sub> +0.3 | 0.8×V <sub>DD</sub>                     |     | V <sub>DD</sub> +0.3 | V     |

| Hysteresis SDA and SCL input buffer hysteresis                                    |                                                                                                                                        | 0.05×V <sub>DD</sub>                        |     |                      | 0.05×V <sub>DD</sub>                    |     |                      | V     |

| V <sub>OL</sub> SDA output buffer LOW voltage sinking 2mA                         |                                                                                                                                        |                                             | 0.4 |                      |                                         | 0.4 |                      | V     |

| C <sub>pin</sub> SDA and SCL pin capacitance                                      | T <sub>A</sub> =25 °C f=1MHZ V <sub>DD</sub> =5V V <sub>IN</sub> =0V V <sub>OUT</sub> =0V                                              |                                             |     | 10                   |                                         |     | 10                   | pF    |

| t <sub>IN</sub> Pulse width suppression time at SDA and SCL inputs                |                                                                                                                                        |                                             |     | 100                  |                                         |     | 50                   | ns    |

| t <sub>AA</sub> SCL falling edge to SDA output data valid                         | SCL falling edge crossing 30%of V <sub>DD</sub> until SDA exits the 30%to 70%of V <sub>DD</sub> window                                 |                                             |     | 900                  |                                         |     | 900                  | ns    |

| t <sub>BUF</sub> Time the bus must be free before the start of a new transmission | SDA crossing 70%of V <sub>DD</sub> during a STOP condition, to SDA crossing 70%of V <sub>DD</sub> during the following START condition | 4700                                        |     |                      | 1300                                    |     |                      | ns    |

| t <sub>LOW</sub> Clock LOW time                                                   | Measured at the 30% of V <sub>DD</sub> crossing                                                                                        | 4700                                        |     |                      | 1300                                    |     |                      | ns    |

| t <sub>HIGH</sub> Clock HIGH time                                                 | Measured at the 70% of V <sub>DD</sub> crossing                                                                                        | 4000                                        |     |                      | 600                                     |     |                      | ns    |

| t <sub>SU:STA</sub> START condition setup time                                    | SCL rising edge to SDA falling edge Both crossing 70% of V <sub>DD</sub>                                                               | 4700                                        |     |                      | 600                                     |     |                      | ns    |

| t <sub>HD:STA</sub> START condition hold time                                     | From SDA falling edge crossing 30% of V <sub>DD</sub> to SCL falling edge crossing 70% of V <sub>DD</sub>                              | 4000                                        |     |                      | 600                                     |     |                      | ns    |

| t <sub>SU:DAT</sub> Input data setup time                                         | From SDA exiting the 30% to 70% of V <sub>DD</sub> window ,to SCL rising edge crossing 30% of V <sub>DD</sub>                          | 250                                         |     |                      | 100                                     |     |                      | ns    |

| t <sub>HD:DAT</sub> Input data hold time                                          | From SCL falling edge crossing 30% of V <sub>DD</sub> to SDA entering the 30% to 70%of V <sub>DD</sub> window                          | 0                                           |     |                      | 0                                       |     |                      | ns    |

| t <sub>SU:STO</sub> STOP condition setup time                                     | From SCL rising edge crossing 70% of V <sub>DD</sub> ,to SDA rising edge crossing 30% of V <sub>DD</sub>                               | 4000                                        |     |                      | 600                                     |     |                      | ns    |

| t <sub>DH</sub> Output data hold time                                             | From SCL falling edge crossing 30% of V <sub>DD</sub> ,until SDA enters the 30% to 70% of V <sub>DD</sub> window.                      | 0                                           |     |                      | 0                                       |     |                      | ns    |

| t <sub>R</sub> SDA and SCL rise time                                              | From 30% to 70% of V <sub>DD</sub>                                                                                                     |                                             |     | 1000                 |                                         |     | 300                  | ns    |

| t <sub>F</sub> SDA and SCL fall time                                              | From 70% to 30% of V <sub>DD</sub>                                                                                                     |                                             |     | 300                  |                                         |     | 300                  | ns    |

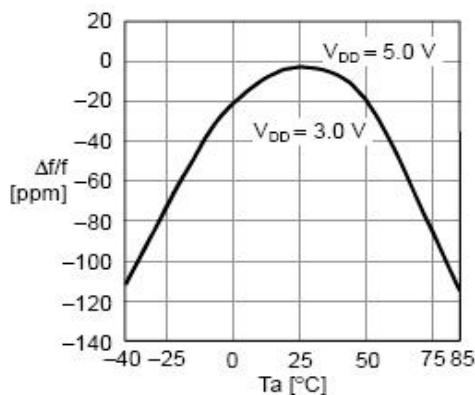

## 12. 频率误差&温度关系曲线

## 13. 封装尺寸 (unit:mm)

SD8568 SOP8 封装尺寸图

备注： SD8568 为湿敏三级 (MSL3) 封装, SOP8 2500PCS 真空盘带包装。

## ■ 编后语

感谢您阅读本资料。由于经验和水平的欠缺，本文难免有错误和遗漏。如果您在使用过程中发现错误或不恰当的地方，请拨打电话：0755-83246178 或请 E-mail：support@whwave.com.cn, 我们将尽快予以答复。

谢谢您的支持与合作！

注：

本资料中的内容如有变化，恕不另行通知。

本资料提供的应用线路及程序仅供参考，本公司不承担由此而引起的任何损失。

由于本公司产品不断更新和提高，希望您经常与本公司联系，以索取最新资料。

本公司不承担在任何使用过程中引起的侵犯第三方专利和其它权利的责任。

注：本文档受中国版权法保护，非授权禁止拷贝、复制、引用或传播

(SD 及 WAVE 均为我公司注册商标)

深圳市兴威帆电子技术有限公司