# 1.5 $\Omega$ , Low Voltage SPDT Analog Switch

#### Descriptions

The FSW3157 is a single, bidirectional, singlepole/ double-throw (SPDT) CMOS analog switch that is designed to operate from a single 1.5V to 5.5V supply. It features high-bandwidth (-3dB @600MHz) and low on-resistance (1.5 $\Omega$  TYP), Targeted applications for audio switching.

The FSW3157 features guaranteed on-resistance matching between switches and guaranteed onresistance flatness over the signal range. This ensures excellent linearity and low distortion when switching audio signals.

The FSW3157 is available in Green SOT23-6 and SOT363 package.

#### Features

- Supply Voltage Range: 1.5V to 5.5V

- On-Resistance:  $1.5\Omega$  (TYP) When A= 5V

- 1.8V Logic Compatible Control Pin

- A Overrides VCC to Achieve True Isolation Even When Supply Is Dead

- Low Quiescent Current (<2uA) With Very Wide Supply Range (1.5V ~ 5.5V)

- High Bandwidth: -3dB @600MHz

- ESD Tolerance: 2kV HBM

- Available in Green SOT23-6 and SOT363 Package

#### **Applications**

- Audio, Video, UART, USB2.0 Signal and Supply Routing

- Portable Instrumentation

- Battery-Operated Equipment

- Computer Peripherals

- Cell Phones

- PDAs

- MP3s

### Order information

| Mode    | Package | Specified Temperature range | Ordering Number    | Packing Option     |  |

|---------|---------|-----------------------------|--------------------|--------------------|--|

| EGW2157 | SOT23-6 | -40°C to +85°C              | FSW3157YSOT236G/TR | Tape and Reel,3000 |  |

| FSW3157 | SOT363  | -40°C to +85°C              | FSW3157YSOT363G/TR | Tape and Reel,3000 |  |

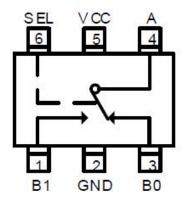

# **Pin Configuration**

| Pin# | Pin Name | Description                                  |  |

|------|----------|----------------------------------------------|--|

| 1    | B1       | Analog/Digital Signal Port (Normally open)   |  |

| 2    | GND      | Ground                                       |  |

| 3    | B0       | Analog/Digital Signal Port (Normally closed) |  |

| 4    | A        | Common Signal Port                           |  |

| 5    | VCC      | Single Power Supply                          |  |

| 6    | SEL      | Logic Input Control                          |  |

# **Function Table**

| Logic Input | Function |

|-------------|----------|

| SEL=0       | B0=A     |

| SEL=1       | B1=A     |

# Absolute Maximum Ratings<sup>(1)</sup>

| Parameter                                                     | Symbol           | Value           | Unit |

|---------------------------------------------------------------|------------------|-----------------|------|

| Supply Voltage                                                | V <sub>CC</sub>  | $-0.3 \sim 6.5$ | V    |

| Control Input Voltage                                         | V <sub>SEL</sub> | -0.3 ~ 6.5      | V    |

| Continuous Current Through A, B0, B1                          |                  | $\pm 100$       | mA   |

| Peak Current Through A, B0, B1 (pulsed at 1ms 50% duty cycle) |                  | $\pm 200$       | mA   |

| Storage Temperature Range                                     | T <sub>STG</sub> | -55 ~ 150       | °C   |

| Junction Temperature under Bias                               | TJ               | 150             | °C   |

| Lead Temperature (Soldering, 10 seconds)                      | TL               | 260             | °C   |

| Thermal resistance                                            | R <sub>0JA</sub> | 350             | °C/W |

#### Note:

1. "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied.

### Recommend operating ratings

| Parameter                | Symbol           | Value         | Unit |  |

|--------------------------|------------------|---------------|------|--|

| Supply Voltage Operating | V <sub>CC</sub>  | 1.5 ~ 5.5     | V    |  |

| Control Input Voltage    | V <sub>SEL</sub> | -0.3 ~ 5.5 V  | V    |  |

| Input Signal Voltage     | V <sub>A</sub>   | -0.3 ~ 5.5    | V    |  |

| Operating Temperature    | T <sub>A</sub>   | $-40 \sim 85$ | °C   |  |

#### **Electrical Characteristics**

(T<sub>A</sub>=25°C, VCC=3.3V, unless otherwise specified)

| Parameter                                  | Symbol             | conditions                                                      | Min. | Тур. | Max       | Unit |

|--------------------------------------------|--------------------|-----------------------------------------------------------------|------|------|-----------|------|

| DC CHARACTERISTICS                         |                    |                                                                 |      |      |           |      |

| T . 1 . 1 . 1 . 1                          |                    | VCC=3.3~5.5V                                                    | 1.6  |      |           | V    |

| Input logic high level                     | VIH                | VCC=1.5~3.3V                                                    | 1.4  |      |           | V    |

| T (1 ' 1 1 1                               | <b>X</b> 7         | VCC=3.3~5.5V                                                    |      |      | 0.6       | V    |

| Input logic low level                      | VIL                | VCC=1.5~3.3V                                                    |      |      | 0.4       | V    |

| Supply quiescent current                   | Icc                | I <sub>A</sub> =0, V <sub>SEL</sub> =0 or V <sub>SEL</sub> =VCC |      |      | 1.0       | uA   |

| т 'т ',                                    | т                  | I <sub>A</sub> =0, VCC=4.5V                                     |      | 1.0  |           |      |

| Increase in $I_{CC}$ per input             | I <sub>CCT</sub>   | V <sub>SEL</sub> >1.8 or V <sub>SEL</sub> <0.5                  |      |      | 1.0       | uA   |

| Off state leakage from A to B0             | т                  |                                                                 |      |      | 125       |      |

| (or B1)                                    | I <sub>A</sub>     | $V_A = 5.5V$ , $V_{B0(or B1)} = 0V$                             |      |      | $\pm 3.5$ | uA   |

|                                            | R <sub>ON1</sub>   | $V_A=0 \sim 1.5V$ ,                                             |      |      | 7.5       | Ω    |

|                                            | R <sub>ON2</sub>   | $V_A = 1.5 \sim 2.0 V$                                          |      |      | 3.5       | Ω    |

| On-Resistance                              | R <sub>ON3</sub>   | $V_A=2.0 \sim 2.5 V$                                            |      |      | 3         | Ω    |

|                                            | R <sub>ON4</sub>   | $V_A=2.5\sim4.0V$                                               |      |      | 2.5       | Ω    |

|                                            | R <sub>FLAT1</sub> | $V_A\!\!=\!\!0\sim 0.5V$                                        |      | 0.7  |           | Ω    |

|                                            | R <sub>FLAT2</sub> | $V_A = 0.5 \sim 2.0 V$                                          |      | 0.5  |           | Ω    |

| On-Resistance Flatness                     | R <sub>FLAT3</sub> | $V_A\!\!=\!\!2.0\sim\!4.0V$                                     |      | 1.6  |           | Ω    |

|                                            | R <sub>FLAT4</sub> | $V_A = 4.0 \sim 5.5 V$                                          |      | 0.3  |           | Ω    |

| On-Resistance<br>Matching Between Channels | ΔRON               | V <sub>A</sub> =0~5.5V                                          |      | 0.1  | 0.2       | Ω    |

| AC CHARACTERISTICS                         | I                  |                                                                 |      |      |           |      |

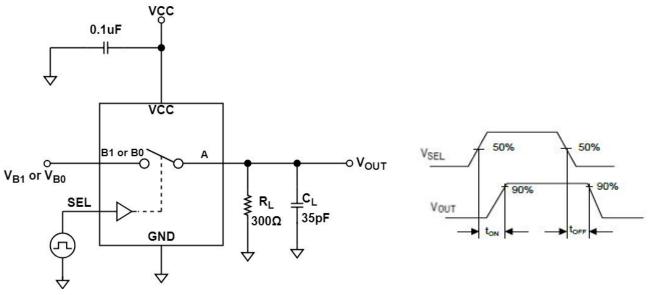

| Turn-On Time                               | Ton                | V <sub>A</sub> =1.5V, C <sub>L</sub> =35pF, RL=50Ω              |      | 200  |           | nS   |

| Turn-Off Time                              | T <sub>OFF</sub>   | V <sub>A</sub> =1.5V, C <sub>L</sub> =35pF, R <sub>L</sub> =50Ω |      | 200  |           | nS   |

| Break-Before-Make time                     | T <sub>BBM</sub>   | V <sub>A</sub> =1.5V, C <sub>L</sub> =35pF, R <sub>L</sub> =50Ω |      | 500  |           | nS   |

| -3dB Bandwidth                             | BW                 | $R_L=50\Omega, C_L=0pF$                                         |      | 600  |           | MHZ  |

|                                            | OIDD               | $F=1KHz, R_L=50\Omega$                                          |      | -81  |           | dB   |

| Off isolation                              | OIRR               | $F=10KHz, R_L=50\Omega$                                         |      | -80  |           | dB   |

|                           |       |                                       |  | _   |  | ···· |

|---------------------------|-------|---------------------------------------|--|-----|--|------|

| Crosstalk                 | Xtalk | $F=1KHz, R_L=50\Omega$                |  | -83 |  | dB   |

| CIOSSIAIK                 |       | F=10KHz, $R_L$ =50 $\Omega$           |  | -82 |  | dB   |

|                           | THD   | F=20Hz to 20KHz                       |  | -80 |  | dB   |

| Total Harmonic Distortion |       | $V_A=600 \text{mVp-p} @R_L=32\Omega,$ |  |     |  |      |

| CAPACITANCE               |       |                                       |  |     |  |      |

| Off capacitance           | COFF  | F=100KHz, VCC=3.3                     |  | 5   |  | pF   |

| On capacitance            | Con   | F=100KHz, VCC=3.3                     |  | 7   |  | pF   |

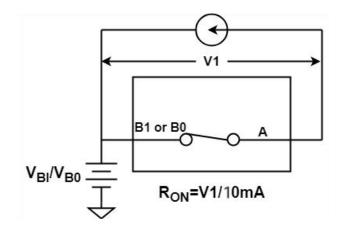

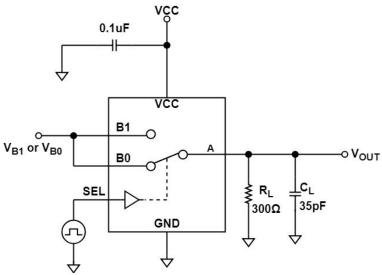

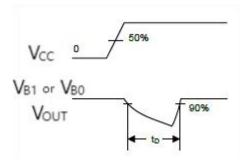

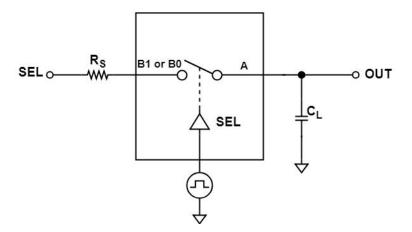

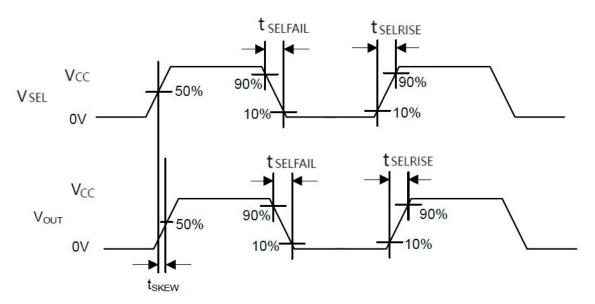

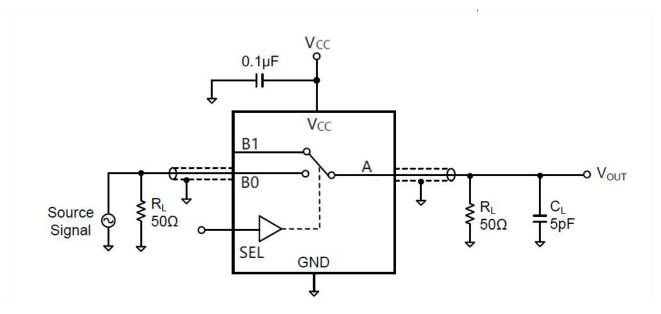

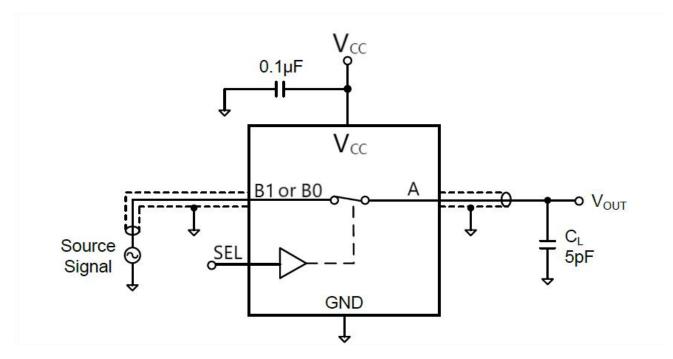

### **Test Circuits**

Test Circuit 1. On-Resistance

Test Circuit 3. Break-Before-Make Time Delay, t<sub>D</sub>

Rise Time Delay = |t<sub>SELRISE</sub>-t<sub>OUTRISE</sub>| Fall Time Delay = |t<sub>SELFALL</sub>-t<sub>OUTFALL</sub>| Rise Time to Fall Time Mismatch = |t<sub>OUTFALL</sub>t<sub>OUTRISE</sub>|

**Test Circuit 5. Off Isolation**

Test Circuit 6. -3dB Bandwidth

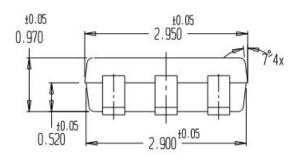

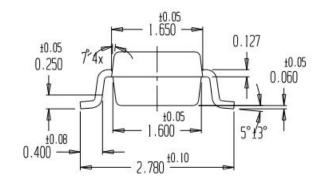

# Package Outline Dimensions(All dimensions in mm.)

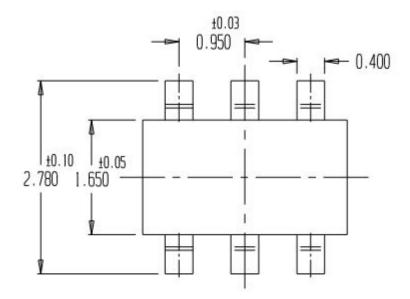

(1) Package Type: SOT23-6

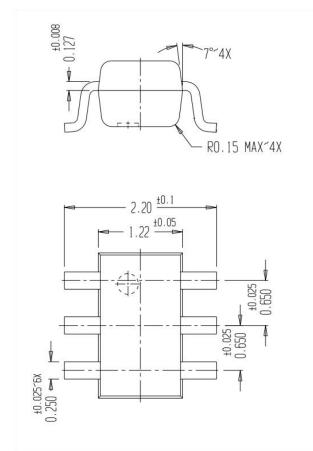

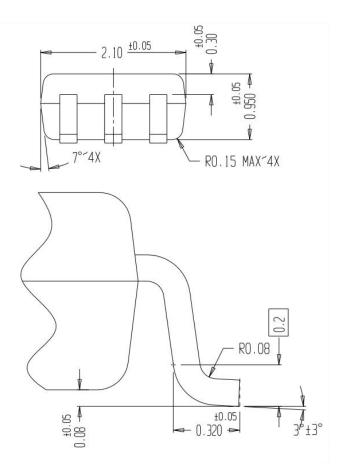

#### (2) Package Type: SOT363

### Important Notice And Disclaimer

• We reserves the right to change the instruction manual without prior notice.

• Any semiconductor product has a certain possibility of failure or malfunction under specific conditions. The buyer is responsible for complying with safety standards and taking safety measures when using our products for system design and overall manufacturing to avoid potential failure risks that may cause personal injury or property damage.

• The improvement of product quality is endless, our company will be dedicated to provide customers with better products.

| Version Number                                                | Revision                                                      |  |

|---------------------------------------------------------------|---------------------------------------------------------------|--|

| first edition                                                 |                                                               |  |

|                                                               | 1. Update the On-Resistance on page 3                         |  |

| V1.0                                                          | 2. Update the Test Circuit 1 on page 4                        |  |

|                                                               | 3. Update the Off state leakage from A to B0(or B1) on page 4 |  |

| N/2 0                                                         | 1. Update the High Bandwidth on page 1&3                      |  |

| V2.0                                                          | 2. Update the Features and Descriptions on page 1.            |  |

| V3.0 1. Update the Important Notice And Disclaimer on page 9. |                                                               |  |

#### Version Modification Record