### 1 DISCRIPTION

The SGM61410 is 40V, 1A buck converter with an integrated 400 m $\Omega$  high-side MOSFET and 200 m $\Omega$  low-side MOSFET. The SGM61410 has wide in put range from 4.6V to 40V, the SGM61410 is suit able for variable applications which is from unreg ulated sources, like industrial or automotive appli cations. The device adopts peak current mode and has the fixed switching frequency. The quiescent current of this device is 80uA in sleep mode and the shutdown current is 1uA, making it suitable for battery-powered system. The device integrates protections, like cycle-by-cycle current limit, thermal shutdown, short-circuit and over-voltage protection. It's available in a cost effective TSOT23-6L package.

### **2 FEATURES**

- Wide Input Range: 4.6V-40V

- Up to 1A Continuous Output Current

- 0.81V ± 2.5% Feedback Reference Voltage

- Integrated 400m $\Omega$  High-Side and 200m $\Omega$  Low-Side Power MOSFETs

- Fixed Frequency 1MHz

- Pulse Skipping Mode (PSM) at Light Load

- 80uA Quiescent Current in Sleep Mode

- 80ns Minimum On-time

- 1ms Internal Soft-start Time

- Over-Current Protection and Hiccup

#### 3 APPLICATIONS

- Industrial 24V Distributed Power Bus

- Power meter

- Elevator, PLC, Servo

- Automatic Control

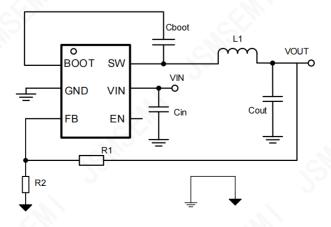

### TYPICAL APPLICATION

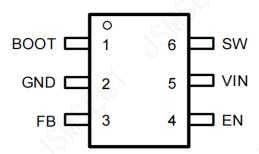

# 4 PIN CONFIGURATION AND FUNCTIONS

Top View: SGM61410 TSOT23-6L

| PIN C | PIN OUT |         |                                                                                                                                                                                                                                                                                                        |  |  |

|-------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME  | NO.     | I/O     | PIN FUNCTION                                                                                                                                                                                                                                                                                           |  |  |

| воот  | 1       | ı       | Power supply for the high-side power MOSFET gate driver. Must connect a 0.1uF or greater ceramic capacitor between BST pin and SW node.                                                                                                                                                                |  |  |

| GND   | 2       | -       | Power ground.                                                                                                                                                                                                                                                                                          |  |  |

| FB    | 3       | ı       | Buck converter output feedback sensing voltage. Connect a resistor divider from VOUT to FB to set up output voltage. The device regulates FB to the internal reference of 0.81V typically.                                                                                                             |  |  |

| EN    | 4       | 25/11/2 | Enable logic input. Floating the pin enables the device. This pin supports high voltage input up to VIN supply to be connected VIN directly to enable the device automatically. The device has precision enable thresholds 1.25V rising / 1.1V falling for programmable UVLO threshold and hysteresis. |  |  |

| VIN   | 5       | I       | Power supply input. Must be locally bypassed.                                                                                                                                                                                                                                                          |  |  |

| SW    | 6       | 0       | Switching node of the buck converter.                                                                                                                                                                                                                                                                  |  |  |

### **5 SPECIFICATIONS**

### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature unless otherwise noted

| DESCRIPTION          | PARAMETER                    | MIN  | MAX | UNIT |

|----------------------|------------------------------|------|-----|------|

|                      | VIN to GND                   | -0.3 | 45  | V    |

| Input Voltage        | EN to GND                    | -0.3 | 45  | V    |

|                      | FB to GND                    | -0.3 | 6   | V    |

| Input Voltage        | BOOT to SW                   | -0.3 | 6   | V    |

| Outset Waltana       | SW to GND                    | -1   | 45  | V    |

| Output Voltage       | SW to GND(≤ 30ns transients) | -3   | 45  | V    |

| Junction temperature | T,                           | -40  | 150 | °C   |

| Storage temperature  | T <sub>STG</sub>             | -55  | 160 | °C   |

### **ESD RATINGS**

| PARAMETER | DEFINITION                                     | MIN | MAX   | UNIT |

|-----------|------------------------------------------------|-----|-------|------|

|           | Human Body Model (HBM), per ANSI-JEDEC-JS-001- | 2   | ±2000 | V    |

| $V_{ESD}$ | 2014 specification, all pins (1)               |     | 12000 | V    |

| V ESD     | Charged Device Model (CDM), per ANSI-JEDEC-JS- |     | ±500  |      |

|           | 002-2014 specification, all pins (1)           |     | ±300  | V    |

<sup>(1)</sup> HBM and CDM stressing are done in accordance with the ANSI/ESDA/JEDEC JS-001-2014 specification

### RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range unless otherwise noted

| PARAMETER  | DEFINITION                     | MIN  | MAX | UNIT |

|------------|--------------------------------|------|-----|------|

| VIN        | Supply voltage range           | 4.6  | 40  | V    |

| воот       | BOOT voltage range             | 5    | 46  | V    |

| BOOT to SW | BOOT to SW voltage             | -0.3 | 6   | V    |

| SW         | SW voltage range               | -1   | 40  | V    |

| FB         | FB voltage range               | 0    | 6   | V    |

| EN         | EN voltage range               | 0    | 40  | V    |

| Tı         | Operating junction temperature | -40  | 125 | °C   |

### THERMAL INFORMATION

| PARAMETER       | THERMAL METRIC                               | TSOT-6L | UNIT |

|-----------------|----------------------------------------------|---------|------|

| $R_{\theta JA}$ | Junction to ambient thermal resistance       | 102     | °C/W |

| $R_{\theta JC}$ | Junction to case thermal resistance          | 36.9    | °C/W |

| Ψлв             | Junction to board characterization parameter | 28.4    | °C/W |

### **ELECTRICAL CHARACTERISTICS**

VIN=EN=12V, T<sub>J</sub>=-40°C~125°C, typical values are tested under 25°C.

| SYMBOL               | PARAMETER                   | TEST CONDITION                             | MIN  | TYP  | MAX  | UNIT |

|----------------------|-----------------------------|--------------------------------------------|------|------|------|------|

| Power Su             | pply                        |                                            |      |      | 1    |      |

| VIN                  | Operating input voltage     |                                            | 4.6  |      | 40   | V    |

| V                    | Input UVLO                  | V <sub>IN</sub> rising                     |      | 4.3  | 4.5  | V    |

| $V_{IN\_UVLO}$       | Hysteresis                  |                                            |      | 450  | 2    | mV   |

| I <sub>SHDN</sub>    | Shutdown current            | EN=0, No load, V <sub>IN</sub> =12         |      | 1    | 3    | uA   |

| 11/2                 | Y                           | EN=floating, No load,                      |      |      |      |      |

| lQ                   | Quiescent current           | No switch, V <sub>IN</sub> =12V,           |      | 80   |      | uA   |

|                      | 25                          | BOOT-SW=5V                                 | (2)  |      |      |      |

| ENABLE a             | nd Feedback                 |                                            |      |      |      | •    |

| V <sub>EN_H</sub>    | Enable high threshold       |                                            | 1.21 | 1.25 | 1.29 | V    |

| V <sub>EN_L</sub>    | Enable low threshold        |                                            |      | 1.1  |      | ٧    |

| $V_{FB}$             | Feedback Voltage            | ic IIII                                    | 0.79 | 0.81 | 0.83 | ٧    |

| Power Mo             | OSFET                       | 2                                          |      |      | 75.  |      |

| R <sub>DSON_H</sub>  | High side FET on-resistance |                                            | 340  | 400  | 740  | mΩ   |

| R <sub>DSON_L</sub>  | Low side FET on-resistance  |                                            | 170  | 200  | 350  | mΩ   |

| Switching            | Characteristics             | 12.                                        | .,(0 | 5    |      | •    |

| F <sub>SW</sub>      | Switching frequency         | V <sub>IN</sub> =12V, V <sub>OUT</sub> =5V | 1811 | 1000 |      | KHz  |

| t <sub>ON_MIN</sub>  | Minimum on-time             |                                            | )    | 80   |      | ns   |

| Soft Start           | Time and Protection         |                                            |      |      |      |      |

| t <sub>SS</sub>      | Internal soft-start time    | .cV                                        |      | 1.5  |      | ms   |

| I <sub>LIM_HSD</sub> | HSD peak current limit      | c/ll2                                      |      | 1.4  |      | Α    |

| I <sub>LIM_LSD</sub> | LSD valley current limit    | 25                                         |      | 1.2  | 19   | Α    |

| <b>T</b>             | Thermal shutdown threshold  |                                            |      | 170  |      | °C   |

| $T_{SD}$             | Hysteresis                  |                                            |      | 30   | b    |      |

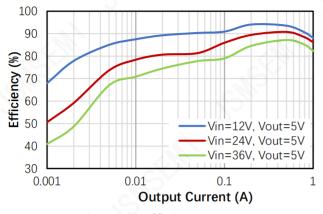

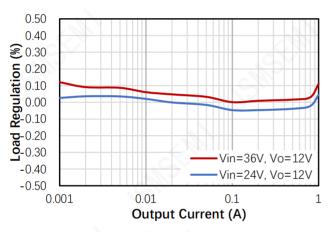

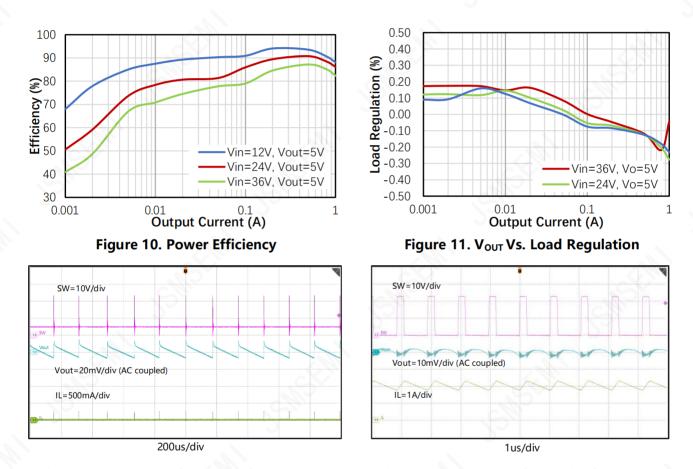

#### 6 TYPICAL CHARACTERISTICS

VIN=12V, L=15uH, Cout=22uF, T<sub>A</sub>= 25°C, unless otherwise noted.

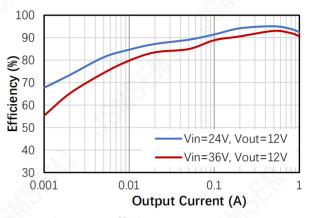

Figure 1. Efficiency Curve

Figure 3. Load Regulation, L=22uH

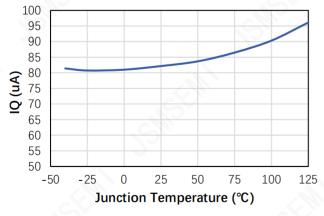

Figure 5. IQ vs Junction Temperature

Figure 2. Efficiency Curve L=22uH

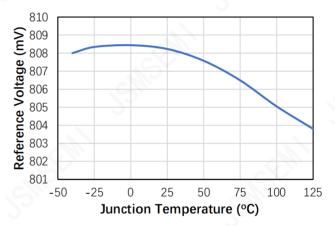

Figure 4. Reference Voltage vs. Junction

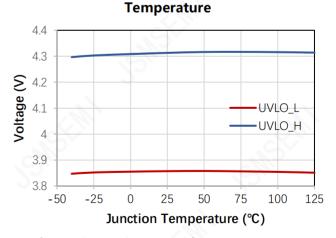

**Figure 6. UVLO vs Junction Temperature**

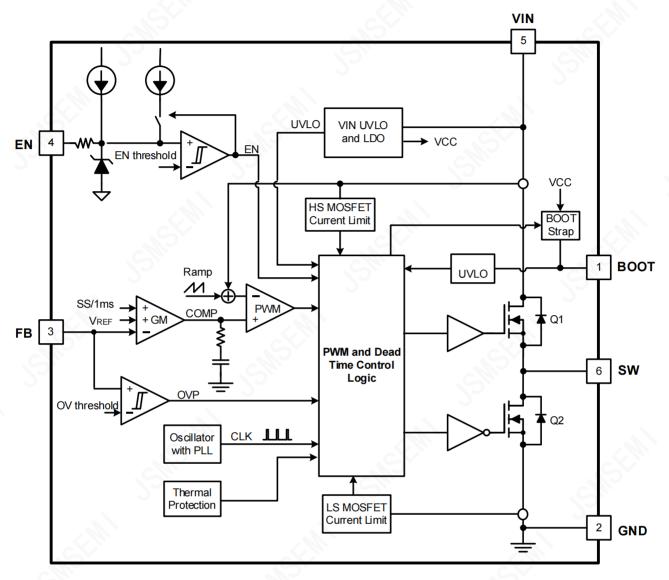

### 7 FUNCTIONAL BLOCK DIAGRAM

Figure 7. Block Diagram for SGM61410

### **8 DISCRIPTION**

#### **Overview**

The SGM61410 is a 40V, 1A buck converter with an integrated 400 m $\Omega$  high-side MOSFET and 200 m $\Omega$  lo w-side MOSFET. With a wide input range from 4.6V to 40V, the device adopts peak current mode a nd supports a fixed 1MHz switching frequency to minimize off-chip components. The SGM61410 features an internal 1ms soft-start time.

The quiescent current of this device is 80uA in sleep mode and the shutdown current is 1uA. The SGM614 10 features an internal 1ms soft-start time. The device has a default input start-up voltage of 4.3V with 450 mV hysteresis. The EN pin is a high-voltage pin with a precision threshold that can be used to adjust the in put voltage lockout thresholds with two external resistors to meet accurate higher UVLO system requireme nts. Floating EN pin enables the device. Connecting EN pin to VIN directly starts up the device automatica llv.

The device integrates protections, like cycle-by-cycle current limit, thermal shutdown protection, output over-voltage protection and output short circuit protection and input voltage under-voltage protection. The device also supports monolithic startup with pre-biased output condition.

### **Peak Current Mode Control**

The SGM61410 employs fixed frequency peak current mode control. An internal clock initiates turning on the integrated high-side power MOSFET in each cycle, then inductor current rises linearly. When the current through high-side MOSFET reaches the threshold level set by the internal compensation voltage of the internal error amplifier, the high-side MOSFET turns off. When the high-side MOSFET turns off, the inductor current discharges through the low-side MOSFET till the next clock cycle begins.

The integrated error amplifier and the internal compensation builds up the feedback loop to regulates the output voltage to the reference. The error amplifier comparing the voltage of the FB pin with an internal reference voltage of 0.81V. The load current increasement reduces the feedback voltage which is relative to a voltage raise of the error amplifier output till the average inductor current matches the increased load current.

The device also integrates an internal slope compensation circuitry to prevent sub-harmonic oscillation when duty cycle is greater than 50% for a fixed frequency peak current mode control.

# **Pulse Skipping Mode (PSM)**

The SGM61410 operates in Pulse Skipping Mode (PSM) with light load current to improve efficiency. A decrease of the load current leads an increasement in the feedback voltage which yields down the compensation voltage. When the compensation voltage drops to a low clamp threshold, the PSM

triggered. During the skipping period, the discharge of output capacitor leads the output voltage drop which makes the FB voltage decay. Once the FB voltage drops lower than the reference voltage and the compensation voltage rises above the low clamp threshold, the integrated high-side MOSFET turns on in next clock pulse. After several switching cycles with typical 0.2A peak inductor current, the internal compensation voltage drops and is clamped again and pulse skipping mode repeats if the output continues light loaded.

This PSM helps achieving higher efficiency by skipping cycles to reduce switching power loss and gate drive charging loss. Regarding to improve efficiency further, the quiescent current is 80uA during skipping period with no switching.

### **VIN Power**

The SGM61410 is designed to operate from an input voltage supply range between 4.6V to 40V, at least 0.1uF and 10uF decoupling ceramic cap are recommended to bypass the supply noise.

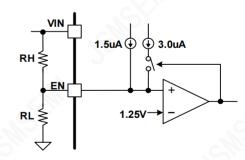

# **Under Voltage Lockout Threshold and Enable**

The EN pin of SGM61410 is a high voltage pin which can be connected to VIN directly to start-up the device. The SGM61410 is enabled when the EN pin voltage higher than the enable threshold of 1.25V and disabled when the EN pin voltage lower than 1.1V. Grace to the internal 1.0uA pull-up current, the device is default enabled when the EN pin floats.

The Under Voltage Lock Out (UVLO) default startup threshold is typical 4.3V with VIN rising and shutdown threshold is 3.85V with VIN falling. The more accurate UVLO threshold can be programmed through the precision enable threshold of EN pin. Connect an external resistor divider (RL and RH) shown in Figure 8 from VIN to EN. The UVLO rising and falling threshold can be calculated by Equation 1 and Equation 2 respectively.

$$RH = \frac{V_{rise} - 1.14 * V_{fall}}{1.14 * 4.5uA - 1.5uA}$$

(1)

$$RL = \frac{1.25V}{\frac{V_{rise} - 1.25V}{R_H} + 1.5uA}$$

(2)

where

- V<sub>rise</sub> is rising threshold of Vin UVLO

- V<sub>fall</sub> is falling threshold of Vin UVLO

Figure 8. System UVLO by EN divider

# **Bootstrap Voltage Regulator**

An external bootstrap capacitor between BOOT pin and SW pin powers floating high-side power MOSFET gate driver. The bootstrap capacitor voltage is charged from an integrated voltage regulator when high-side power MOSFET is off.

The floating supply (BOOT to SW) UVLO threshold is 2.7V rising and hysteresis of 350mV. When the converter operates with high duty cycle or prolongs in sleep mode for certain long time, the required time interval to recharging bootstrap capacitor is too long to keep the voltage at bootstrap capacitor sufficient. When the voltage across bootstrap capacitor drops below 2.35V, BOOT UVLO occurs.

# **Output Voltage**

The SGM61410 regulates the internal reference voltage at 0.81V with  $\pm 1\%$  tolerance over the operating temperature and voltage range.

The output voltage is set by a resistor divider from the output node to the FB pin. It is recommended to use 1% tolerance or better resistors. Use Equation 3 to calculate resistance of resistor dividers. To improve efficiency at light loads, larger value resistors are recommended. However, if the value is higher, the regulator will be more noise sensitive. RFB\_BOT in the range of  $10k\Omega$  to  $100k\Omega$  is recommended for most application.

$$R_{FB\_TOP} = \left(\frac{V_{OUT}}{0.81V} - 1\right) * R_{FB\_BOT} \tag{3}$$

where

- R<sub>FB TOP</sub> is the resistor connecting the output to the FB pin.

- R<sub>FB BOT</sub> is the resistor connecting the FB pin to the ground.

#### **Overcurrent and Short Circuit Protection**

The SGM61410 adopts the peak current mode control. In the overcurrent momentum, the output voltage is yield down by heavy load and the error amplifier drives the compensation voltage high to increase the switching current. As the error amplifier output increases, it will be clamped internally, and the high-side current is clamped by a maximum peak current threshold. The peak current threshold is constant over the full duty cycle range.

When the output overcurrent or short circuit occurs, the device will trigger a cycle-by-cycle peak current clamping and frequency foldback by skipping pulse. This will lead more time for the inductor current to ramp down. Furthermore, a lower switching frequency contributes on lower switching loss, avoids overheating and other potential damages.

# SGM61410XN6G-JSM 1MHz, 1A, 45V Synchronous Step-Down Converter

## **Overvoltage Protection**

The SGM61410 implements the overvoltage protection (OVP) circuitry to minimize output voltage overshoot during load transient, recovering from output fault condition or light load transient. When the FB pin voltage reaches the rising OVP threshold which is typically 109% of  $V_{REF}$ , the high-side MOSFET will be turned off immediately which make the device under OVP. When the FB pin voltage drops below the falling OVP threshold, the high-side MOSFET is turned on and resumed normal operation. The falling OVP threshold is typically 105% of  $V_{REF}$ .

### **Thermal Shutdown**

The SGM61410 features an internal thermal shutdown circuit to protect the device from the damage during excessive heat and power dissipation conditions. The thermal shutdown circuit will be asserted when the junction temperature exceeds typically 170°C. When the junction temperature falls below 140°C, the device restarts with internal soft start phase.

### **9 APPLICATION INFORMATION**

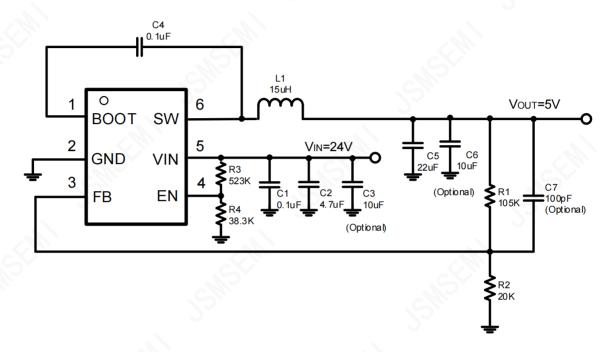

### **Typical Application**

Figure 9. 24V Input, 5V/1A Output

**Table 1. Design Parameters**

| Design Parameters                     | Example Value      |  |  |

|---------------------------------------|--------------------|--|--|

| Input Voltage                         | 24V typical, 6~36V |  |  |

| Output Voltage                        | 5V                 |  |  |

| Output Current                        | 1A                 |  |  |

| Output voltage ripple (peak to peak)  | <50mV              |  |  |

| Overshoot/Undershoot range (0.1~0.9A) | <5%                |  |  |

| Switching Frequency                   | 1MHz               |  |  |

V1.0 www.jsmsemi.com 第11页,共18页

## **Set Output Voltage**

The SGM61410 output voltage can be easily set up using a resistor divider network R1 and R2 as shown in the typical application circuit Figure 9. Use Equation (4) to calculate the resistor divider values.

$$R1 = \frac{(V_{OUT} - 0.8) \times R2}{0.8} \tag{4}$$

In this design example the Vout is 5V. Set the resistor R2 value to be approximately 20k.

$$R1 = \frac{(V_{OUT} - 0.8) \times R2}{0.8} = \frac{(5 - 0.8) \times 20k\Omega}{0.8} = 105 k\Omega$$

Slightly increasing or decreasing R1 to a closest available resistance, the  $105k\Omega$  is selected.

# **Input Capacitor Selection**

For good input voltage filtering, choose low-ESR ceramic capacitors. A X7R ceramic capacitor 4.7uF to  $10\mu$ F is recommended for the decoupling capacitor and a  $0.1\mu$ F ceramic bypass capacitor is recommended to be placed as close as possible to the VIN pin. These capacitors must be rated for 50V.

For this design, one 4.7uF X7R capacitors and one 0.1uF capacitor rated 50V is recommended.

The input voltage ripple can be calculated by using Equation (5) to calculate the input voltage ripple:

$$\Delta V_{IN} = \frac{I_{OUT}}{C_{IN} \times f_{SW}} \times \frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) = \frac{1A}{4.7uF \times 1000k} \times \frac{5V}{24V} \times \left(1 - \frac{5V}{24V}\right) = 35mV \tag{5}$$

Where:

- C<sub>IN</sub> is the input capacitor value

- f<sub>sw</sub> is the converter switching frequency

- I<sub>OUT</sub> is the maximum load current

#### **Inductor Selection**

The performance of inductor affects the power supply's steady state operation, transient behavior, loop stability, and buck converter efficiency. The critical parameters of inductor is the inductance, the DC resistance (DCR), the saturation current and the RMS current.

Use following equation to the minimum inductance:

$$L_{MIN} = \frac{V_{OUT} \times (V_{INMAX} - V_{OUT})}{V_{INMAX} \times K_{IND} \times I_{OUT} \times f_{SW}}$$

(6)

Where

- V<sub>OUT</sub> is output voltage

- K<sub>IND</sub> is the Ripple Ration of the inductor ripple current (ΔiL/I<sub>OUT</sub>), 0.3 is recommended here

- V<sub>INMAX</sub> is the maximum input voltage

- f<sub>SW</sub> is the converter switching frequency

- I<sub>OUT</sub> is the output current

In this design example:

$$L > L_{MIN} = \frac{V_{OUT} \times (V_{INMAX} - V_{OUT})}{V_{INMAX} \times K_{IND} \times I_{OUT} \times f_{SW}} = \frac{5V \times (40V - 5V)}{40V \times 0.3 \times 1A \times 1MHz} = 14.6 \text{ uH}$$

15uH is selected in the design example. Generally, the Inductor values can have ±20% or even ±30% tolerance with no current bias. When the inductor current approaches saturation level, its inductance can decrease 20% to 35% from the value at 0A current depending on how the inductor vendor defines saturation. When selecting an inductor, choose its rated current especially the saturation current larger than its peak current during the operation.

# **Output Capacitor**

The output capacitor must be chosen carefully with the reason that this capacitor value determines the regulator pole, the output voltage ripple, and how the regulator responds to a large change in load current. Generally, choose a low-ESR output capacitor like a ceramic capacitor from X5R or X7R family to get small output voltage ripple.

From the required output voltage ripple (<5mV), use the Equation 7 to calculate the minimum required effective capacitance, C<sub>OUT</sub>.

$$C_{OUT} > \frac{\Delta I_{LPP}}{8 \times V_{OUT\_Ripple} \times f_{SW}} = \frac{K_{IND} \times I_{OUT}}{8 \times V_{OUT\_Ripple} \times f_{SW}}$$

(7)

The allowed maximum ESR of the output capacitor is calculated by the equation 8.

$$R_{ESR} < \frac{V_{OUT\_Ripple}}{k_{IND} \times I_{OUT}} \tag{8}$$

Where

- V<sub>OUT\_Ripple</sub> is output voltage ripple caused by charging and discharging of the output capacitor.

- k<sub>IND</sub> is the Ripple Ration of the inductor ripple current (∆iL/I<sub>OUT</sub>), 0.3 is recommended here

- I<sub>OUT</sub> is the maximum output current

- $f_{SW}$  is the converter switching frequency.

In this design, V<sub>OUT Ripple</sub> is smaller than 5mV, f<sub>SW</sub> is 1000kHz, l<sub>OUT</sub> is 1A and K<sub>IND</sub> is 0.3:

$$C_{OUT} > \frac{0.3 \times 1A}{8 \times 5mV \times 1000k} = 7.5 uF$$

$$R_{ESR} < \frac{5mV}{0.3 \times 1A} = 16.7 m\Omega$$

Therefore, a X7R capacitor of 22uF with 16V DC rating and 15mΩ ESR is selected

# **Bootstrap Capacitor**

For proper operation of the device, a 0.1uF ceramic capacitor of X5R or X7R must be placed between the SW pin to the BOOT pin. The DC rating of this capacitor is must be 10V or higher voltage level.

# **Application Curves**

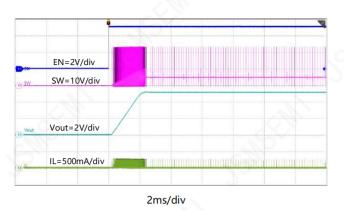

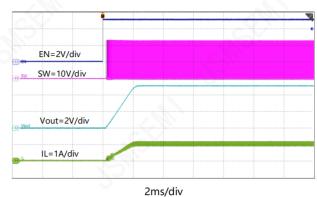

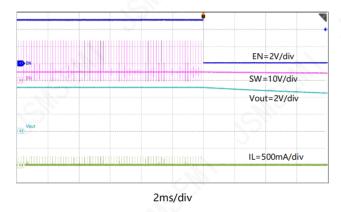

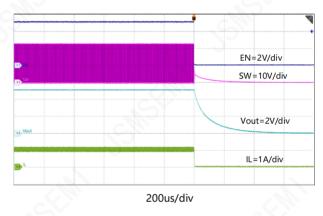

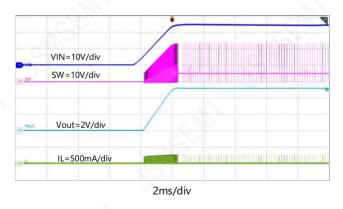

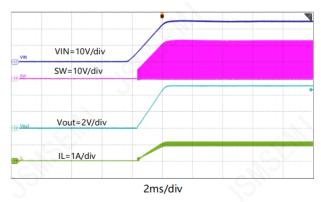

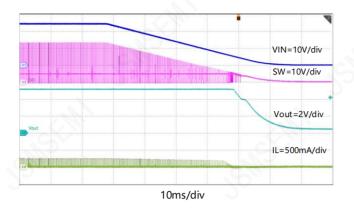

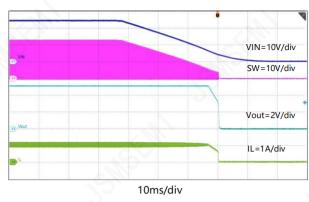

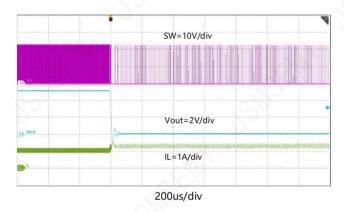

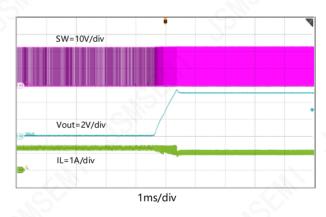

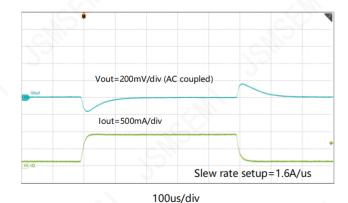

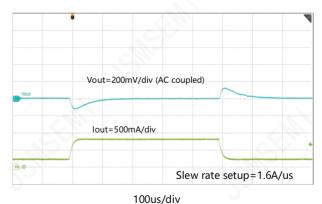

Figure 10 through Figure 25 apply to the circuit of Figure 9.  $V_{IN} = 24 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$  unless otherwise specified

Figure 12. Output Voltage Ripple, IouT=1mA

Figure 13. Output Voltage Ripple, IOUT=1A

Figure 14. Start-Up with EN, IOUT=1mA

Figure 15. Start-Up with EN, IOUT=1A

Figure 16. Shut-down with EN, IOUT=1mA

Figure 17. Shut-down with EN, IOUT=1A

Figure 18. Start-Up with VIN rising, IOUT=1mA

Figure 19. Start-Up with VIN Rising, IOUT=1A

Figure 20. Shut-Down with VIN falling,  $I_{OUT}=1mA$

Figure 21. Shut-Down with VIN falling, I = 1A

Figure 22. 1A Operation to HardShort, IOUT=1A

Figure 23. HardShort Recovery, IOUT=1A

Figure 24. Transient Response 0.1A-0.9A

Figure 25. Transient Response 0.2A-0.8A

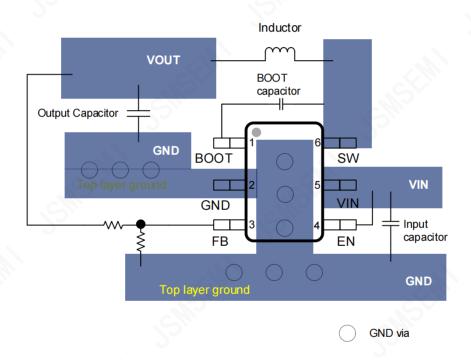

# **10 Layout Guideline and Layout Example**

Layout is critical for proper operation. Please follow the layout guidelines.

- 1. The power ground is very critical. The power trace should take lowest impedance as possible and the ground area should be sufficient to optimize thermal, 8mil max thermal via recommended.

- 2. Place the bypass input capacitor with low ESR as close as possible to the VIN pin and GND. The bypassing loop from VIN terminal to the GND should be as short as possible.

- 3. The inductor should be located as close as possible to the SW pin for reducing magnetic and electrostatic noise.

- 4. The feedback resistor divider should be placed close to the FB pin.

- 5. The ground connected to the input capacitors and output capacitors should be tied to the system ground plane in only one spot to minimize conducted noise to the system ground plane.

Figure 26. Layout Example

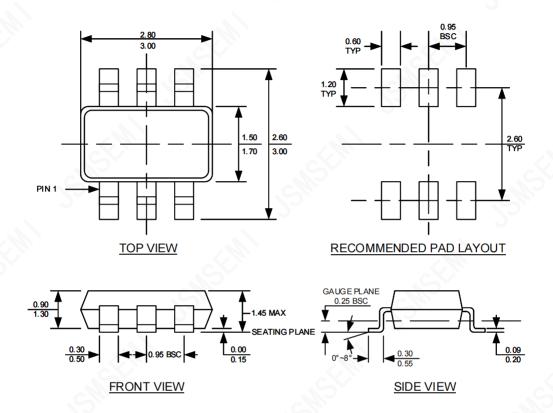

# Package Description

#### SOT23-6

## NOTE:

- 1. CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2. PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3. PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5. DRAWING CONFORMS TO JEDEC MS-012, VARIATION BA.

- 6. DRAWING IS NOT TO SCALE.