# 12V, 100mA, Ultralow Noise, Ultrahigh PSRR LDO

#### **DESCRIPTION**

The 1033 is an ultralow noise and ultrahigh PSRR LDO. Using an advanced structure, it achieves excellent line and load transient response with only a 4.7µF ceramic output capacitor.

The 1033 is capable of sourcing 100mA at a typical 250mV dropout voltage. And it can be easily paralleled to further increase output current and reduce noise.

The device is suitable for powering noise sensitive applications, such as RF circuit, high precision ADC/DAC and high precision sensor.

### **DEVICE INFORMATION**

| Part No. | Package             | Packing     |  |

|----------|---------------------|-------------|--|

| 1033TR   | DFN-10-3×3×0.75-0.5 | Tape & Reel |  |

#### **FEATURES**

- Ultralow RMS Noise: 0.9µV<sub>RMS</sub> (10Hz to 100kHz)

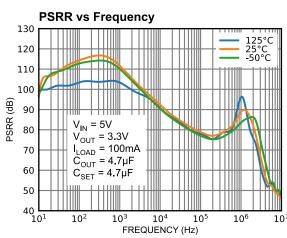

- Ultrahigh PSRR: 78dB@100kHz, 88dB@1MHz

- Wide Input Voltage Range: 2V to 12V

- Wide Output Voltage Range: 0V to 9V

- Output Current: 100mA

- Low Dropout Voltage: 250mV

- Programmable PG Threshold

# **APPLICATIONS**

- RF Circuit: LNA, PLL, Mixer

- High Precision ADC/DAC

- High Precision Sensor

- High Precision Signal Process Circuit

- Medical Instrument

- Post-Regulator for SMPS

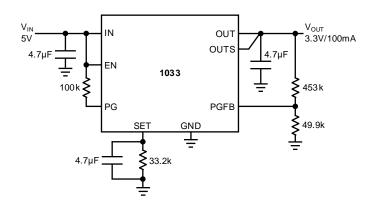

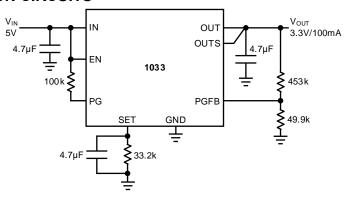

### **TYPICAL APPLICATION**

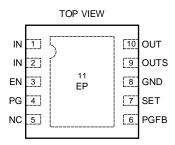

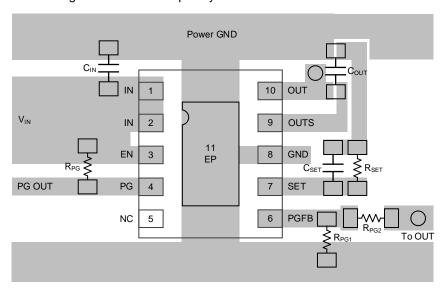

# **PIN CONFIGURATION**

# **PIN FUNCTIONS**

| Pin No.        | Pin Name       | I/O                                                                                     | Function Description                                                                    |  |                                                                                       |

|----------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|---------------------------------------------------------------------------------------|

| 1. 2 IN        |                | -                                                                                       | Power Supply. Supply voltage ranges from 2V to 12V. A bypass capacitor at the IN pin is |  |                                                                                       |

| 1, 2           | 1, 2   IN   I  |                                                                                         | required.                                                                               |  |                                                                                       |

| 2              | 3 EN I         |                                                                                         | 2 EN                                                                                    |  | Enable. Regulator enable control or undervoltage lockout threshold input. The typical |

| 3              |                |                                                                                         | threshold voltage is 1.27V.                                                             |  |                                                                                       |

| 4              | PG             | 0                                                                                       | Power Good Indication. This is an open-collector pin. Float the PG pin if not used.     |  |                                                                                       |

| 5              | NC             | -                                                                                       | No Connection.                                                                          |  |                                                                                       |

| C DOED         |                | Power Good Feedback. Connect PGFB to the center point of the external resistor divider. |                                                                                         |  |                                                                                       |

| б              | 6 PGFB         |                                                                                         | The typical PGFB threshold voltage is 300mV.                                            |  |                                                                                       |

| 7              | SET            | I                                                                                       | Output Voltage Set Pin.                                                                 |  |                                                                                       |

| 8              | GND            | G                                                                                       | GND.                                                                                    |  |                                                                                       |

| 9              | OUTS           | I                                                                                       | Output Voltage Sensing Feedback. Connect OUTS to output side of the output capacitor.   |  |                                                                                       |

| 10             | OUT            | 0                                                                                       | Regulator Output. Bypass with a minimum 4.7µF ceramic capacitor to GND.                 |  |                                                                                       |

| 44             | - FD           | -                                                                                       | Exposed Pad. No internal electrical connection. Solder the EP to GND pin and connect to |  |                                                                                       |

| 11             | EP             |                                                                                         | a large copper plane to reduce thermal resistance.                                      |  |                                                                                       |

| I = Input, O = | Output, G = Gr | ound                                                                                    |                                                                                         |  |                                                                                       |

# **ABSOLUTE MAXIMUM RATING**

| Parameter                              | Symbol                | Rating      | Unit |

|----------------------------------------|-----------------------|-------------|------|

| IN Voltage                             | V <sub>IN</sub>       | -0.3 ~ 13.2 | V    |

| EN Voltage                             | V <sub>EN</sub>       | -0.3 ~ 13.2 | V    |

| PG Voltage                             | V <sub>PG</sub>       | -0.3 ~ 13.2 | V    |

| PGFB Voltage                           | V <sub>PGFB</sub>     | -0.3 ~ 13.2 | V    |

| SET Voltage                            | Vset                  | -0.3 ~ 10   | V    |

| OUT Voltage                            | Vout                  | -0.3 ~ 10   | V    |

| OUTS Voltage                           | Vouts                 | -0.3 ~ 10   | V    |

| Lead Temperature (Soldering 5 Sec)     | T <sub>LEAD</sub>     | 260         | °C   |

| Operating Junction Temperature Range   | TJ                    | -40 ~ 125   | °C   |

| Storage Temperature Range              | T <sub>STG</sub>      | -65 ~ 150   | °C   |

| Junction-to-Ambient Thermal Resistance | θја                   | 34          | °C/W |

| ESD Protection (HBM)                   | V <sub>ESD_</sub> HBM | ±2000       | V    |

| ESD Protection (CDM)                   | V <sub>ESD_CDM</sub>  | ±1000       | V    |

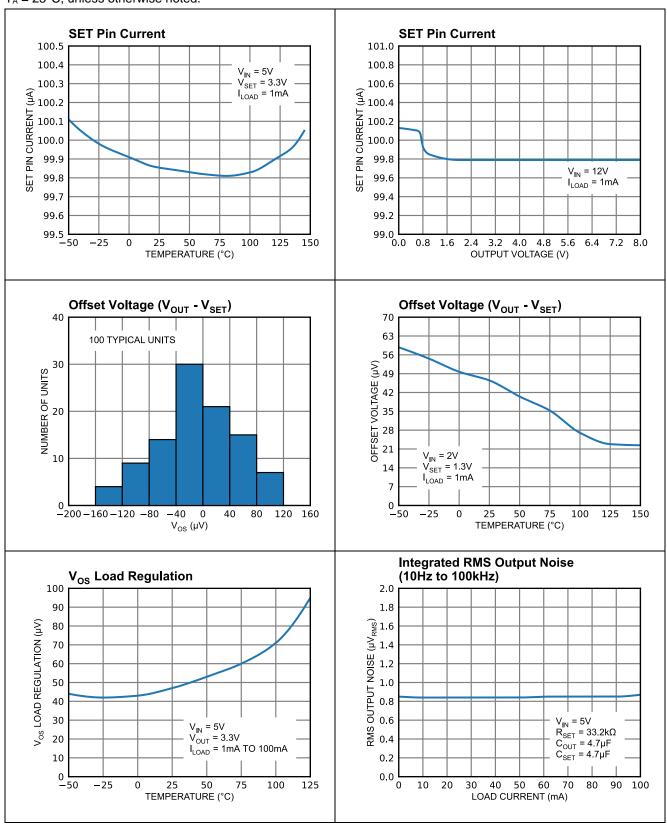

# **ELECTRICAL CHARACTERISTICS**

The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A$  = 25°C.  $C_{SET}$  = 4.7 $\mu$ F,  $C_{OUT}$  = 4.7 $\mu$ F, unless otherwise noted.

| Parameter                       | Symbol                 | Test Conditions                                                                         |   | Min. | Тур. | Max. | Unit          |

|---------------------------------|------------------------|-----------------------------------------------------------------------------------------|---|------|------|------|---------------|

| Minimum IN Pin Voltage          | V <sub>IN_MIN</sub>    | I <sub>LOAD</sub> = 10mA, V <sub>IN</sub> UVLO Rising                                   | • |      | 1.75 | 2    | V             |

| CET Die Comment                 | I <sub>SET</sub>       | V <sub>IN</sub> = 2V, V <sub>OUT</sub> = 1.4V, I <sub>LOAD</sub> = 1mA                  |   | 99   | 100  | 101  | μA            |

| SET Pin Current                 |                        | $2V \le V_{IN} \le 12V$ , $0V \le V_{OUT} \le 9V$ , $1mA \le I_{LOAD} \le 100mA$        | • | 98   | 100  | 102  | μA            |

| SET Pin Current During Fast     | la== ==                | $V_{PGFB} = 289 \text{mV}, V_{IN} = 2.8 \text{V}, V_{SET} = 1.4 \text{V}$               |   |      | 2.1  |      | mA            |

| Start-Up                        | ISET_FS                |                                                                                         |   |      | 2.1  |      | IIIA          |

| Output Offset Voltage           | Vos                    | V <sub>IN</sub> = 2V, V <sub>OUT</sub> = 1.4V, I <sub>LOAD</sub> = 1mA                  |   | -0.4 |      | 0.4  | mV            |

| (Vout - Vset)                   | VOS                    | $2V \le V_{IN} \le 12V$ , $0V \le V_{OUT} \le 9V$ , $1mA \le I_{LOAD} \le 100mA$        | • | -1   |      | 1    | mV            |

| Line Degulation                 | $\Delta I_{SET}$       | $V_{IN} = 2V \text{ to } 12V, V_{OUT} = 1.4V, I_{LOAD} = 1\text{mA}$                    |   |      | 0.5  |      | nA/V          |

| Line Regulation                 | $\Delta V_{\text{OS}}$ | $V_{IN} = 2V \text{ to } 12V, V_{OUT} = 1.4V, I_{LOAD} = 1\text{mA}$                    | • |      | 1    | ±3   | μV/V          |

| Load Regulation                 | $\Delta I_{SET}$       | $I_{LOAD} = 1 \text{mA to } 100 \text{mA}, V_{IN} = 2 \text{V}, V_{OUT} = 1.4 \text{V}$ |   |      | 9    |      | nA            |

| Load Regulation                 | $\Delta V_{\text{OS}}$ | $I_{LOAD} = 1 \text{mA to } 100 \text{mA}, V_{IN} = 2 \text{V}, V_{OUT} = 1.4 \text{V}$ | • |      | 0.06 | 0.3  | mV            |

| Dropout Voltage                 | $V_{DROP}$             | $V_{IN} = 3.3V$ , $V_{SET} = 3.3V$ , $I_{LOAD} = 100$ mA                                | • |      | 250  | 320  | mV            |

| Ovice cont Comment in Charleson | I <sub>Q_SD</sub> \    | V <sub>IN</sub> = 6V, V <sub>EN</sub> = 0V                                              |   |      | 0.5  | 1    | μΑ            |

| Quiescent Current in Shutdown   |                        |                                                                                         | • |      |      | 5    | μA            |

|                                 |                        | $f_{RIPPLE} = 1kHz$ , $V_{RIPPLE} = 100mV_{PP}$ , $I_{LOAD} = 100mA$                    |   |      | 112  |      | dB            |

| Ripple Rejection                | PSRR                   | $f_{RIPPLE} = 100kHz$ , $V_{RIPPLE} = 100mV_{PP}$ , $I_{LOAD} = 100mA$                  |   |      | 78   |      | dB            |

|                                 |                        | $f_{RIPPLE} = 1MHz$ , $V_{RIPPLE} = 100mV_{PP}$ , $I_{LOAD} = 100mA$                    |   |      | 88   |      | dB            |

| Output RMS Noise                | $V_{\text{NOISE}}$     | BW = 10Hz to 100kHz, V <sub>OUT</sub> = 3.3V, I <sub>LOAD</sub> = 100mA                 |   |      | 0.9  |      | $\mu V_{RMS}$ |

| EN Threshold                    | $V_{EN\_TH}$           | V <sub>IN</sub> = 10V                                                                   | • | 1.18 | 1.25 | 1.32 | V             |

| EN Threshold Hysteresis         | V <sub>EN_HYS</sub>    | V <sub>IN</sub> = 10V                                                                   |   |      | 200  |      | mV            |

| EN Pin Current                  | I <sub>EN</sub>        | V <sub>IN</sub> = 10V, V <sub>EN</sub> = 1.4V                                           | • |      | 0.04 | 1    | μA            |

| Current Limit                   | I <sub>LIMIT</sub>     | V <sub>IN</sub> = 9V, V <sub>OUT</sub> = 0V                                             | • | 120  | 150  | 180  | mA            |

| PGFB Threshold                  | $V_{PGFB\_TH}$         | PGFB Rising                                                                             | • | 292  | 301  | 310  | mV            |

| PGFB Threshold Hysteresis       | V <sub>PGFB_HYS</sub>  |                                                                                         |   |      | 7    |      | mV            |

| PGFB Pin Current                | I <sub>PGFB</sub>      | V <sub>IN</sub> = 2V, V <sub>PGFB</sub> = 300mV                                         | • | -100 | -34  | 100  | nA            |

| PG Output Low Voltage           | $V_{PG\_LOW}$          | I <sub>PG</sub> = 100μA                                                                 | • |      | 50   | 100  | mV            |

| Thermal Shutdown                | T <sub>SD</sub>        | T <sub>J</sub> Rising                                                                   |   |      | 164  |      | °C            |

| Thermal Shutdown Hysteresis     | T <sub>SD_HYS</sub>    |                                                                                         |   |      | 7    |      | °C            |

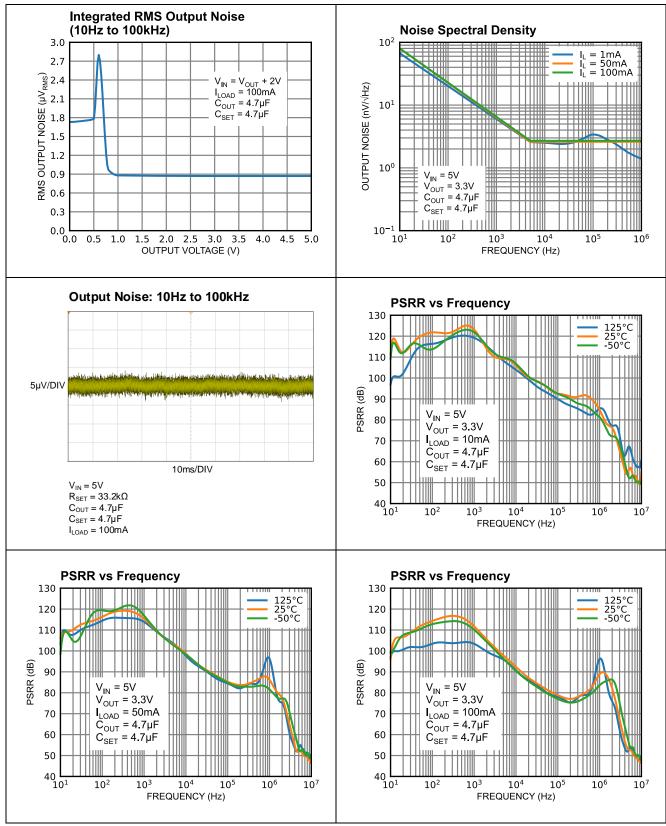

## TYPICAL PERFORMANCE CHARACTERISTICS

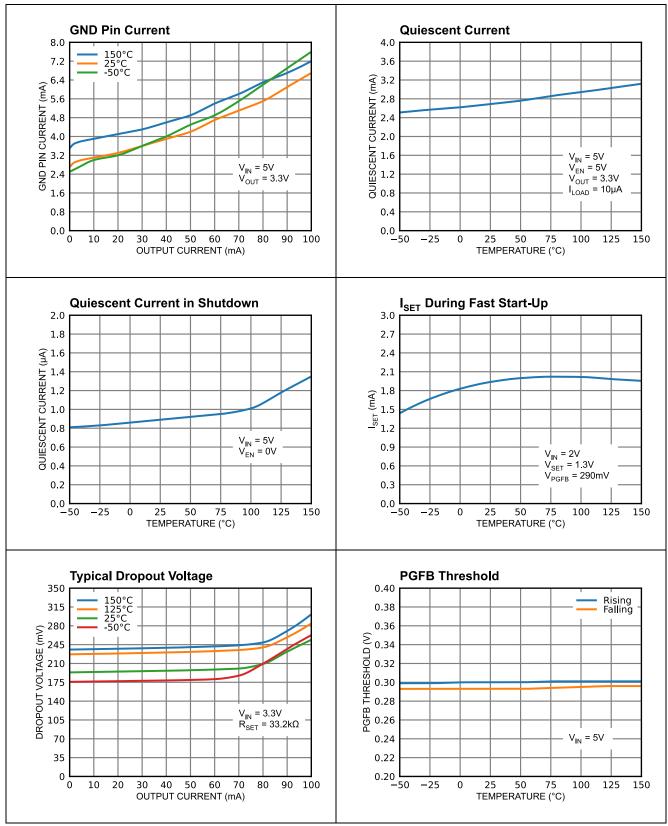

# TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)

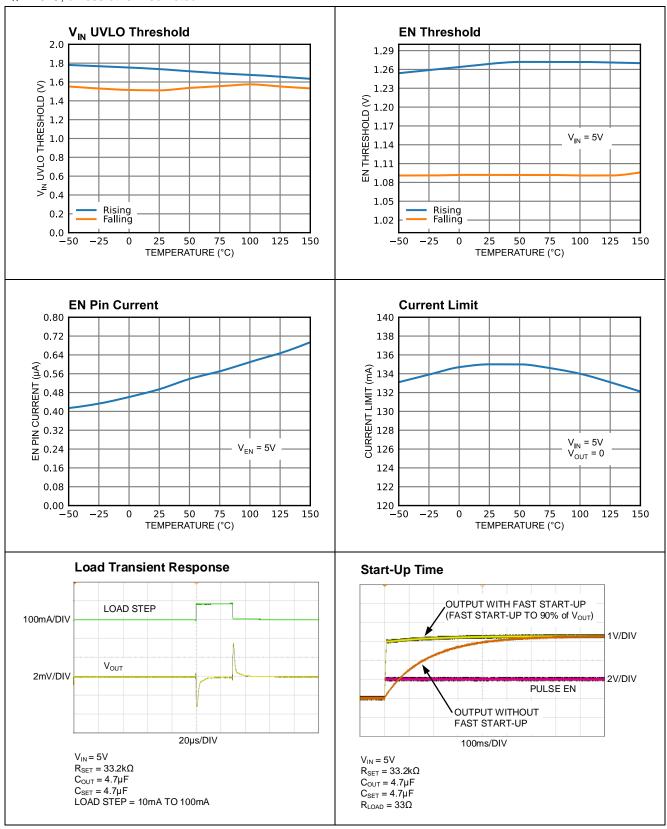

# TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)

# TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)

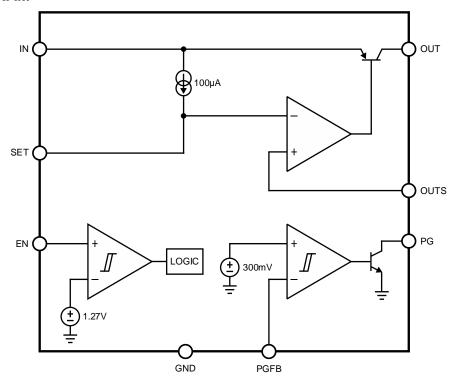

#### **BLOCK DIAGRAM**

### **OPERATION**

The 1033 is an ultralow noise and ultrahigh PSRR LDO for powering noise sensitive applications. It consists of a precision 100µA current reference, an error amplifier and a PNP pass device. With a resistor connected from SET to ground, the current reference flows of the SET pin and generates a reference voltage for the error amplifier. The error amplifier amplifies the difference of the reference voltage and feedback voltage from the output. When the load current increases it causes a reduction in the feedback voltage relative to the reference voltage, the base of the PNP devices will then be puller lower, allowing more current to be delivered and increasing the output voltage.

The 1033 incorporates all the necessary protections including input UVLO, short-circuit and thermal shutdown.

#### **Output Enable/ Undervoltage Lockout (UVLO)**

The EN pin is used to put the regulator into a shut-down state. The output voltage is enabled when the EN pin voltage exceeds 1.27V, and disabled when the EN pin voltage is less than 1.09V. If independent enable control of the output is not needed, then tie the EN to the IN pin. Do not float the EN pin. If a resistor divider between IN, EN and GND is used, the EN pin can set an input UVLO threshold to control the output voltage dependently.

### **Dropout Voltage**

Dropout voltage ( $V_{DROP}$ ) is defined as the  $V_{IN} - V_{OUT}$  voltage when  $V_{IN} = V_{OUT(NOMINAL)}$ . If the input falls below the nominal output regulation, then the output follows the input. The typical dropout voltage of 1033 is 250mV.

#### **Current Limit**

The 1033 includes a current limit circuit that limits the maximum output current to 135mA (typical). When the output load exceeds 135mA, the output voltage is reduced to maintain a constant current limit.

### **Thermal Shutdown**

When the 1033 junction temperature exceeds 164°C (typical), the internal thermal shutdown circuit disables the LDO. Thermal shutdown hysteresis assures the LDO resets (turns on) when the temperature falls to 157°C (typical). The internal thermal protection is designed to protect against the device under overload conditions. For reliable operation, limit the junction temperature to a maximum of 125°C.

### **Power-Good Function**

The 1033 includes a power good circuit that monitors the voltage at the power good feedback pin (PGFB) to indicate output voltage regulation. The power good pin (PG) will be pulled high by the external PG resistor if PGFB exceeds 300mV(typical), and will be internally pulled to ground when PGFB falls below 293mV (typical). Connecting a resistor divider between OUT, PGFB and GND sets a programmable power good threshold. If the power good function is not needed, float the PG pin.

#### Soft-Start and Fast Start-Up

Using a bypass capacitor at the SET pin improves the noise and PSRR performance of the 1033. Also, this bypass capacitor provides the soft-start capability for the output. The ramp-up time of the V<sub>OUT</sub> (from 0 to 90%, fast start-up disabled) can be expressed as:

$$t_{SS} \approx 2.3 \cdot R_{SET} \cdot C_{SET}$$

For the applications that ultralow noise is expected, the customer may use a larger SET pin bypass capacitor. Normally, this large bypass capacitor will significantly increase the start-up time. The 1033 features the fast start-up capability by increasing the SET pin current to about 2mA to speed up the start-up. This feature is automatically enabled during the start-up when PGFB voltage is below 300mV. When fast start-up is not used, connect PGFB to a voltage higher than 300mV (such as IN pin).

### APPLICATION INFORMATION

### **Adjustable Output**

The 1033 has an adjustable output voltage from 0 to 9V given a 2V to 12V input, by using a resistor R<sub>SET</sub> that connects the SET pin to GND. Use the below equation to calculate the resistor value needed for the desirable output voltage:

$$V_{OUT} = I_{SET} \cdot R_{SET}$$

The SET pin resistor should be a precision resistor to assure that reference voltage is enough accurate. Some factors in PCB may lead to a leakage current in SET pin, so high quality insulation is necessary. Since the SET pin is a high impedance node, a minimum 10nF SET capacitor is suggested to avoid unwanted coupling.

Table 1 lists the resistor value required to achieve a few of the most common rails using commercially available, 1% -tolerance resistors.

Table 1. Recommended SET Resistor Values

| Vout (V) | R <sub>SET</sub> (kΩ) |

|----------|-----------------------|

| 1.8      | 18.2                  |

| 3.3      | 33.2                  |

| 5.0      | 49.9                  |

#### **Output Sensing**

The OUTS pin is the noninverting input to the error amplifier. It's very important to tie the OUTS pin directly to the output capacitor and the GND side of  $C_{SET}$  to the GND side of the  $C_{OUT}$ , which decreases effects of PCB inductances. Place the GND side of  $C_{IN}$  and the GND side of the  $C_{OUT}$  as close to each other as possible.

#### **Stability and Capacitance Recommendation**

The 1033 is designed to be stable using low equivalent series resistance (ESR) ceramic capacitors at the output and input pin. For output capacitance, a minimum  $4.7\mu F$  capacitor with below  $50m\Omega$  of ESR and below 2nH ESL is recommended. A large output capacitance can only slightly improve the performance because it decreases the bandwidth of regulator.

Place a high-quality ceramic capacitor with low leakage in SET pin, and thus reduce the impact of current error in SET pin. A typical 4.7µF capacitance bypass capacitor is recommended.

A minimum  $4.7\mu F$  input ceramic capacitor with low ESR is recommended for the IN pin. Note that using a small ceramic input capacitance might cause the regulator to be instable. Use a larger capacitance ceramic input capacitor if a distantly located supply powers the input pin. The long wire inductance and the input capacitor, form a resonant LC circuit which might lead to the regulator's instability. In addition to using a larger input capacitor, using a series resistor (range from  $100m\Omega$  to  $500m\Omega$ ) between the supply and the input pin of regulator can also stabilize the regulator.

If the IN pin of 1033 is supplied by a switching converter's output in some applications, the ac current at the switching frequency flows through the input capacitor of 1033. Because the input capacitor is close to 1033, the current generates a magnetic field that couples to the 1033 output, which degrades the PSRR performance. The method to reduce the unwanted situation is that removes the input capacitor and places the switching converter's output capacitor far from 1033.

The switching converter's output may introduce very high frequency (larger than 100MHz) ripples to the IN pin of the 1033, which directly affect the output due to a low PSRR performance at very high frequency. A short PCB trace between the switcher's output and the 1033's input, which acts as inductance to a LC-filter, can be used to suppress these very high frequency ripples.

#### **Power Dissipation**

The power dissipation in the regulator (P<sub>D</sub>) can be calculated as below:

$$P_D = (V_{IN} - V_{OUT}) \cdot I_{LOAD} + V_{IN} \cdot I_{GND}$$

The junction temperature  $(T_J)$  of the device is dependent on the ambient temperature  $(T_A)$ , the power dissipation of the device  $(P_D)$ , and the junction to ambient thermal resistance of the package  $(\theta_{JA})$ . Using the following equation to calculate the maximum junction temperature:

$$T_J = T_A + P_D \cdot \theta_{JA}$$

The junction to ambient thermal resistance is highly dependent on the PCB layout. Careful attention to PCB thermal design is required if high maximum power dissipation exists in the application.

## **PCB Layout Guide**

PCB layout is very important to achieve good regulation, ripple rejection and thermal performance. Place input capacitor and output capacitor close to each other, and tie the GND side of C<sub>SET</sub> directly to the GND side of C<sub>OUT</sub>. For further details, please refer to Figure 1 for the example layout.

Figure 1. 1033 Example Layout

# **TYPICAL APPLICATION CIRCUITS**

Figure 2. Typical Application Circuit

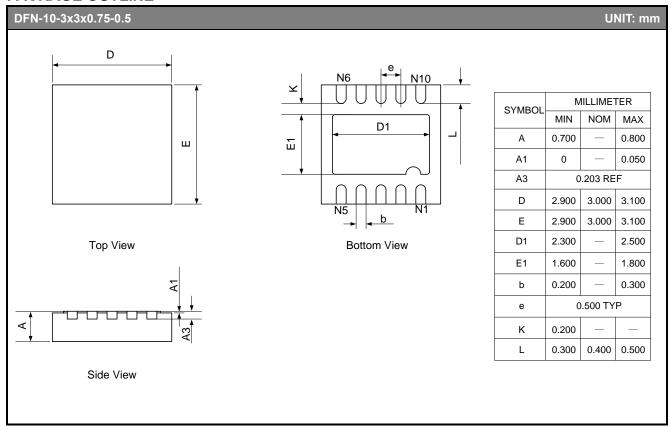

# **PACKAGE OUTLINE**

### Important notice:

- 1. The instructions are subject to change without notice!

- 2. Customers should obtain the latest relevant information before placing orders and should verify that such information is complete and current. Please read the instructions carefully before using our products, including the circuit operation precautions.

- 3. Our products are consumer electronic products or the other civil electronic products.

- 4. When using our products, please do not exceed the maximum rating of the products, otherwise the reliability of the whole machine will be affected. There is a certain possibility of failure or malfunction of any semiconductor product under specific conditions. The buyer is responsible for complying with safety standards and taking safety measures when using our products for system design, sample and whole machine manufacturing, so as to avoid potential failure risk that may cause personal injury or property loss.

- 5. It is strongly recommended to identify the trademark when buying our products. Please contact us if there is any question.

- 6. Product promotion is endless, our company will wholeheartedly provide customers with better products!

| Part No           | o.: 1033                                                   |      |            |  |  |  |

|-------------------|------------------------------------------------------------|------|------------|--|--|--|

|                   |                                                            |      |            |  |  |  |

| Rev.              | 1.1                                                        | Date | 2024-03-12 |  |  |  |

| Descrip           | Description:                                               |      |            |  |  |  |

| 1.                | 1. Update maximum output voltage from 8V to 9V.            |      |            |  |  |  |

| 2.                | 2. Some minor changes to ELECTRICAL CHARACTERISTICS table. |      |            |  |  |  |

| Rev.              | 1.0                                                        | Date | 2022-06-18 |  |  |  |

| Description:      |                                                            |      |            |  |  |  |

| 1. First release. |                                                            |      |            |  |  |  |

|                   |                                                            |      |            |  |  |  |