### **MPQ4242**

# 5A, 36V, Fully Integrated USB PD Solution with Integrated Buck-Boost Converter, AEC-Q100 Qualified

#### DESCRIPTION

The MPQ4242 is a fully integrated power delivery (PD) solution for USB Type-C sourcing ports. It integrates a buck-boost converter with four power switches and a USB PD controller. The device supports up to 5A of continuous output current ( $I_{OUT}$ ) under a certain input supply range.

The MPQ4242's USB Type-C port supports USB PD revision 3.0 with PPS. It is backward compatible with DCP schemes for battery charging specification (BC1.2), 3A divider mode, and 1.2V/1.2V mode. The MPQ4242 also supports QC 2.0/3.0 and Huawei FCP mode.

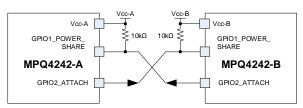

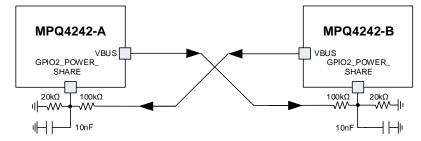

The MPQ4242 provides a configurable PD power management state machine when the battery voltage (V<sub>BATT</sub>) is low, or if an overtemperature condition occurs. When two MPQ4242s are used as dual PD ports, the internal power sharing logic can effectively distribute the total power.

Fault condition protections include I/O pin short for the BUS and VIN pins, CC over-current protection (OCP), current limiting with hiccup mode, output over-voltage protection (OVP), and thermal shutdown.

The MPQ4242 requires a minimal number of readily available, standard external components. It is available in a QFN-22 (4mmx5mm) package.

#### **FEATURES**

- All-In-One USB PD Solution for Automotive Sourcing Ports

- Integrated 4-Switch Buck-Boost Converter

- Integrated PD 3.0 Controller

- Wide 4.8V to 36V Operating Input Voltage (V<sub>IN</sub>) Range

- 3.3V to 22.5V Output Voltage (V<sub>OUT</sub>) Range

- Accurate Output CC Current Limit: ±5%

- External High-Side MOSFET (HS-FET) can be Paralleled

- Low I<sub>Q</sub> when USB Type-C is Disconnected

- 250kHz / 420kHz Configurable Frequency with Spread Spectrum

- Supports USB Type-C V2.0

- Supports USB PD R3.0, V2.0, and PPS with 7 PDO List

- Supports QC 3.0 Specification, Huawei FCP

- Supports DCP Schemes for BC1.2, 3A Divider Mode, and 1.2V/1.2V Mode

- CCx, DP, and DM Short to V<sub>BUS</sub> / V<sub>BATT</sub> Protection

- Battery Short to Ground Protection Driver

- I<sup>2</sup>C Slave Interface

- Output Line Drop Compensation

- Configurable PD Power Management during Low Battery Voltages or High Temperatures

- Supports Dual-Port PD Power Sharing

- PWM Duty Cycle Configurable LED Driver

- Up to 120 Minutes for EN Off Delay

- Available in a QFN-22 (4mmx5mm)

Package with Wettable Flanks

- Available in AEC-Q100 Grade 1

#### **APPLICATIONS**

- USB Power Delivery Charging Ports

- USB Power Supplies

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

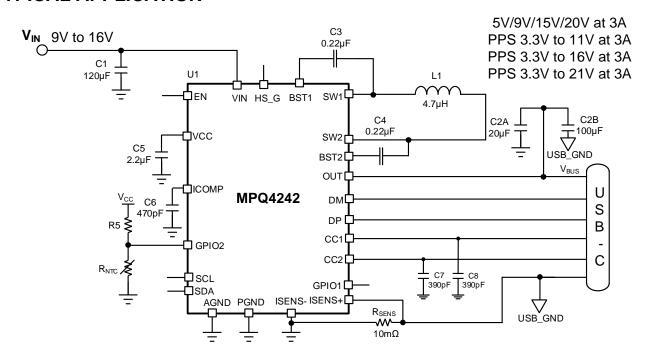

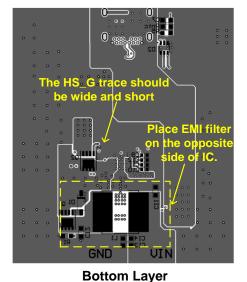

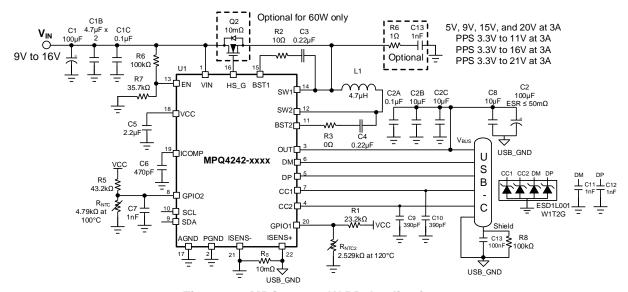

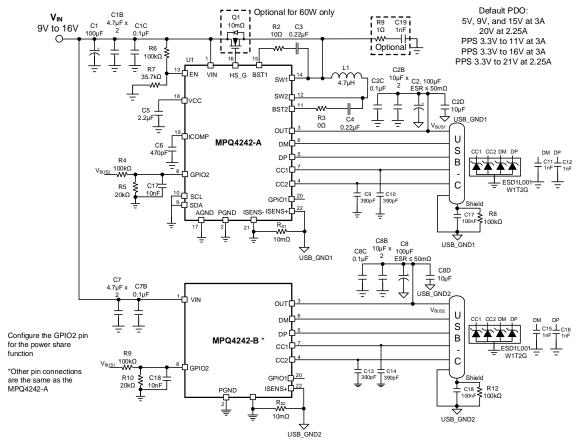

#### TYPICAL APPLICATION

#### ORDERING INFORMATION

| Part Number*           | Package   | Top Marking | MSL |

|------------------------|-----------|-------------|-----|

| MPQ4242GVE-0000-AEC1   |           |             |     |

| MPQ4242GVE-0001-AEC1   | QFN-22    | Soo Polow   | 4   |

| MPQ4242GVE-0015-AEC1   | (4mmx5mm) | See Below   | l l |

| MPQ4242GVE-xxxx-AEC1** |           |             |     |

| EVKT-MPQ4242           | -         | -           | -   |

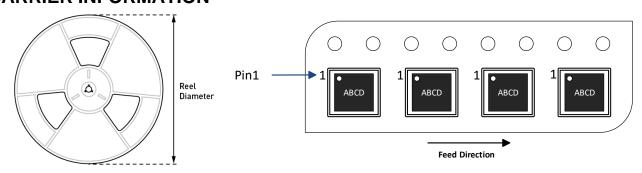

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MPQ4242GVE-xxxx-AEC1-Z).

#### **TOP MARKING**

MPSYWW MP4242 LLLLLL E

MPS: MPS prefix Y: Year code WW: Week code MP4242: Part number LLLLL: Lot number E: Wettable flank

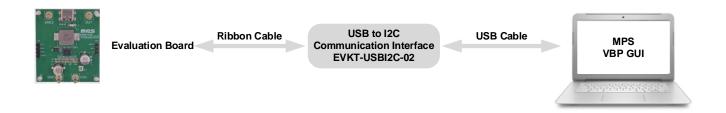

#### **EVALUATION KIT EVKT-MPQ4242**

EVKT-MPQ4242 kit contents (items below can be ordered separately):

| # | Part Number          | Item                                                                                                     | Quantity |

|---|----------------------|----------------------------------------------------------------------------------------------------------|----------|

| 1 | EVQ4242-VE-00B       | The MPQ4242 evaluation board                                                                             | 1        |

| 2 | EVKT-USBI2C-02       | Includes one USB to I <sup>2</sup> C communication interface device, one USB cable, and one ribbon cable | 1        |

| 3 | MPQ4242GVE-0000-AEC1 | The MPQ4242 IC, which can be used for OTP configurations                                                 | 2        |

Order directly from MonolithicPower.com or our distributors.

Figure 1: EVKT-MPQ4242 Evaluation Kit Set-Up

<sup>\*\* &</sup>quot;-xxxx" is the configuration code identifier for the register setting stored in the OTP. Each "x" can be a hexadecimal value between 0 and F. Work with an MPS FAE to create this unique number.

<sup>\*\*\*</sup> The MPQ4242GVE-0000-AEC1 is the default 60W PD version, which can be configured once by the one-time programmable (OTP) memory. The MPQ4242GVE-0001-AEC1 is the standard version for a 45W PD application, and it cannot be written with the OTP again.

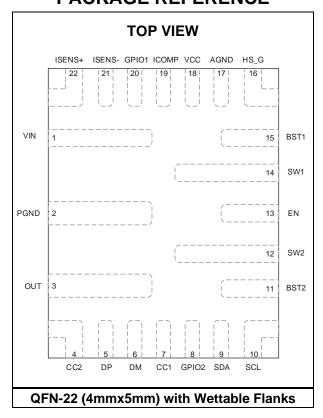

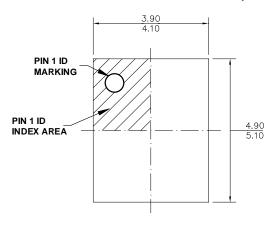

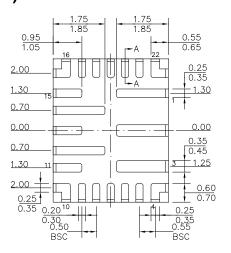

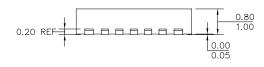

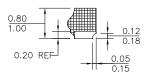

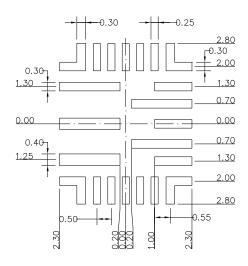

### **PACKAGE REFERENCE**

### **PIN FUNCTIONS**

| Pin # | Name  | Description                                                                                                                       |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                         |  |  |  |  |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1     | VIN   | capacitor (C <sub>IN</sub> ) is re the IC as possible.                                                                            | <b>Supply voltage.</b> The MPQ4242 operates from a 4.8V to 36V unregulated input. An input capacitor ( $C_{IN}$ ) is required to prevent large voltage spikes at the input. Place $C_{IN}$ as close to the IC as possible. The VIN pin is the drain of the internal power device, and it is the power supply for the whole chip. |                                                                                                                                                                                         |  |  |  |  |

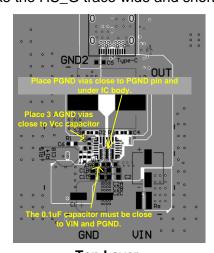

| 2     | PGND  | path to prevent swit                                                                                                              | ace the PGND pin outside of the $C_{\text{IN}}$ and output capacitor ( $C_{\text{OUT}}$ ) ground ching current spikes. PGND requires extra consideration during the PCB GND connection with copper traces and vias.                                                                                                              |                                                                                                                                                                                         |  |  |  |  |

| 3     | OUT   |                                                                                                                                   | <b>t pin.</b> $C_{\text{OUT}}$ is required to prevent large voltage spikes from appearing at post and boost mode. Place $C_{\text{OUT}}$ as close to the IC as possible.                                                                                                                                                         |                                                                                                                                                                                         |  |  |  |  |

| 4     | CC2   | Configuration characteristics a USB Type                                                                                          | <b>nnel (CC).</b> The CC2 pin discovers, configures, and manages connections -C cable.                                                                                                                                                                                                                                           |                                                                                                                                                                                         |  |  |  |  |

| 5     | DP    | D+ data line to US portable devices.                                                                                              | <b>B connector.</b> The DP pin is the input/output used for handshaking with                                                                                                                                                                                                                                                     |                                                                                                                                                                                         |  |  |  |  |

| 6     | DM    | <b>D- data line to US</b> portable devices.                                                                                       | B connector. The DM pin is the input/output used for handshaking with                                                                                                                                                                                                                                                            |                                                                                                                                                                                         |  |  |  |  |

| 7     | CC1   | Configuration Cha<br>across a USB Type                                                                                            | <b>nnel (CC).</b> The CC1 pin discovers, configures, and manages connections -C cable.                                                                                                                                                                                                                                           |                                                                                                                                                                                         |  |  |  |  |

|       | GPIO2 |                                                                                                                                   | POL                                                                                                                                                                                                                                                                                                                              | <b>USB Type-C polarity indication.</b> The POL pin is an open drain. When CC1 is selected as the CC line, POL is pulled low; when CC2 is selected as the CC line, POL is an open drain. |  |  |  |  |

|       |       | NTC                                                                                                                               | NTC thermal-sense input.                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                         |  |  |  |  |

|       |       | VCONN_IN                                                                                                                          | 1W VCONN power supply input.                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                         |  |  |  |  |

| 8     |       | LED_PWM                                                                                                                           | Output for the PWM driver to the LED.                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                         |  |  |  |  |

|       |       | ATTACH                                                                                                                            | Output to indicate if the device is attached. The ATTACH pin is active low.                                                                                                                                                                                                                                                      |                                                                                                                                                                                         |  |  |  |  |

|       |       | POWER_SHARE2                                                                                                                      | <b>Power sharing 2 input.</b> The POWER_SHARE2 pin is active high. When this pin's voltage exceeds 1.87V, the PD power drops to the PS_PDP_THD setting.                                                                                                                                                                          |                                                                                                                                                                                         |  |  |  |  |

| 9     | SDA   | I <sup>2</sup> C data line.                                                                                                       |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                         |  |  |  |  |

| 10    | SCL   | I <sup>2</sup> C clock signal in                                                                                                  | put.                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                         |  |  |  |  |

| 11    | BST2  |                                                                                                                                   | ect a 0.22µF capacitor between the SW2 and BST2 pins to form a floating igh-side switch driver.                                                                                                                                                                                                                                  |                                                                                                                                                                                         |  |  |  |  |

| 12    | SW2   | Switch 2 output. U                                                                                                                | se a wide PCB trace to make the SW2 connection.                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                         |  |  |  |  |

| 13    | EN    |                                                                                                                                   | Enable control pin. Apply a logic high voltage on the EN pin to enable the IC. Pull EN to logic low to disable the IC. The EN pin has an internal 6µA pull-up.                                                                                                                                                                   |                                                                                                                                                                                         |  |  |  |  |

| 14    | SW1   | Switch 1 output. Use a wide PCB trace to make the SW1 connection.                                                                 |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                         |  |  |  |  |

| 15    | BST1  | Bootstrap 1. Place a 0.22µF capacitor between the SW1 and BST1 pins to form a floating supply across the high-side switch driver. |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                         |  |  |  |  |

| 16    | HS_G  | High-side gate driv                                                                                                               | ver signal for an external N-channel MOSFET.                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                         |  |  |  |  |

| 17    | AGND  | Analog ground. Co                                                                                                                 | onnect the AGND pin to PGND.                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                         |  |  |  |  |

| 18    | VCC   | Internal 5V LDO re                                                                                                                | gulator output. Decouple the VCC pin with a 2.2µF capacitor.                                                                                                                                                                                                                                                                     |                                                                                                                                                                                         |  |  |  |  |

| 19    | ICOMP | Compensation pin capacitor.                                                                                                       | for the CC current limit loop. Decouple the ICOMP pin with a 470pF                                                                                                                                                                                                                                                               |                                                                                                                                                                                         |  |  |  |  |

### PIN FUNCTIONS (continued)

| Pin# | Name    | Description        |                                                                                                                                                                             |                                                                       |                                                   |                        |                         |  |  |

|------|---------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------|------------------------|-------------------------|--|--|

|      |         | GATE               | Gate drive for the extra GATE pin is an of the power MOSFET with GATE is not selected disabled.                                                                             | pen-drain<br>when the se                                              | structure. GATE pu                                | ulls low<br>mit is tri | to turn of<br>ggered. I |  |  |

|      |         | POWER_SHARE1       | <b>Power sharing 1 input.</b> The POWER_SHARE1 pin is active low. When this pin's voltage is low, the PD power drops to the value set by PS_PDP_THD.                        |                                                                       |                                                   |                        |                         |  |  |

|      | GPIO1 N | FAULT              | Fault indication. Oper pulls low.                                                                                                                                           | Fault indication. Open-drain output. If a fault occurs, the FAULT pin |                                                   |                        |                         |  |  |

| 20   |         | NTC2               | <b>Second NTC detection input.</b> If the NTC2 pin is triggered, PDP reduces its power to the set power share value.                                                        |                                                                       |                                                   |                        |                         |  |  |

|      |         | ATTACH FIT ALT     | Attach and fault indi<br>drain output. If no faul<br>when a sink plug-in is<br>truth table below for m                                                                      | t event has detected.                                                 | s occurred, this pin  <br>If a fault occurs, it p | puİls lov              | v for 12µs              |  |  |

|      |         | ATTACH_FLT_ALT     | Device Plug In                                                                                                                                                              | 0                                                                     | 1                                                 | 1                      | 0                       |  |  |

|      |         |                    | Fault Event                                                                                                                                                                 | 0                                                                     | 0                                                 | 1                      | 1                       |  |  |

|      |         | ATTACH_FLT_<br>ALT | Open<br>drain                                                                                                                                                               | 12µs pull-down<br>pulse                                               | Low                                               | Low                    |                         |  |  |

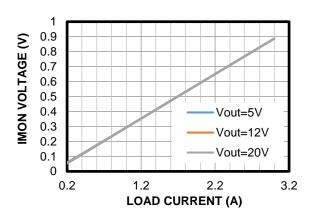

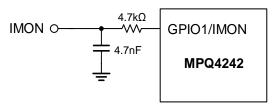

|      |         | IMON               | <b>Current monitor output.</b> The IMON pin represents the signal between the ISENS+ and ISENS- pins.                                                                       |                                                                       |                                                   |                        |                         |  |  |

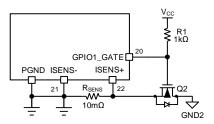

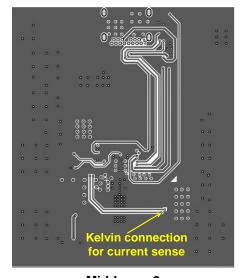

| 21   | ISENS-  |                    | Negative node of current-sense signal input. Place a current-sense resistor between the PGND pin and the USB port's GND. Connect the ISENS- pin to the PGND side.           |                                                                       |                                                   |                        |                         |  |  |

| 22   | ISENS+  |                    | Positive node of current-sense signal input. Place a current-sense resistor between the PGND pin and the USB port's GND. Connect the ISENS+ pin to the USB port's GND side. |                                                                       |                                                   |                        |                         |  |  |

### **ABSOLUTE MAXIMUM RATINGS (1)** Supply voltage (V<sub>IN</sub>) .....-0.3V to +40V $V_{HS\ G}$ .....-0.3V to $V_{IN}$ + 12V V<sub>EN</sub> .....-0.3V to +40V $V_{OUT}$ , $V_{CC1}$ , $V_{CC2}$ , $V_{DP}$ , $V_{DM}$ ....-0.3V to +26V V<sub>SW1</sub>.....-0.3V (-5V for <10ns) to $V_{IN} + 0.3V$ (+43V for <10ns) V<sub>SW2</sub>.....-0.3V (-5V for <10ns) to $V_{OUT} + 0.3V$ (29V for <10ns) $V_{BST1}$ ..... $V_{SW1} + 6.5V$ $V_{BST2}$ ..... $V_{SW2}$ + 6.5V All other pins .....-0.3V to +5.5V Continuous power dissipation ( $T_A = 25$ °C) (2) QFN-22 (4mmx5mm) ...... 4.55W Junction temperature ......150°C Lead temperature ......260°C Storage temperature.....-65°C to +150°C ESD Ratings (3) CC1/CC2/DP/DM (HBM) (4) ..... ±8kV Human body model (HBM) ..... ±2kV Charged device model (CDM) ..... ±750V Recommended Operating Conditions (5) Supply voltage (V<sub>IN</sub>) ......4.8V to 36V Output current......5A or 100W peak Operating junction temp (T<sub>J</sub>).... -40°C to +150°C

| Thermal Resistance   | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |      |

|----------------------|-------------------------|-------------------------|------|

| EVQ4242-VE-00B (6)   | 27.5                    | 5.2.                    | °C/W |

| QFN-22 (4mmx5mm) (7) | 44                      | 9.                      | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the device may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) HBM, per JEDEC specification JESD22-A114; CDM, per JEDEC specification JESD22-C101, AEC specification AECQ100-011. JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

- 4) HBM with regard to GND.

- The device is not guaranteed to function outside of its operating conditions.

- 6) Measured on MPQ4242 test board, 43mmx5mm, 4-layer PCB.

- 7) Measured on JESD51-7, 4-layer PCB. The value of θ<sub>JA</sub> given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7 and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

### **ELECTRICAL CHARACTERISTICS**

| Parameter                                                  | Symbol               | Condition                                                                        | Min   | Тур                  | Max   | Units |

|------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------|-------|----------------------|-------|-------|

| 0                                                          |                      | EN = 0V, T <sub>J</sub> = 25°C                                                   |       | 12                   | 20    | μA    |

| Supply current (shutdown)                                  | I <sub>IN</sub>      | EN = 0V, T <sub>J</sub> = -40°C ~125°C                                           |       | 12                   | 80    | μA    |

| Supply current (standby)                                   | IQ_STB               | No device attached, set EN to 1b via the I <sup>2</sup> C, T <sub>J</sub> = 25°C |       | 150                  | 200   | μA    |

| Supply current (quiescent)                                 | I <sub>Q_BB</sub>    | Buck-boost non-switching, CC attached                                            |       | 4                    |       | mA    |

| EN rising threshold                                        | VEN_RISING           |                                                                                  | -4%   | 1.3                  | +4%   | V     |

| EN hysteresis                                              | V <sub>EN_HYS</sub>  |                                                                                  |       | 100                  |       | mV    |

| EN pull-up current                                         | I <sub>EN</sub>      | V <sub>EN</sub> = 2V                                                             | 3     | 6                    | 9     | μΑ    |

| Thermal shutdown (8)                                       | T <sub>TSD</sub>     |                                                                                  |       | 175                  |       | °C    |

| Thermal hysteresis (8)                                     | T <sub>TSD_HYS</sub> |                                                                                  |       | 20                   |       | °C    |

| V <sub>IN</sub> under-voltage lockout threshold rising     | VIN_UVLO_RISING      |                                                                                  | -4%   | 4.3                  | +4%   | ٧     |

| V <sub>IN</sub> under-voltage lockout threshold hysteresis | VIN_UVLO_HYS         |                                                                                  |       | 400                  |       | mV    |

| VCC regulator                                              | Vcc                  |                                                                                  | 4.75  | 5                    | 5.25  | V     |

| VCC load regulation                                        | $V_{CC\_REG}$        | I <sub>CC</sub> = 70mA                                                           |       | 3                    |       | %     |

| VBUS_UV falling threshold 1                                | V <sub>BUS_UV1</sub> |                                                                                  | 2.9   | 3                    | 3.1   | V     |

| VBUS_UV falling threshold 2                                | V <sub>BUS_UV2</sub> |                                                                                  | -3%   | 4.5                  | +3%   | V     |

| <b>Buck-boost Converter</b>                                |                      |                                                                                  |       |                      |       |       |

| Switch A on resistance                                     | Rds_on_a             |                                                                                  |       | 16.3                 |       | mΩ    |

| Switch B on resistance                                     | R <sub>DS_ON_B</sub> |                                                                                  |       | 41.5                 |       | mΩ    |

| Switch C on resistance                                     | R <sub>DS_ON_C</sub> |                                                                                  |       | 15                   |       | mΩ    |

| Switch D on resistance                                     | R <sub>DS_ON_D</sub> |                                                                                  |       | 15.3                 |       | mΩ    |

| VHS_G voltage                                              | V <sub>HSG</sub>     |                                                                                  |       | V <sub>IN</sub> + 10 |       | ٧     |

| VHS_G source current (8)                                   | Insg                 |                                                                                  |       | 100                  |       | μA    |

| VHS_G pull-down                                            | R <sub>HS_DN</sub>   |                                                                                  |       | 3                    | 6.5   | Ω     |

|                                                            | V <sub>ОUТ0</sub>    |                                                                                  | -3%   | 3.3                  | +3%   | V     |

| Outrout wells as                                           | V <sub>OUT1</sub>    |                                                                                  | -2%   | 5                    | +2%   | V     |

| Output voltage                                             | V <sub>OUT2</sub>    |                                                                                  | -1.5% | 9                    | +1.5% | V     |

|                                                            | V <sub>OUT3</sub>    |                                                                                  | -1.5% | 20                   | +1.5% | V     |

| Output over-voltage protection (OVP)                       | Vove                 |                                                                                  | 112   | 117                  | 122   | %     |

| Output absolute OVP                                        | Vovp_abs             |                                                                                  | 24    | 25                   | 26    | V     |

| OVP recovery hysteresis                                    | V <sub>OVP_HYS</sub> |                                                                                  |       | 10                   |       | %     |

| Input over-voltage protection                              | V <sub>IN_OVP</sub>  | OTP trim option                                                                  | 21.4  | 22.4                 | 23.4  | V     |

| Input OVP recovery hysteresis                              | Vovp_hys             | OTP trim option                                                                  |       | 2                    |       | V     |

| Parameter                                 | Symbol                 | Condition                                                                                                | Min  | Тур | Max  | Units |

|-------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------|------|-----|------|-------|

|                                           |                        | V <sub>EN</sub> = 0V, V <sub>SW</sub> = 36V, T <sub>J</sub> = 25°C                                       |      |     | 1000 | nA    |

| Switch leakage                            | SWLKG                  | V <sub>EN</sub> = 0V, V <sub>SW</sub> = 36V, T <sub>J</sub> = -<br>40°C~125°C                            |      |     | 80   | μA    |

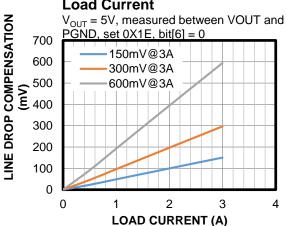

| Line drop compensation                    | VLDC                   | Set LINE_DROP_COMP to 01b via the I <sup>2</sup> C, Vout = 5V, lout = 3A (only enabled when Vout > 4.9V) |      | 150 |      | mV    |

| ISENS OC Threshold                        | loc <sub>1</sub>       | OC threshold = 1A,<br>$R_{SENS} = 10m\Omega$                                                             | 9    | 10  | 11   | mV    |

| ISENS OC TITESTICIO                       | I <sub>OC2</sub>       | OC threshold = $3A$ ,<br>$R_{SENS} = 10m\Omega$                                                          | 28.5 | 30  | 31.5 | mV    |

| Switch A current limit                    | I <sub>LIMIT1</sub>    | Switch A, boost mode                                                                                     |      | 20  |      | Α     |

| Switch B valley limit                     | I <sub>LIMIT2</sub>    | Switch B, buck mode                                                                                      |      | 6.7 |      | Α     |

| On all lates of the account of            | f <sub>SW1</sub>       | Set FREQ to 00b via the I <sup>2</sup> C                                                                 | 200  | 250 | 300  | kHz   |

| Oscillator frequency                      | f <sub>SW2</sub>       | Set FREQ to 01b via the I <sup>2</sup> C                                                                 | 350  | 420 | 490  | kHz   |

| Frequency dithering span                  | f <sub>DITH_SPAN</sub> | Set FREQ to 01b via the I <sup>2</sup> C                                                                 |      | ±11 |      | %     |

| Minimum on time (8)                       | ton_min                | Buck SWC                                                                                                 |      | 80  |      | ns    |

| Minimum off time (8)                      | toff_min               | Buck SWB                                                                                                 |      | 60  |      | ns    |

| Soft-start time                           | tss                    | 5V output from 10% to 90%,<br>Constant slew rate for other VouT                                          | 0.5  | 1.1 | 1.7  | ms    |

| Output discharge resistance               | R <sub>DIS_OUT</sub>   |                                                                                                          |      | 320 |      | Ω     |

| Ground NMOSFET Gate Drive                 | r                      |                                                                                                          |      | I.  | I.   |       |

| GND short to battery threshold            | $V_{RGND}$             | $R_{SENS} = 10m\Omega$                                                                                   |      | 135 |      | mV    |

| Short to battery retry delay (8)          | t <sub>SBP</sub>       |                                                                                                          |      | 1   |      | S     |

| Gate pull-down resistance                 | R <sub>PD</sub>        |                                                                                                          |      | 20  | 45   | Ω     |

| NTC, NTC2                                 |                        |                                                                                                          |      | I.  | I.   |       |

| External thermal sense triggering voltage | V <sub>NTC_ETY</sub>   | $R_P = 43.2k\Omega, R_{NTC} = 4.79k\Omega$<br>(100°C)                                                    | 8%   | 10% | 12%  | Vcc   |

| External thermal sense recovery voltage 1 | V <sub>NTC_RCY1</sub>  | Set NTC_HYSTERESIS to 0b via the I <sup>2</sup> C                                                        |      | 20% |      | Vcc   |

| External thermal sense recovery voltage 2 | V <sub>NTC_RCY2</sub>  | Set NTC_HYSTERESIS to 1b via the I <sup>2</sup> C                                                        |      | 30% |      | Vcc   |

| GPIO1                                     |                        |                                                                                                          |      |     |      |       |

| Power share input high                    | $V_{IH\_PS}$           |                                                                                                          | 2    |     |      | V     |

| Power share input low                     | V <sub>IL_PS</sub>     |                                                                                                          |      |     | 8.0  | V     |

| Power share pull-up resistance            | I <sub>LKG_PS</sub>    | 5V pull-up                                                                                               |      | 1   |      | МΩ    |

| Fault pull-down resistance                | R <sub>PD_FAULT</sub>  |                                                                                                          |      | 20  | 45   | Ω     |

| Fault leakage                             | ILKG_FAULT             |                                                                                                          |      |     | 3    | μA    |

| GPIO2                                     |                        |                                                                                                          |      |     |      |       |

| POL pull-down resistance                  | R <sub>PD_POL</sub>    | Connect CC1 to GND with a $5.1k\Omega$ resistor                                                          |      |     | 45   | Ω     |

| POL leakage                               | I <sub>LKG_POL</sub>   | Connect CC2 to GND with a 5.1kΩ resistor                                                                 |      |     | 3    | μΑ    |

| Parameter                                                   | Symbol                   | Condition                               | Min  | Тур  | Max  | Units |

|-------------------------------------------------------------|--------------------------|-----------------------------------------|------|------|------|-------|

| LED PWM output FREQ                                         | f <sub>LED</sub>         |                                         | 21   | 24   | 27   | kHz   |

| LED_PWM output duty                                         | D <sub>LED</sub>         |                                         |      | 50   |      | %     |

| Connected output                                            | Vатто                    | USB Type-C connected, force 50µA        |      |      | 0.4  | V     |

| Power share input threshold                                 | V <sub>TH_PS</sub>       |                                         | 1.52 | 1.87 | 2.22 | V     |

| <b>USB Charging Mode Identifica</b>                         | ation                    |                                         |      |      |      |       |

| BC1.2 DCP Mode                                              |                          |                                         |      |      |      |       |

| DP and DM short resistance                                  | R <sub>DP_DM_SHORT</sub> | $V_{DP} = 0.8V, I_{DM} = 1mA$           |      | 30   | 70   | Ω     |

| Divider Mode                                                |                          |                                         |      |      |      |       |

| DP output voltage                                           | V <sub>DIVIDER_DP</sub>  | Vout = 5V                               | 2.5  | 2.7  | 2.9  | V     |

| DM output voltage                                           | V <sub>DIVIDER_DM</sub>  | Vout = 5V                               | 3.05 | 3.3  | 3.55 | V     |

| DP output impedance                                         | R <sub>DIVIDER_DP</sub>  |                                         |      | 23   |      | kΩ    |

| DM output impedance                                         | R <sub>DIVIDER_DM</sub>  |                                         |      | 17   |      | kΩ    |

| 1.2V/1.2V Mode                                              |                          |                                         |      |      |      |       |

| DP/DM output voltage                                        | $V_{DP\_DM\_1.2V}$       | V <sub>OUT</sub> = 5V                   | 1.15 | 1.25 | 1.35 | V     |

| DP/DM output impedance                                      | R <sub>DP_DM_1.2V</sub>  |                                         |      | 75   |      | kΩ    |

| Quick Charge 3.0 Mode                                       |                          |                                         |      |      |      |       |

| DP/DM low voltage                                           | $V_{QC\_LOW}$            |                                         | 0.2  | 0.3  | 0.4  | V     |

| DP/DM high voltage                                          | V <sub>QC_HIGH</sub>     |                                         | 1.8  | 2    | 2.2  | V     |

| QC mode entry voltage glitch time (QC identify) (8)         | t <sub>QC_GLITCH</sub>   |                                         |      | 1000 |      | ms    |

| DP output impendence                                        | R <sub>DP_QC</sub>       |                                         |      | 350  |      | kΩ    |

| DM output impendence                                        | R <sub>DM_QC</sub>       |                                         |      | 20   |      | kΩ    |

| Request voltage time (8)                                    | tv_new_request           |                                         | 200  |      |      | ms    |

| Output voltage change glitch time (8)                       | tGLITCH_V_CHANGE         |                                         | 20   |      | 60   | ms    |

| Unplug V <sub>BUS</sub> discharge time (8)                  | tvbus_disc_qc            |                                         |      |      | 500  | ms    |

| CDP Mode                                                    |                          |                                         |      |      |      |       |

| DM CDP output voltage                                       | V <sub>DM_SRC</sub>      | $V_{DP} = 0.6V$ , DM sink = 250 $\mu$ A | 0.5  | 0.6  | 0.7  | V     |

| DP rising lower window threshold for V <sub>DM_SRC</sub> EN | V <sub>DAT_REF</sub>     |                                         | 0.25 | 0.35 | 0.45 | V     |

| DP rising lower window threshold hysteresis                 | VDAT_REF_HYS             |                                         |      | 30   |      | mV    |

| DP rising upper window threshold for V <sub>DM_SRC</sub>    | V <sub>LGC_SRC</sub>     |                                         | 0.8  | 0.9  | 1    | V     |

| DP rising upper window threshold hysteresis                 | VLGC_SRC_HYS             |                                         |      | 50   |      | mV    |

| FCP Mode                                                    | •                        |                                         |      |      |      |       |

| DM Tx high voltage <sup>(8)</sup>                           | V <sub>FCPT_H</sub>      | $R_{LOAD} = 15k\Omega$                  | 2.55 |      | 5    | V     |

| DM Tx low voltage <sup>(8)</sup>                            | V <sub>FCPT_L</sub>      | $R_{LOAD} = 15k\Omega$                  |      |      | 0.4  | V     |

| DM Rx high voltage                                          | V <sub>FCPR</sub> H      |                                         | 1.5  |      | 5    | V     |

| Parameter                                           | Symbol                 | Condition                                                                                                              | Min  | Тур | Max  | Units |

|-----------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| DM Rx low voltage                                   | V <sub>FCPR_L</sub>    | Condition                                                                                                              |      | 196 | 1    | V     |

| DM pull-low resistance                              | RLD_D-                 |                                                                                                                        |      | 15  | '    | kΩ    |

| Unit interval of PHY <sup>(8)</sup>                 | UI                     |                                                                                                                        | 144  | 160 | 176  |       |

| USB Type-C - CC1 and CC2 p                          | _                      |                                                                                                                        | 144  | 100 | 170  | μs    |

| CC pull-up current 1                                | I <sub>RP1</sub>       | V 5V @ 2A T 0°C to 95°C                                                                                                | -8%  | 330 | +8%  |       |

| CC pull-up current 2                                |                        | V <sub>BUS</sub> = 5V @ 3A, T <sub>J</sub> = 0°C to 85°C<br>V <sub>BUS</sub> = 5V @ 1.5A, T <sub>J</sub> = 0°C to 85°C | -8%  | 180 |      | μΑ    |

|                                                     | I <sub>RP2</sub>       | VBUS = 5V @ 1.5A, 1J = 0 C to 65 C                                                                                     | -0%  | 100 | +8%  | μA    |

| CC voltage to enable VCONN for 3A USB Type-C mode   | V <sub>RA1</sub>       |                                                                                                                        |      |     | 0.75 | V     |

| CC voltage to enable VBUS for 3A USB Type-C mode    | V <sub>RD1</sub>       |                                                                                                                        | 0.85 |     | 2.45 | V     |

| CC disconnect threshold for 3A USB Type-C mode      | V <sub>OPEN1</sub>     |                                                                                                                        | 2.75 |     |      | V     |

| CC voltage to enable VCONN for 1.5A USB Type-C mode | V <sub>RA2</sub>       |                                                                                                                        |      |     | 0.35 | V     |

| CC voltage to enable VBUS for 1.5A USB Type-C mode  | $V_{RD2}$              |                                                                                                                        | 0.45 |     | 1.5  | V     |

| CC disconnect threshold for 1.5A USB Type-C mode    | V <sub>OPEN2</sub>     |                                                                                                                        | 1.7  |     |      | V     |

| CC voltage falling de-bounce timer                  | tcc_debounce           | VBUS enable deglitch                                                                                                   | 100  | 150 | 200  | ms    |

| CC voltage rising de-bounce timer                   | tpd_debounce           | VBUS disable deglitch                                                                                                  | 5    | 10  | 15   | ms    |

| 100mW VCONN output power                            | Pvconn_100m<br>W       | Default                                                                                                                | 100  |     |      | mW    |

| 1W VCONN output power                               | Pvconn_1w              | Set GPIO2 to 011b via the I2C                                                                                          | 1    |     |      | W     |

| USB PD                                              |                        |                                                                                                                        |      |     |      |       |

| Unit interval time (8)                              | tui                    |                                                                                                                        | 3.03 |     | 3.7  | μs    |

| Transmitter                                         |                        |                                                                                                                        |      |     |      |       |

| End drive BMC time (8)                              | t <sub>EDBMC</sub>     |                                                                                                                        |      |     | 23   | μs    |

| Falling time (8)                                    | t <sub>FALL</sub>      |                                                                                                                        | 300  | 400 |      | ns    |

| Rising time (8)                                     | t <sub>RISE</sub>      |                                                                                                                        | 300  | 400 |      | ns    |

| Hold low BMC time (8)                               | thlbmc                 |                                                                                                                        | 1    |     |      | μs    |

| Logic high voltage                                  | V <sub>LH</sub>        |                                                                                                                        | 1.05 |     | 1.2  | V     |

| Logic low voltage                                   | V <sub>LL</sub>        |                                                                                                                        |      |     | 70   | mV    |

| Output impedance                                    | Z <sub>TX</sub>        |                                                                                                                        |      | 45  |      | Ω     |

| Receiver (8)                                        | <u> </u>               |                                                                                                                        |      | •   |      |       |

| CC receiver capacitance                             | Creceiver              |                                                                                                                        |      |     | 600  | pF    |

| Transitions for signal detection                    | NTRANSITION            |                                                                                                                        | 3    |     |      | Edges |

| Rx bandwidth limiting filter                        | t <sub>RX_FILTER</sub> |                                                                                                                        | 100  |     |      | ns    |

| Time window for detecting non-idle                  | transition_wi          |                                                                                                                        | 12   |     | 20   | μs    |

$V_{IN}$  = 12V,  $V_{EN}$  = floating,  $T_J$  = -40°C to +150°C, typical value is tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                          | Symbol                  | Condition                                         | Min  | Тур | Max  | Units |

|----------------------------------------------------|-------------------------|---------------------------------------------------|------|-----|------|-------|

| Receiver input impedance                           | $Z_{BMC\_RX}$           |                                                   | 1    |     |      | МΩ    |

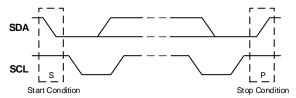

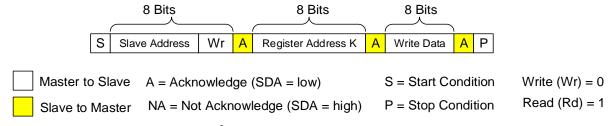

| I <sup>2</sup> C Interface Specifications          | <b>s</b> <sup>(8)</sup> | •                                                 |      | •   | •    | •     |

| Input logic high                                   | ViH                     | I <sup>2</sup> C pull-up VDD can be to 1.8V to 5V | 1.26 |     |      | V     |

| Input logic low                                    | V <sub>IL</sub>         |                                                   |      |     | 0.54 | V     |

| Output voltage logic low                           | V <sub>OUT_L</sub>      |                                                   |      |     | 0.45 | V     |

| SCL clock frequency                                | f <sub>SCL</sub>        |                                                   |      | 400 |      | kHz   |

| SCL high time                                      | t <sub>HIGH</sub>       |                                                   | 60   |     |      | ns    |

| SCL low time                                       | tLOW                    |                                                   | 160  |     |      | ns    |

| Data set-up time                                   | tsu_dat                 |                                                   | 10   |     |      | ns    |

| Data hold time                                     | thd_dat                 |                                                   |      | 70  |      | ns    |

| Set-up time for repeated start condition           | tsu_sta                 |                                                   | 160  |     |      | ns    |

| Hold time for repeated start condition             | thd_sta                 |                                                   | 160  |     |      | ns    |

| Bus free time between a start and a stop condition | t <sub>BUF</sub>        |                                                   | 160  |     |      | ns    |

| Set-up time for stop condition                     | tsu_sto                 |                                                   | 160  |     |      | ns    |

| Rising time of SCL and SDA                         | t <sub>R</sub>          |                                                   | 10   |     | 300  | ns    |

| Falling time of SCL and SDA                        | t⊧                      |                                                   | 10   |     | 300  | ns    |

| Pulse width of suppressed spike                    | tsp                     |                                                   | 0    |     | 50   | ns    |

| Capacitance bus for each bus line                  | Св                      |                                                   |      |     | 400  | pF    |

| SCL low time                                       | t <sub>LOW</sub>        |                                                   | 160  |     |      | ns    |

#### Note:

8) Guaranteed by characterization sample test.

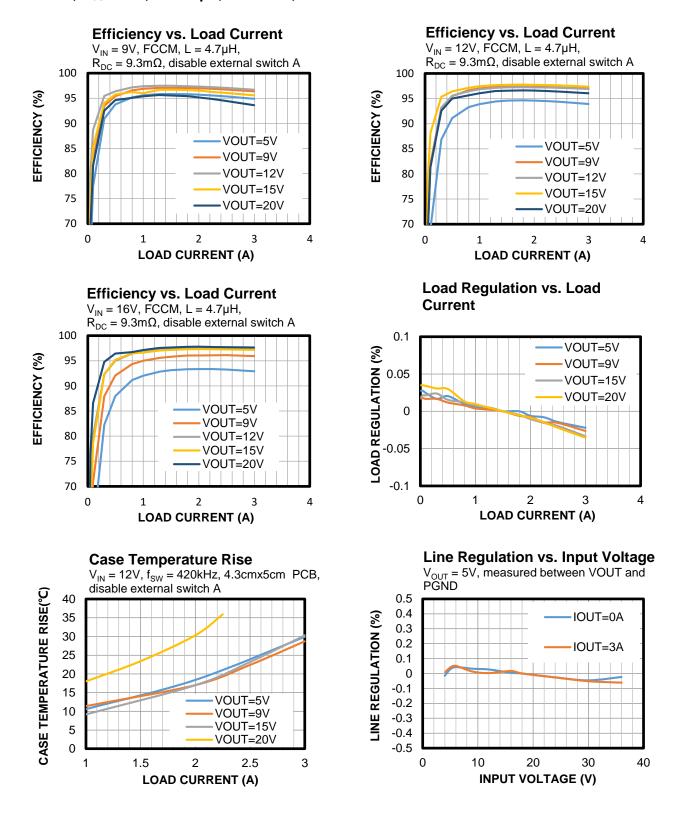

#### TYPICAL CHARACTERISTICS

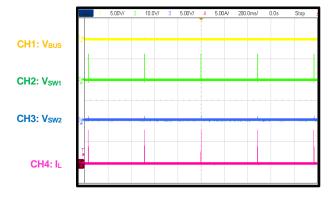

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

#### **IMON Voltage vs. Load Current**

## Line Drop Compensaton vs. Load Current

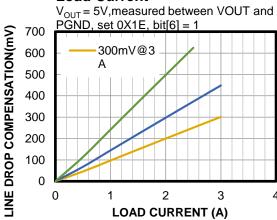

# Line Drop Compensaton vs. Load Current

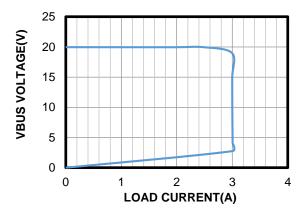

### **VBUS Voltage vs. Load Current**

#### TYPICAL PERFORMANCE CHARACTERISTICS

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

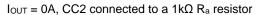

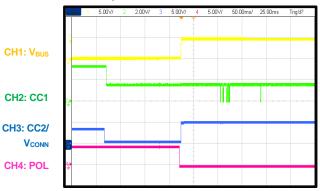

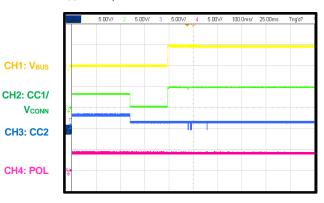

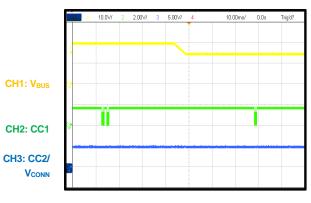

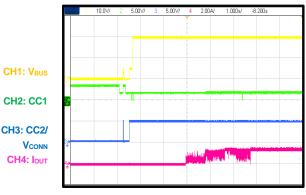

CH2: CC1

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

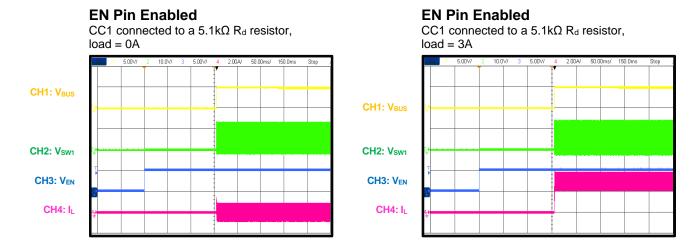

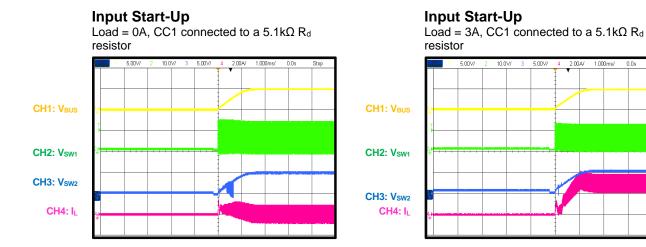

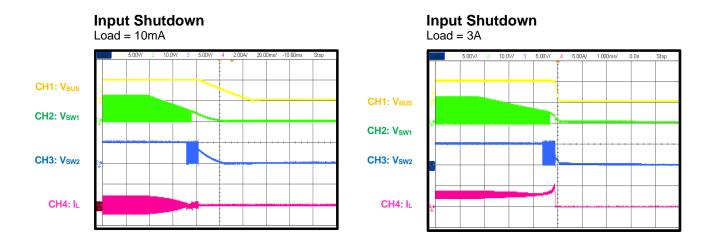

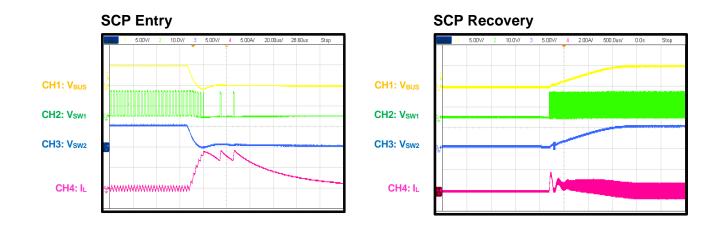

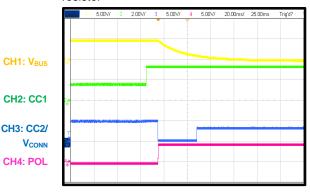

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

#### **SCP Steady State**

#### CC1 Connected to R<sub>d</sub> to Enable **VBUS**

#### CC1 Disconnected from Rd to Disable VBUS

$I_{OUT} = 0A$ , CC2 connected to a  $1k\Omega$  R<sub>A</sub> resistor

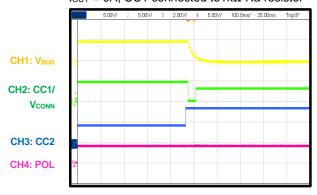

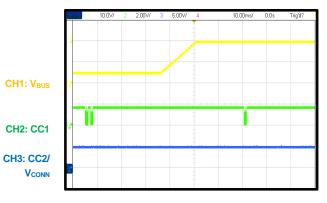

#### CC2 Connected to R<sub>d</sub> to Enable **VBUS**

$I_{OUT} = 0A$ , CC1 connected to a  $1k\Omega$  R<sub>A</sub> resistor

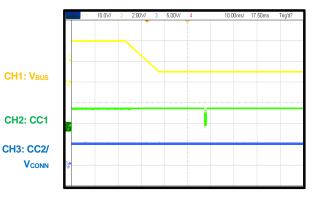

#### CC2 Disconnected from R<sub>d</sub> to **Disable VBUS**

$I_{OUT} = 0A$ , CC1 connected to 1k $\Omega$  Ra resistor

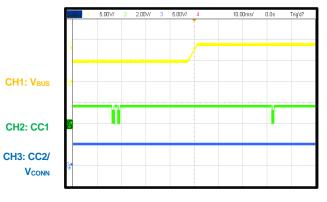

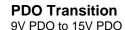

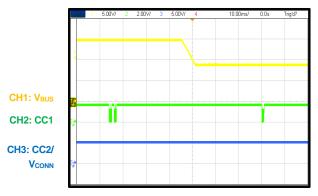

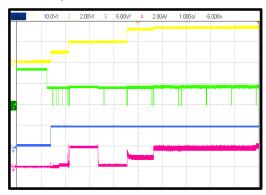

#### **PDO Transition**

5V PDO to 9V PDO

V<sub>CONN</sub>

CH1: V<sub>BUS</sub>

CH2: CC1

CH3: CC2/

**V**CONN

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

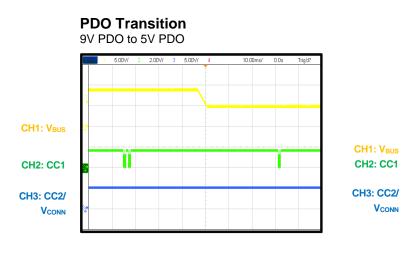

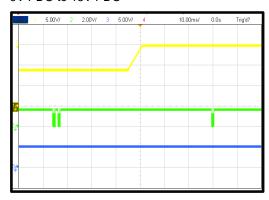

#### **PDO Transition**

15V PDO to 9V PDO

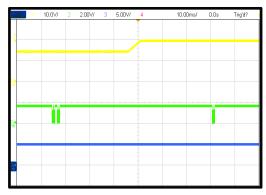

#### **PDO Transition**

15V PDO to 20V PDO

#### **PDO Transition**

20V PDO to 15V PDO

#### **PDO Transition**

5V PDO to 20V PDO

CH1: V<sub>BUS</sub>

CH2: CC1

CH3: CC2/

V<sub>CONN</sub>

CH4: I<sub>OUT</sub>

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

#### **PDO Transition**

20V PDO to 5V PDO

### **Mobile Phone Charging Test**

Phone requests 3.3V to 21V APDO

### **Laptop Charging Test**

Laptop requests 20V PDO

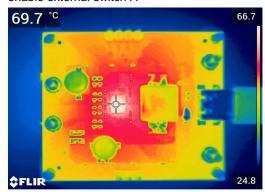

#### **Thermal Image**

$V_{\text{IN}}$  = 13.5V,  $V_{\text{OUT}}$  = 20V,  $I_{\text{OUT}}$  = 3A,  $f_{\text{SW}}$  = 420kHz, 4.3cmx5cm PCB, top/bottom layer: 2oz; mid-layer 1 and 2: 1oz, enable external switch A

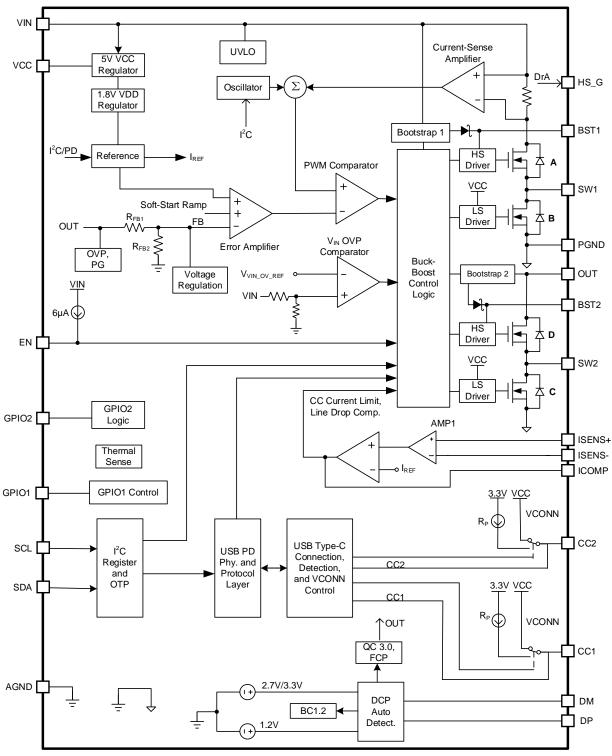

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 2: Functional Block Diagram

#### **OPERATION**

The MPQ4242 is a buck-boost converter with four integrated switches and USB charging protocols. The buck-boost converter works in current mode, which provides a fast transient response for buck, boost, and buck-boost modes. One special buck-boost control strategy provides high efficiency across the full input range and smooths transitions between different modes. Figure 2 on page 21 shows the internal block diagram.

#### **Pulse-Width Modulation (PWM) Operation**

The MPQ4242 operates in a fixed-frequency peak current mode control to regulate the output voltage ( $V_{OUT}$ ). The internal clock initiates the PWM cycle and turns on the related power switch. The switch remains on until its current reaches the value set by the COMP voltage ( $V_{COMP}$ ). When the power switch is off, it remains off until the next clock cycle starts. The switching frequency ( $f_{SW}$ ) can be configured to 250kHz or 420kHz via the I<sup>2</sup>C.

#### **Buck-Boost Operation**

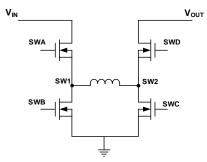

The MPQ4242 can regulate  $V_{\text{OUT}}$  to be above, below, or equal to the input voltage ( $V_{\text{IN}}$ ). Figure 3 shows a buck-boost power structure with one inductor and four switches (SWA, SWB, SWC, and SWD).

Figure 3: Buck-Boost Topology

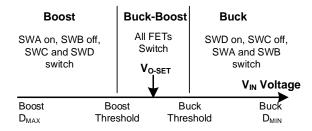

Buck mode, boost mode, and buck-boost mode can have different V<sub>IN</sub> inputs (see Figure 4).

Figure 4: Buck-Boost Operation Range

#### Buck Mode ( $V_{IN} > V_{OUT}$ )

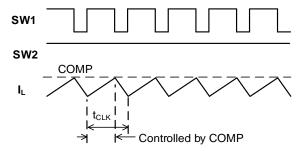

When  $V_{\text{IN}}$  exceeds  $V_{\text{OUT}}$ , the MPQ4242 works in buck mode. In buck mode, switch A (SWA) and switch B (SWB) switch for buck regulation. Meanwhile, switch C (SWC) is off, and switch D (SWD) stays on to conduct the inductor current ( $I_L$ ).

SWA works with a peak current mode control logic, and SWB turns on until the  $t_{\text{CLK}}$  times out. In each buck mode cycle, SWA turns on to charge  $I_{\text{L}}$ . When  $I_{\text{L}}$  reaches the value set by  $V_{\text{COMP}}$ , SWA turns off and SWB turns on. SWB stays on until the next clock begins. Then SWA turns on and the cycle repeats. The COMP signal is the error amplifier (EA) output from the  $V_{\text{OUT}}$  feedback and the internal FB reference voltage. Figure 5 shows the buck mode waveform.

Figure 5: Buck Mode Waveform

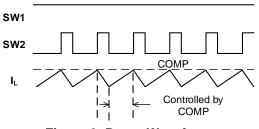

#### Boost Mode ( $V_{IN} < V_{OUT}$ )

When  $V_{\text{IN}}$  is below  $V_{\text{OUT}}$ , the MPQ4242 works in boost mode. In boost mode, SWC and SWD switch for boost regulation. Meanwhile, SWB is off and SWA stays on to conduct  $I_L$

SWC turns on at the beginning of each clock cycle. SWC turns off when  $I_L$  reaches the value set by  $V_{COMP}$ . SWD turns on until  $t_{CLK}$  times out to boost  $I_L$  to the output. Figure 6 shows the boost work waveform.

Figure 6: Boost Waveform

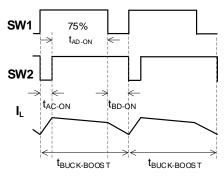

#### Buck-Boost Mode ( $V_{IN} \approx V_{OUT}$ )

When  $V_{\text{IN}}$  is almost equal to  $V_{\text{OUT}}$ , the converter cannot provide enough energy to the load in buck mode due to SWA's minimum off time. In boost mode, the converter supplies too much power to the load due to SWC's minimum on time. Under these conditions, the MPQ4242 adopts buck-boost control to regulate the output (see Figure 7).

Figure 7: Buck-Boost Waveform

If  $V_{\text{IN}}$  is almost equal to  $V_{\text{OUT}}$ , buck-boost mode activates. The MOSFET turn-on sequence is as follows:

- 1. SWA and SWC

- 2. SWA and SWD

- 3. SWB and SWD

Throughout this process,  $I_L$  can reach the  $V_{\text{COMP}}$  requirement, and supply enough current to the output.

The SWA and SWD turn-on time is fixed to 75% of the buck-boost operation frequency.

If the buck mode minimum off time is almost reached, the IC enters buck-boost mode. If  $V_{\text{IN}}$  is about 10% above  $V_{\text{OUT}}$  in buck-boost mode, the IC changes to buck mode. If  $V_{\text{IN}}$  is about 10% below  $V_{\text{OUT}}$ , the IC enters boost mode. If the boost mode minimum on time is almost reached, the IC enters buck-boost mode.

#### **External High-Side MOSFET Gate Driver**

An external N-channel MOSFET can be added to improve system efficiency, especially for PD applications exceeding 45W. For applications below 45W, an external MOSFET is not required, and EXT\_HS\_FET\_RON should be set to 000b.

The external MOSFET is paralleled with the internal SWA. To accurately sense the input current, a  $5m\Omega$  to  $12m\Omega$  R<sub>DS(ON)</sub> MOSFET is

recommended. The EXT\_HS\_FET\_RON configuration value should match (or be close to) the MOSFET's real  $R_{\rm DS(ON)}$  under a  $10V_{\rm GS}$  condition. The external MOSFET only turns on in boost mode when  $V_{\rm IN}$  is significantly below  $V_{\rm OUT}$ .

#### 5V Internal VCC Regulator

The 5V internal regulator powers the CC pin's pull-up, VCONN, and most of the internal logic circuitries. The regulator takes the VIN input and operates across the full  $V_{\rm IN}$  range. When  $V_{\rm IN}$  exceeds 5V, the regulator's output is in full regulation. If  $V_{\rm IN}$  is below 5V, the output decreases with  $V_{\rm IN}$ .

The VCC pin can support 0.1W of output power ( $P_{OUT}$ ). The VCC pin requires a 2.2 $\mu$ F ceramic decoupling capacitor.

#### Under-Voltage Lockout (UVLO)

Under-voltage lockout (UVLO) protects the chip from operating at an insufficient supply voltage. The MPQ4242's UVLO comparator monitors V<sub>IN</sub>.

#### **Internal Soft-Start**

Soft start prevents the converter's  $V_{OUT}$  from overshooting during start-up. When the chip starts, the internal circuitry generates a soft-start voltage ( $V_{SS}$ ) that ramps up from 0V to 5V. When SS is below the reference voltage ( $V_{REF}$ ), the error amplifier uses  $V_{SS}$  as the reference. When  $V_{SS}$  exceeds  $V_{REF}$ , the error amplifier uses  $V_{REF}$  as the reference. The SS time is internally set to 1ms for a 5V  $V_{OUT}$ .

If the output of the MPQ4242 is pre-biased to a certain voltage during start-up, the IC disables the switching of both the high-side and low-side switches until the voltage on the internal soft-start capacitor exceeds the internal feedback voltage.

#### Constant Current (CC) Mode Over-Current-Protection (OCP)

The MPQ4242 senses the ground current via an external current-sense resistor. The device uses this information to limit the output current ( $I_{OUT}$ ). This is a highly accurate current limit. If  $I_{OUT}$  exceeds the current-limit threshold, the MPQ4242 enters constant current (CC) limit mode, and the current amplitude is limited.

If the MPQ4242 works in fixed PDO mode, it sends a hard reset message once I<sub>OUT</sub> exceeds the constant current limit. If the MPQ4242 works

in APDO mode and continues to reduce the load resistance,  $V_{\text{OUT}}$  drops until reaches its undervoltage (UV) threshold (about 3V). If a UV condition is triggered, the MPQ4242 sends a hard reset message. If  $I_{\text{OUT}}$  still exceeds the overcurrent protection (OCP) threshold, the MPQ4242 enters hiccup mode to periodically restart the part.

This protection is especially useful when the output is dead-shorted to ground. This operation greatly reduces the average short-circuit current, alleviates thermal issues, and protects the regulator. The MPQ4242 exits hiccup mode once the OC condition is removed.

The current limit threshold can be set from 1A to 6.35A (with a 50mA resolution) via the I<sup>2</sup>C.

#### Peak and Valley Current Limit.

In addition to the output CC limit, the MPQ4242 also has SWA peak current and SWB valley current limits.

In buck mode and buck-boost mode, both the SWA peak current limit and the SWB valley current limit work as thresholds. The SWB's valley current limit has a 6.7A falling threshold. In boost mode, only the SWA peak current limit threshold operates. The peak current limit can be configured via the I<sup>2</sup>C or one-time-programmable (OTP) memory.

#### **Output Over-Voltage Protection (OVP)**

The MPQ4242 has output over-voltage protection (OVP). If  $V_{\text{OUT}}$  exceeds 117% of  $V_{\text{REF}}$ , SWA, SWB, SWC, and SWD turn off. The resistor discharge path from the OUT pin to ground turns on. When  $V_{\text{OUT}}$  drops to 107% of  $V_{\text{REF}}$ , the chip returns to normal operation.

The absolute output OVP threshold is about 25V. The discharge resistor turns on when absolute OVP is triggered.

#### Input Over-Voltage Protection (V<sub>IN</sub> OVP)

The MPQ4242 has input OVP. If  $V_{\text{IN}}$  exceeds its OVP rising threshold (about 22V), SWA, SWB, SWC, and SWD turn off. The chip returns to normal operation when  $V_{\text{IN}}$  drops to its OVP falling threshold (about 20V).

$V_{\text{IN}}$  OVP if disabled by default, and it is controlled by OTP trimming. The MPQ4242-0000 does not have  $V_{\text{IN}}$  OVP. The MPQ4242-0001 provides  $V_{\text{IN}}$  OVP.

#### Floating Driver and Bootstrap Charging

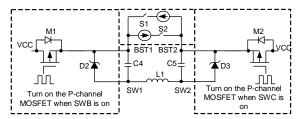

An external bootstrap capacitor powers the floating power MOSFET driver. This floating driver has its own UVLO protection. Its UVLO rising threshold is 2.2V, with a hysteresis of 150mV. The BST1 capacitor's voltage is regulated internally by VCC through D2, M1, and C4. The BST2 capacitor's voltage is regulated internally by VCC through D3, M2, and C5 (see Figure 8).

Figure 8: Internal Bootstrap Charging Circuit

In buck mode, S2 is always on, and BST2 is charged by BST1. In boost mode, S1 is always on, and BST1 is charged by BST2.

#### **Output Line Drop Compensation**

The MPQ4242 is capable of compensating for a  $V_{\text{OUT}}$  drop.

If  $I_{OUT}$  is 0A, there is no compensation. If  $I_{OUT}$  is 3A, the line drop compensation voltage is 150mV. For example, if the USB output current exceeds 3A, the line drop compensation voltage stays at 150mV and does not rise. The line drop compensation value can be set to 150mV, 300mV, or 600mV via 0x18, bits[2:1]. Set 0x1E, bit[6] = 1 to enable an additional compensation voltage. Then the line drop compensation value can be set to 300mV, 450mV, or 750mV when the load is 3A.

Line drop compensation can be configured via the I<sup>2</sup>C or OTP. The compensated voltage is the same for all voltages.

For the default IC, line drop compensation is disabled in PPS mode. Line drop compensation can be enabled in PPS mode through factory OTP trimming.

#### Thermal Shutdown

Thermal shutdown prevents the chip from operating at exceedingly high temperatures.

If the silicon die temperature exceeds 175°C, the whole chip shuts down. When the temperature

falls below its lower threshold (about 155°C), the chip is enabled again.

# CHARGING MODE AUTO-DETECTION Legacy USB 2.0 Mode

The MPQ4242 integrates a USB-dedicated charging port automatic detection function that recognizes most mainstream portable devices. The device supports the following charging schemes:

- USB battery charging specification (BC1.2) / Chinese Telecommunications Industry Standard YD/T 1591-2009

- Apple 3A Divider Mode

- 1.2V/1.2V Mode

- QC 3.0

- Huawei FCP Class A

The automatic detection function is a state machine that supports all of the above DCP charging schemes. This function starts in 3A divider mode. If a device compliant to divider mode is connected, the MPQ4242 stays in divider mode. Meanwhile, 3.3V is applied to the DM pin, while 2.7V is applied to the DP pin.

If a BC1.2 or YD/T 1591-2009 compliant device is connected, the MPQ4242 operates in 1.2V/1.2V and BC1.2 DCP mode. In this scenario, DM and DP are shorted together with a resistance. The device then stays in this mode until the data line is released. If this occurs, the MPQ4242 returns to 3A divider mode.

When a QC 3.0 or FCP device (without PD protocol) is connected, the MPQ4242 can automatically enter high-voltage, quick charge mode.

The MPQ4242 supports BC1.2 charging downstream port (CDP) handshaking as well. This can be enabled by setting CDP\_EN to 1b via the I<sup>2</sup>C.

If a USB PD contract is established after the sink is connected, the QC 3.0 and FCP functions are disabled.

#### **USB Type-C Port**

The USB Type-C receptacle, plug, and cable solution incorporates a configuration process to detect a downstream facing port (DFP) to upstream facing port (UFP) connection. This

detection function is used for  $V_{\text{BUS}}$  management and can determine the host-to-device connection.

Initially, a DFP-to-UFP connection is detected by a host (DFP) when one of the CC pins at its USB Type-C receptacle senses a specified resistance at GND. Subsequently, DFP-to-UFP disconnect is detected when the CC pin that was terminated at its USB Type-C receptacle is no longer connected to GND via a specified resistance.

Power is not applied to the USB Type-C host or hub receptacle (VBUS or VCONN) until the DFP detects the presence of a connected device (UFP) port. When a DFP-to-UFP connection is detected, the DFP is expected to enable power to the receptacle and proceed to normal USB operation with the connected device. When a DFP-to-UFP disconnect is detected, the port sourcing V<sub>BUS</sub> removes power.

The MPQ4242's power supply capability is rated for 5V @ 3A by default.  $V_{\text{CONN}}$  is provided by the DFP to power cables with electronics that are plugged in.  $V_{\text{CONN}}$  is provided power over the CC pin that is not connected to the cable's CC wire. The maximum output power of  $V_{\text{CONN}}$  is 1W.

VCONN is disabled until  $R_A$  is detected.  $R_A$  is a pull-down resistor connected from the CC pin to GND. It resistance must be below 1.2k $\Omega$ .

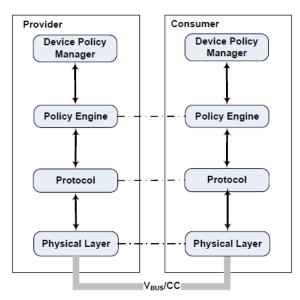

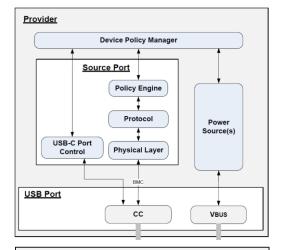

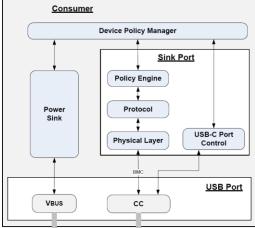

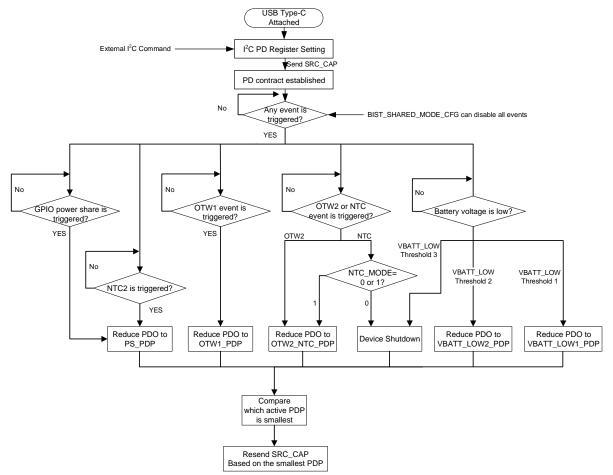

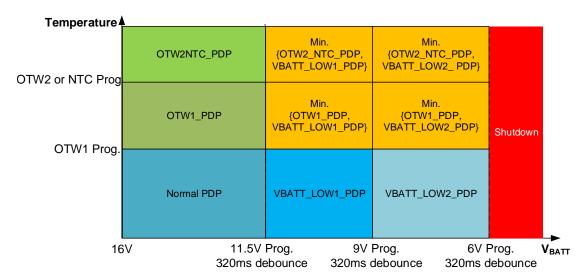

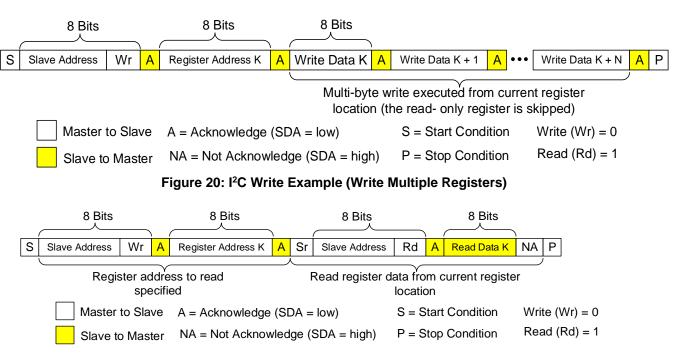

#### **USB Power Delivery (PD) 3.0**