## **General Description**

- Trench Power LV MOSFET technology

- High density cell design for low R<sub>DS(ON)</sub>

- High Speed switching

### **Applications**

- Battery protection

- Load switch

- Power management

| VDS                    | 30  | ٧  |

|------------------------|-----|----|

| RDS(on),Typ.@ VGS=10 V | 20  | mΩ |

| ID                     | 5.6 | Α  |

**Absolute Maximum Ratings** (T<sub>A</sub>=25 ℃ unless otherwise noted)

| Parameter                                           |                      | Symbol           | Limit            | Unit       |  |

|-----------------------------------------------------|----------------------|------------------|------------------|------------|--|

| Drain-source Voltage                                |                      | $V_{DS}$         | 30               | V          |  |

| Gate-source Voltage                                 |                      | $V_{GS}$         | ±12              | V          |  |

| Drain Current                                       | T <sub>A</sub> =25℃  | 1                | 5.6              | А          |  |

| Drain Current                                       | T <sub>A</sub> =70°C | - I <sub>D</sub> | 4.5              |            |  |

| Pulsed Drain Current <sup>A</sup>                   |                      | I <sub>DM</sub>  | 23               | А          |  |

| Total Power Dissipation                             | T <sub>A</sub> =25℃  | P₀               | 1.2              | W          |  |

| Total Fower Dissipation                             | T <sub>A</sub> =70℃  | FD               | 0.8              | W          |  |

| Thermal Resistance Junction-to-Ambient <sup>B</sup> |                      | R <sub>0JA</sub> | 104              | °C/W       |  |

| Junction and Storage Temperature Range              |                      | $T_J,T_STG$      | <b>-</b> 55∼+150 | $^{\circ}$ |  |

Electrical Characteristics (T<sub>J</sub>=25°C unless otherwise noted)

| Parameter                         | Symbol              | Conditions                                                     | Min  | Тур   | Max  | Units |

|-----------------------------------|---------------------|----------------------------------------------------------------|------|-------|------|-------|

| Static Parameter                  |                     |                                                                | '    | 1     |      |       |

| Drain-Source Breakdown Voltage    | BV <sub>DSS</sub>   | V <sub>GS</sub> =0V, I <sub>D</sub> =250μA                     | 30   |       |      | V     |

| Zero Gate Voltage Drain Current   | I <sub>DSS</sub>    | V <sub>DS</sub> =30V,V <sub>GS</sub> =0V                       |      |       | 1    | μA    |

| Gate-Body Leakage Current         | I <sub>GSS1</sub>   | $V_{GS}$ = $\pm$ 12 $V$ , $V_{DS}$ =0 $V$                      |      |       | ±100 | nA    |

| Gate Threshold Voltage            | V <sub>GS(th)</sub> | $V_{DS}$ = $V_{GS}$ , $I_D$ =250 $\mu$ A                       | 0.65 | 0.9   | 1.5  | ٧     |

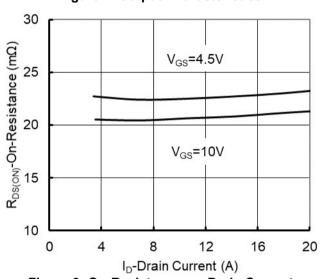

|                                   |                     | V <sub>GS</sub> =10V, I <sub>D</sub> =5.6A                     |      | 20    | 25   |       |

| Static Drain-Source On-Resistance | R <sub>DS(ON)</sub> | V <sub>GS</sub> =4.5V, I <sub>D</sub> =5A                      |      | 23    | 31   | mΩ    |

|                                   |                     | V <sub>GS</sub> =2.5V, I <sub>D</sub> =3A                      |      | 27    | 45   |       |

| Diode Forward Voltage             | V <sub>SD</sub>     | I <sub>S</sub> =5.6A,V <sub>GS</sub> =0V                       |      |       | 1.2  | V     |

| Dynamic Parameters                |                     |                                                                |      |       |      |       |

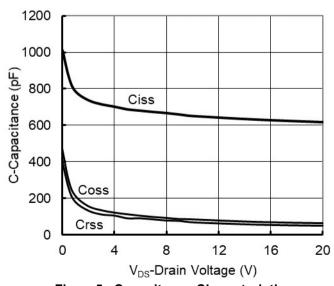

| Input Capacitance                 | C <sub>iss</sub>    |                                                                |      | 630   |      | pF    |

| Output Capacitance                | C <sub>oss</sub>    | $V_{DS}$ =15V, $V_{GS}$ =0V,f=1MHZ                             |      | 55    |      |       |

| Reverse Transfer Capacitance      | C <sub>rss</sub>    |                                                                |      | 71    |      |       |

| Switching Parameters              |                     |                                                                | 1    | 1     | 1    |       |

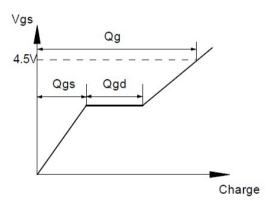

| Total Gate Charge                 | Q <sub>g</sub>      |                                                                |      | 17.25 |      |       |

| Gate-Source Charge                | Q <sub>gs</sub>     | V <sub>GS</sub> =10V,V <sub>DS</sub> =15V,I <sub>D</sub> =5.6A |      | 2.1   |      |       |

| Gate-Drain Charge                 | Q <sub>gd</sub>     |                                                                |      | 2     |      | - nC  |

| Reverse Recovery Chrage           | Q <sub>rr</sub>     | L 504 W/W 4004/                                                |      | 1.1   |      |       |

| Reverse Recovery Time             | t <sub>rr</sub>     | I <sub>F</sub> =5.6A, di/dt=100A/us                            |      | 13.1  |      |       |

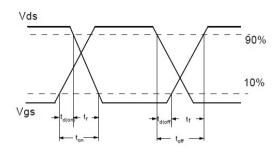

| Turn-on Delay Time                | t <sub>D(on)</sub>  |                                                                |      | 4.4   |      |       |

| Turn-on Rise Time                 | t <sub>r</sub>      | $V_{GS}$ =10V, $V_{DS}$ =15V, $I_{D}$ =5.6A                    |      | 28.2  |      | ns    |

| Turn-off Delay Time               | t <sub>D(off)</sub> | R <sub>GEN</sub> =3Ω                                           |      | 16.2  |      |       |

| Turn-off fall Time                | t <sub>f</sub>      |                                                                |      | 26    |      |       |

A. Pulse Test: Pulse Width  $\leqslant$  300us, Duty cycle  $\leqslant$  2%.

B.  $R_{\theta JA}$  is the sum of the junction-to-case and case-to-ambient thermal resistance, where the case thermal reference is defined as the solder mounting surface of the drain pins.  $R_{\theta JC}$  is guaranteed by design, while  $R_{\theta JA}$  is determined by the board design. The maximum rating presented here is based on mounting on a 1 in 2 pad of 2oz copper.

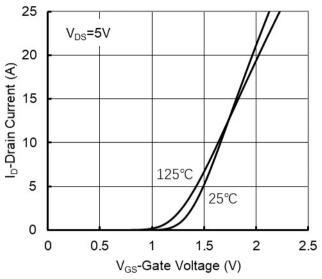

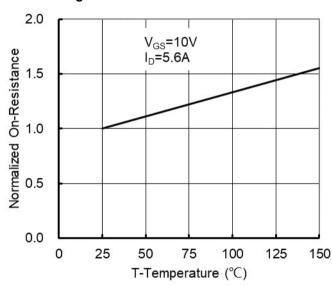

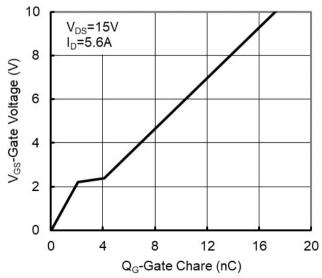

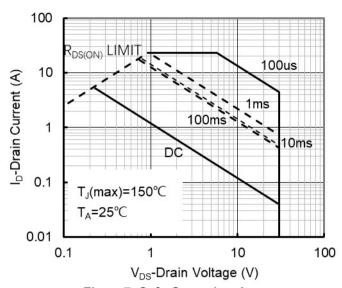

#### **Typical Performance Characteristics**

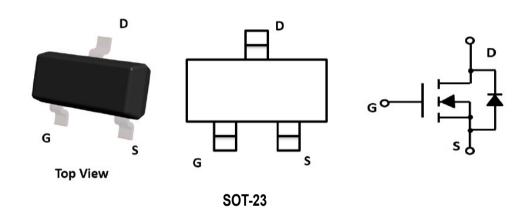

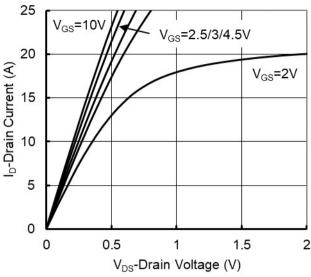

Figure 1. Output Characteristics

Figure 3: On-Resistance vs. Drain Current and Gate Voltage

Figure 5. Capacitance Characteristics

Figure 2. Transfer Characteristics

Figure 4: On-Resistance vs. Junction Temperature

Figure 6. Gate Charge

Figure 7. Safe Operation Area

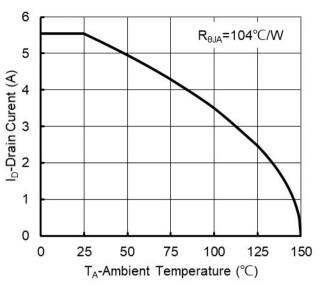

Figure8. Maximum Continuous Drain Current vs Ambient Temperature

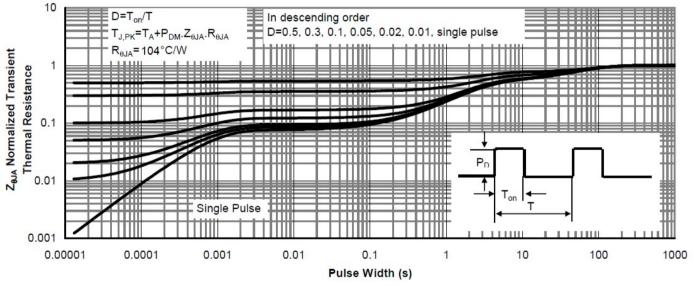

Figure 9. Normalized Maximum Transient Thermal Impedance

# **Test Circuit**

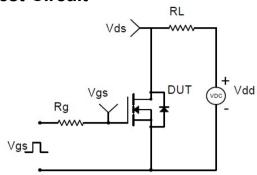

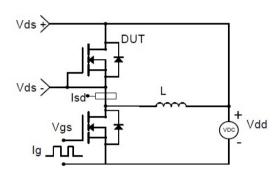

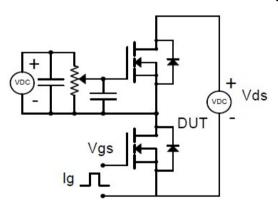

#### **Resistive Switching Test Circuit & Waveforms**

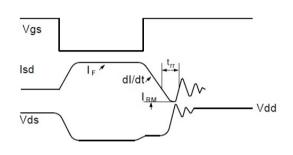

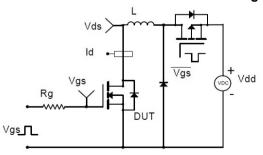

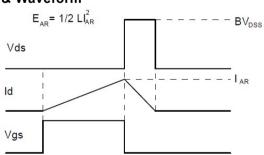

#### **Diode Recovery Test Circuit & Waveforms**

#### Gate Charge Test Circuit & Waveform

**Unclamped Inductive Switching (UIS) Test Circuit & Waveforms**

# **Ordering and Marking Information**

| Ordering Device No. | Marking | Package | Packing   | Quantity  |

|---------------------|---------|---------|-----------|-----------|

| ASDM3400ZA-R        | A09T    | SOT-23  | Tape&Reel | 3000/Reel |

| SOT-23 | PACKAGE | MARKING |

|--------|---------|---------|

|        |         | A09T    |

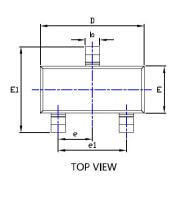

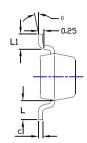

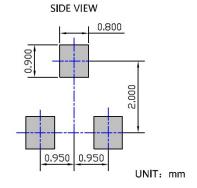

### **SOT-23 Package information**

AZ A

SIDE VIEW

SUGGESTED SOLDER PAD LAYOUT

|           | DIMENSIONS        |       |       |                 |       |       |

|-----------|-------------------|-------|-------|-----------------|-------|-------|

| SYMBOL    | INCHES            |       |       | Millimeter      |       |       |

| 2 I WRITE | MIN.              | NDM,  | MAX.  | MIN,            | NDM.  | MAX.  |

| Α         | 0.035             |       | 0,045 | 0,900           |       | 1,150 |

| A1        | 0,000             |       | 0,004 | 0,000           |       | 0,100 |

| A2        | 0,035             | 0.038 | 0.041 | 0.900 0,975 1.  |       |       |

| b         | 0,012             | 0.016 | 0.020 | 0.300 0.400 0.5 |       | 0.500 |

| u         | 0,004             | -     | 0.008 | 0.100 0.2       |       | 0.200 |

| D         | 0.110             | 0.114 | 0.118 | 2.800 2.900     |       | 3,000 |

| E         | 0.047             | 0,051 | 0,055 | 1.200 1.300     |       | 1,400 |

| E1        | 0,089             | 0,094 | 0.100 | 2,250 2,400 2,5 |       | 2,550 |

| е         | 0.037TYP          |       |       | 0.950TYP        |       |       |

| e1        | 0.071             | 0.075 | 0.079 | 1.800           | 1.900 | 2.000 |

| L         | 0.022REF 0.550REF |       |       | 10              |       |       |

| L1        | 0.012             | 0.016 | 0,200 | 0,300           | 0,400 | 0,500 |

| θ         | 0, 8, 0,          |       |       |                 | 8*    |       |

#### NOTE

- 1.PACKAGE BODY SIZES EXCLUDE MOLD FLASH AND GATE BURRS,

- 2.TOLERANCE 0.1mm UNLESS OTHERWISE SPECIFIED.

- 3.THE PAD LAYOUT IS FOR REFERENCE PURPOSES ONLY.

30V N-Channel MOSFET

#### **IMPORTANT NOTICE**

ShenZhen Ascend Semiconductor incorporated MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

ShenZhen Ascend Semiconductor Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. ShenZhen Ascend Semiconductor Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does ShenZhen Ascend Semiconductor Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume.

all risks of such use and will agree to hold Ascendsemi Incorporated and all the companies whose products are represented on ShenZhen Ascend Semiconductor Incorporated website, harmless against all damages.

ShenZhen Ascend Semiconductor Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use ShenZhen Ascend Semiconductor Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold ShenZhen Ascend Semiconductor Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

| www.asdsemi.cn |

|----------------|

|                |

|                |

|                |

|                |

|                |

|                |

|                |

|                |

|                |

|                |

|                |

|                |

|                |