# 1.0 Watt Audio Power Amplifier

The HT2890 is an audio power amplifier designed for portable communication device applications such as mobile phone applications. The HT2890 is capable of delivering 1.0 W of continuous average power to an 8.0  $\Omega$  BTL load from a 5.0 V power supply, and 320 mW to a 4.0  $\Omega$  BTL load from a 2.6 V power supply.

The HT2890 provides high quality audio while requiring few external components and minimal power consumption. It features a low–power consumption shutdown mode, which is achieved by driving the SHUTDOWN pin with logic low.

The HT2890 contains circuitry to prevent from "pop and click" noise that would otherwise occur during turn-on and turn-off transitions.

For maximum flexibility, the HT2890 provides an externally controlled gain (with resistors), as well as an externally controlled turn—on time (with the bypass capacitor).

Due to its excellent PSRR, it can be directly connected to the battery, saving the use of an LDO.

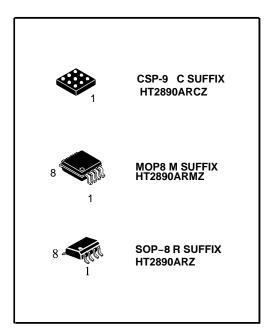

This device is available in a 9-Pin Flip-Chip CSP (standard Tin-Lead and Lead-Free versions) and a Micro8 <sup>™</sup> package.

# Features

- 1.0 W to an 8.0 Ω BTL Load from a 5.0 V Power Supply

- Excellent PSRR: Direct Connection to the Battery

- "Pop and Click" Noise Protection Circuit

- Ultra Low Current Shutdown Mode

- 2.2 V-5.5 V Operation

- External Gain Configuration Capability

- External Turn-on Time Configuration Capability

- Up to 1.0 nF Capacitive Load Driving Capability

- Thermal Overload Protection Circuitry

- AEC-Q100 Qualified Part Available

- Pb-Free Packages are Available

- NCV Prefix for Automotive and Other Applications Requiring Site and Control Changes

#### **Typical Applications**

- Portable Electronic Devices

- PDAs

- Wireless Phones

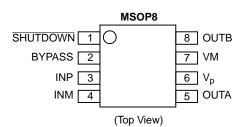

# PIN CONNECTIONS

CSP-9 Α1 A2 АЗ INM **OUTA** INP В1 B2 ВЗ VM\_P VM C1 C2 С3 **BYPASS OUTB SHUTDOWN**

(Top View)

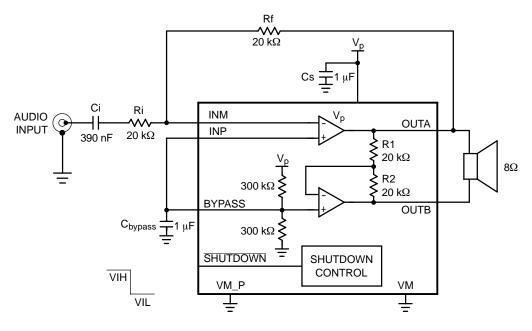

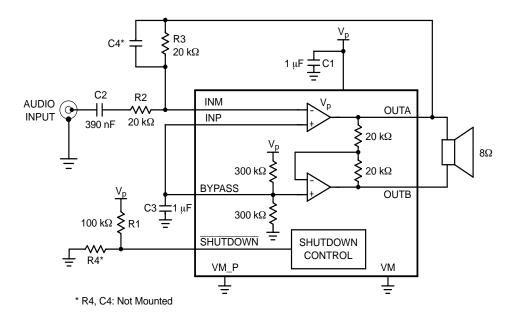

Figure 1. Typical Audio Amplifier Application Circuit with Single Ended Input

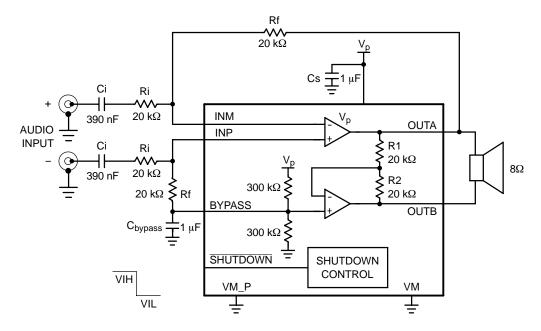

Figure 2. Typical Audio Amplifier Application Circuit with a Differential Input

This device contains 671 active transistors and 1899 MOS gates.

#### PIN DESCRIPTION

| 9-Pin Flip-Chip<br>CSP | Micro8 | Туре | Symbol         | Description                                                                                                                                         |  |

|------------------------|--------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A1                     | 4      | I    | INM            | Negative input of the first amplifier, receives the audio input signal. Connected to the feedback resistor $R_f$ and to the input resistor $R_in$ . |  |

| A2                     | 5      | 0    | OUTA           | Negative output of the HT2890. Connected to the load and to the feedback resistor Rf.                                                               |  |

| А3                     | 3      | I    | INP            | Positive input of the first amplifier, receives the common mode voltage.                                                                            |  |

| B1                     | NA     | I    | VM_P           | Power Analog Ground.                                                                                                                                |  |

| B2                     | 7      | I    | VM             | Core Analog Ground.                                                                                                                                 |  |

| В3                     | 6      | I    | V <sub>p</sub> | Positive analog supply of the cell. Range: 2.2 V-5.5 V.                                                                                             |  |

| C1                     | 2      | I    | BYPASS         | Bypass capacitor pin which provides the common mode voltage (Vp/2).                                                                                 |  |

| C2                     | 8      | 0    | OUTB           | Positive output of the HT2890. Connected to the load.                                                                                               |  |

| C3                     | 1      | I    | SHUTDOWN       | The device enters in shutdown mode when a low level is applied on this pin.                                                                         |  |

### MAXIMUM RATINGS (Note 1)

| Rating                                                                     | Symbol           | Value                                   | Unit |

|----------------------------------------------------------------------------|------------------|-----------------------------------------|------|

| Supply Voltage                                                             | V <sub>p</sub>   | 6.0                                     | V    |

| Operating Supply Voltage                                                   | Op Vp            | 2.2 to 5.5 V<br>2.0 V = Functional Only | -    |

| Input Voltage                                                              | V <sub>in</sub>  | -0.3 to Vcc +0.3                        | V    |

| Max Output Current                                                         | lout             | 500                                     | mA   |

| Power Dissipation (Note 2)                                                 | Pd               | Internally Limited                      | _    |

| Operating Ambient Temperature                                              | T <sub>A</sub>   | -40 to +85                              | °C   |

| Max Junction Temperature                                                   | TJ               | 150                                     | °C   |

| Storage Temperature Range                                                  | T <sub>stg</sub> | -65 to +150                             | °C   |

| Thermal Resistance Junction–to–Air Micro8 9–Pin Flip–Chip CSP              | $R_{	heta JA}$   | 230<br>(Note 3)                         | °C/W |

| ESD Protection Human Body Model (HBM) (Note 4) Machine Model (MM) (Note 5) | -                | 8000<br>>250                            | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- 1. Maximum electrical ratings are defined as those values beyond which damage to the device may occur at T<sub>A</sub> = +25°C.

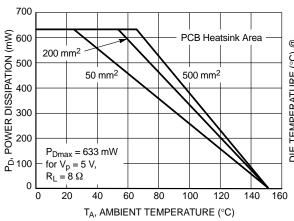

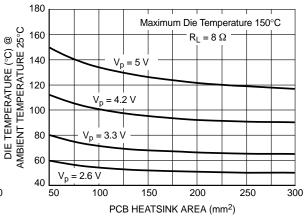

- 2. The thermal shutdown set to 160°C (typical) avoids irreversible damage on the device due to power dissipation. For further information see

- page 10.

3. For the 9–Pin Flip–Chip CSP package, the  $R_{\theta JA}$  is highly dependent of the PCB Heatsink area. For example,  $R_{\theta JA}$  can equal 195°C/W with a same thermal resistance and 50 mm<sup>2</sup> total area and also 135°C/W with 500 mm<sup>2</sup>. For further information see page 10. The bumps have the same thermal resistance and all need to be connected to optimize the power dissipation.

- 4. Human Body Model, 100 pF discharge through a 1.5 kΩ resistor following specification JESD22/A114.

- 5. Machine Model, 200 pF discharged through all pins following specification JESD22/A115.

## **ELECTRICAL CHARACTERISTICS** Limits apply for T<sub>A</sub> between -40°C to +85°C (Unless otherwise noted).

| Characteristic                        | Symbol                | Conditions                                                                                                           | Min<br>(Note 6) | Тур               | Max<br>(Note 6) | Unit |

|---------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|------|

| Supply Quiescent Current              | I <sub>dd</sub>       | $V_p = 2.6 \text{ V}$ , No Load $V_p = 5.0 \text{ V}$ , No Load                                                      | -<br>-          | 1.5<br>1.7        | 4               | mA   |

|                                       |                       | $V_p = 2.6 \text{ V}, 8 \Omega$<br>$V_p = 5.0 \text{ V}, 8 \Omega$                                                   |                 | 1.7<br>1.9        | 5.5             |      |

| Common Mode Voltage                   | V <sub>cm</sub>       | -                                                                                                                    | _               | V <sub>p</sub> /2 | _               | V    |

| Shutdown Current                      | I <sub>SD</sub>       | -                                                                                                                    | -               | 10                | 600             | nA   |

| Shutdown Voltage High                 | V <sub>SDIH</sub>     | _                                                                                                                    | 1.2             | _                 | -               | V    |

| Shutdown Voltage Low                  | V <sub>SDIL</sub>     | _                                                                                                                    | _               | _                 | 0.4             | V    |

| Turning On Time (Note 8)              | T <sub>WU</sub>       | C <sub>by</sub> = 1 μF                                                                                               | -               | 285               | -               | ms   |

| Output Swing                          | V <sub>loadpeak</sub> | $V_p = 2.6 \text{ V}, \ R_L = 8.0 \ \Omega$<br>$V_p = 5.0 \text{ V}, \ R_L = 8.0 \ \Omega \text{ (Note 7)}$          | 2.0<br>4.0      | 2.12<br>4.15      | -<br>-          | V    |

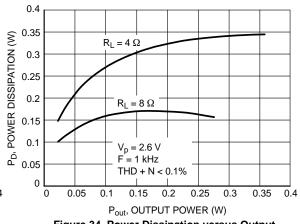

| Rms Output Power                      | Po                    | $V_p = 2.6 \text{ V}, \ R_L = 4.0 \ \Omega$                                                                          | _               | 0.36              | _               | W    |

|                                       |                       | THD + N < 0.1%<br>$V_p = 2.6 \text{ V}, R_L = 8.0 \Omega$<br>THD + N < 0.1%                                          | _               | 0.28              | _               |      |

|                                       |                       | $V_p = 5.0 \text{ V}, R_L = 8.0 \Omega$<br>THD + N < 0.1%                                                            |                 | 1.08              |                 |      |

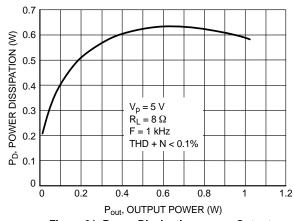

| Maximum Power Dissipation (Note 8)    | P <sub>Dmax</sub>     | $V_p = 5.0 \text{ V}, \ R_L = 8.0 \ \Omega$                                                                          | -               | -                 | 0.65            | W    |

| Output Offset Voltage                 | V <sub>OS</sub>       | $V_p = 2.6 \text{ V}$<br>$V_p = 5.0 \text{ V}$                                                                       | -30             |                   | 30              | mV   |

| Signal-to-Noise Ratio                 | SNR                   | V <sub>p</sub> = 2.6 V, G = 2.0<br>10 Hz < F < 20 kHz                                                                | -               | 84                | -               | dB   |

|                                       |                       | V <sub>p</sub> = 5.0 V, G = 10<br>10 Hz < F < 20 kHz                                                                 | -               | 77                | -               |      |

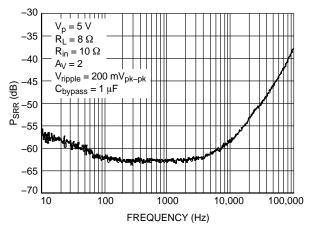

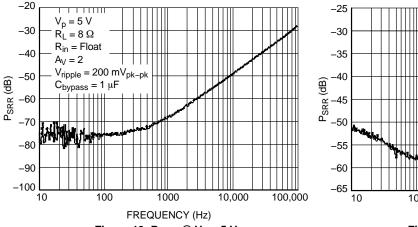

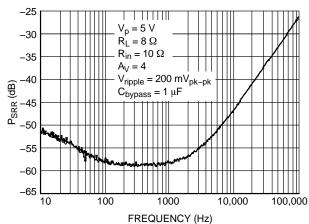

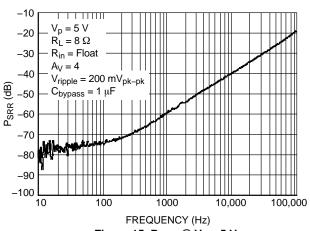

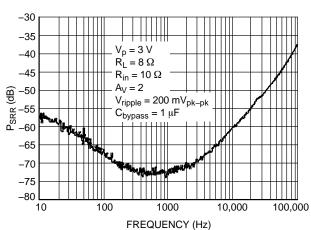

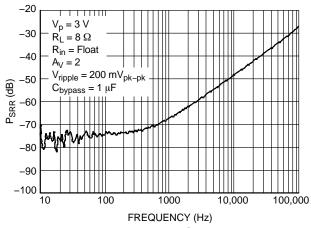

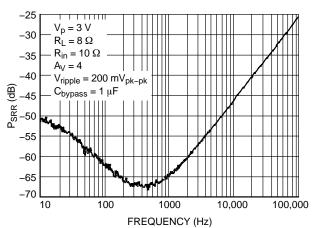

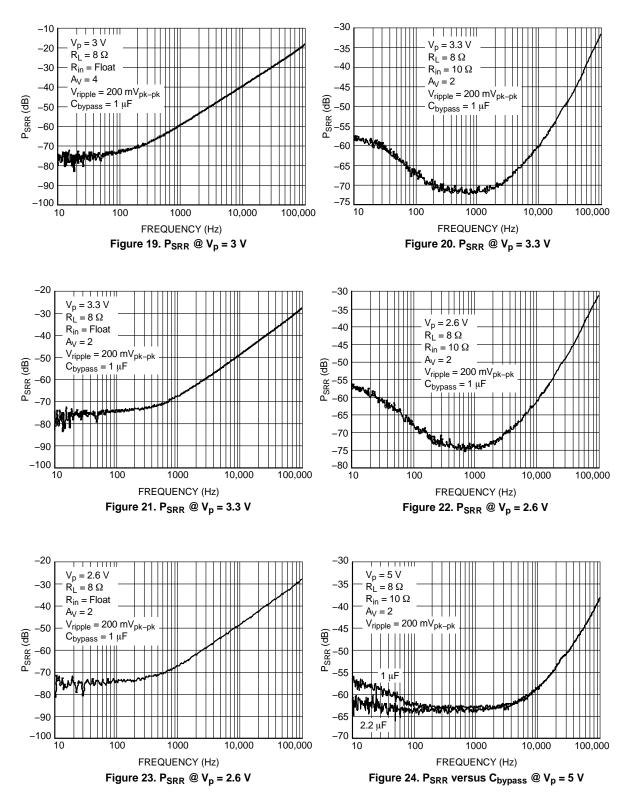

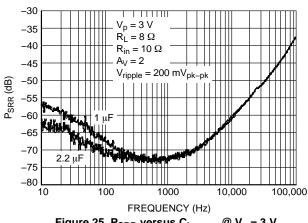

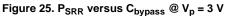

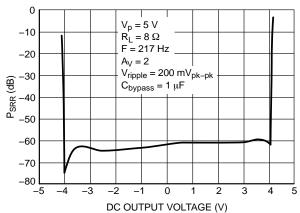

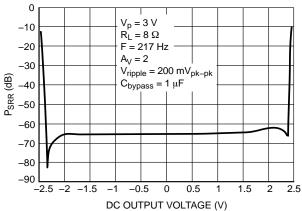

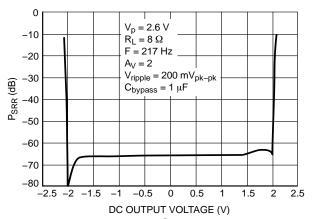

| Positive Supply Rejection Ratio       | PSRR V+               | $G = 2.0, R_L = 8.0 \Omega$ $Vp_{ripple\_pp} = 200 \text{ mV}$ $C_{by} = 1.0 \mu\text{F}$ Input Terminated with 10 Ω |                 |                   |                 | dB   |

|                                       |                       | $F = 217 \text{ Hz} \\ V_p = 5.0 \text{ V} \\ V_p = 3.0 \text{ V} \\ V_p = 2.6 \text{ V}$                            | -<br>-<br>-     | -64<br>-72<br>-73 | -<br>-<br>-     |      |

|                                       |                       | $F = 1.0 \text{ kHz} V_p = 5.0 \text{ V} V_p = 3.0 \text{ V} V_p = 2.6 \text{ V}$                                    | -<br>-<br>-     | -64<br>-74<br>-75 | -<br>-<br>-     |      |

| Efficiency                            |                       | $V_p = 2.6 \text{ V}, \ P_{orms} = 320 \text{ mW}$<br>$V_p = 5.0 \text{ V}, \ P_{orms} = 1.0 \text{ W}$              | _<br>_          | 48<br>63          | -<br>-          | %    |

| Thermal Shutdown Temperature (Note 9) | T <sub>sd</sub>       |                                                                                                                      | 140             | 160               | 180             | °C   |

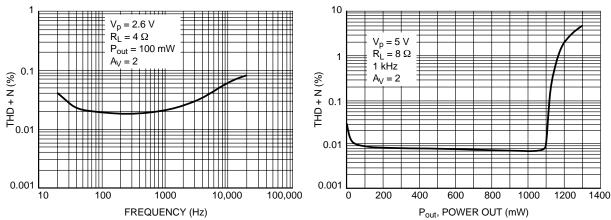

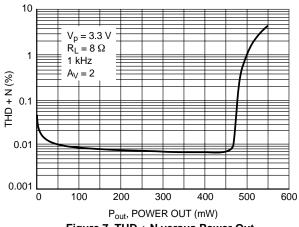

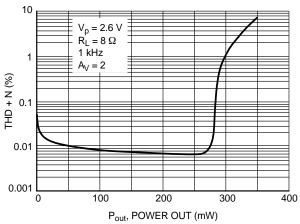

| Total Harmonic Distortion             | THD                   | $V_p = 2.6, F = 1.0 \text{ kHz}$<br>$R_L = 4.0 \Omega, A_V = 2.0$<br>$P_O = 0.32 \text{ W}$                          | -<br>-<br>-     | -<br>0.04<br>-    | -<br>-<br>-     | %    |

|                                       |                       | $V_p = 5.0 \text{ V}, F = 1.0 \text{ kHz}$ $R_L = 8.0 \Omega, A_V = 2.0$ $P_O = 1.0 \text{ W}$                       | -<br>-<br>-     | _<br>0.02<br>_    | -<br>-<br>-     |      |

<sup>6.</sup> Min/Max limits are guaranteed by design, test or statistical analysis.

7. This parameter is not tested in production for 9–Pin Flip–Chip CSP package in case of a 5.0 V power supply.

8. See page 11 for a theoretical approach of this parameter.

9. For this parameter, the Min/Max values are given for information.

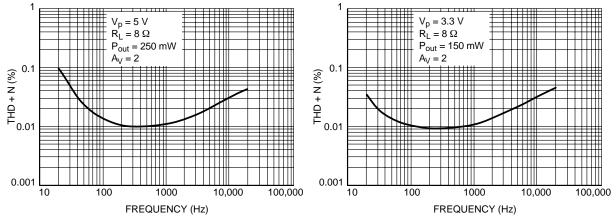

Figure 1. THD + N versus Frequency

Figure 2. THD + N versus Frequency

Figure 3. THD + N versus Frequency

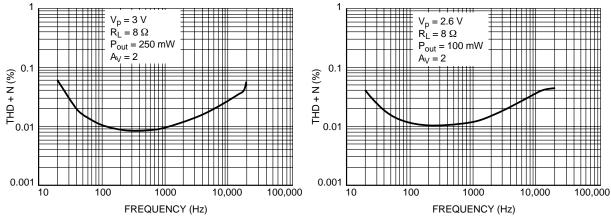

Figure 4. THD + N versus Frequency

Figure 5. THD + N versus Frequency

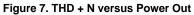

Figure 6. THD + N versus Power Out

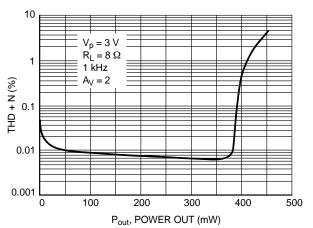

Figure 8. THD + N versus Power Out

Figure 9. THD + N versus Power Out

Figure 10. THD + N versus Power Out

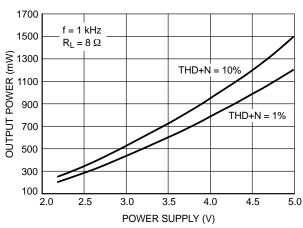

Figure 11. Output Power versus Power Supply

Figure 12.  $P_{SRR} @ V_p = 5 V$

Figure 14.  $P_{SRR} @ V_p = 5 V$

Figure 15.  $P_{SRR} @ V_p = 5 V$

Figure 16.  $P_{SRR} @ V_p = 3 V$

Figure 17.  $P_{SRR} @ V_p = 3 V$

Figure 18.  $P_{SRR} @ V_p = 3 V$

Figure 26.  $P_{SRR}$  @ DC Output Voltage

Figure 27. PSRR @ DC Output Voltage

Figure 28. P<sub>SRR</sub> @ DC Output Voltage

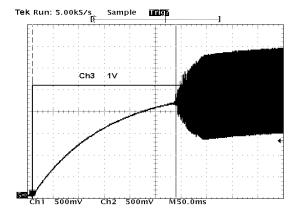

Figure 29. Turning On Time –  $V_p = 5 \text{ V}$

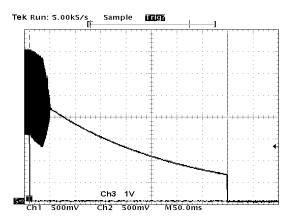

Figure 30. Turning Off Time –  $V_p = 5 \text{ V}$

Figure 31. Power Dissipation versus Output Power

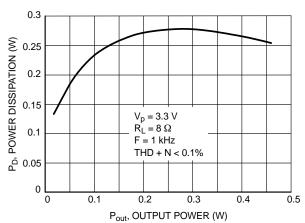

Figure 32. Power Dissipation versus Output Power

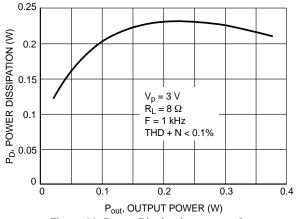

Figure 33. Power Dissipation versus Output Power

Figure 34. Power Dissipation versus Output Power

Figure 35. Power Derating - 9-Pin Flip-Chip CSP

Figure 36. Maximum Die Temperature versus PCB Heatsink Area

#### APPLICATION INFORMATION

#### **Detailed Description**

The HT2890 audio amplifier can operate under 2.6 V until 5.5 V power supply. It delivers 320 mW rms output power to 4.0  $\Omega$  load (V $_p$  = 2.6 V) and 1.0 W rms output power to 8.0  $\Omega$  load (V $_p$  = 5.0 V).

The structure of the HT2890 is basically composed of two identical internal power amplifiers; the first one is externally configurable with gain–setting resistors  $R_{in}$  and  $R_f$  (the closed–loop gain is fixed by the ratios of these resistors) and the second is internally fixed in an inverting unity–gain configuration by two resistors of 20  $k\Omega$ . So the load is driven differentially through OUTA and OUTB outputs. This configuration eliminates the need for an output coupling capacitor.

#### **Internal Power Amplifier**

The output PMOS and NMOS transistors of the amplifier were designed to deliver the output power of the specifications without clipping. The channel resistance  $(R_{on})$  of the NMOS and PMOS transistors does not exceed 0.6  $\Omega$  when they drive current.

The structure of the internal power amplifier is composed of three symmetrical gain stages, first and medium gain stages are transconductance gain stages to obtain maximum bandwidth and DC gain.

#### Turn-On and Turn-Off Transitions

A cycle with a turn-on and turn-off transition is illustrated with plots that show both single ended signals on the previous page.

In order to eliminate "pop and click" noises during transitions, output power in the load must be slowly established or cut. When logic high is applied to the shutdown pin, the bypass voltage begins to rise exponentially and once the output DC level is around the common mode voltage, the gain is established slowly (50 ms). This way to turn—on the device is optimized in terms of rejection of "pop and click" noises.

The device has the same behavior when it is turned—off by a logic low on the shutdown pin. During the shutdown mode, amplifier outputs are connected to the ground.

When a shutdown low level is applied, it takes 350 ms before the DC output level is tied to Ground. However, as shown on Figure 30, the turn off time of the audio signal is 40 ms.

A theoretical value of turn-on time at 25°C is given by the following formula.

C<sub>by</sub>: bypass capacitor

R: internal 300 k resistor with a 25% accuracy

$T_{on} = 0.95 * R * C_{by}$  (285 ms with  $C_{by} = 1 \mu F$ )

If a faster turn on time is required then a lower bypass capacitor can be used. The other option is to use NCP2892 which offers 100 ms with 1  $\mu$ F bypass capacitor.

#### **Shutdown Function**

The device enters shutdown mode when shutdown signal is low. During the shutdown mode, the DC quiescent current of the circuit does not exceed 100 nA.

#### **Current Limit Circuit**

The maximum output power of the circuit (Porms =  $1.0~W,~V_p$  =  $5.0~V,~R_L$  =  $8.0~\Omega$ ) requires a peak current in the load of 500 mA.

In order to limit the excessive power dissipation in the load when a short–circuit occurs, the current limit in the load is fixed to 800 mA. The current in the four output MOS transistors are real–time controlled, and when one current exceeds 800 mA, the gate voltage of the MOS transistor is clipped and no more current can be delivered.

#### **Thermal Overload Protection**

Internal amplifiers are switched off when the temperature exceeds 160°C, and will be switched on again only when the temperature decreases fewer than 140°C.

The HT2890 is unity-gain stable and requires no external components besides gain-setting resistors, an input coupling capacitor and a proper bypassing capacitor in the typical application.

The first amplifier is externally configurable ( $R_{\rm f}$  and  $R_{\rm in}$ ), while the second is fixed in an inverting unity gain configuration.

The differential-ended amplifier presents two major advantages:

- The possible output power is four times larger (the output swing is doubled) as compared to a single-ended amplifier under the same conditions.

- Output pins (OUTA and OUTB) are biased at the same potential V<sub>p</sub>/2, this eliminates the need for an output coupling capacitor required with a single-ended amplifier configuration.

The differential closed loop-gain of the amplifier is given by  $A_{Vd} = 2 * \frac{R_f}{R_{in}} = \frac{V_{orms}}{V_{inrms}}$ .

Output power delivered to the load is given by  $P_{orms} = \frac{(Vopeak)^2}{2*R_L}$  (Vopeak is the peak differential output voltage).

When choosing gain configuration to obtain the desired output power, check that the amplifier is not current limited or clipped.

The maximum current which can be delivered to the load is 500 mA  $I_{opeak} = \frac{V_{opeak}}{R_I}$ .

#### Gain-Setting Resistor Selection (Rin and Rf)

R<sub>in</sub> and R<sub>f</sub> set the closed-loop gain of the amplifier.

In order to optimize device and system performance, the HT2890 should be used in low gain configurations.

The low gain configuration minimizes THD + noise values and maximizes the signal to noise ratio, and the amplifier can still be used without running into the bandwidth limitations.

A closed loop gain in the range from 2 to 5 is recommended to optimize overall system performance.

An input resistor ( $R_{in}$ ) value of 22 k $\Omega$  is realistic in most of applications, and doesn't require the use of a too large capacitor  $C_{in}$ .

#### Input Capacitor Selection (Cin)

The input coupling capacitor blocks the DC voltage at the amplifier input terminal. This capacitor creates a high–pass filter with  $R_{\rm in}$ , the cut–off frequency is given by

$$fc = \frac{1}{2 * \Pi * R}$$

.

The size of the capacitor must be large enough to couple in low frequencies without severe attenuation. However a large input coupling capacitor requires more time to reach its quiescent DC voltage  $(V_p/2)$  and can increase the turn–on pops.

An input capacitor value between 0.1  $\mu$  and 0.39  $\mu F$  performs well in many applications (With  $R_{in}=22~K\Omega$ ).

#### **Bypass Capacitor Selection (Cby)**

The bypass capacitor Cby provides half-supply filtering and determines how fast the HT2890 turns on.

This capacitor is a critical component to minimize the turn—on pop. A 1.0  $\mu F$  bypass capacitor value ( $C_{in}$  =  $<0.39~\mu F)$  should produce clickless and popless shutdown transitions. The amplifier is still functional with a 0.1  $\mu F$  capacitor value but is more susceptible to "pop and click" noises.

Thus, a 1.0 μF bypassing capacitor is recommended.

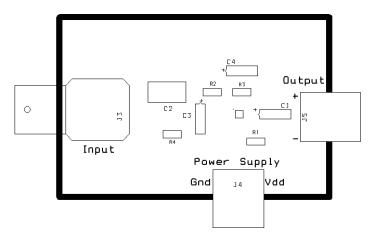

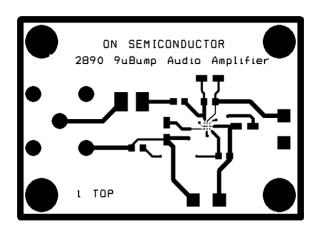

Figure 37. Schematic of the Demonstration Board of the 9-Pin Flip-Chip CSP Device

Silkscreen Layer

Top Layer

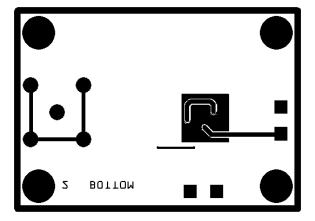

**Bottom Layer**

Figure 38. Demonstration Board for 9-Pin Flip-Chip CSP Device - PCB Layers

# **BILL OF MATERIAL**

| Item | Part Description                                                        | Ref.   | PCB<br>Footprint | Manufacturer     | Manufacturer<br>Reference |

|------|-------------------------------------------------------------------------|--------|------------------|------------------|---------------------------|

| 1    | HT2890 Audio Amplifier                                                  | -      | -                | ON Semiconductor | HT2890                    |

| 2    | SMD Resistor 100 KΩ                                                     | R1     | 0805             | Vishay-Draloric  | D12CRCW Series            |

| 3    | SMD Resistor 20 KΩ                                                      | R2, R3 | 0805             | Vishay-Draloric  | CRCW0805 Series           |

| 4    | Ceramic Capacitor 1.0 μF 16 V X7R                                       | C1     | 1206             | Murata           | GRM42-6X7R105K16          |

| 5    | Ceramic Capacitor 390 nF 50 V Z5U                                       | C2     | 1812             | Kemet            | C1812C394M5UAC            |

| 6    | Ceramic Capacitor 1.0 μF 16 V X7R                                       | C3     | 1206             | Murata           | GRM42-6X7R105K16          |

| 7    | Not Mounted                                                             | R4, C4 | -                | -                | -                         |

| 8    | BNC Connector                                                           | J3     | -                | Telegartner      | JO1001A1948               |

| 9    | I/O Connector. It can be plugged by BLZ5.08/2<br>(Weidmüller Reference) | J4, J5 | -                | Weidmüller       | SL5.08/2/90B              |

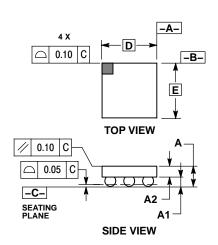

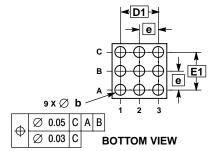

#### **PACKAGE DIMENSIONS**

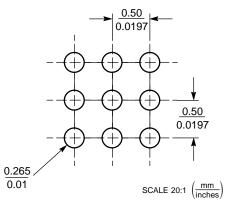

#### 9 PIN FLIP-CHIP CASE 499E-01 **ISSUE A**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. COPLANARITY APPLIES TO SPHERICAL CROWNS OF SOLDER BALLS.

|     | MILLIMETERS |       |  |  |  |  |

|-----|-------------|-------|--|--|--|--|

| DIM | MIN MA      |       |  |  |  |  |

| Α   | 0.540       | 0.660 |  |  |  |  |

| A1  | 0.210       | 0.270 |  |  |  |  |

| A2  | 0.330       | 0.390 |  |  |  |  |

| D   | 1.450 BSC   |       |  |  |  |  |

| E   | 1.450 BSC   |       |  |  |  |  |

| b   | 0.290       | 0.340 |  |  |  |  |

| е   | 0.500 BSC   |       |  |  |  |  |

| D1  | 1.000 BSC   |       |  |  |  |  |

| E1  | 1.000 BSC   |       |  |  |  |  |

#### **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

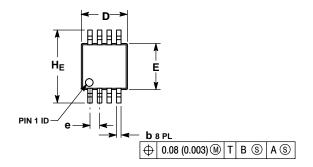

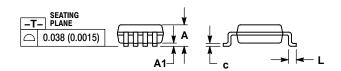

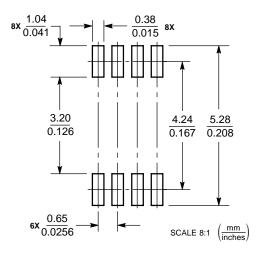

#### **PACKAGE DIMENSIONS**

#### Micro8™ CASE 846A-02 **ISSUE G**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

4. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.

5. 846A-01 OBSOLETE, NEW STANDARD 846A-02.

MILLIMETERS

INCHES

|     | М        | ILLIMETE | RS   | INCHES    |       |       |  |

|-----|----------|----------|------|-----------|-------|-------|--|

| DIM | MIN      | NOM      | MAX  | MIN       | MOM   | MAX   |  |

| Α   |          |          | 1.10 |           | -     | 0.043 |  |

| A1  | 0.05     | 0.08     | 0.15 | 0.002     | 0.003 | 0.006 |  |

| b   | 0.25     | 0.33     | 0.40 | 0.010     | 0.013 | 0.016 |  |

| С   | 0.13     | 0.18     | 0.23 | 0.005     | 0.007 | 0.009 |  |

| D   | 2.90     | 3.00     | 3.10 | 0.114     | 0.118 | 0.122 |  |

| E   | 2.90     | 3.00     | 3.10 | 0.114     | 0.118 | 0.122 |  |

| е   | 0.65 BSC |          |      | 0.026 BSC |       |       |  |

| L   | 0.40     | 0.55     | 0.70 | 0.016     | 0.021 | 0.028 |  |

| HE  | 4.75     | 4.90     | 5.05 | 0.187     | 0.193 | 0.199 |  |

## **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.