#### LOW-POWER CAN TRANSCEIVER WITH BUS WAKE-UP

#### (compatible to SN65HVD1040)

The HT651040 meets or exceeds the specifications of the ISO 11898 standard for use in applications employing a Controller Area Network (CAN). As CAN transceivers, these devices provide differential transmit and receive capability for a CAN controller at signaling rates of up to 1 megabit per second (Mbps). (1)

Designed for operation in especially harsh environments, the device features  $\pm 12$  kV ESD protection on the bus and split pins, cross-wire, overvoltage and loss of ground protection from -27 to 40 V, overtemperature shutdown, a -12 V to 12 V common-mode range, and will withstand voltage transients from -200 V to 200 V according to ISO 7637.

#### **FEATURES**

- Improved Drop-in Replacement for the TJA1040

- ±12 kV ESD Protection

- Low-Current Standby Mode with Bus Wake-up: 5 μA Typical

- Bus-Fault Protection of –27 V to 40 V

- Rugged Split-Pin Bus Stability

- Dominant Time-Out Function

- Power-Up/Down Glitch-Free Bus Inputs and Outputs

- High Input Impedance with Low V<sub>CC</sub>

- Monotonic Outputs During Power Cycling

- DeviceNet Vendor ID # 806

#### **APPLICATIONS**

- Battery Operated Applications

- Hand-Held Diagnostics

- Medical Scanning and Imaging

- HVAC

- Security Systems

- Telecom Base Station Status and Control

- SAE J1939 Standard Data Bus Interface

- NMEA 2000 Standard Data Bus Interface

- ISO 11783 Standard Data Bus Interface

- Industrial Automation

- DeviceNet<sup>™</sup> Data Buses

#### **ORDERINGINFORMATION**

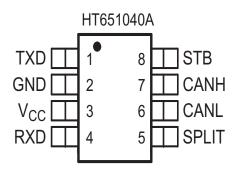

SOP8 R SUFFIX HT651040ARZ

MSOP8 M SUFFIX HT651040ARMZ

DFN8(3\*3) D SUFFIX HT651040ARDZ

$T_A = -40^{\circ}$  to 125°C for all packages.

(1) The signaling rate of a line is the number of voltage transitions that are made per second expressed in the units bps (bits per second).

#### **DESCRIPTION (Continued)**

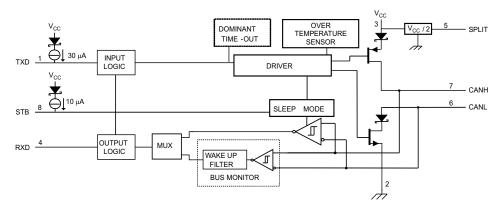

The STB input (pin 8) selects between two different modes of operation; high-speed or low-power mode. The high-speed mode of operation is selected by connecting STB to ground.

If a high logic level is applied to the STB pin of the HT651040, the device enters a low-power bus-monitor standby mode. While the HT651040 is in the low-power bus-monitor standby mode, a dominant bit greater than 5  $\mu$ s on the bus is passed by the bus-monitor circuit to the receiver output. The local protocol controller may then reactivate the device when it needs to transmit to the bus.

A dominant-time-out circuit in the HT651040 prevents the driver from blocking network communication during a hardware or software failure. The time-out circuit is triggered by a falling edge on TXD (pin 1). If no rising edge is seen before the time-out constant of the circuit expires, the driver is disabled. The circuit is then reset by the next rising edge on TXD.

The SPLIT output (pin 5) is available on the HT651040 as a  $V_{CC}/2$  common-mode bus voltage bias for a split-termination network. The HT651040 is characterized for operation from  $-40^{\circ}$ C to  $125^{\circ}$ C.

#### ABSOLUTE MAXIMUM RATINGS(1)

|                     |                                |                                     | VALUE           |

|---------------------|--------------------------------|-------------------------------------|-----------------|

| $V_{CC}$            | Supply voltage <sup>(2)</sup>  |                                     | -0.3 V to 7 V   |

| V <sub>I(bus)</sub> | Voltage range at any bus term  | inal (CANH, CANL, SPLIT)            | –27 V to 40 V   |

| I <sub>O(OUT)</sub> | Receiver output current        |                                     | -20 mA to 20 mA |

|                     | Voltage input, transient pulse | <sup>3)</sup> , (CANH, CANL, SPLIT) | –200 V to 200 V |

|                     | Human Body Model               | Bus terminals and GND               | ±12 kV          |

| ESD                 | Human body model (4)           | All pins                            | ±4 kV           |

| ESD                 | Charged-device-model (5)       | All pins                            | ±1 kV           |

|                     | Machine model                  |                                     | ±200 V          |

| VI                  | Voltage input range (TXD, STI  | 3)                                  | –0.5 V to 6 V   |

| $T_J$               | Junction temperature           |                                     | −55°C to 170°C  |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

|                                   |                                         |                 | MIN                | NOM MAX | UNIT |

|-----------------------------------|-----------------------------------------|-----------------|--------------------|---------|------|

| V <sub>CC</sub>                   | Supply voltage                          | Supply voltage  |                    | 5.25    | V    |

| $V_{\text{I}}$ or $V_{\text{IC}}$ | Voltage at any bus terminal (separately | or common mode) | -12 <sup>(1)</sup> | 12      | V    |

| V <sub>IH</sub>                   | High-level input voltage                | TVD CTD         | 2                  | 5.25    | V    |

| V <sub>IL</sub>                   | Low-level input voltage                 | TXD, STB        | 0                  | 0.8     | V    |

| $V_{ID}$                          | Differential input voltage              |                 | -6                 | 6       | V    |

|                                   | High lavel autout august                | Driver          | -70                |         | A    |

| OH                                | High-level output current               | Receiver        | -2                 |         | - mA |

|                                   | Law lawal autout aumant                 | Driver          |                    | 70      |      |

| IOL                               | Low-level output current                | Receiver        |                    | 2       | - mA |

| t <sub>SS</sub>                   | Maximum pulse width to remain in stand  | dby             |                    | 0.7     | μs   |

| TJ                                | Junction temperature                    |                 | -40                | 150     | С    |

<sup>(1)</sup> The algebraic convention, in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

#### **SUPPLY CURRRENT**

over operating free-air temperature range (unless otherwise noted)

| PARAMETER       |                                 | TEST CONDITIONS | MIN                                                     | TYP | MAX | UNIT |    |

|-----------------|---------------------------------|-----------------|---------------------------------------------------------|-----|-----|------|----|

|                 |                                 | Dominant        | $V_I = 0 \text{ V}, 60 \Omega \text{ Load, STB at 0 V}$ |     | 50  | 70   | Л  |

| I <sub>CC</sub> | Supply current, V <sub>CC</sub> | Recessive       | V <sub>I</sub> = V <sub>CC</sub> , STB at 0 V           |     | 6   | 10   | mA |

|                 |                                 | Standby         | STB at VCC, VI = VCC                                    |     | 5   | 12   | μΑ |

#### **DEVICE SWITCHING CHARACTERISTICS**

over recommended operating conditiions (unless otherwise noted)

|                    | PARAMETER                                                                | TEST<br>CONDITIONS | MIN | TYP MAX | UNIT |

|--------------------|--------------------------------------------------------------------------|--------------------|-----|---------|------|

| t <sub>loop1</sub> | Total loop delay, driver input to receiver output, Recessive to Dominant | STB at 0 V,        | 90  | 230     |      |

| t <sub>loop2</sub> | Total loop delay, driver input to receiver output, Dominant to Recessive | See Figure 9       | 90  | 230     | ns   |

<sup>(2)</sup> All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

<sup>(3)</sup> Tested in accordance with ISO 7637, test pulses 1, 2, 3a, 3b, 5, 6 & 7.

<sup>(4)</sup> Tested in accordance JEDEC Standard 22, Test Method A114-A.

(5) Tested in accordance JEDEC Standard 22, Test Method C101.

#### **DRIVER ELECTRICAL CHARACTERISTICS**

over recommended operating conditiions (unless otherwise noted)

|                     | PARAMETER                                                                           |         | TEST CONDITIONS                                                                            | MIN                 | TYP <sup>(1)</sup> | MAX                 | UNIT     |  |

|---------------------|-------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------|---------------------|--------------------|---------------------|----------|--|

| V <sub>O(D)</sub>   | Bus output voltage                                                                  | CANH    | $V_I$ = 0 V, STB at 0 V, $R_L$ = 60 $\Omega$ , See Figure 1 and                            | 2.9                 | 3.4                | 4.5                 | V        |  |

| (Dominant)          |                                                                                     | CANL    | Figure 2                                                                                   | 0.8                 |                    | 1.75                | V        |  |

| $V_{O(R)}$          | Bus output voltage (Recessive                                                       | )       | V <sub>I</sub> = 3 V, STB at 0 V, See Figure 1 and Figure 2                                | 2                   | 2.5                | 3                   | V        |  |

| Vo                  | Bus output voltage (Standby)                                                        |         | $R_L = 60 \Omega$ , STB at $V_{CC}$ , See Figure 1 and Figure 2                            | -0.1                |                    | 0.1                 | V        |  |

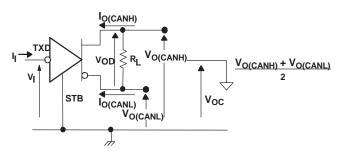

| V                   | Differential output valtere (Der                                                    | minant) | $V_{I}$ = 0 V, $R_{L}$ = 60 $\Omega$ , STB at 0 V, See Figure 1 and Figure 2, and Figure 3 | 1.5                 |                    | 3                   | <b>V</b> |  |

| $V_{OD(D)}$         | Differential output voltage (Dor                                                    | ninani) | $V_{I}$ = 0 V, $R_{L}$ = 45 $\Omega$ , STB at 0 V, See Figure 1 and Figure 2               | 1.4                 |                    | 3                   | V        |  |

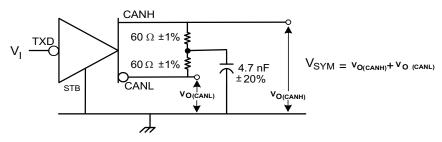

| V <sub>SYM</sub>    | Output symmetry (Dominant or Recessive) [ V <sub>O(CANH)</sub> + V <sub>O(CAI</sub> |         | STB at 0 V, See Figure 2 and Figure 13                                                     | 0.9×V <sub>CC</sub> | V <sub>CC</sub>    | 1.1×V <sub>CC</sub> | V        |  |

| V <sub>OD(R)</sub>  | DD(R) Differential output voltage (Recessive)                                       |         | $V_{I}$ = 3 V, $R_{L}$ = 60 $\Omega$ , STB at 0 V, See Figure 1 and Figure 2               | -0.012              |                    | 0.012               | ٧        |  |

| 05(.1)              |                                                                                     |         | V <sub>I</sub> = 3 V, STB at 0 V, No Load                                                  | -0.5                |                    | 0.05                |          |  |

| V <sub>OC(D)</sub>  | Common-mode output voltage (Dominant)                                               |         | STR at 0 V See Figure 9                                                                    | 2                   | 2.3                | 3                   | V        |  |

| V <sub>OC(pp)</sub> | Peak-to-peak common-mode c                                                          | utput   | STB at 0 V, See Figure 8                                                                   |                     | 0.3                |                     | V        |  |

| I <sub>IH</sub>     | High-level input current, TXD in                                                    | nput    | V <sub>I</sub> at V <sub>CC</sub>                                                          | -2                  |                    | 2                   | μΑ       |  |

| I <sub>IL</sub>     | Low-level input current, TXD in                                                     | put     | V <sub>I</sub> at 0 V                                                                      | -50                 |                    | -10                 | μΑ       |  |

| I <sub>O(off)</sub> | Power-off TXD Leakage currer                                                        | nt      | V <sub>CC</sub> at 0 V, TXD at 5 V                                                         |                     |                    | 1                   | μΑ       |  |

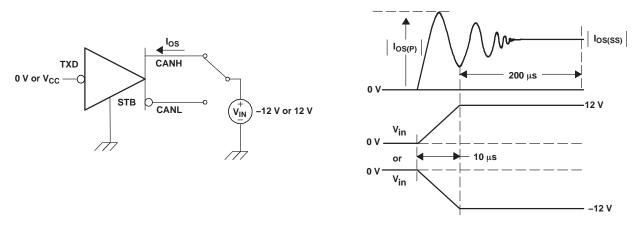

|                     |                                                                                     |         | V <sub>CANH</sub> = -12 V, CANL Open, See Figure 12                                        | -120                | -72                |                     |          |  |

|                     | Short-circuit steady-state output                                                   | ıt      | V <sub>CANH</sub> = 12 V, CANL Open, See Figure 12                                         |                     | 0.36               | 1                   | 1        |  |

| I <sub>OS(ss)</sub> | <sup>OS(ss)</sup> current                                                           |         | V <sub>CANL</sub> = -12 V, CANH Open, See Figure 12                                        | -1                  | -0.5               | 5 m <i>l</i>        |          |  |

|                     |                                                                                     |         | V <sub>CANL</sub> = 12 V, CANH Open, See Figure 12                                         |                     | 71                 | 120                 |          |  |

| Co                  | Output capacitance                                                                  |         | See Input capacitance to ground in RECEIVER ELECTRICAL CHARACTERISTICS.                    |                     |                    |                     |          |  |

<sup>(1)</sup> All typical values are at 25 C with a 5-V supply.

#### **DRIVER SWITCHING CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                    | PARAMETER                                           | TEST CONDITIONS          | MIN | TYP | MAX | UNIT |

|--------------------|-----------------------------------------------------|--------------------------|-----|-----|-----|------|

| t <sub>PLH</sub>   | Propagation delay time, low-to-high-level output    |                          | 25  | 65  | 120 |      |

| t <sub>PHL</sub>   | Propagation delay time, high-to-low-level output    |                          | 25  | 45  | 120 |      |

| t <sub>sk(p)</sub> | Pulse skew ( t <sub>PHL</sub> - t <sub>PLH</sub>  ) | STB at 0 V, See Figure 4 |     |     | 25  | ns   |

| t <sub>r</sub>     | Differential output signal rise time                |                          |     | 25  |     |      |

| t <sub>f</sub>     | Differential output signal fall time                |                          |     | 50  |     |      |

| t <sub>en</sub>    | Enable time from silent mode to dominant            | See Figure 7             |     |     | 10  | μs   |

| t <sub>dom</sub>   | Dominant time-out                                   | See Figure 10            | 300 | 450 | 700 | μs   |

#### RECEIVER ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                                                                |                    | TEST CONDITIONS                                        | MIN | TYP <sup>(1)</sup> | MAX  | UNIT |

|---------------------|------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------|-----|--------------------|------|------|

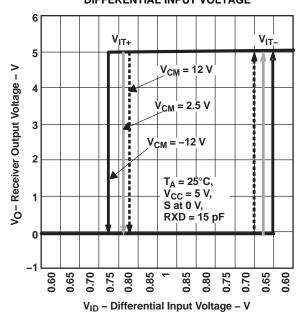

| V <sub>IT+</sub>    | Positive-going input threshold voltage                                                   |                    | CTD at 0 \/ See Table 4                                |     | 800                | 900  |      |

| V <sub>IT-</sub>    | Negative-going input threshold voltage                                                   | High-speed<br>mode | STB at 0 V, See Table 1                                | 500 | 650                |      | mV   |

| $V_{hys}$           | Hysteresis voltage (V <sub>IT+</sub> - V <sub>IT-</sub> )                                |                    | STB at V <sub>CC</sub>                                 | 100 | 125                |      |      |

| $V_{IT}$            | Input threshold voltage                                                                  | Standby mode       | STB at V <sub>CC</sub>                                 | 500 |                    | 1150 |      |

| V <sub>OH</sub>     | High-level output voltage                                                                |                    | I <sub>O</sub> = -2 mA, See Figure 6                   | 4   | 4.6                |      | V    |

| $V_{OL}$            | Low-level output voltage                                                                 |                    | I <sub>O</sub> = 2 mA, See Figure 6                    |     | 0.2                | 0.4  | V    |

| I <sub>I(off)</sub> | Power-off bus input current                                                              |                    | CANH or CANL = 5 V, V <sub>CC</sub> at 0 V, TXD at 0 V |     |                    | 5    | μΑ   |

| I <sub>O(off)</sub> | Power-off RXD leakage current                                                            |                    | V <sub>CC</sub> at 0 V, RXD at 5 V                     |     |                    | 20   | μΑ   |

| Cı                  | Input capacitance to ground, (CAN                                                        | NH or CANL)        | TXD at 3 V, V <sub>I</sub> = 0.4 sin (4E6πt) + 2.5 V   |     | 20                 |      | рF   |

| C <sub>ID</sub>     | Differential input capacitance                                                           |                    | TXD at 3 V, V <sub>I</sub> = 0.4 sin (4E6πt)           |     | 10                 |      | pF   |

| R <sub>ID</sub>     | Differential input resistance                                                            |                    | TXD at 3 V, STD at 0 V                                 | 30  |                    | 80   | 1.0  |

| R <sub>IN</sub>     | Input resistance, (CANH or CANL)                                                         |                    | TXD at 3 V, STD at 0 V                                 | 15  | 30                 | 40   | kΩ   |

| R <sub>I(m)</sub>   | Input resistance matching [1 – (R <sub>IN (CANH)</sub> / R <sub>IN (CANL)</sub> )] x 100 | %                  | V <sub>CANH</sub> = V <sub>CANL</sub>                  | -3% | 0%                 | 3%   |      |

<sup>(1)</sup> All typical values are at 25 C with a 5-V supply.

#### RECEIVER SWITCHING CHARACTERISTICS

over recommended operating conditiions (unless otherwise noted)

|                  | PARAMETER                                                             | TEST CONDITIONS                  | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------------------------------------------------|----------------------------------|-----|-----|-----|------|

| t <sub>pLH</sub> | Propagation delay time, low-to-high-level output                      |                                  | 60  | 100 | 130 |      |

| t <sub>pHL</sub> | Propagation delay time, high-to-low-level output                      | STB at 0 V, TXD at 3 V, See      | 45  | 70  | 130 | no   |

| t <sub>r</sub>   | Output signal rise time                                               | Figure 6                         |     | 8   |     | ns   |

| t <sub>f</sub>   | Output signal fall time                                               |                                  |     | 8   |     |      |

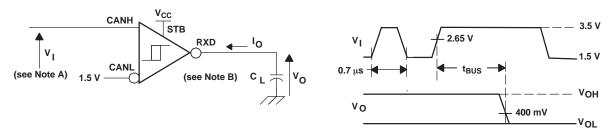

| t <sub>BUS</sub> | Dominant time required on bus for wake-up from standby <sup>(1)</sup> | STB at V <sub>CC</sub> Figure 11 | 0.7 |     | 5   | μs   |

<sup>(1)</sup> The device under test shall not signal a wake-up condition with dominant pulses shorter than t<sub>BUS</sub> (min) and shall signal a wake-up condition with dominant pulses longer than t<sub>BUS</sub> (max). Dominant pulses with a length between t<sub>BUS</sub> (min) and t<sub>BUS</sub> (max) may lead to a wake-up.

#### **SPLIT-PIN CHARACTERISTICS**

over recommended operating conditiions (unless otherwise noted)

|                     | PARAMETER                    | TEST CONDITIONS                           | MIN                 | TYP                 | MAX                 | UNIT |

|---------------------|------------------------------|-------------------------------------------|---------------------|---------------------|---------------------|------|

| Vo                  | Output voltage               | –500 μA < I <sub>O</sub> < 500 μA         | 0.3×V <sub>CC</sub> | $0.5 \times V_{CC}$ | $0.7 \times V_{CC}$ | V    |

| I <sub>O(stb)</sub> | Standby mode leakage current | STB at 2 V, −12 V ≤ V <sub>O</sub> ≤ 12 V | <b>-</b> 5          |                     | 5                   | μΑ   |

#### **STB-PIN CHARACTERISTICS**

over recommended operating conditiions (unless otherwise noted)

|                 | PARAMETER                | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------|--------------------------|-----------------|-----|-----|-----|------|

| I <sub>IH</sub> | High level input current | STB at 2 V      | -10 |     | 0   | μΑ   |

| $I_{IL}$        | Low level input current  | STB at 0 V      | -10 |     | 0   | μΑ   |

#### PARAMETER MEASUREMENT INFORMATION

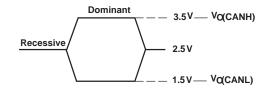

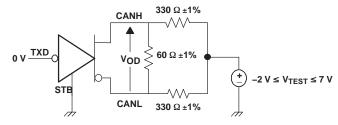

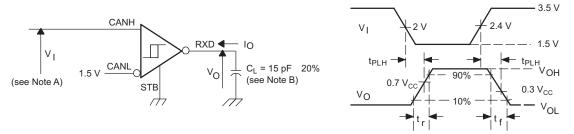

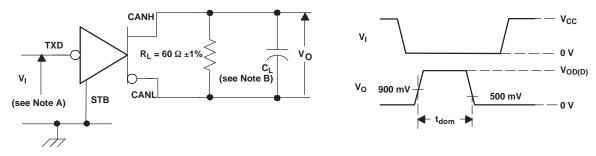

Figure 1. Driver Voltage, Current, and Test Definition

Figure 2. Bus Logic State Voltage Definitions

Figure 3. Driver  $V_{\text{OD}}$  Test Circuit

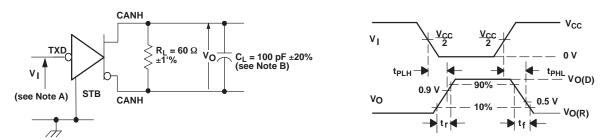

Figure 4. Driver Test Circuit and Voltage Waveforms

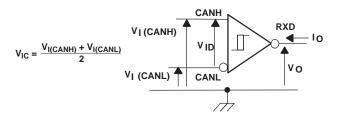

Figure 5. Receiver Voltage and Current Definitions

#### PARAMETER MEASUREMENT INFORMATION (continued)

- A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  125 kHz, 50% duty cycle,  $t_r \leq$  6 ns,  $t_f \leq$  6ns,  $Z_O = 50 \Omega$ .

- B. C<sub>L</sub> includes instrumentation and fixture capacitance within 20%.

Figure 6. Receiver Test Circuit and Voltage Waveforms

|                   | •                                   | J      |   |                 |  |  |

|-------------------|-------------------------------------|--------|---|-----------------|--|--|

|                   | INPUT                               |        |   |                 |  |  |

| V <sub>CANH</sub> | V <sub>CANH</sub> V <sub>CANL</sub> |        | ı | ₹               |  |  |

| –11.1 V           | –12 V                               | 900 mV | L | V <sub>OL</sub> |  |  |

| 12 V              | 11.1 V                              | 900 mV | L |                 |  |  |

| −6 V              | –12 V                               | 6 V    | L |                 |  |  |

| 12 V              | 6 V                                 | 6 V    | L |                 |  |  |

| –11.5 V           | –12 V                               | 500 mV | Н | V <sub>OH</sub> |  |  |

| 12 V              | 11.5 V                              | 500 mV | Н |                 |  |  |

| –12 V             | -6 V                                | 6 V    | Н |                 |  |  |

| 6 V               | 12 V                                | 6 V    | Н |                 |  |  |

| Open              | Open                                | Х      | Н |                 |  |  |

**Table 1. Differential Input Voltage Threshold Test**

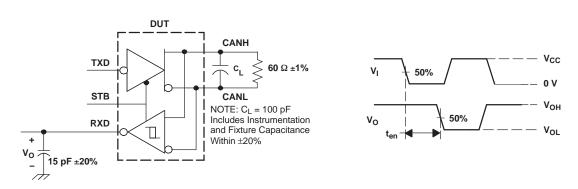

Figure 7. t<sub>en</sub> Test Circuit and Voltage Waveforms

A. All  $V_I$  input pulses are from 0 V to  $V_{CC}$  and supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 6$  ns. Pulse Repetition Rate (PRR) = 125 kHz, 50% duty cycle.

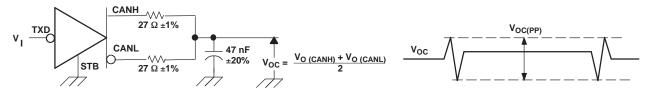

Figure 8. Peak-to-Peak Common Mode Output Voltage Test and Waveform

A. All  $V_1$  input pulses are from 0 V to  $V_{CC}$  and supplied by a generator with the following characteristics:  $t_f$  or  $t_f \le 6$  ns. Pulse Repetition Rate (PRR) = 125 kHz, 50% duty cycle.

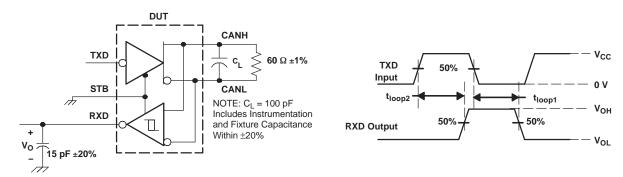

Figure 9. t<sub>loop</sub> Test Circuit and Voltage Waveforms

- A. All  $V_1$  input pulses are from 0 V to  $V_{CC}$  and supplied by a generator with the following characteristics:  $t_r$  or  $t_f \le 6$  ns. Pulse Repetition Rate (PRR) = 500 Hz, 50% duty cycle.

- B.  $C_L = 100 \text{ pF}$  includes instrumentation and fixture capacitance within 20%.

Figure 10. Dominant Time-Out Test Circuit and Waveform

- A. For  $V_I$  bit width  $\leq 0.7~\mu s$ ,  $V_O = V_{OH}$ . For  $V_II$  bit width  $\geq 5~\mu s$ ,  $V_O = V_{OL}$ .  $V_I$  input pulses are supplied from a generator with the following characteristics;  $t_f$  or  $t_f \leq 6$  ns. Pulse Repetition Rate (PRR) = 50 Hz, 30% duty cycle.

- B.  $C_L = 15 \text{ pF}$  includes instrumentation and fixture capacitance within 20%.

Figure 11. t<sub>BUS</sub> Test Circuit and Waveform

Figure 12. Driver Short-Circuit Current Test and Waveform

Figure 13. Driver Output Symmetry Test Circuit

#### **DEVICE INFORMATION**

Table 2. DRIVER FUNCTION TABLE(1)

| INP  | INPUTS    |      | PUTS | BUS STATE |

|------|-----------|------|------|-----------|

| TXD  | STB       | CANH | CANL |           |

| L    | L         | Н    | L    | DOMINANT  |

| Н    | L         | Z    | Z    | RECESSIVE |

| Open | Х         | Z    | Z    | RECESSIVE |

| Х    | H or Open | Z    | Z    | RECESSIVE |

(1) H = high level; L = low level; X = irrelevant; Z = high impedance

Table 3. RECEIVER FUNCTION TABLE<sup>(1)</sup>

| DIFFERENTIAL INPUTS V <sub>ID</sub> = CANH - CANL | STB       | OUTPUT<br>RXD | BUS STATE |

|---------------------------------------------------|-----------|---------------|-----------|

| $V_{ID} \ge 0.9 V$                                | L         | L             | DOMINANT  |

| V <sub>ID</sub> ≥ 1.15 V                          | H or Open | L             | DOMINANT  |

| 0.5 V < V <sub>ID</sub> < 0.9 V                   | X         | ?             | ?         |

| V <sub>ID</sub> ≤ 0.5 V                           | Х         | Н             | RECESSIVE |

| Open                                              | X         | Н             | RECESSIVE |

(1) H = high level; L = low level; X = irrelevant; ? = indeterminate; Z = high impedance

#### THERMAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|                                                                       | PARAMETER                                           | TEST CONDITIONS                                                                  | MIN | TYP | MAX | UNIT  |

|-----------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|-----|-----|-----|-------|

| O Thomas Basistana America ta                                         | Thermal Desistance Junction to Air                  | Low-K Thermal Resistance <sup>(1)</sup>                                          |     | 211 |     | °C/W  |

| θ <sub>JA</sub>                                                       | θ <sub>JA</sub> Thermal Resistance, Junction-to-Air | High-K Thermal Resistance                                                        |     | 131 |     | °C/W  |

| $\theta_{JB}$                                                         | Thermal Resistance,<br>Junction-to-Board            |                                                                                  |     | 53  |     | °C/W  |

| $\theta_{JC}$                                                         | Thermal Resistance,<br>Junction-to-Case             |                                                                                  |     | 79  |     | *C/VV |

| P <sub>D</sub>                                                        | Device Power Dissipation                            | $R_L$ = 60 $\Omega$ , S at 0 V, Input to TXD a 500kHz 50% duty-cycle square wave |     | 112 | 170 | mW    |

| T <sub>JS</sub> Junction Temperature, Thermal Shutdown <sup>(2)</sup> |                                                     |                                                                                  | 190 |     | °C  |       |

<sup>(1)</sup> Tested in accordance with the Low-K or High-K thermal metric definitions of EIA/JESD51-3 for leaded surface mount packages.

<sup>(2)</sup> Extended operation in thermal shutdown may affect device reliability, see the Application Information section.

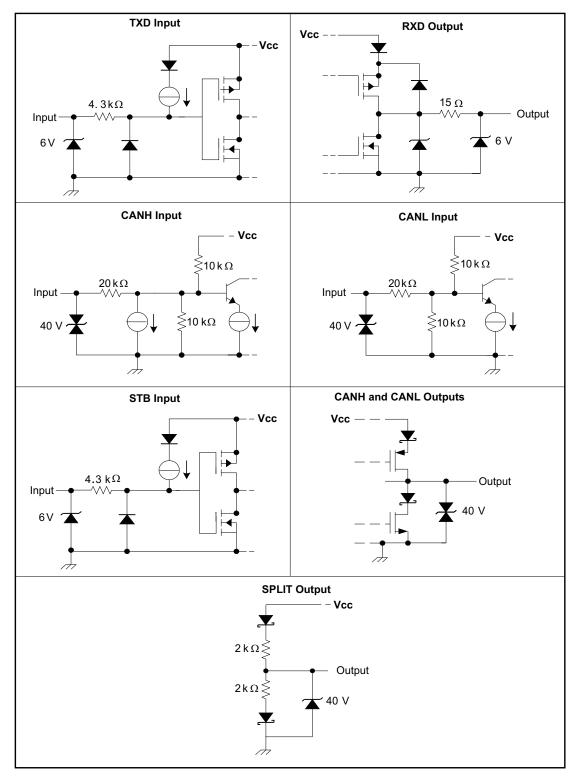

#### **Equivalent Input and Output Schematic Diagrams**

#### TYPICAL CHARACTERISTICS

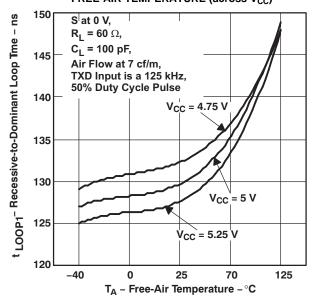

# RECESSIVE-TO-DOMINANT LOOP TIME VS FREE-AIR TEMPERATURE (across V<sub>CC</sub>)

Figure 14.

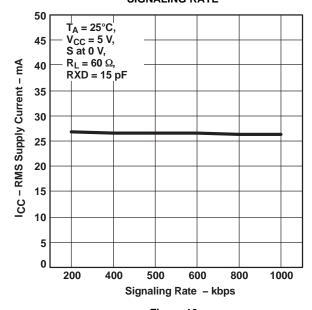

# SUPPLY CURRENT (RMS) vs SIGNALING RATE

Figure 16.

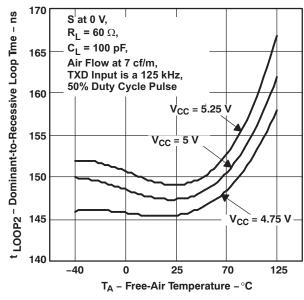

# DOMINANT-TO-RECESSIVE LOOP TIME VS FREE-AIR TEMPERATURE (across V<sub>CC</sub>)

Figure 15.

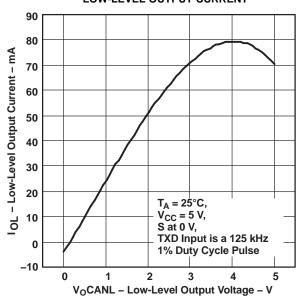

## DRIVER LOW-LEVEL OUTPUT VOLTAGE vs LOW-LEVEL OUTPUT CURRENT

Figure 17.

#### **TYPICAL CHARACTERISTICS (continued)**

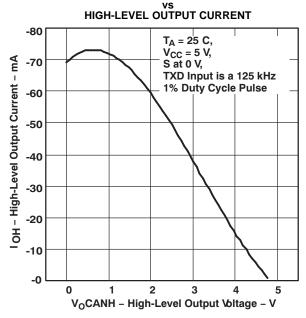

## DRIVER HIGH-LEVEL OUTPUT VOLTAGE vs

Figure 18.

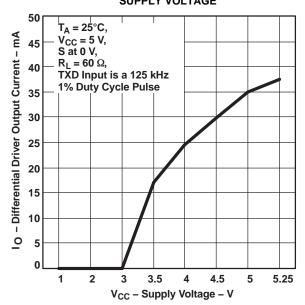

# DRIVER OUTPUT CURRENT vs SUPPLY VOLTAGE

Figure 20.

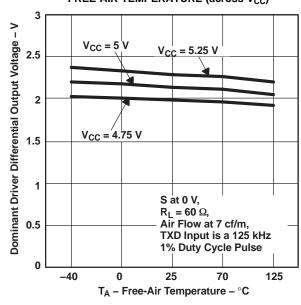

# DRIVER DIFFERENTIAL OUTPUT VOLTAGE vs FREE-AIR TEMPERATURE (across V<sub>CC</sub>)

Figure 19.

## RECEIVER OUTPUT VOLTAGE VS DIFFERENTIAL INPUT VOLTAGE

Figure 21.

#### **TYPICAL CHARACTERISTICS (continued)**

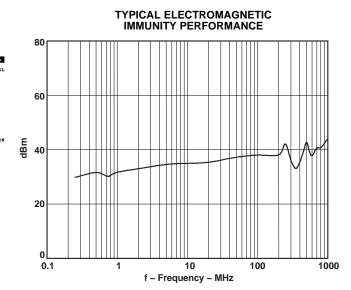

# TYPICAL ELECTROMAGNETIC EMISSIONS UP TO 50 MHZ (Peak Amplitude) 80 70 50 50 FRM Start 20 kHz 4.998 MHz/ Stop 50 MHz

Figure 22. Frequency Spectrum of Common-Mode Emissions

Figure 23. Direct Power Injection (DPI) Response vs Frequency

#### **APPLICATION INFORMATION**

#### **CAN Basics**

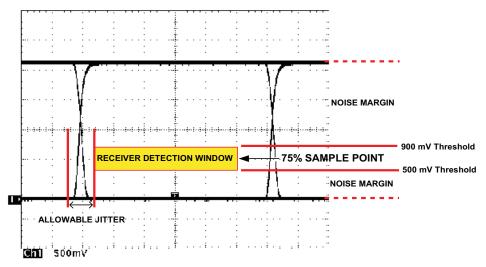

The basics of arbitration require that the receiver at the sending node designate the first bit as dominant or recessive after the initial wave of the first bit of a message travels to the most remote node on a network and back again. Typically, this "sample" is made at 75% of the bit width, and within this limitation, the maximum allowable signal distortion in a CAN network is determined by network electrical parameters.

Factors to be considered in network design include the approximately 5 ns/m propagation delay of typical twisted-pair bus cable; signal amplitude loss due to the loss mechanisms of the cable; and the number, length, and spacing of drop-lines (stubs) on a network. Under strict analysis, variations among the different oscillators in a system also need to be accounted for with adjustments in signaling rate and stub and bus length. Table 5 lists the maximum signaling rates achieved with the HT651040 with several bus lengths of category 5, shielded twisted pair (CAT 5 STP) cable.

Table 5. Maximum Signaling Rates for Various Cable Lengths

| Bus Length (m) | Signaling Rate (kbps) |  |

|----------------|-----------------------|--|

| 30             | 1000                  |  |

| 100            | 500                   |  |

| 250            | 250                   |  |

| 500            | 125                   |  |

| 1000           | 62.5                  |  |

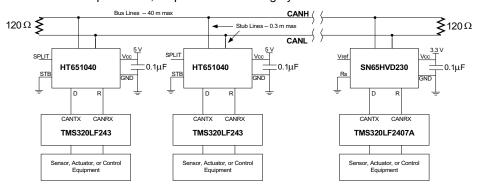

The ISO 11898 Standard specifies a maximum bus length of 40 m and maximum stub length of 0.3 m with a maximum of 30 nodes. However, with careful design, users can have longer cables, longer stub lengths, and many more nodes to a bus. (Note: Non-standard application may come with a trade-off in signaling rate.) A large number of nodes requires a transceiver with high input impedance such as the HT651040.

The Standard specifies the interconnect to be a single twisted-pair cable (shielded or unshielded) with 120  $\Omega$  characteristic impedance ( $Z_0$ ). Resistors equal to the characteristic impedance of the line terminate both ends of the cable to prevent signal reflections. Unterminated drop-lines connect nodes to the bus and should be kept as short as possible to minimize signal reflections.

Connectors, while not specified by the standard should have as little effect as possible on standard operating parameters such as capacitive loading. Although unshielded cable is used in many applications, data transmission circuits employing CAN transceivers are usually used in applications requiring a rugged interconnection with a wide common-mode voltage range. Therefore, shielded cable is recommended in these electronically harsh environments, and when coupled with the Standard's –2-V to 7-V common-mode range of tolerable ground noise, helps to ensure data integrity. The HT651040 enhances the Standard's insurance of data integrity with an extended –12 V to 12 V range of common-mode operation.

Figure 24. Typical CAN Differential Signal Eye-Pattern

An eye pattern is a useful tool for measuring overall signal quality. As displayed in Figure 25, the differential signal changes logic states in two places on the display, producing an "eye." Instead of viewing only one logic crossing on the scope, an entire "bit" of data is brought into view. The resulting eye pattern includes all of the effects of systemic and random distortion, and displays the time during which a signal may be considered valid.

The height of the eye above or below the receiver threshold voltage level at the sampling point is the noise margin of the system. Jitter is typically measured at the differential voltage zero-crossing during the logic state transition of a signal. Note that jitter present at the receiver threshold voltage level is considered by some to be a more effective representation of the jitter at the input of a receiver.

As the sum of skew and noise increases, the eye closes and data is corrupted. Closing the width decreases the time available for accurate sampling, and lowering the height enters the 900 mV or 500 mV threshold of a receiver.

Different sources induce noise onto a signal. The more obvious noise sources are the components of a transmission circuit themselves; the signal transmitter, traces and cables, connectors, and the receiver. Beyond that, there is a termination dependency, cross-talk from clock traces and other proximity effects,  $V_{CC}$  and ground bounce, and electromagnetic interference from near-by electrical equipment.

The balanced receiver inputs of the HT651040 mitigate most all sources of signal corruption, and when used with a quality shielded twisted-pair cable, help insure data integrity.

Figure 25. Typical HT651040 Application

#### Thermal Shutdown

The HT651040 has a thermal shutdown that turns off the driver outputs when the junction temperature nears 190°C. This shutdown prevents catastrophic failure from bus shorts, but does not protect the circuit from possible damage. The user should strive to maintain recommended operating conditions, and not exceed absolute maximum ratings at all times. If the HT651040 is subjected to many or long durations faults that can put the device into thermal shutdown, it should be replaced.

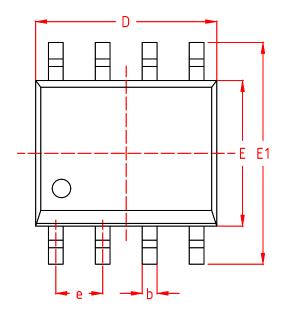

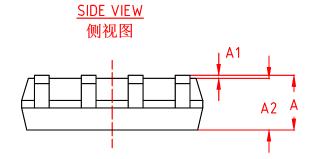

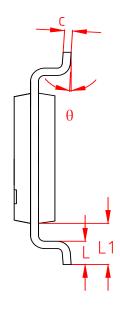

## **SOP8** package information

TOP VIEW 正视图

SIDE VIEW 侧视图

| 机械尺寸/mm      |            |                |            |  |  |

|--------------|------------|----------------|------------|--|--|

|              | Dimensions |                |            |  |  |

| 字符<br>SYMBOL | 最小值<br>MIN | 典型值<br>NOMINAL | 最大值<br>MAX |  |  |

| Α            | -          | ı              | 1.75       |  |  |

| A1           | 0.10       | 0.15           | 0.25       |  |  |

| A2           | 1.30       | 1.40           | 1.50       |  |  |

| b            | 0.35       | ı              | 0.50       |  |  |

| С            | 0.19       | _              | 0.25       |  |  |

| D            | 4.80       | 4.90           | 5.00       |  |  |

| E            | 3.80       | 3.90           | 4.00       |  |  |

| E1           | 5.80       | 6.00           | 6.20       |  |  |

| e            | 1.27 BSC   |                |            |  |  |

| h            | 0.25       |                | 0.45       |  |  |

| L            | 0.50       | -              | 0.80       |  |  |

| θ            | 0°         |                | 8°         |  |  |

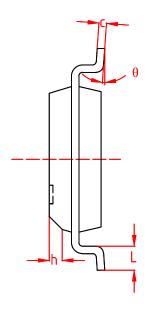

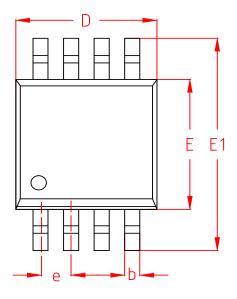

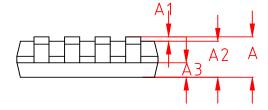

## **MSOP8** package information

SIDE VIEW 侧视图

## SIDE VIEW 侧视图

|        | 机械尺寸/mm  |               |      |  |  |

|--------|----------|---------------|------|--|--|

|        | Dimer    | <u>nsions</u> |      |  |  |

| 字符     | 最小值      | 典型值           | 最大值  |  |  |

| SYMBOL | MIN      | NOMINAL       | MAX  |  |  |

| Α      | -        | -             | 1.10 |  |  |

| A1     | 0.05     | ı             | 0.15 |  |  |

| A2     | 0.75     | 0.85          | 0.95 |  |  |

| A3     | 0.30     | 0.35          | 0.40 |  |  |

| b      | 0.28     | _             | 0.36 |  |  |

| С      | 0.15     | _             | 0.19 |  |  |

| D      | 2.90     | 3.00          | 3.10 |  |  |

| E      | 2.90     | 3.00          | 3.10 |  |  |

| E1     | 4.70     | 4.90          | 5.10 |  |  |

| е      | 0.65 BSC |               |      |  |  |

| L1     | 0.95 REF |               |      |  |  |

| L      | 0.40     | _             | 0.70 |  |  |

| θ      | 0°       | -             | 8°   |  |  |

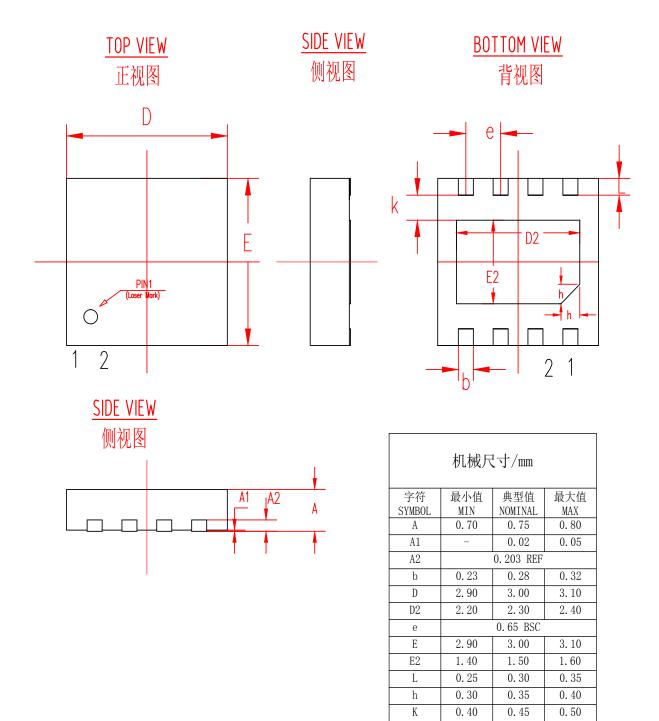

## DFN8L(3X3X0.75-P0.65) package information