数字信号处理器及其解决方案提供商

# FDM320RV335 数据手册

版本V1.0

青岛本原微电子有限公司

| 版本号  | 修改日期       | 修改人     | 修改内容                |

|------|------------|---------|---------------------|

| 0.1  | 2023/9/26  | 邢园园, 徐琛 | 初版                  |

| 0.11 | 2023/12/12 | 邢园园, 徐琛 | 引脚图, springcore 子系统 |

| 0.2  | 2023/12/20 | 徐琛      | 增加寄存器详细描述           |

| 1.0  | 2024/1/4   | 徐琛      | 增加 DMA 寄存器并更正错误     |

|      |            |         |                     |

## 目 录

|                                                     |    |

|-----------------------------------------------------|----|

| 1. 产品特色 .....                                       | 4  |

| 2. 功能结构图 .....                                      | 6  |

| 3. 引脚说明 .....                                       | 7  |

| 4. 设备详细描述 .....                                     | 15 |

| 4.1. FDM320RV335 处理器核 .....                         | 15 |

| 4.1.1. 指令集 .....                                    | 16 |

| 4.1.2. 地址映射 .....                                   | 17 |

| 4.2. 系统控制 .....                                     | 17 |

| 4.2.1. 振荡器和锁相环模块 .....                              | 19 |

| 4.2.2. 看门狗模块 .....                                  | 20 |

| 4.3. 中断 .....                                       | 24 |

| 4.4. 外设 .....                                       | 32 |

| 4.4.1. DMA .....                                    | 33 |

| 4.4.2. 定时器 .....                                    | 34 |

| 4.4.3. 增强型 PWM 模块 .....                             | 36 |

| 4.4.4. 高分辨率 PWM(HRPWM) .....                        | 40 |

| 4.4.5. 增强型 CAP 模块 .....                             | 41 |

| 4.4.6. 增强型 QEP 模块 .....                             | 42 |

| 4.4.7. 模数转换器(ADC 模块) .....                          | 44 |

| 4.4.8. 多通道缓冲串行端口 (MCBSP) 模块 .....                   | 47 |

| 4.4.9. 增强型控制器局域网 (ECAN) 模块(ECAN-A 和 ECAN-B) .....   | 50 |

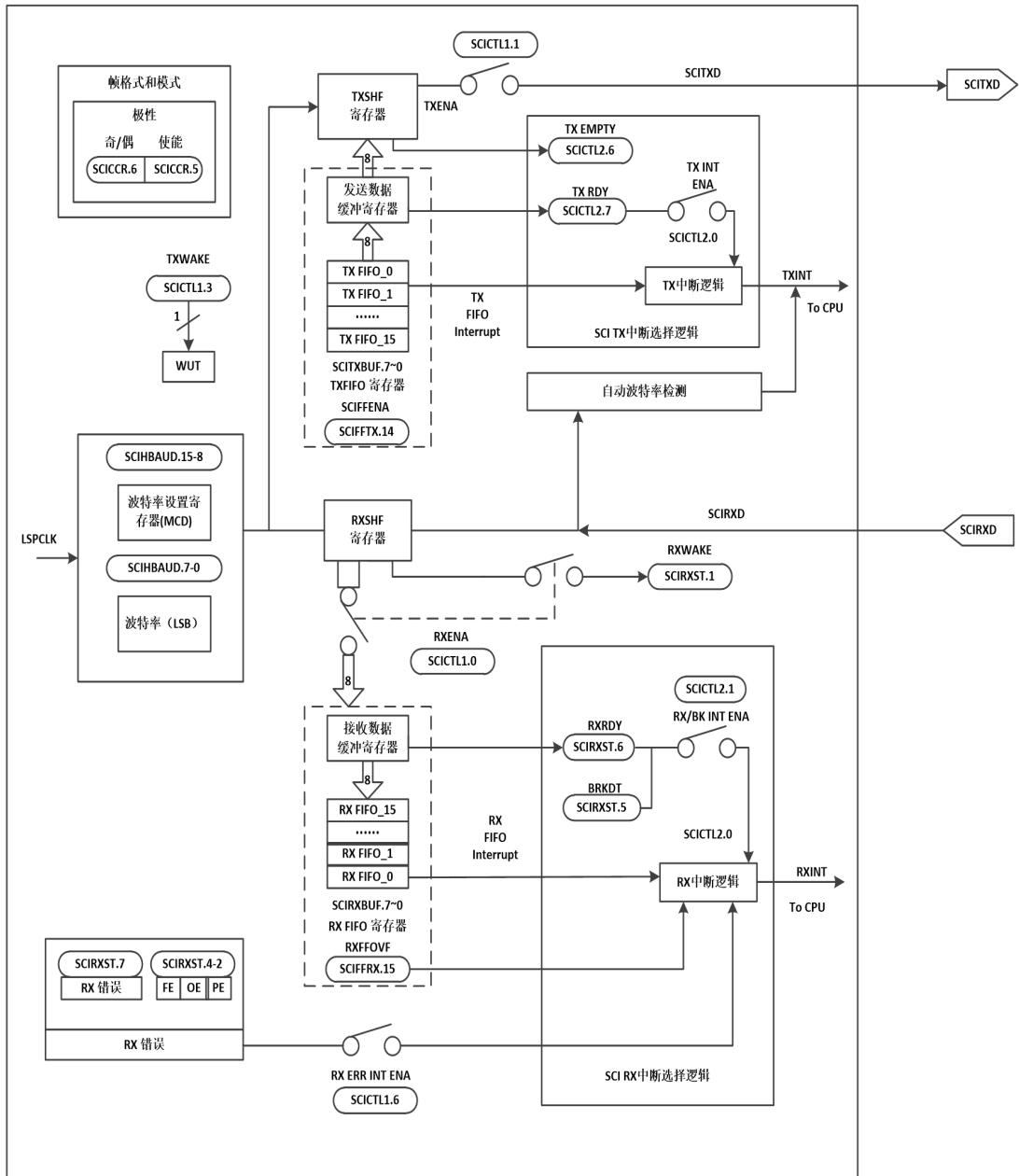

| 4.4.10. 串行通信接口 (SCI) 模块 (SCI-A, SCI-B, SCI-C) ..... | 55 |

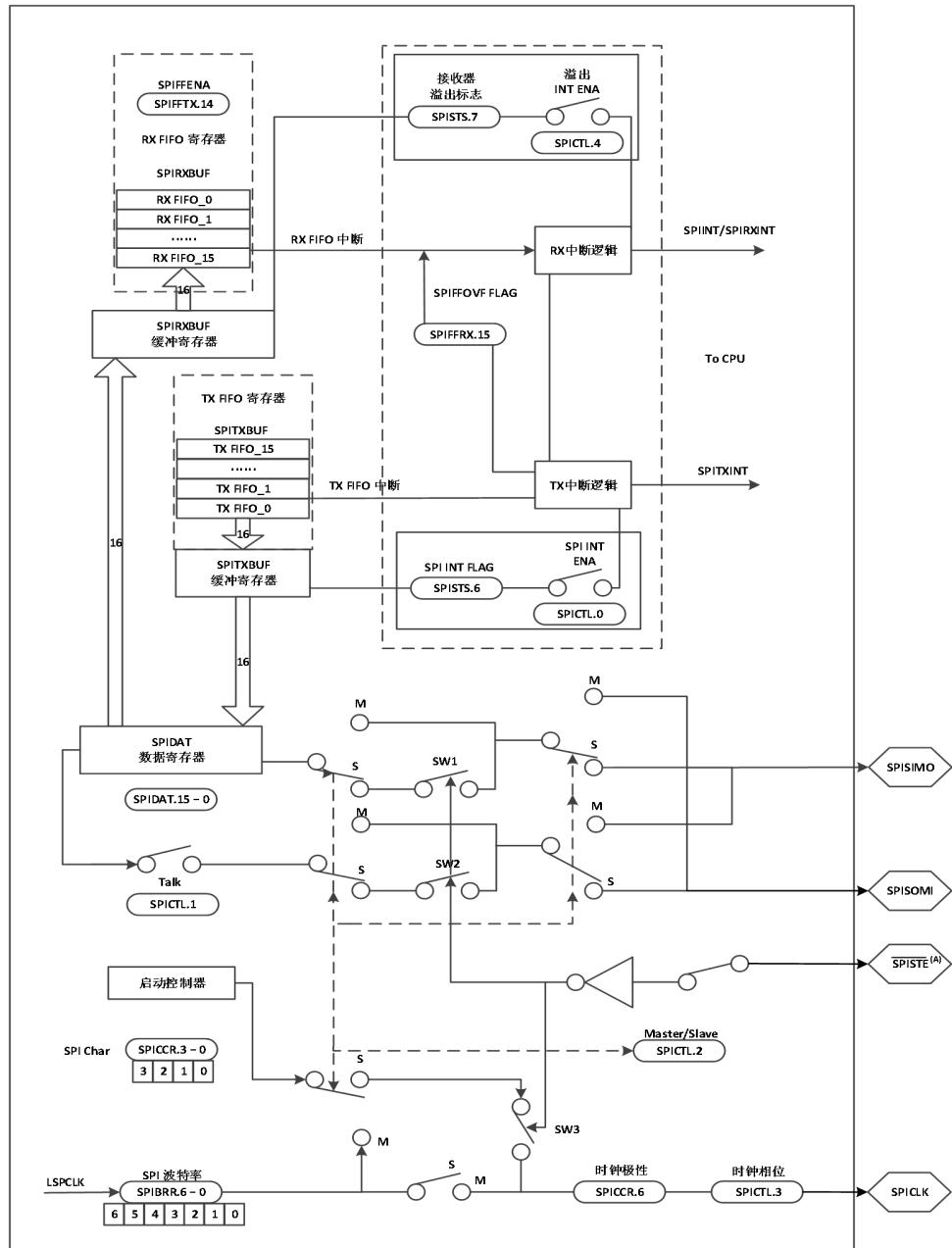

| 4.4.11. 串行外设接口 (SPI) 模块 (SPI-A) .....               | 59 |

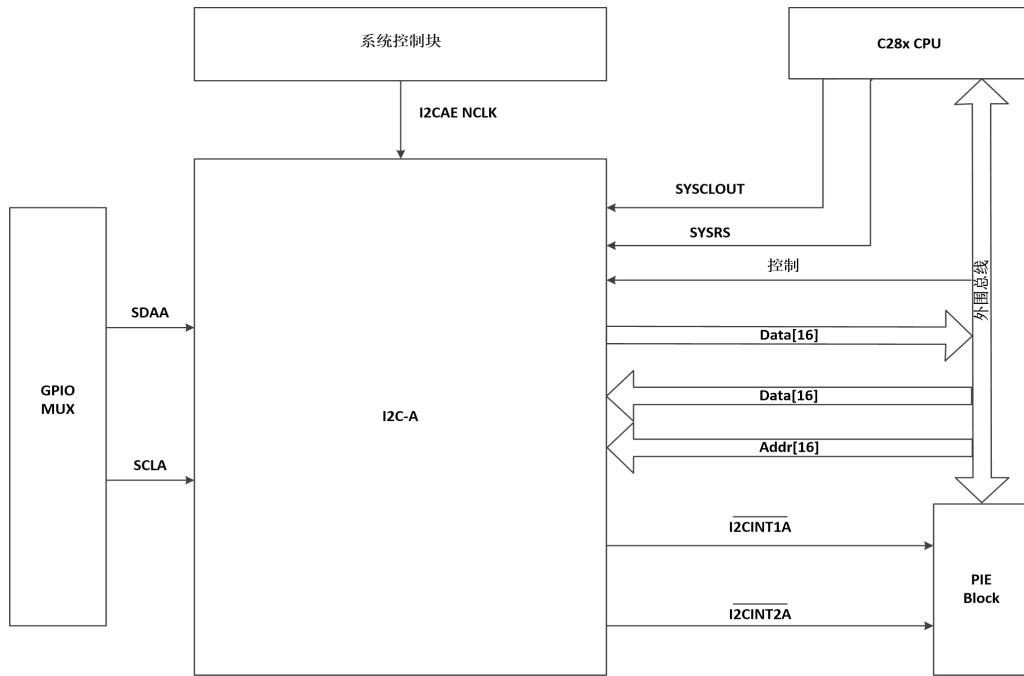

| 4.4.12. 内部集成电路(I2C) .....                           | 62 |

|                                 |         |

|---------------------------------|---------|

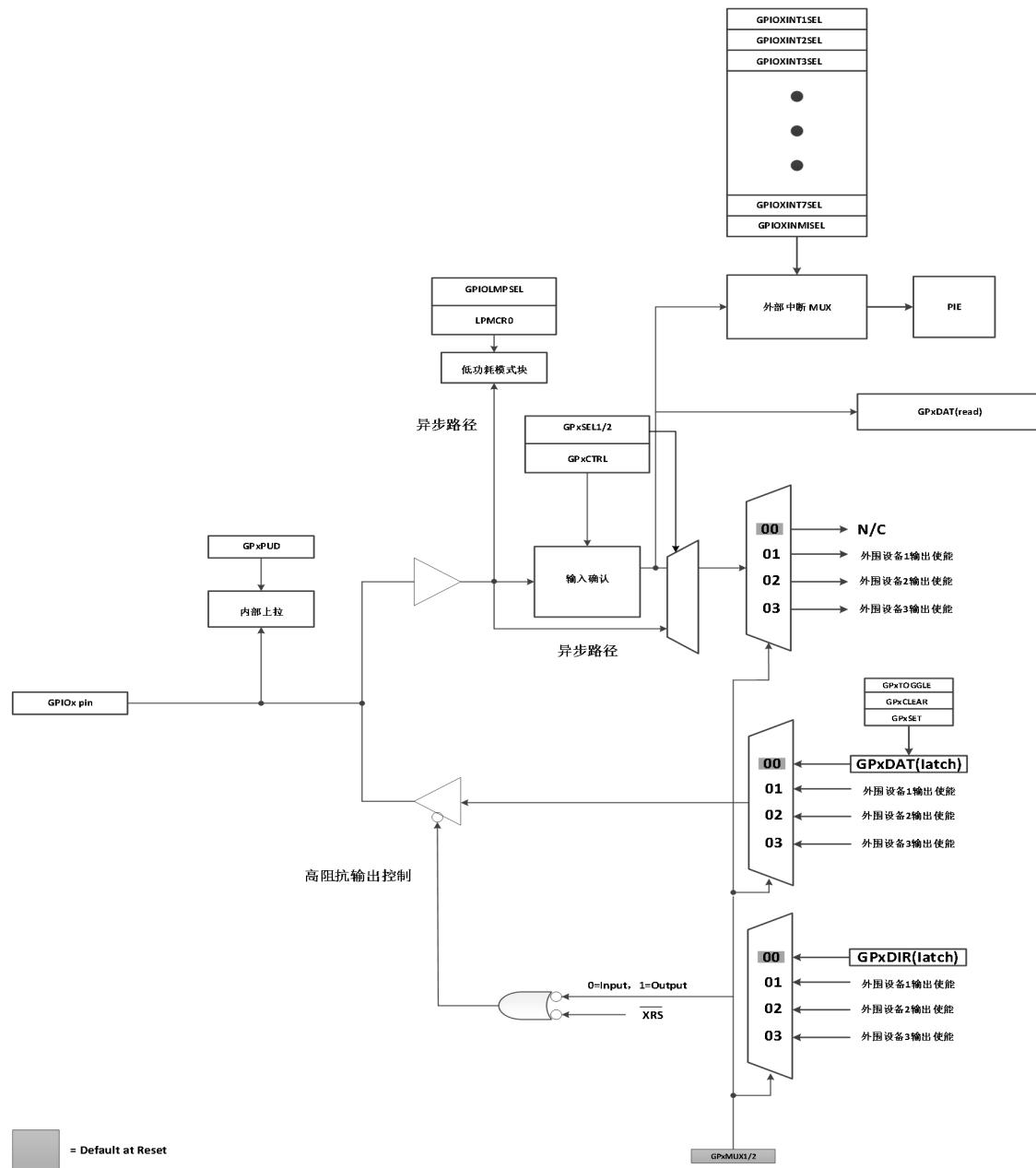

| 4.4.13. GPIO MUX.....           | 65      |

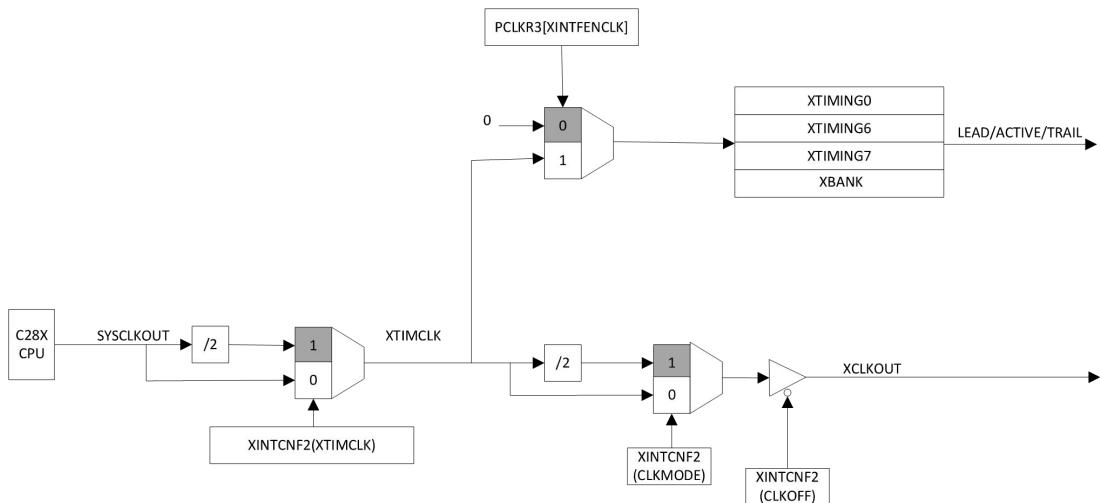

| 4.4.14. 外部接口(XINTF).....        | 72      |

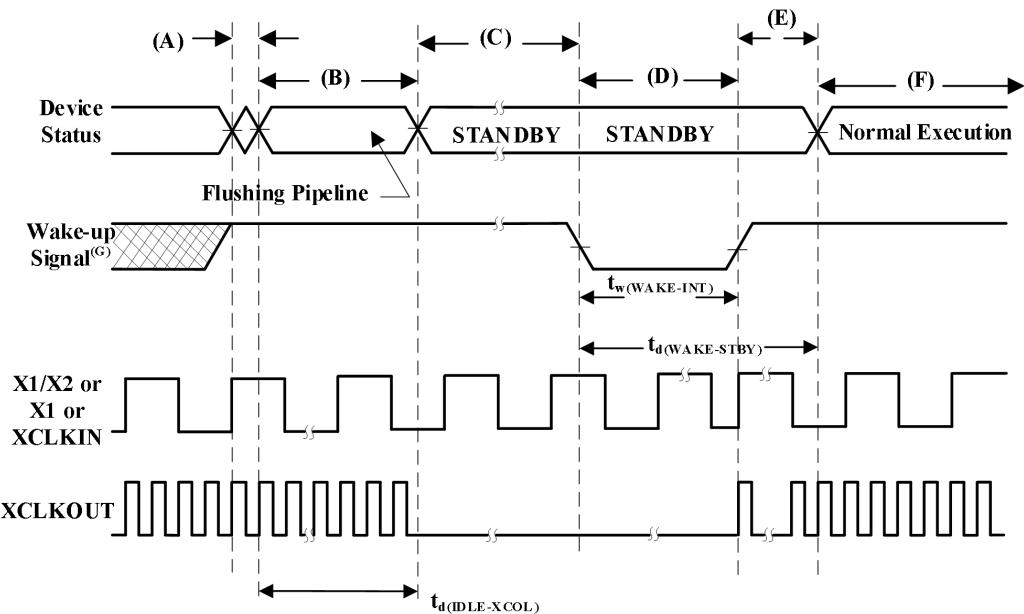

| 4.5. 低功耗模式 .....                | 75      |

| 4.6. 所有外设寄存器列表 .....            | 75      |

| 4.6.1. 寄存器映射 .....              | 75      |

| 4.6.2. 闪存和 OTP 寄存器 .....        | 76      |

| 4.6.3. 代码安全模块（CSM）寄存器.....      | 81      |

| 4.6.4. DMA 寄存器 .....            | 82      |

| 4.7. 启动流程与 BOOT ROM .....       | 86      |

| <br>                            |         |

| 5. 时序和开关特性.....                 | 87      |

| <br>                            |         |

| 5.1. 时序参数符号 .....               | 87      |

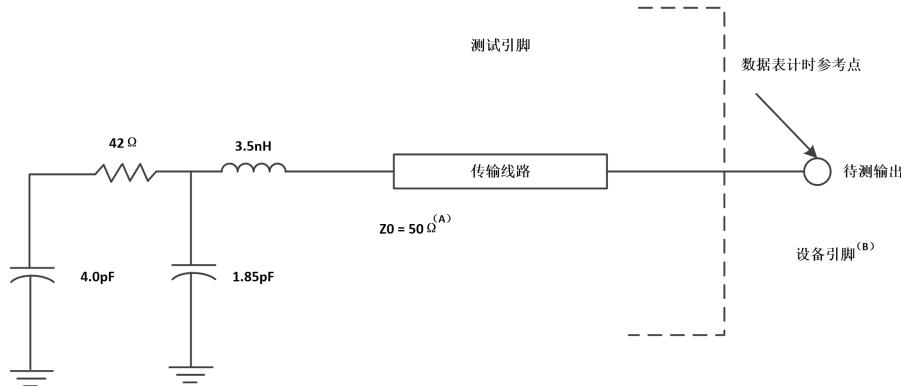

| 5.2. 测试负载电路 .....               | 88      |

| 5.3. 器件时钟表 .....                | 88      |

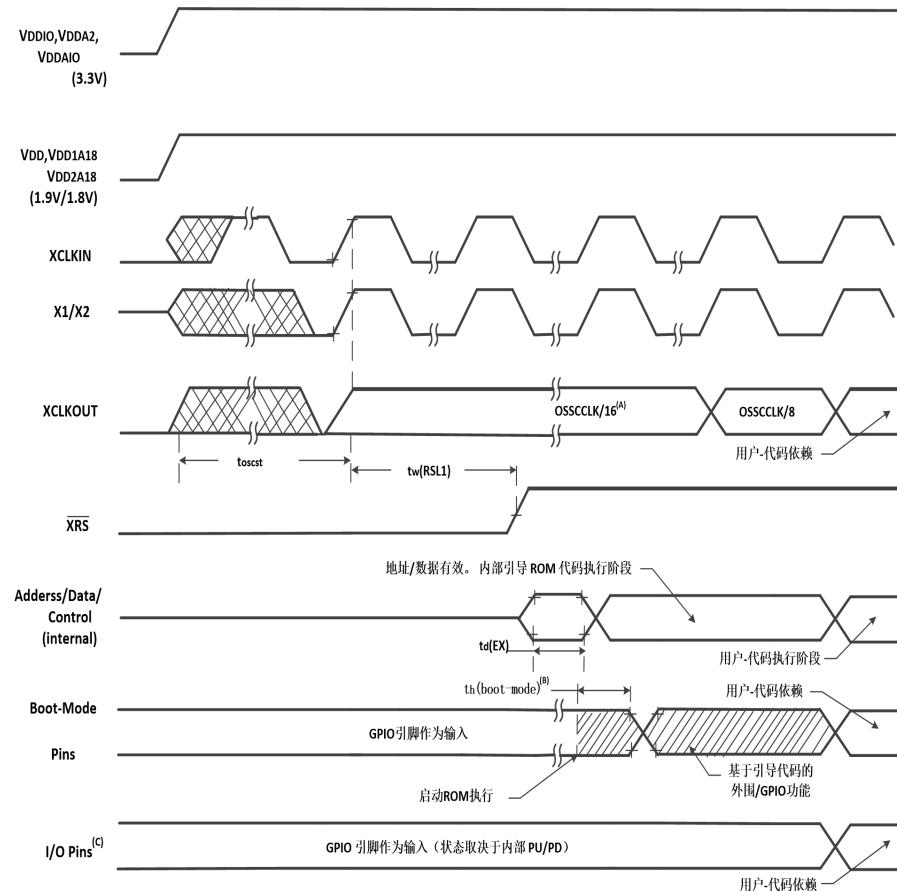

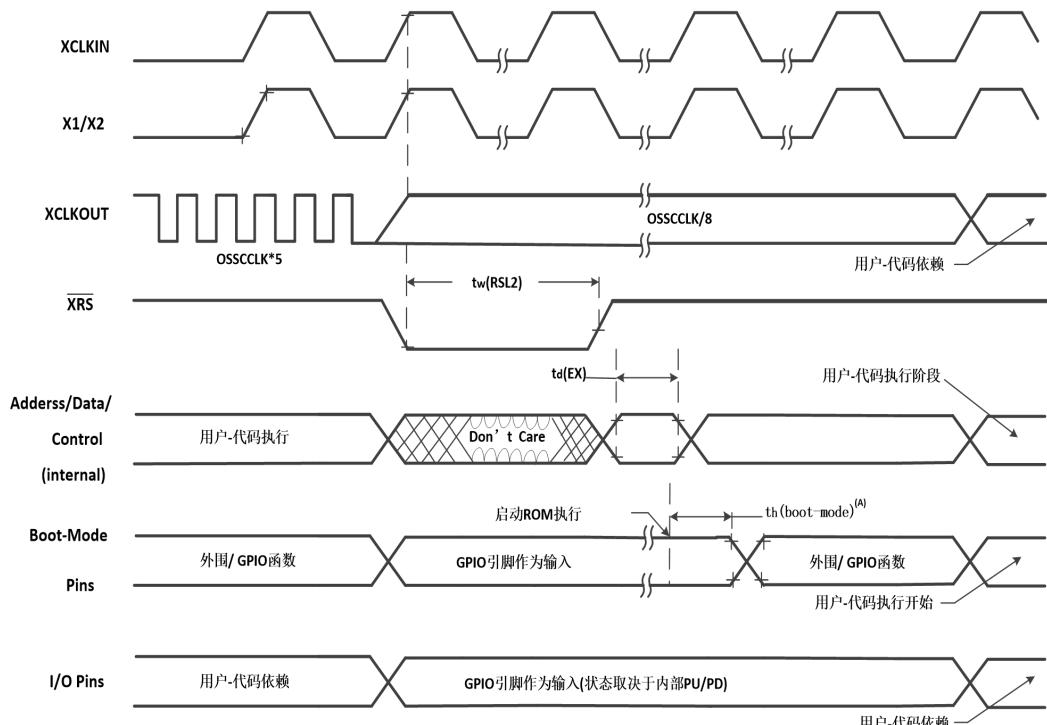

| 5.4. 电源排序 .....                 | 89      |

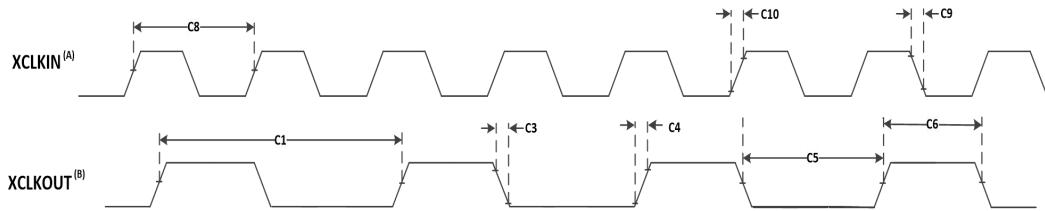

| 5.5. 时钟要求和特性 .....              | 91      |

| 5.6. 外设时序 .....                 | 93      |

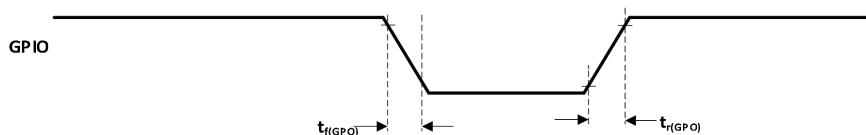

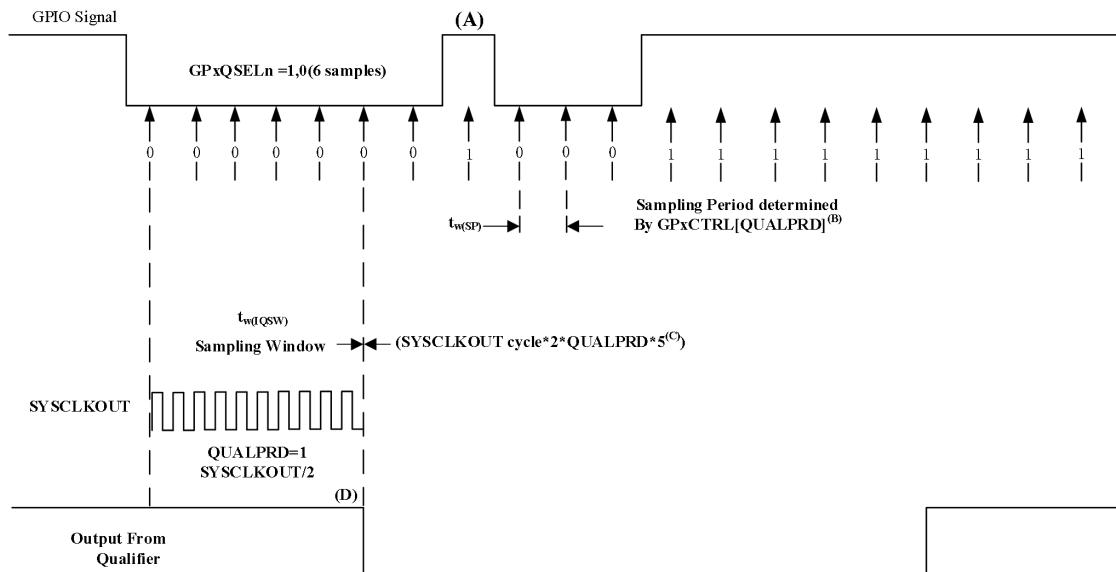

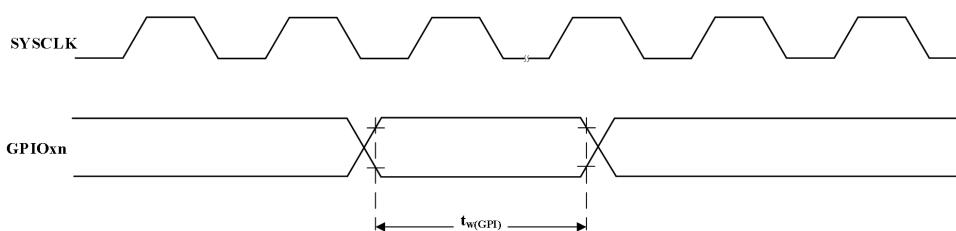

| 5.6.1. 通用输入输出（GPIO） .....       | 93      |

| 5.6.2. 增强型控制外设 .....            | 99      |

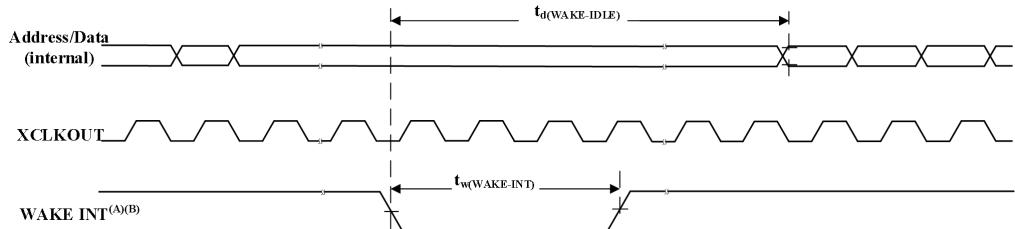

| 5.6.3. 外部中断时序 .....             | 101     |

| 5.6.4. I2C 电气规格和时序 .....        | 102     |

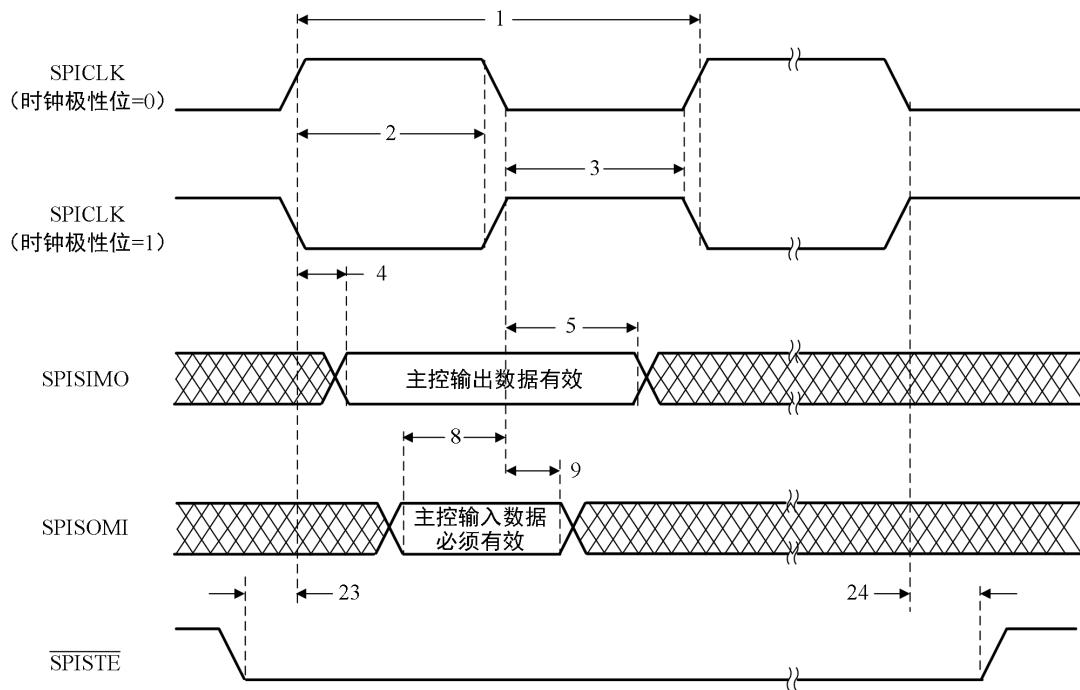

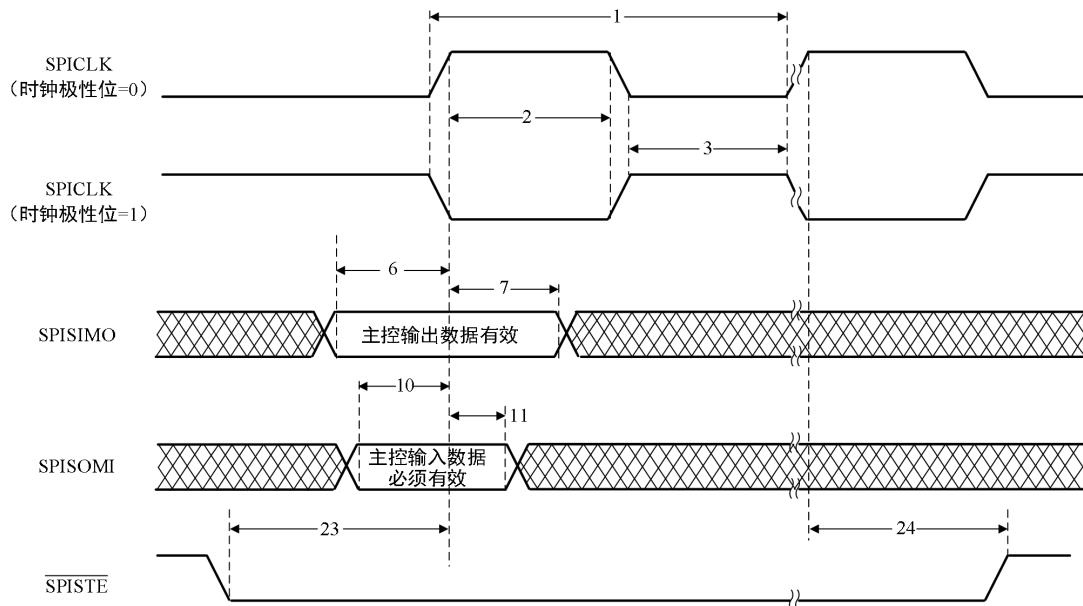

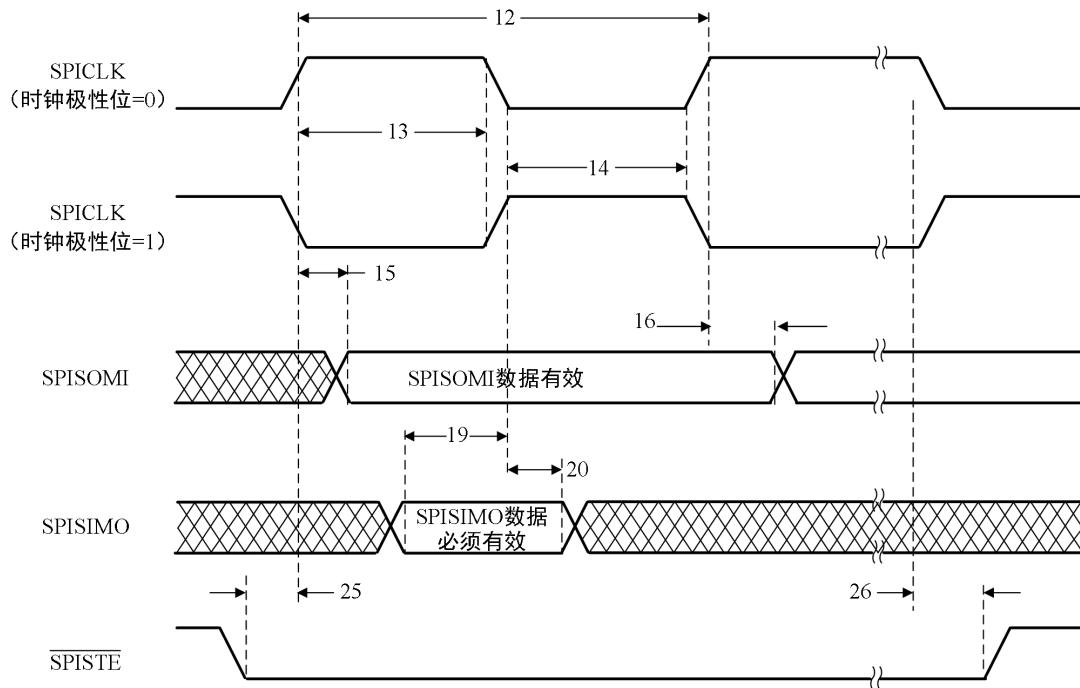

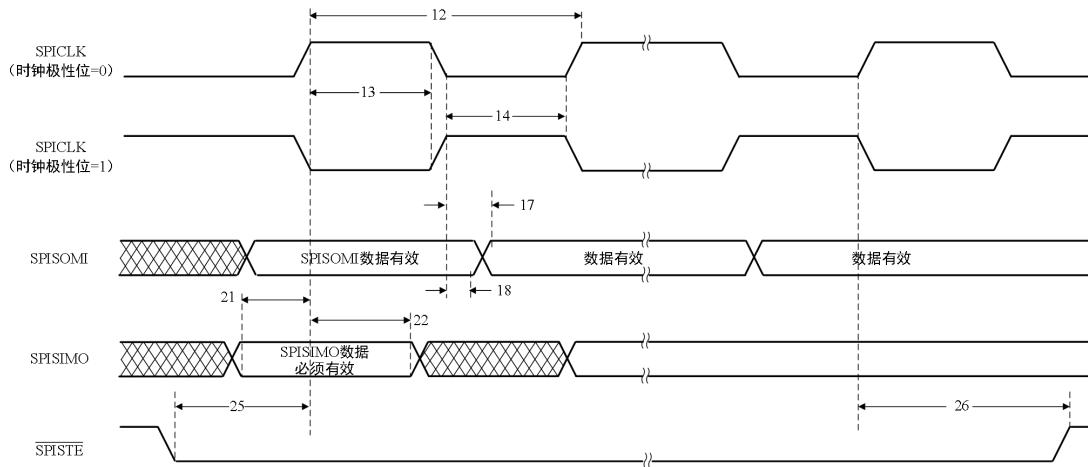

| 5.6.5. 串行外设接口（SPI）时序 .....      | 102     |

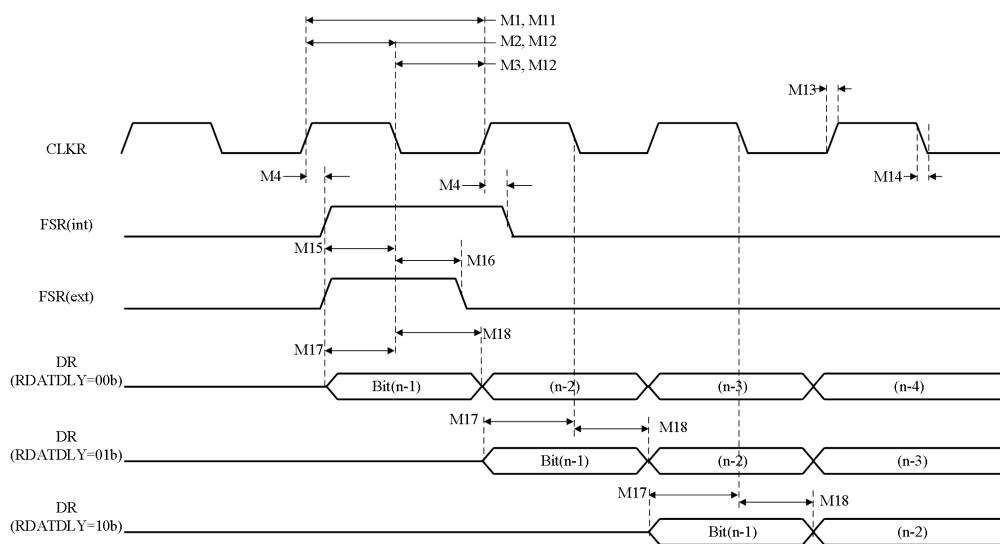

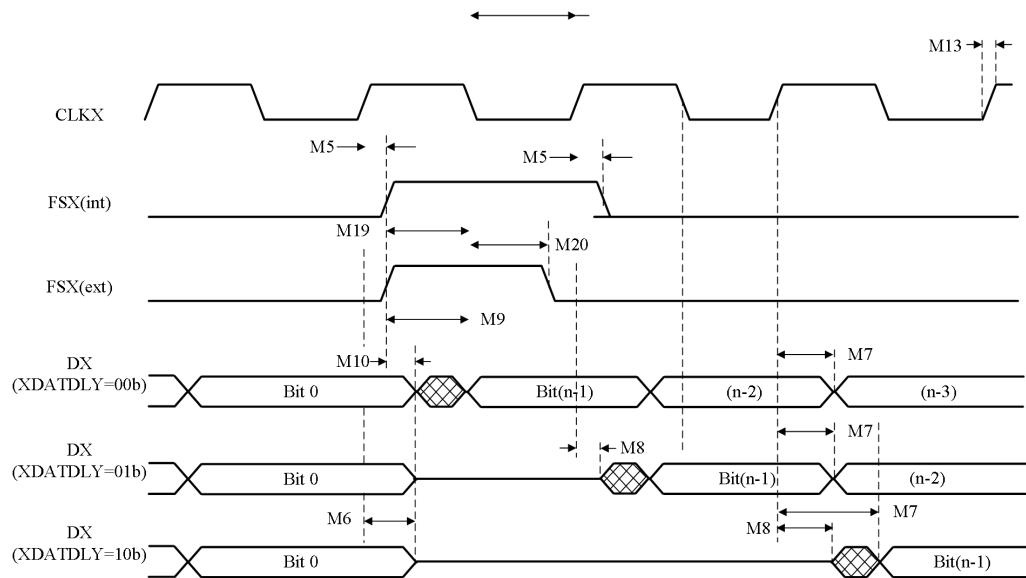

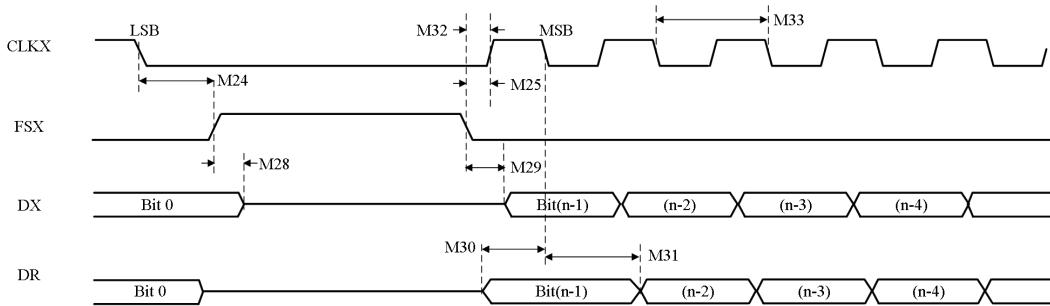

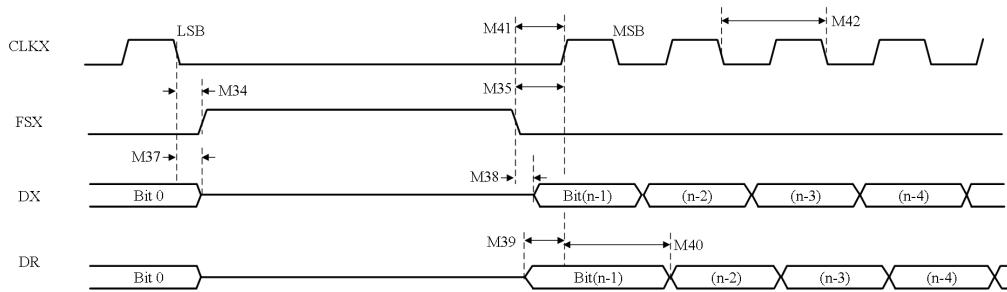

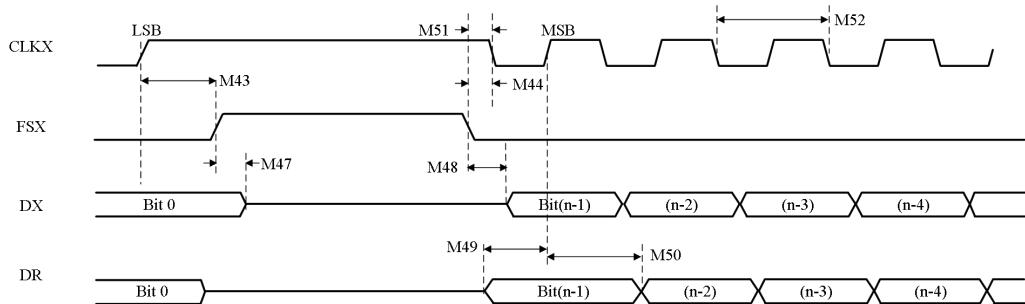

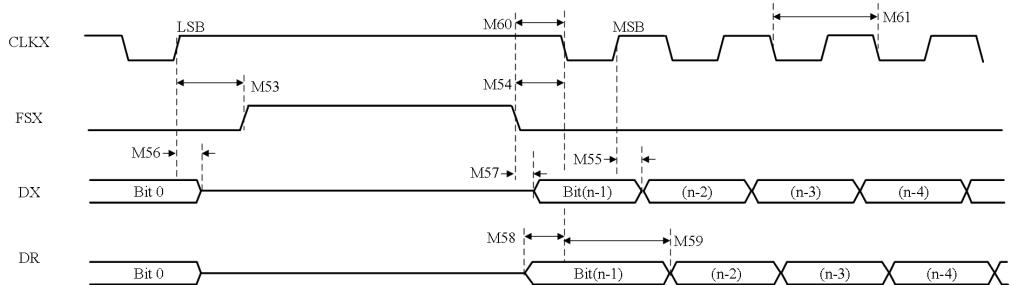

| 5.6.6. 多通道缓冲串行端口（MCBSP）时序 ..... | 107     |

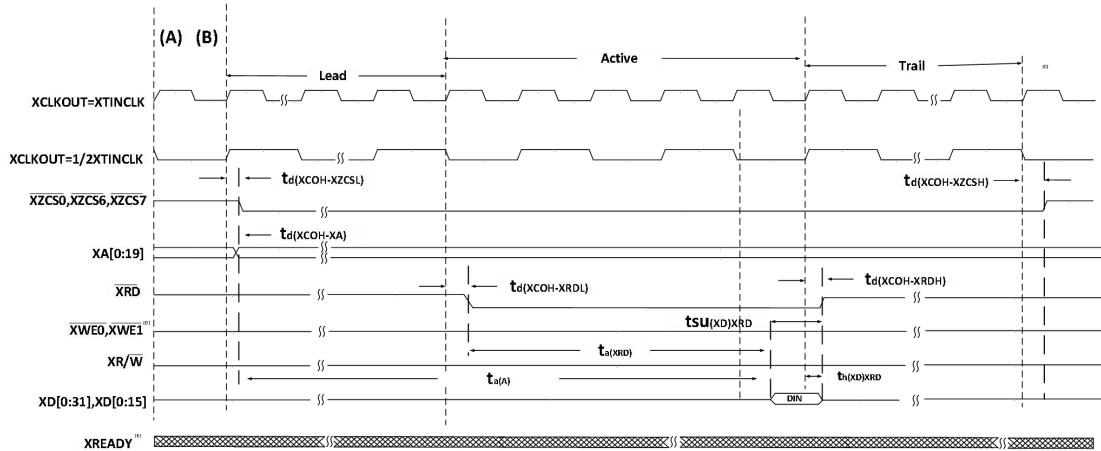

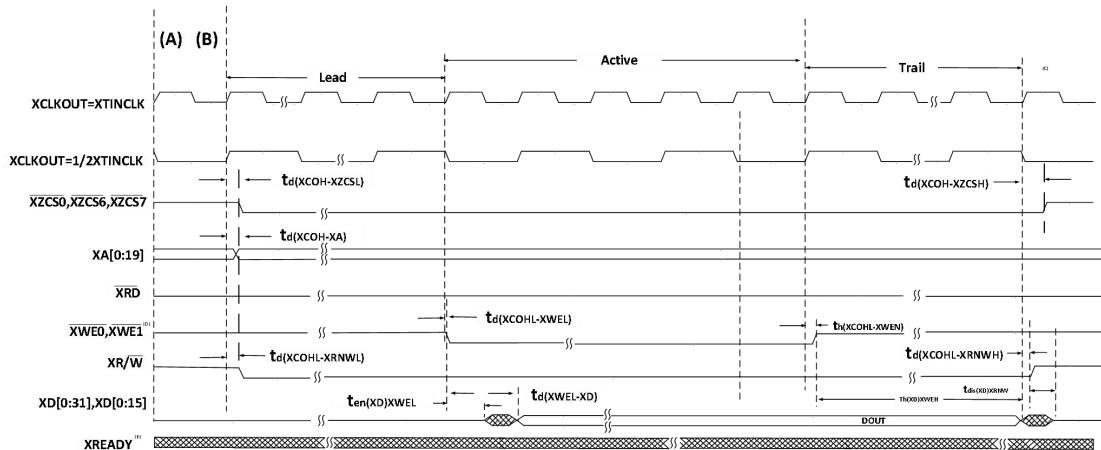

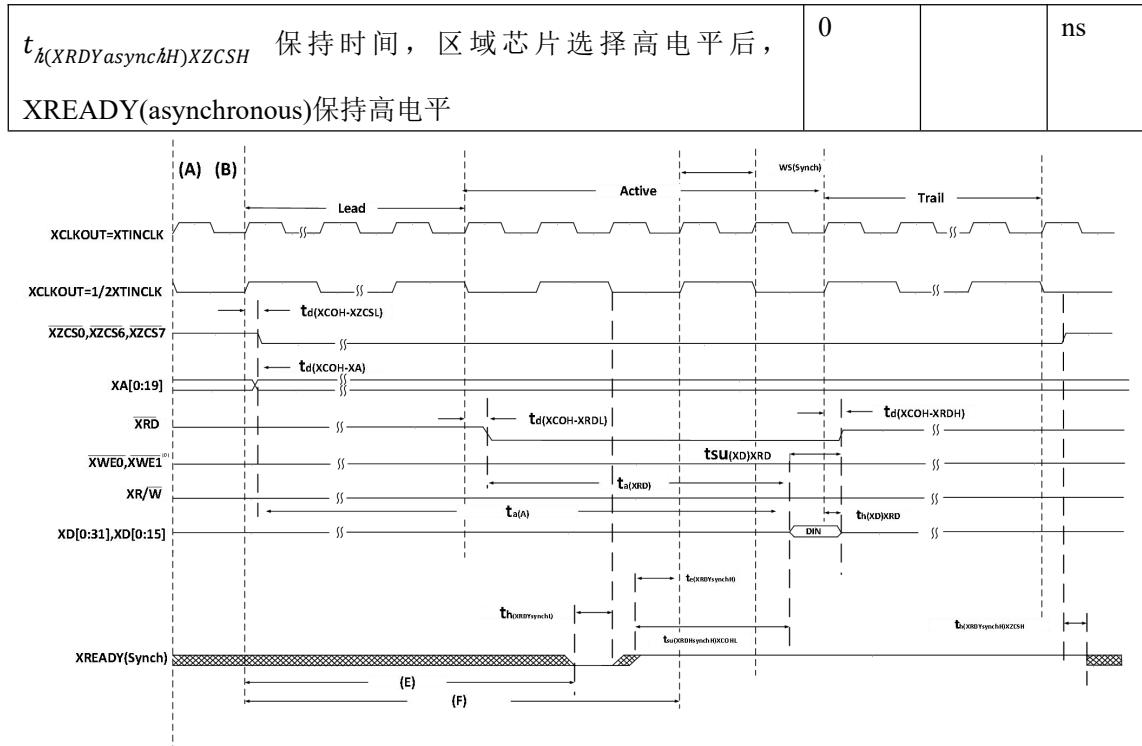

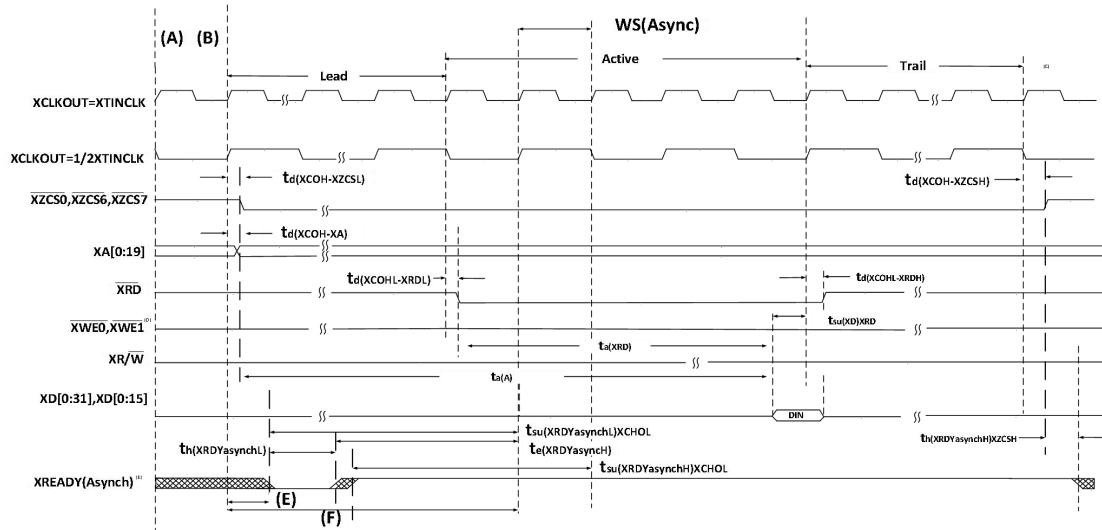

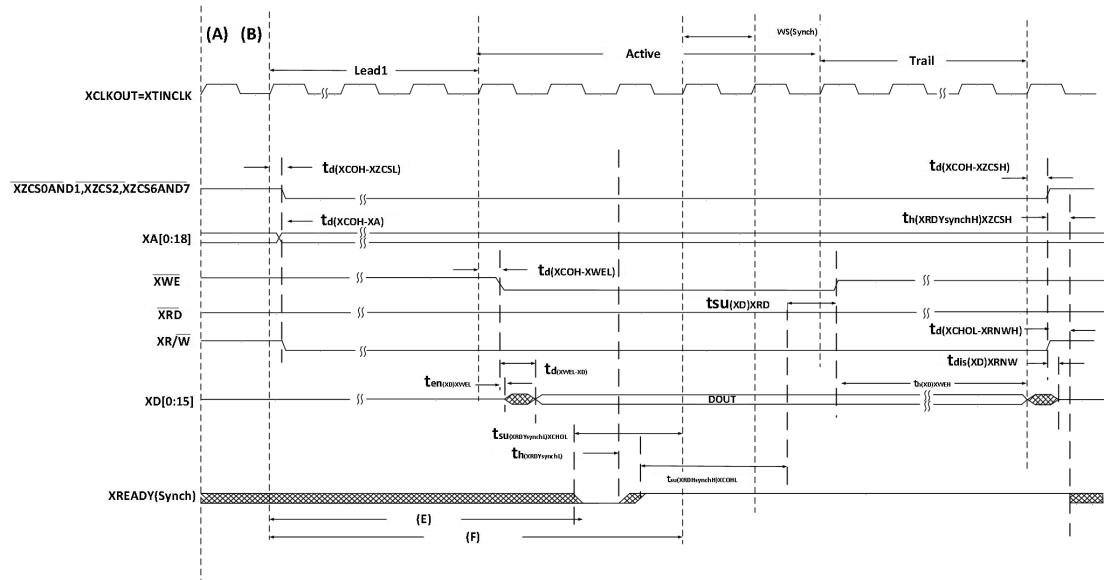

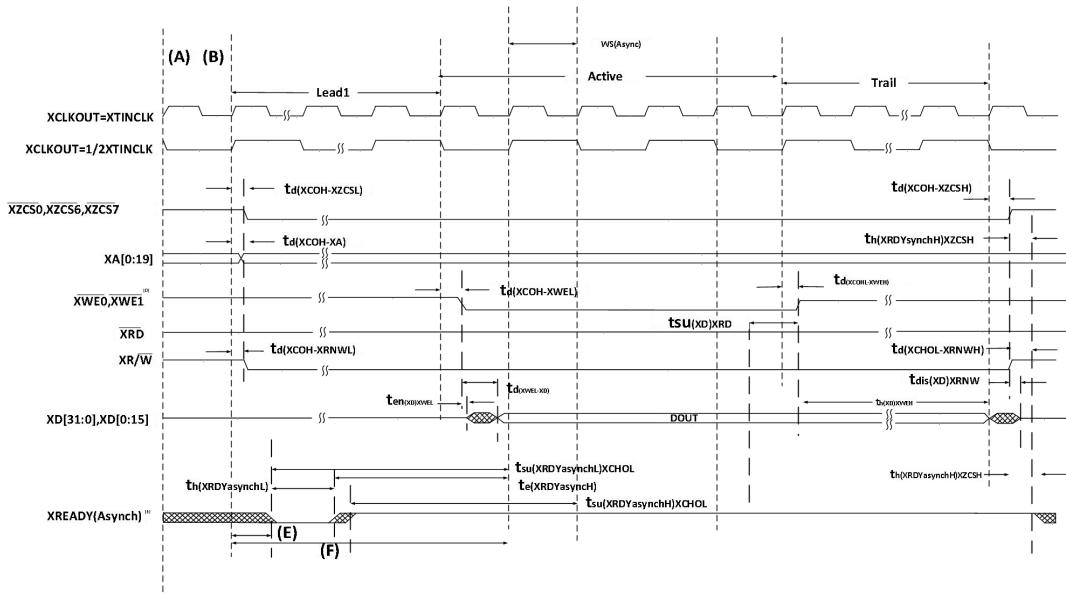

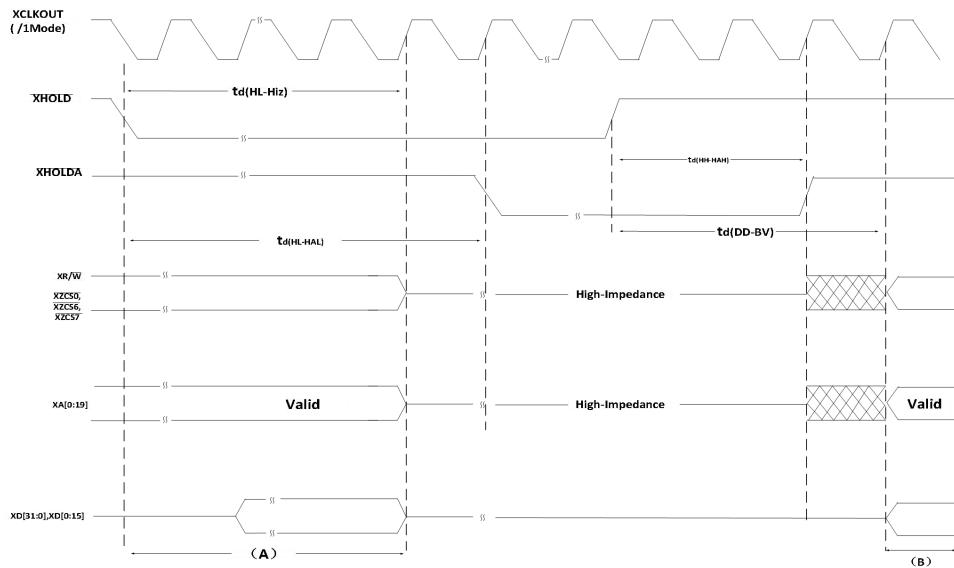

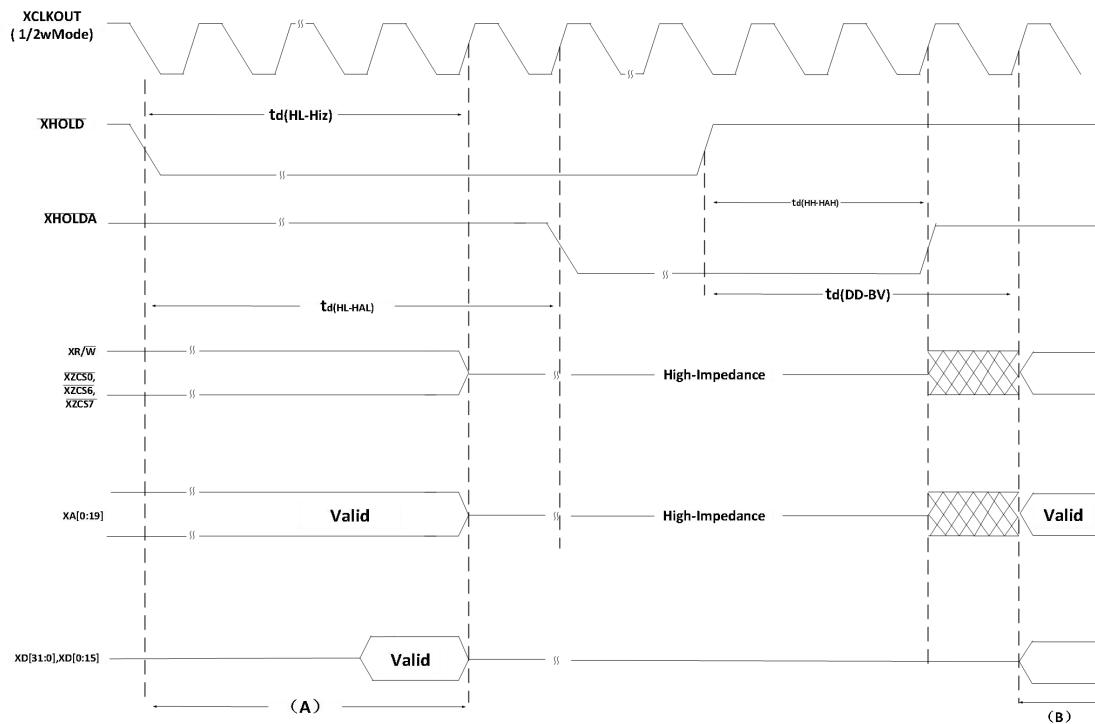

| 5.6.7. 外部接口(XINTF)时序 .....      | 114     |

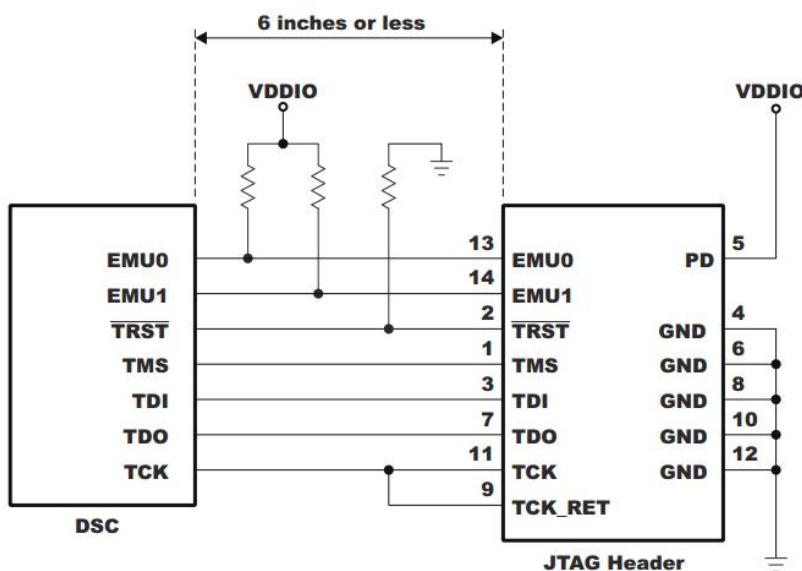

| 5.6.8. 不带信号缓冲的 DSP 仿真器连接 .....  | 115     |

| 5.6.9. 闪存(FLASH)时序 .....        | - 133 - |

| <br>                            |         |

| 6. 程序移植 .....                   | - 136 - |

|                    |         |

|--------------------|---------|

| 6.1. 可移植性 .....    | - 136 - |

| 6.2. 转换程序 .....    | - 136 - |

| 7. 电气规范 .....      | - 136 - |

| 7.1. 最大绝对额定值 ..... | - 136 - |

| 7.2. 建议的运行条件 ..... | - 137 - |

| 7.3. 电气特性 .....    | - 138 - |

# 1. 产品特色

- 高性能数字信号处理器技术

- 高达 150MHz(6.67ns周期时间)

- 1.8V/1.9V内核, 3.3V I/O设计

- 高性能32位 DSP

- IEEE 754-2008单精度浮点单元(FPU), RNE、RTZ、RDN、RUP、RMM 舍入模式

- 16×16和32×32乘累加运算 (MAC), 40bit的MR寄存器(Multiply-accumulate Register)

- 16×16双乘累加运算(MAC)

- 哈佛(Harvard)总线架构

- 快速中断响应和处理, 增强实现RISC-V中断标准 (PLIC+CLINT)

- 统一存储器编程模型

- 高效代码(使用C/C++和汇编语言)

- 6通道DMA处理器(用于ADC, McBSP, ePWM, XINTF和SARAM)

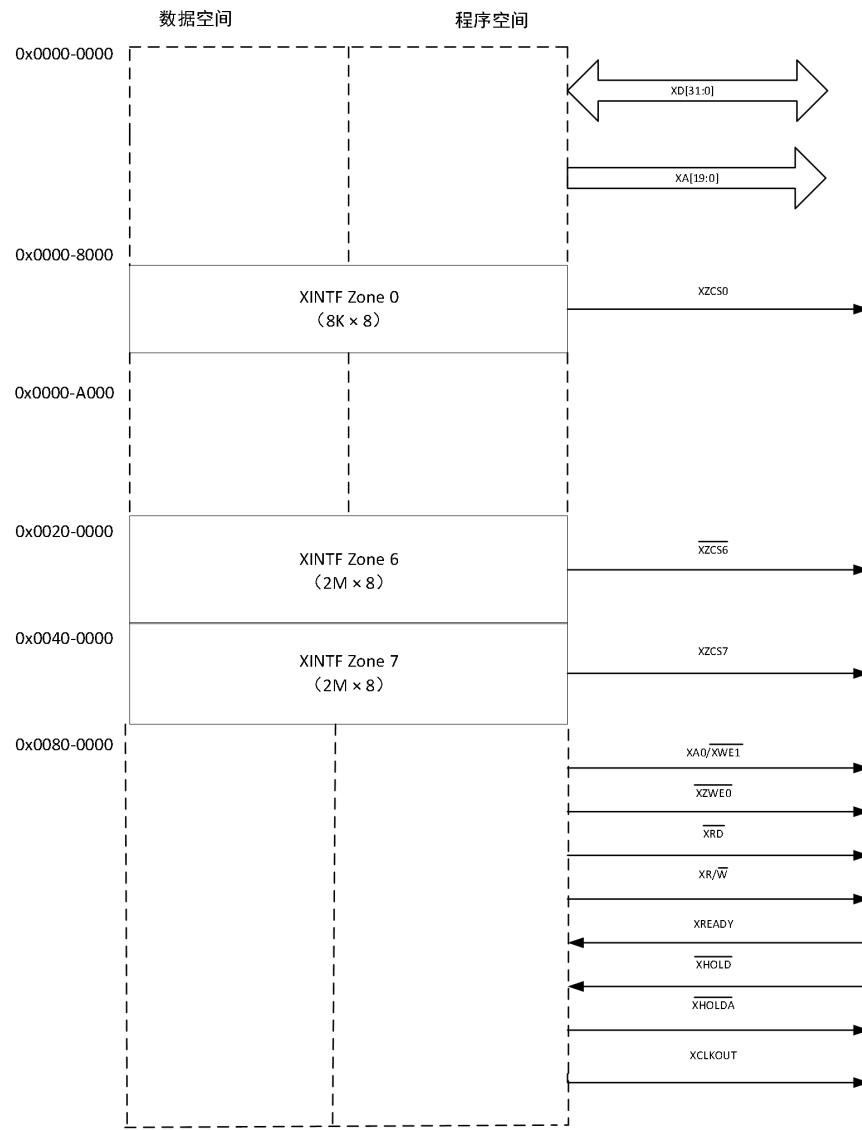

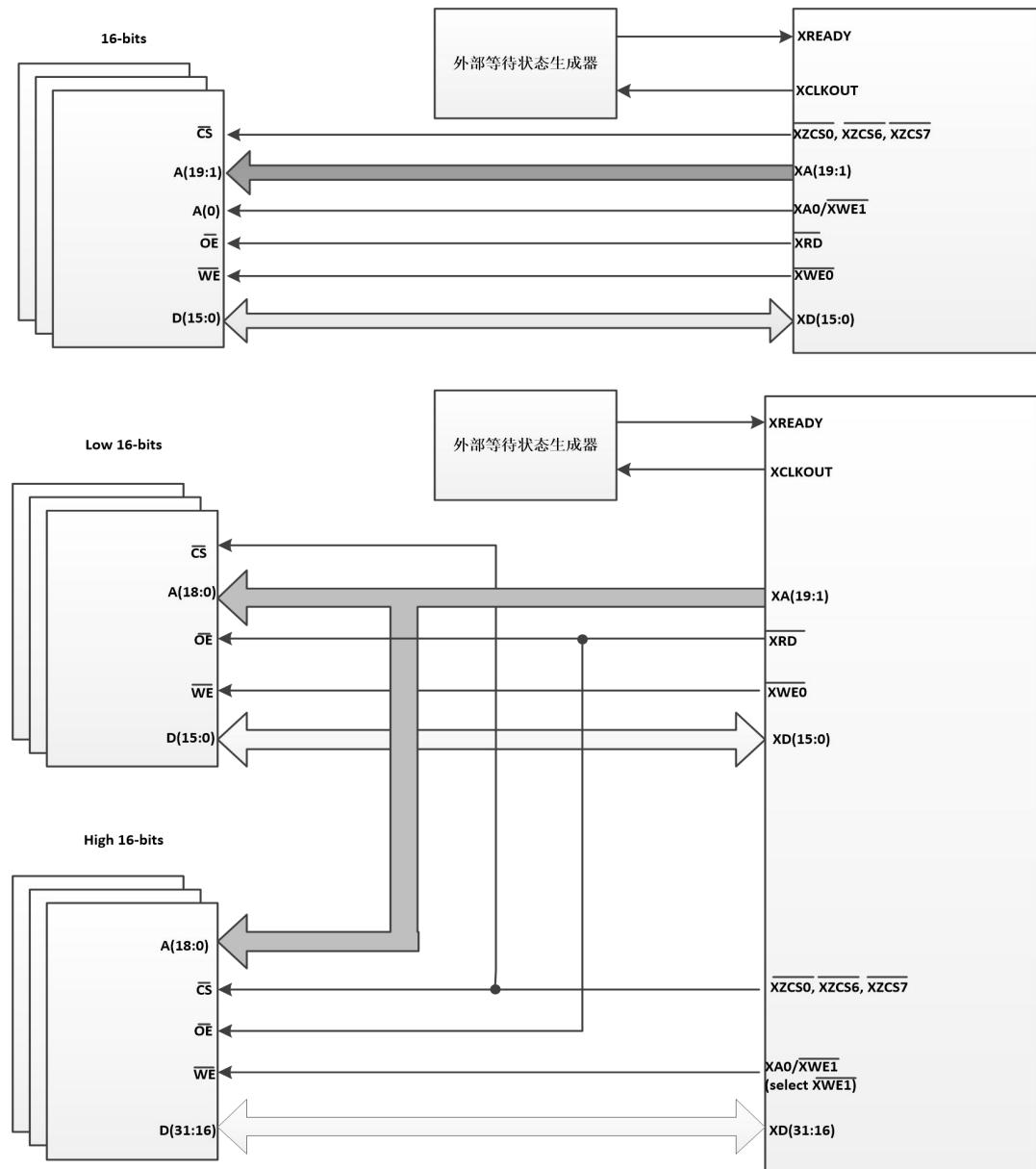

- 16位或32位外部接口(XINTF)

- 超过4M×8地址范围

- 片载存储器

- 512K×8闪存, 16K×8 SARAM

- 4K×8一次性可编程(OTP)ROM

- 引导ROM (16K×8)

- 支持软件引导模式(通过SCI, SPI, CAN, I2C, McBSP, XINTF和并行I/O)

- 标准数学查找表

- 时钟和系统控制

- 支持动态锁相环(PLL)比率变化

- 片载振荡器

- 安全装置定时器模块

- GPIO0到 GPIO63引脚可以连接到八个外部内核中断其中的一个

- 128 位安全密钥/锁

- 保护闪存/OTP/RAM 模块

- 防止固件逆向工程

- 增强型控制外设

- 多达18个脉宽调制(PWM)输出

- 高达 6 个支持 150ps 微边界定位(MEP)分辨率的高分辨率脉宽调制(HRPWM)输出

- 高达6个事件捕捉输入

- 多达两个正交编码器接口

- 高达8个32位定时器(6个eCAP以及 2个eQEP)

- 高达9个32位定时器(6个ePWM以及 3个XINTCTR)

- 三个 32 位 DSP定时器

- 串行端口外设

- 多达2个控制器局域网(CAN)模块

- 多达3个SCI (UART)模块

- 高达2个 McBSP模块(可配置为SPI)

- 一个SPI模块

- 一个内部集成电路(I2C)总线

- 12位模数转换器(ADC), 16个通道

- 80ns转换率

- $2 \times 8$ 通道输入复用器

- 两个采样保持

- 单一/同步转换

- 内部或者外部基准

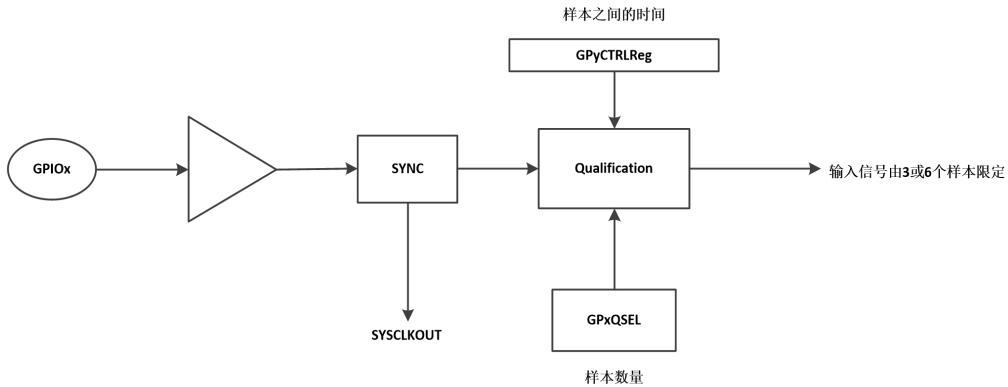

- 多达88个具有输入滤波功能可单独编程的多路复用通用输入输出(GPIO)引脚

- 支持RISC-V Debug 0.13.2调试标准

- 高级仿真特性

- 分析和断点功能

- 借助硬件的实时调试

- 开发支持包括

- ANSI C/C++编译器/汇编语言/链接器

- 数字电机控制和数字电源软件库

- 低功耗模式和省电模式

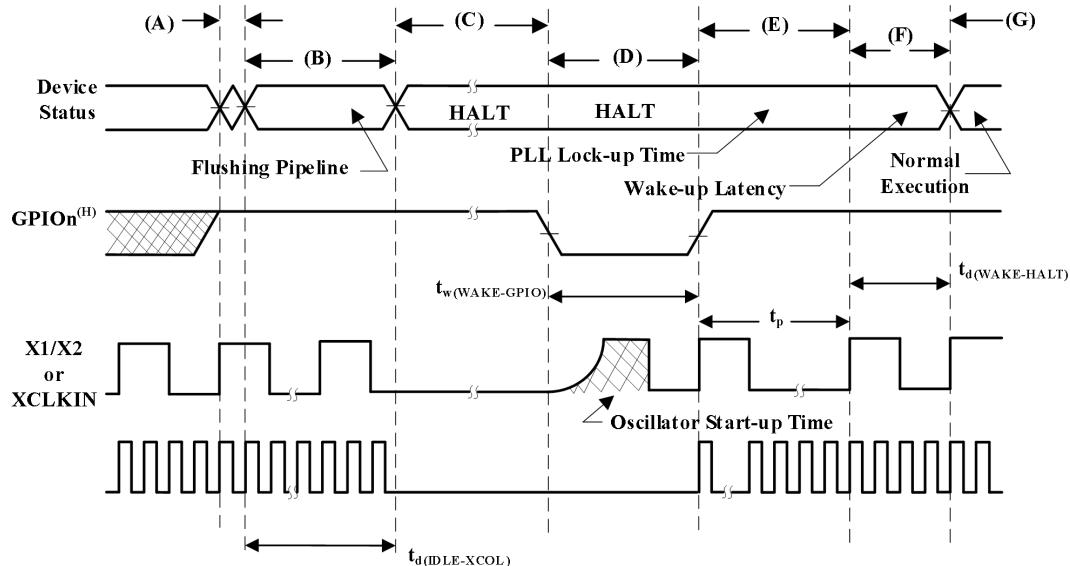

- 支持IDLE(空闲)、STANDBY(待机)、HALT(暂停)模式

- 可禁用独立外设时钟

- 字节存放顺序: 小端模式

- 封装选项:

- 无铅, 绿色封装

- 塑料四方扁平176管脚 (LQFP176) 封装

- 尺寸按GB/T 7092的规定

- 工作温度

- E - 工业应用+, -40~125°C

## 2. 功能结构图

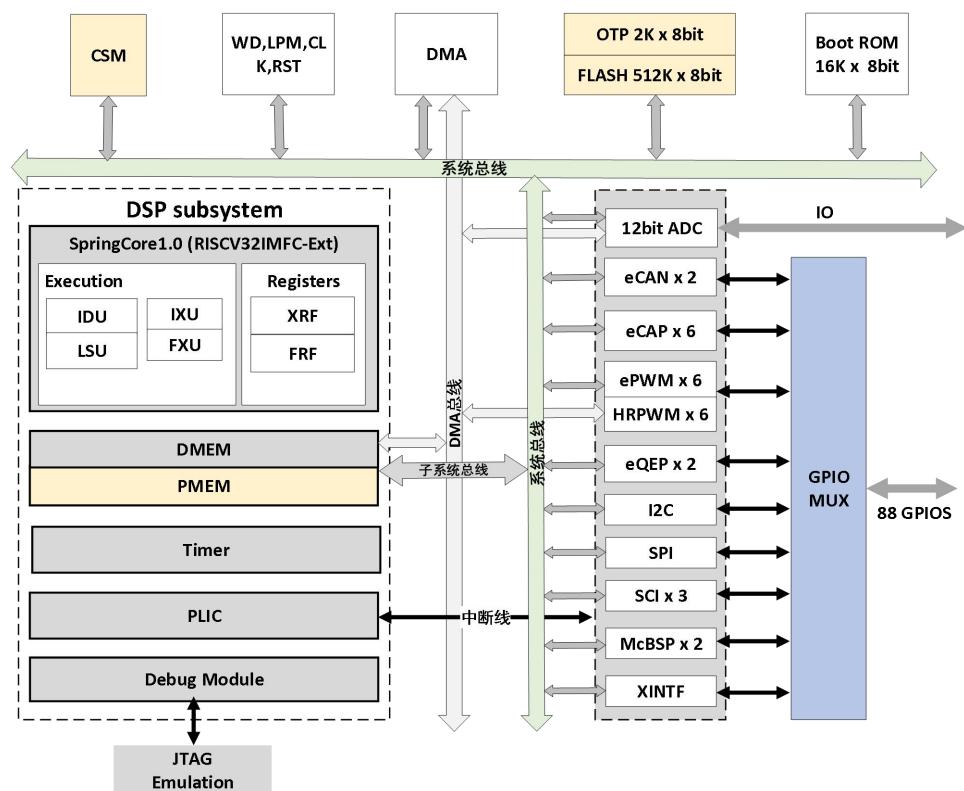

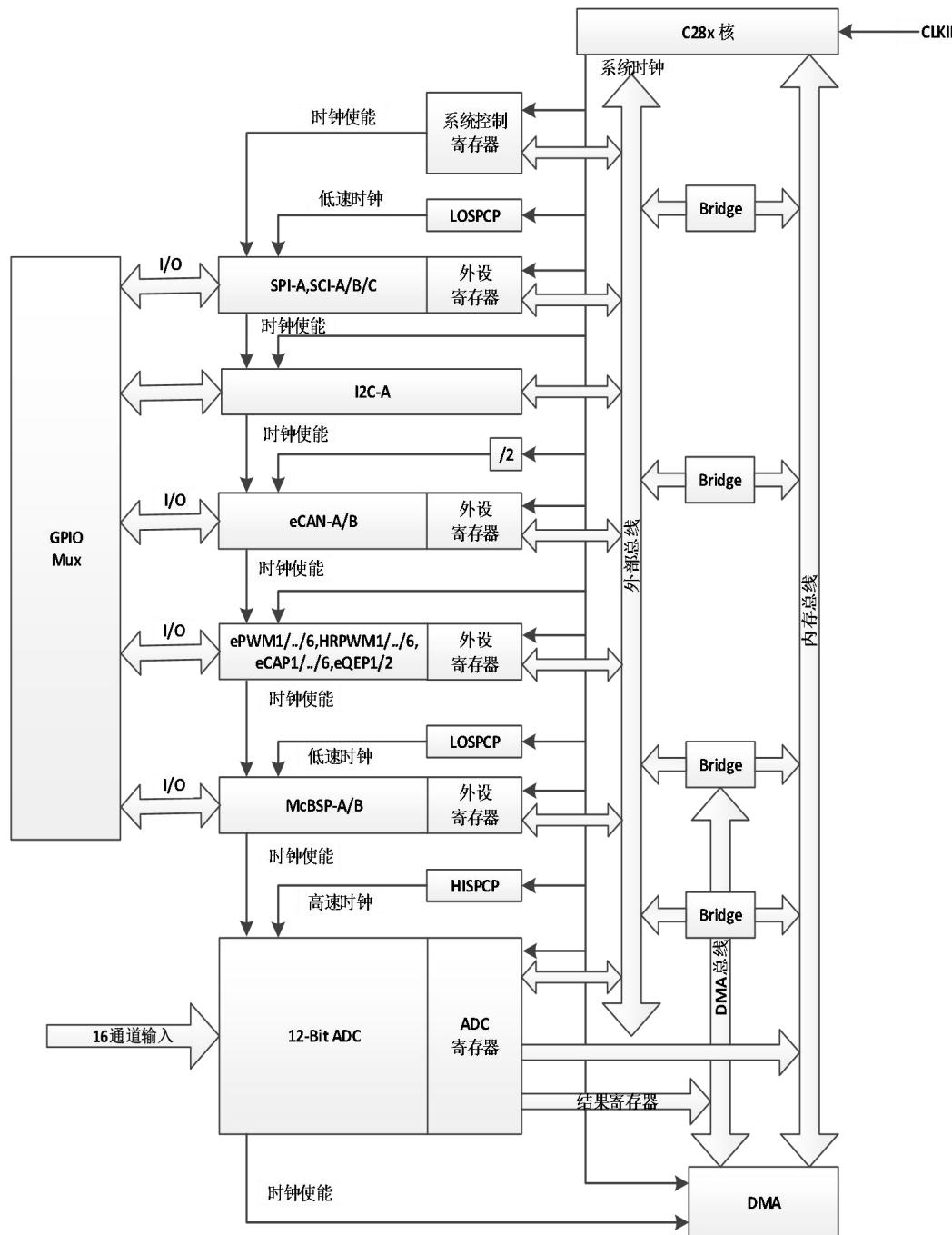

FDM320RV335 结构框图如图 2-1 所示。

图 2-1 FDM320RV335 功能结构图

FDM320RV335 所有组件均挂在系统总线上, 其中主设备包括 DSP 子系统和

DMA。DSP 子系统包括 RISC-V 架构的 SpringCore1.0、独立的内部存储单元、定时器、中断控制器和调试单元。

SpringCore1.0 发起访问时, DSP 子系统内部总线首先对地址进行判定, 如果地址属于子系统内部, 则在内部完成访问; 否则, 内部总线将访问请求发送至系统总线, 在系统总线的调度下完成访问。DMA 作为主设备发起访问前, 首先作为从设备接受 SpringCore1.0 的配置, 其后 DMA 发起访问。DMA 能够访问的从设备包括: DSP 子系统内部的数据存储单元、ADC 的结果寄存器、ePWM+HRPWM 的寄存器。所有外设通过中断控制器 (PLIC) 对 DSP 子系统内部进行系统的访问和设置。PLIC 接入多个外部中断源将其仲裁后生成一根外部中断信号, 通给 DSP 子系统。

### 3. 引脚说明

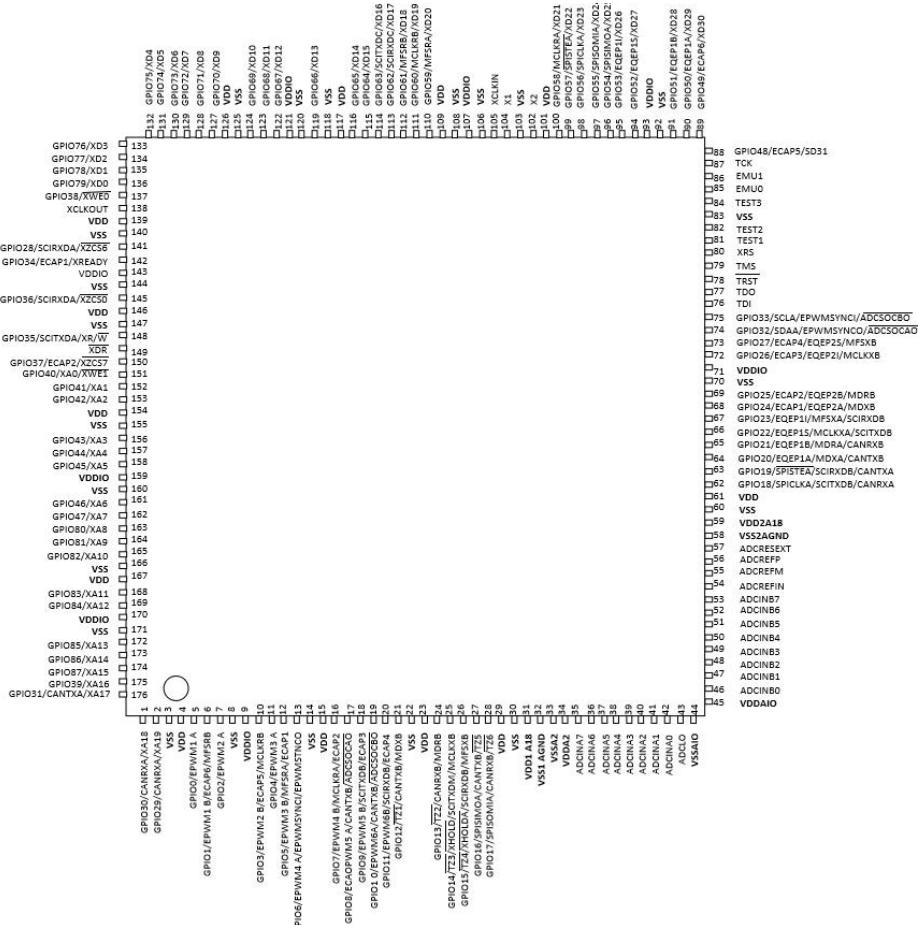

引脚分配如图 3-1 所示。各引脚的功能如表 3-1 所示。

图 3-1 RV335 引脚图

各引脚的信号描述如表 3-1 所示。GPIO 功能（用斜体表示）在复位时为缺省值，在它们下面列出的外设信号是供替代的功能。所有能够产生 XINTF 输出功能的引脚有 8mA(典型)的驱动强度，即使引脚没有配置 XINTF 功能，也可以有此驱动能力。所有其他引脚有一个 4mA 驱动力的驱动典型值(除非另有说明)。所有 GPIO 引脚都是 I/O/Z 且有一个内部上拉电阻器，此内部上拉电阻器可在每个引脚的基础上有选择性地启用/禁用。这一特性只适用于 GPIO 引脚。GPIO0-GPIO11 引脚的上拉电阻器在复位时并不启用。GPIO12-GPIO87 引脚上的上拉电阻器复位时被启用。

表 3-1 引脚信号描述

| 引出端编号 | 功能                                                         | 符号                                       | 引出端编号 | 功能                                        | 符号                       |

|-------|------------------------------------------------------------|------------------------------------------|-------|-------------------------------------------|--------------------------|

| LQFP  |                                                            |                                          | LQFP  |                                           |                          |

| 1     | 通用输入/输出 30<br>增强型 CAN-A 接收<br>外部接口地址线 18                   | <i>GPIO30</i><br>CANRXA<br>XA18          | 89    | 通用输入/输出 49<br>增强型捕捉输入/输出 6<br>外部接口数据线 30  | GPIO49<br>ECAP6<br>XD30  |

| 2     | 通用输入/输出 29<br>SCI 传输数据<br>外部接口地址线 19                       | <i>GPIO29</i><br>SCITXDA<br>XA19         | 90    | 通用输入/输出 50<br>增强型 QEP1 输入 A<br>外部接口数据线 29 | GPIO50<br>EQEP1A<br>XD29 |

| 3     | 数字逻辑地引脚                                                    | V <sub>ss</sub>                          | 91    | 通用输入/输出 51<br>增强型 QEP1 输入 B<br>外部接口数据线 28 | GPIO51<br>EQEP1B<br>XD28 |

| 4     | 内核与数字逻辑电源                                                  | V <sub>DD</sub>                          | 92    | 数字逻辑地引脚                                   | V <sub>ss</sub>          |

| 5     | 通用输入/输出 0<br>增强型 PWM1 输出 A 和 HRPWM 通道                      | <i>GPIO0</i><br>EPWM1A                   | 93    | 数字 I/O 电源                                 | V <sub>DDIO</sub>        |

| 6     | 通用输入/输出 1<br>增强型 PWM1 输出 B<br>增强型捕捉输入输出 6<br>McBSP-B 接收帧同步 | <i>GPIO1</i><br>EPWM1B<br>ECAP6<br>MFSRB | 94    | 通用输入/输出 52<br>增强型 QEP1 选通脉冲<br>外部接口数据线 27 | GPIO52<br>EQEP1S<br>XD27 |

| 7     | 通用输入/输出 2<br>增强型 PWM2 输出 A 和 HRPWM 通道                      | <i>GPIO2</i><br>EPWM2A                   | 95    | 通用输入/输出 53<br>增强型 QEP1 索引<br>外部接口数据线 26   | GPIO53<br>EQEP1I<br>XD26 |

|    |                                                                        |                                              |     |                                          |                            |

|----|------------------------------------------------------------------------|----------------------------------------------|-----|------------------------------------------|----------------------------|

| 8  | 数字逻辑地引脚                                                                | V <sub>ss</sub>                              | 96  | 通用输入/输出 54<br>SPI-A 从输入主输出<br>外部接口数据线 25 | GPIO54<br>SPISIMOA<br>XD25 |

| 9  | 数字 I/O 电源                                                              | V <sub>DDIO</sub>                            | 97  | 通用输入/输出 55<br>SPI-A 从输出主输入<br>外部接口数据线 24 | GPIO55<br>SPISOMIA<br>XD24 |

| 10 | 通用输入/输出 3<br>增强 PWM2 输出 B<br>增强型捕捉 5 输入输出<br>McBSP-B 接收帧同步             | GPIO3<br>EPWM2B<br>ECAP5<br>MCLKRB           | 98  | 通用输入/输出 56<br>SPI-A 时钟<br>外部接口数据线 23     | GPIO56<br>SPICLKA<br>XD23  |

| 11 | 通用输入/输出 4<br>增强型 PWM3 输出 A 和<br>HRPWM 通道                               | GPIO4<br>EPWM3A                              | 99  | 通用输入/输出 57<br>SPI-A 从发送使能<br>外部接口数据线 22  | GPIO57<br>SPISTEA<br>XD22  |

| 12 | 通用输入/输出 5<br>增强型 PWM3 输出 B<br>McBSP-B 接收帧同步<br>增强型捕捉输入输出 1             | GPIO5<br>EPWM3B<br>MFSRA<br>ECAP1            | 100 | 通用输入/输出 58<br>McBSP-A 接收时钟<br>外部接口数据线 21 | GPIO58<br>MCLKRA<br>XD21   |

| 13 | 通用输入/输出 6<br>增强型 PWM4 输出 A 和<br>HRPWM 通道<br>ePWM 同步脉冲输入<br>ePWM 同步脉冲输出 | GPIO6<br>EPWM4A<br>EPWMSYNC<br>I<br>EPWMSNCO | 101 | 内核与数字逻辑电源                                | V <sub>DD</sub>            |

| 14 | 数字逻辑地引脚                                                                | V <sub>ss</sub>                              | 102 | 内部振荡器输出                                  | X2                         |

| 15 | 内核与数字逻辑电源                                                              | V <sub>DD</sub>                              | 103 | 数字逻辑地引脚                                  | V <sub>ss</sub>            |

| 16 | 通用输入/输出 7<br>增强 PWM4 输出 B<br>McBSP-B 接收时钟<br>增强型捕捉输入输出 2               | GPIO7<br>EPWM4B<br>MCLKRA<br>ECAP2           | 104 | 内部振荡器输入                                  | X1                         |

| 17 | 通用输入/输出 8<br>增强型 PWM5 输出 A 和<br>HRPWM 通道<br>增强型 CAN-B 传输<br>ADC 转换启动 A | GPIO8<br>EPWM5A<br>CANTXB<br>ADCSOCDAO       | 105 | 外部振荡器输入                                  | XCLKIN                     |

| 18 | 通用输入/输出 9<br>增强型 PWM5 输出 B<br>SCI-B 发送数据                               | GPIO9<br>EPWM5B<br>SCITXDB                   | 106 | 数字逻辑地引脚                                  | V <sub>ss</sub>            |

|    |                                                                         |                                          |     |                                               |                           |

|----|-------------------------------------------------------------------------|------------------------------------------|-----|-----------------------------------------------|---------------------------|

|    | 增强型捕捉输入/输出 3                                                            | ECAP3                                    |     |                                               |                           |

| 19 | 通用输入/输出 10<br>增强型 PWM6 输出 A 和<br>HRPWM 通道<br>增强型 CAN-B 接收<br>ADC 转换启动 B | GPIO10<br>EPWM6A<br>CANRXB<br>ADCSOCBO   | 107 | 数字 I/O 电源                                     | V <sub>DDIO</sub>         |

| 20 | 通用输入/输出 11<br>增强型 PWM6 输出 B<br>SCI-B 接收数据<br>增强型捕捉输入/输出 4               | GPIO11<br>EPWM6B<br>SCIRXDB<br>ECAP4     | 108 | 数字逻辑地引脚                                       | V <sub>ss</sub>           |

| 21 | 通用输入/输出 12<br>触发区输入 1<br>增强型 CAN-B 传输<br>McBSP-B 串行数据传输                 | GPIO12<br>TZ1<br>CANTXB<br>MDXB          | 109 | 内核与数字逻辑电<br>源                                 | V <sub>DD</sub>           |

| 22 | 数字逻辑地引脚                                                                 | V <sub>ss</sub>                          | 110 | 通用输入/输出 59<br>McBSP-A 接收帧同<br>步<br>外部接口数据线 20 | GPIO59<br>MFSRA<br>XD20   |

| 23 | 内核与数字逻辑电源                                                               | V <sub>DD</sub>                          | 111 | 通用输入/输出 60<br>McBSP-B 接收时钟<br>外部接口数据线 19      | GPIO60<br>MCLKRB<br>XD19  |

| 24 | 通用输入/输出 13<br>触发区输入 2<br>增强型 CAN-B 接收<br>McBSP-B 串行数据接收                 | GPIO13<br>TZ2<br>CANRXB<br>MDRB          | 112 | 通用输入/输出 61<br>McBSP-B 接收帧同<br>步<br>外部接口数据线 18 | GPIO61<br>MFSRB<br>XD18   |

| 25 | 通用输入/输出 14<br>触发区输入 3/外部保持<br>请求<br>SCI-B 传输<br>McBSP-B 传输时钟            | GPIO14<br>TZ3/XHOLD<br>SCITXDB<br>MCLKXB | 113 | 通用输入/输出 62<br>SCI-C 接收数据<br>外部接口数据线 17        | GPIO62<br>SCIRXDC<br>XD17 |

| 26 | 通用输入/输出 15<br>触发区输入 4/外部保持<br>确<br>SCI-B 接收<br>McBSP-B 传输帧同步            | GPIO15<br>TZ3/XHOLDA<br>SCIRXDB<br>MFSXB | 114 | 通用输入/输出 63<br>SCI-C 发送数据<br>外部接口数据线 16        | GPIO63<br>SCITXDC<br>XD16 |

| 27 | 通用输入/输出 16                                                              | GPIO16                                   | 115 | 通用输入/输出 64                                    | GPIO64                    |

|    |                                                        |                                                |     |                          |                   |

|----|--------------------------------------------------------|------------------------------------------------|-----|--------------------------|-------------------|

|    | SPI 从输入/主输出<br>增强型 CAN-B 发送<br>触发区输入 5                 | SPISIMOA<br>CANTXB<br><br><u>TZ5</u>           |     | 外部接口数据线 15               | XD15              |

| 28 | 通用输入/输出 17<br>SPI-A 从输出/主输入<br>增强型 CAN-B 接收<br>触发区输入 6 | GPIO17<br>SPISOMIA<br>CANRXB<br><br><u>TZ6</u> | 116 | 通用输入/输出 65<br>外部接口数据线 14 | GPIO65<br>XD14    |

| 29 | 内核与数字逻辑电源                                              | V <sub>DD</sub>                                | 117 | 内核与数字逻辑电源                | V <sub>DD</sub>   |

| 30 | 数字逻辑地引脚                                                | V <sub>SS</sub>                                | 118 | 数字逻辑地引脚                  | V <sub>SS</sub>   |

| 31 | ADC 模拟低电源引脚 1                                          | V <sub>DD1A18</sub>                            | 119 | 通用输入/输出 66<br>外部接口数据线 13 | GPIO66<br>XD13    |

| 32 | ADC 模拟地引脚                                              | V <sub>SS1AGND</sub>                           | 120 | 数字逻辑地引脚                  | V <sub>SS</sub>   |

| 33 | ADC 模拟地引脚                                              | V <sub>SSA2</sub>                              | 121 | 数字 I/O 电源                | V <sub>DDIO</sub> |

| 34 | ADC 模拟高电源引脚                                            | V <sub>DDA2</sub>                              | 122 | 通用输入/输出 67<br>外部接口数据线 12 | GPIO67<br>XD12    |

| 35 | ADC 组 A, 通道 7 输入                                       | ADCINA7                                        | 123 | 通用输入/输出 68<br>外部接口数据线 11 | GPIO68<br>XD11    |

| 36 | ADC 组 A, 通道 6 输入                                       | ADCINA6                                        | 124 | 通用输入/输出 69<br>外部接口数据线 10 | GPIO69<br>XD10    |

| 37 | ADC 组 A, 通道 5 输入                                       | ADCINA5                                        | 125 | 数字逻辑地引脚                  | V <sub>SS</sub>   |

| 38 | ADC 组 A, 通道 4 输入                                       | ADCINA4                                        | 126 | 内核与数字逻辑电源                | V <sub>DD</sub>   |

| 39 | ADC 组 A, 通道 3 输入                                       | ADCINA3                                        | 127 | 通用输入/输出 70<br>外部接口数据线 9  | GPIO70<br>XD9     |

| 40 | ADC 组 A, 通道 2 输入                                       | ADCINA2                                        | 128 | 通用输入/输出 71<br>外部接口数据线 8  | GPIO71<br>XD8     |

| 41 | ADC 组 A, 通道 1 输入                                       | ADCINA1                                        | 129 | 通用输入/输出 72<br>外部接口数据线 7  | GPIO72<br>XD7     |

| 42 | ADC 组 A, 通道 0 输入                                       | ADCINA0                                        | 130 | 通用输入/输出 73<br>外部接口数据线 6  | GPIO73<br>XD6     |

| 43 | ADC 基准 0 电平                                            | ADCLO                                          | 131 | 通用输入/输出 74<br>外部接口数据线 5  | GPIO74<br>XD5     |

| 44 | ADC 模拟 IO 地引脚                                          | V <sub>SSAIO</sub>                             | 132 | 通用输入/输出 75<br>外部接口数据线 4  | GPIO75<br>XD4     |

| 45 | ADC 模拟 IO 电源引脚                                         | V <sub>DDAIO</sub>                             | 133 | 通用输入/输出 76               | GPIO76            |

|    |                                  |                      |     |                                        |                                   |

|----|----------------------------------|----------------------|-----|----------------------------------------|-----------------------------------|

|    |                                  |                      |     | 外部接口数据线 3                              | XD3                               |

| 46 | ADC 组 B, 通道 0 输入                 | ADCINB0              | 134 | 通用输入/输出 77<br>外部接口数据线 2                | GPIO77<br>XD2                     |

| 47 | ADC 组 B, 通道 1 输入                 | ADCINB1              | 135 | 通用输入/输出 78<br>外部接口数据线 1                | GPIO78<br>XD1                     |

| 48 | ADC 组 B, 通道 2 输入                 | ADCINB2              | 136 | 通用输入/输出 79<br>外部接口数据线 0                | GPIO79<br>XD0                     |

| 49 | ADC 组 B, 通道 3 输入                 | ADCINB3              | 137 | 通用输入/输出 38<br>外部接口写入使能 0               | GPIO38<br><u>XWE0</u>             |

| 50 | ADC 组 B, 通道 4 输入                 | ADCINB4              | 138 | SYSCLKOUT 的输出时钟                        | XCLKOUT                           |

| 51 | ADC 组 B, 通道 5 输入                 | ADCINB5              | 139 | 内核与数字逻辑电源                              | V <sub>DD</sub>                   |

| 52 | ADC 组 B, 通道 6 输入                 | ADCINB6              | 140 | 数字逻辑地引脚                                | V <sub>SS</sub>                   |

| 53 | ADC 组 B, 通道 7 输入                 | ADCINB7              | 141 | 通用输入/输出 28<br>SCI 接收数据<br>外部接口 6 芯片选择  | GPIO28<br>SCIRXDA<br><u>XZCS6</u> |

| 54 | ADC 外部基准输入                       | ADCREFIN             | 142 | 通用输入/输出 34<br>增强型捕捉输入/输出 1<br>外部接口就绪信号 | GPIO34<br>ECAP1<br>XREADY         |

| 55 | ADC 内部基准中输出                      | ADCREFM              | 143 | 数字 I/O 电源                              | V <sub>DDIO</sub>                 |

| 56 | ADC 内部基准正输出                      | ADCREFP              | 144 | 数字逻辑地引脚                                | V <sub>SS</sub>                   |

| 57 | ADC 电流偏置外接电阻管脚, 接 22kΩ 精确电阻至模拟地。 | ADCRESEX<br>T        | 145 | 通用输入/输出 36<br>SCI 接收数据<br>外部接口 0 区芯片选择 | GPIO36<br>SCIRXDA<br><u>XZCS0</u> |

| 58 | ADC 模拟地引脚                        | V <sub>SS2AGND</sub> | 146 | 内核与数字逻辑电源                              | V <sub>DD</sub>                   |

| 59 | ADC 模拟低电源引脚 2                    | V <sub>DD2A18</sub>  | 147 | 数字逻辑地引脚                                | V <sub>SS</sub>                   |

| 60 | 数字逻辑地引脚                          | V <sub>SS</sub>      | 148 | 通用输入/输出 35<br>SCI 传输数据<br>外部接口读取       | GPIO35<br>SCITXDA<br><u>XR/W</u>  |

| 61 | 内核与数字逻辑电源                        | V <sub>DD</sub>      | 149 | 外部接口读取使能                               | <u>XRD</u>                        |

|    |                                                               |                                        |     |                                            |                          |

|----|---------------------------------------------------------------|----------------------------------------|-----|--------------------------------------------|--------------------------|

| 62 | 通用输入/输出 18<br>SPI-A 时钟输入/输出<br>SCI-B 传输<br>增强型 CAN-A 接收       | GPIO18<br>SPICLKA<br>SCITXDB<br>CANRXA | 150 | 通用输入/输出 37<br>增强型捕获输入/输出 2<br>外部接口 7 区芯片选择 | GPIO37<br>ECAP2<br>XZCS7 |

| 63 | 通用输入/输出 19<br>SPI-A 从器件发送使能<br>SCI-B 接收<br>增强型 CAN-A 传输       | GPIO19<br>SPISTEA<br>SCIRXDB<br>CANTXA | 151 | 通用输入/输出 40<br>外部接口地址线路 0/外部接口写入使能 1        | GPIO40<br>XA0/XWE1       |

| 64 | 通用输入/输出 20<br>增强型 QEP1 输入 A<br>McBSP-A 串行数据传输<br>增强型 CAN-B 传输 | GPIO20<br>EQEP1A<br>MDXA<br>CANTXB     | 152 | 通用输入/输出 41<br>外部接口地址线 1                    | GPIO41<br>XA1            |

| 65 | 通用输入/输出 21<br>增强型 QEP1 输入 B<br>McBSP-A 串行数据接收<br>增强型 CAN-B 接收 | GPIO21<br>EQEP1B<br>MDRA<br>CANRXB     | 153 | 通用输入/输出 42<br>外部接口地址线 2                    | GPIO42<br>XA2            |

| 66 | 通用输入/输出 22<br>增强型 QEP1 选通脉冲<br>McBSP-A 传输时钟<br>SCI-B 传输       | GPIO22<br>EQEP1S<br>MCLKXA<br>SCITXDB  | 154 | 内核与数字逻辑电源                                  | V <sub>DD</sub>          |

| 67 | 通用输入/输出 23<br>增强型 QEP1 索引<br>McBSP-A 传输帧同步<br>SCI-B 接收        | GPIO23<br>EQEP1I<br>MFSXA<br>CIRXDB    | 155 | 数字逻辑地引脚                                    | V <sub>SS</sub>          |

| 68 | 通用输入/输出 24<br>增强型捕获 1<br>增强型 QEP2 输入 A<br>McBSP-B 串行数据传输      | GPIO24<br>ECAP1<br>EQEP2A<br>MDXB      | 156 | 通用输入/输出 43<br>外部接口地址线 3                    | GPIO43<br>XA3            |

| 69 | 通用输入/输出 25<br>增强型捕获 2<br>增强型 QEP2 输入 B<br>McBSP-B 串行数据接收      | GPIO25<br>ECAP2<br>EQEP2B<br>MDRB      | 157 | 通用输入/输出 44<br>外部接口地址线 4                    | GPIO44<br>XA4            |

| 70 | 数字逻辑地引脚                                                       | V <sub>SS</sub>                        | 158 | 通用输入/输出 45<br>外部接口地址线路 5                   | GPIO45<br>XA5            |

| 71 | 数字 I/O 电源                                                     | V <sub>DDIO</sub>                      | 159 | 数字 I/O 电源                                  | V <sub>DDIO</sub>        |

|    |                                                                 |                                             |     |                          |                   |

|----|-----------------------------------------------------------------|---------------------------------------------|-----|--------------------------|-------------------|

| 72 | 通用输入/输出 26<br>增强型捕获 3<br>增强型 QEP2 索引<br>McBSP-B 传输时钟            | GPIO26<br>ECAP3<br>EQEP2I<br>MCLKXB         | 160 | 数字逻辑地引脚                  | V <sub>ss</sub>   |

| 73 | 通用输入/输出 27<br>增强型捕获 4<br>增强型 QEP2 选通脉冲<br>McBSP-B 传输帧同步         | GPIO27<br>ECAP4<br>EQEP2S<br>MFSXB          | 161 | 通用输入/输出 46<br>外部接口地址线路 6 | GPIO46<br>XA6     |

| 74 | 通用输入/输出 32<br>I2C 数据开漏双向端口<br>增强型 PWM 同步脉冲<br>输入<br>ADC 转换启动 A  | GPIO32<br>SDAA<br>EPWMSYNC<br>I<br>ADCSOCAO | 162 | 通用输入/输出 47<br>外部接口地址线路 7 | GPIO47<br>XA7     |

| 75 | 通用输入/输出 33<br>I2C 时钟开漏双向端口)<br>增强型 PWM 同步脉冲<br>输出<br>ADC 转换启动 B | GPIO33<br>SCLA<br>EPWMSYNC<br>O<br>ADCSOCBO | 163 | 通用输入/输出 80<br>外部接口地址线 8  | GPIO80<br>XA8     |

| 76 | JTAG 测试数据输入                                                     | TDI                                         | 164 | 通用输入/输出 81<br>外部接口地址线 9  | GPIO81<br>XA9     |

| 77 | JTAG 测试数据输出                                                     | TDO                                         | 165 | 通用输入/输出 82<br>外部接口地址线 10 | GPIO82<br>XA10    |

| 78 | JTAG 测试复位                                                       | TRST                                        | 166 | 数字逻辑地引脚                  | V <sub>ss</sub>   |

| 79 | JTAG 测试模式选择                                                     | TMS                                         | 167 | 内核与数字逻辑电<br>源            | V <sub>DD</sub>   |

| 80 | 器件复位输入和安全装<br>置复位输出                                             | XRS                                         | 168 | 通用输入/输出 83<br>外部接口地址线 11 | GPIO83<br>XA11    |

| 81 | 测试引脚 1                                                          | TEST1                                       | 169 | 通用输入/输出 84<br>外部接口地址线 12 | GPIO84<br>XA12    |

| 82 | 测试引脚 2                                                          | TEST2                                       | 170 | 数字 I/O 电源                | V <sub>DDIO</sub> |

| 83 | 数字逻辑地引脚                                                         | V <sub>ss</sub>                             | 171 | 数字逻辑地引脚                  | V <sub>ss</sub>   |

| 84 | 测试引脚 3                                                          | TEST3                                       | 172 | 通用输入/输出 85<br>外部接口地址线 13 | GPIO85<br>XA13    |

| 85 | 仿真器引脚 0                                                         | EMU0                                        | 173 | 通用输入/输出 86<br>外部接口地址线 14 | GPIO86<br>XA14    |

|    |                                          |                         |     |                                          |                          |

|----|------------------------------------------|-------------------------|-----|------------------------------------------|--------------------------|

| 86 | 仿真器引脚 1                                  | EMU1                    | 174 | 通用输入/输出 87<br>外部接口地址线路 15                | GPIO87<br>XA15           |

| 87 | JTAG 测试时钟                                | TCK                     | 175 | 通用输入/输出 39<br>外部接口地址线 16                 | GPIO39<br>XA16           |

| 88 | 通用输入/输出 48<br>增强型捕捉输入/输出 5<br>外部接口数据线 31 | GPIO48<br>ECAP5<br>XD31 | 176 | 通用输入/输出 31<br>增强型 CAN-A 传输<br>外部接口地址线 17 | GPIO31<br>CANTXA<br>XA17 |

| -  | -                                        | -                       | -   | 数字 I/O 电源                                | V <sub>DDIO</sub>        |

## 4. 设备详细描述

### 4.1. FDM320RV335 处理器核

FDM320RV335 处理器核是嵌入式领域的 RISC-V 兼容的高能效、低成本 32 位处理器。FDM320RV335 采用 RV32IMFC-Ext 指令集架构，主要面向数字电源、电机控制等高性能实时信号处理领域。FDM320RV335 处理器核的主要特征有：

- 1) RISC-V 架构。

- 2) 支持整型、定点计算类型。

- 3) 支持 32-bit 单精度数据类型。

- 4) 支持 32 个整型 X0-X31 通用寄存器。

- 5) 支持 32 个浮点 F0-F31 通用寄存器。

- 6) 硬件 RAW 和 WAR 相关判断。

- 7) 支持 RISC-V Debug 0.13.2 调试标准，可以进行设置断点、单步等操作。

- 8) 定制化指令加速关键性能路径。

- 9) 快速切换上下文进行实时处理加速。

- 10) 16 位压缩指令。

独立的存储空间：

- 1) 私有的快速程序空间 PMEM 和数据空间 DMEM。

- 2) 外部 master 可进行 DMEM 的初始化。

- 3) 32 位地址可寻址空间。

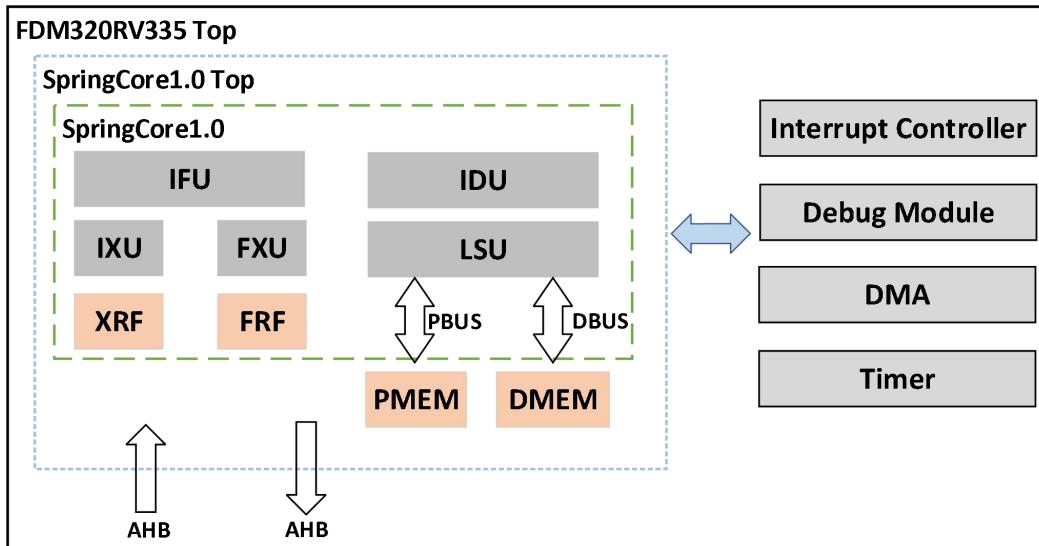

FDM320RV335 处理器 DSP 子系统的结构框图如下所示：

图 4-1 FDM320RV335 子系统框图

FDM320RV335 DSP 包括取指单元、译码单元、存储访问单元、跳转控制单元、整型处理单元和浮点处理单元，以及两类寄存器堆，X Regfile 和 F Regfile，分别用来进行整型和浮点型运算。各模块的含义及功能包括：

- 1) IFU: Instruction Fetch Unit, 负责指令的取指，包括外部输入的中断和分支指令的影响处理，也包括 Core 的异常处理以及流水线前端处理。

- 2) IDU: Instruction Decode Unit, 负责指令的译码以及指令到各个功能单元的分发。

- 3) IXU: Integer Execution Unit, 负责整型/定点类型的 ALU 计算。

- 4) FXU: Float Execution Unit, 负责单精度浮点类型的 ALU 计算。

- 5) LSU: Load Store Unit, 负责 memory 的存取操作，地址计算等。

- 6) XRF: X Register File, X 寄存器堆，存放整型数据。

- 7) FRF: F Register File, F 寄存器堆，存放浮点类型数据。

- 8) PMEM: Program Memory, 程序存储器。

- 9) DMEM: Data Memory, 数据存储器。

#### 4.1.1. 指令集

FDM320RV335 DSP 采用 RV32IMFC-Ext 指令集架构，详细描述参考《FDM320RV335 指令集参考手册》。

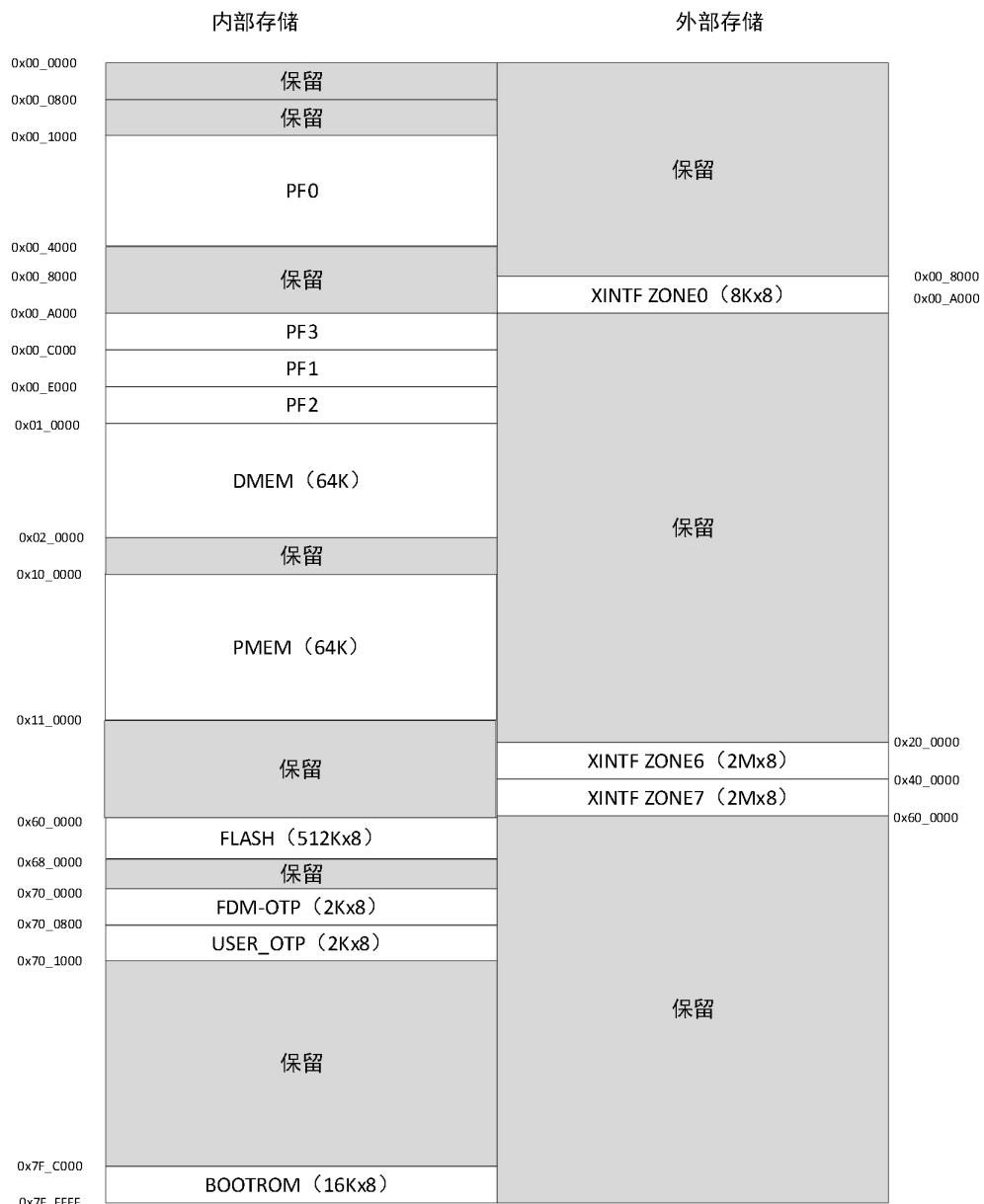

### 4.1.2. 地址映射

如图 4-2，整个芯片的地址空间是 0x00\_0000~0x7F\_FFFF，每个地址对应 8 位数据。图中的保留区，对保留区的访问为无效访问。

图 4-2 地址映射

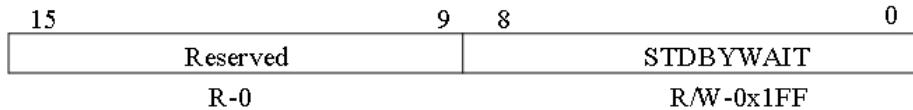

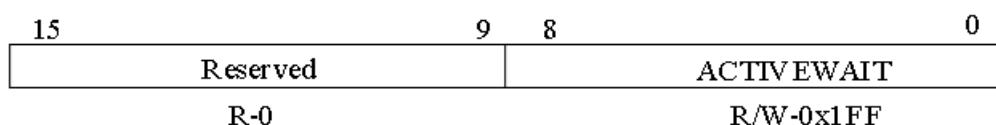

### 4.2. 系统控制

这个部分描述了振荡器、锁相环和计时机制、安全装置功能和低功耗模式。图 4-3 列出了将要讨论的各种时钟和复位域。

图 4-3 时钟与复位域

从写入 PCLKCR0, PCLKCR1 和 PCLKCR2 寄存器（启用外设时钟）发生到操作有效，有两个 SYSLKOUT 周期延迟。在尝试访问外围设备配置寄存器前，必须把该延迟考虑在内。

PLL, 计时, 安全装置和低功耗模式由表 4-1 中列出的寄存器控制。

表 4-1 PLL, 时钟, 安全装置, 和低功耗模式寄存器

| 名称 | 地址 | 大小(字节) | 说明 |

|----|----|--------|----|

|----|----|--------|----|

|         |                     |    |                    |

|---------|---------------------|----|--------------------|

| PLLSTS  | 0x00 E022-0x00 E023 | 2  | PLL 状态寄存器          |

| 保留      | 0x00 E024-0x00 E031 | 14 | 保留                 |

| 保留      | 0x00 E032-0x00 E033 | 2  | 保留                 |

| HISPCP  | 0x00 E034-0x00 E035 | 2  | 高速外设时钟预分频寄存器       |

| LOSPCP  | 0x00 E036-0x00 E037 | 2  | 低速外设时钟预分频寄存器       |

| PCLKCR0 | 0x00 E038-0x00 E039 | 2  | 外设时钟控制寄存器 0        |

| PCLKCR1 | 0x00 E03A-0x00 E03B | 2  | 外设时钟控制寄存器 1        |

| LPMCR0  | 0x00 E03C-0x00 E03D | 2  | 低功耗模式控制寄存器 0       |

| 保留      | 0x00 E03E-0x00 E03F | 2  | 保留                 |

| PCLKCR3 | 0x00 E040-0x00 E041 | 2  | 外设时钟控制寄存器 3        |

| PLLCR   | 0x00 E042-0x00 E043 | 2  | PLL 控制寄存器          |

| SCSR    | 0x00 E044-0x00 E045 | 2  | 系统控制与状态寄存器         |

| WDCNTR  | 0x00 E046-0x00 E047 | 2  | 安全装置计数器寄存器         |

| 保留      | 0x00 E048-0x00 E049 | 2  | 保留                 |

| WDKEY   | 0x00 E04A-0x00 E04B | 2  | 安全装置复位密钥寄存器        |

| 保留      | 0x00 E04C-0x00 E051 | 6  | 保留                 |

| WDCR    | 0x00 E052-0x00 E053 | 2  | 安全装置控制寄存器          |

| 保留      | 0x00 E054-0x00 E05B | 8  | 保留                 |

| MAPCNF  | 0x00 E05C-0x00 E05D | 2  | EPWM/HRPWM 重新映射寄存器 |

#### 4.2.1. 振荡器和锁相环模块

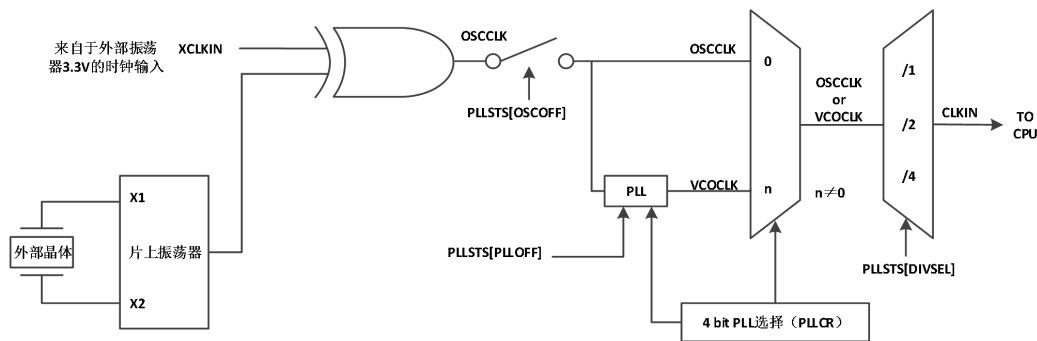

图 4-4 显示了 OSC 和 PLL 块

图 4-4 OSC 和 PLL 模块方框图

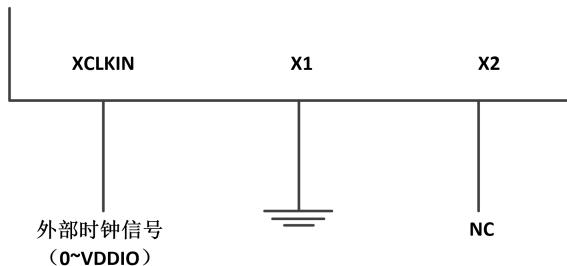

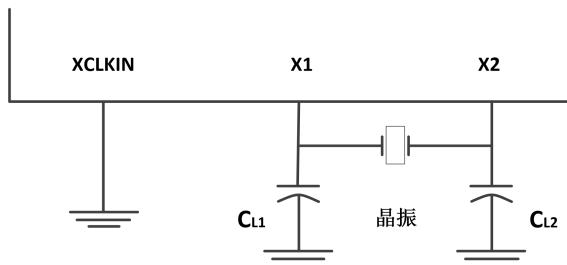

片载振荡器电路启用一个使用 X1 和 X2 引脚连接至 RV335 器件的晶振/谐振器。如果片载振荡器未被使用，那么一个外部振荡器可被用在下列配置中：

一个 3.3V 外部振荡器可被直接接至 XCLKIN 引脚。X2 引脚应被悬空，而 X1 引脚应在低电平时。这个情况下的逻辑高电平不用超过 VDDIO。

图 4-5 和图 4-6 显示了这两个可能的输入时钟配置。

图 4-5 使用一个 3.3V 外部振荡器

图 4-6 使用内部振荡器

30MHz 外部石英晶振的典型技术规范如下：

- 基本模式、并联谐振

- $CL(\text{负载电容})=12\text{pF}$

- $CL1=CL2=24\text{pF}$

- $C\text{并联}=6\text{pF}$

- ESR 范围 = 25 至  $40\Omega$

基于 PLL 的时钟模块为器件提供所有需要的时钟信号，以及对低功耗模式进入的控制。PLL 有一个 4 位比率控制 PLLCR[DIV] 来选择不同的 DSP 时钟速率。在写入 PLLCR 寄存器之前，安全装置模块应该被禁用。在 PLL 模式稳定后，它可被重新启用(如果需要的话)，重新启用的时间为 131072 个 OSCCLK 周期。输入时钟和 PLLCR[DIV] 位应该在 PLL (VCOCLK) 的输出频率不超过 300MHz 时候选择。

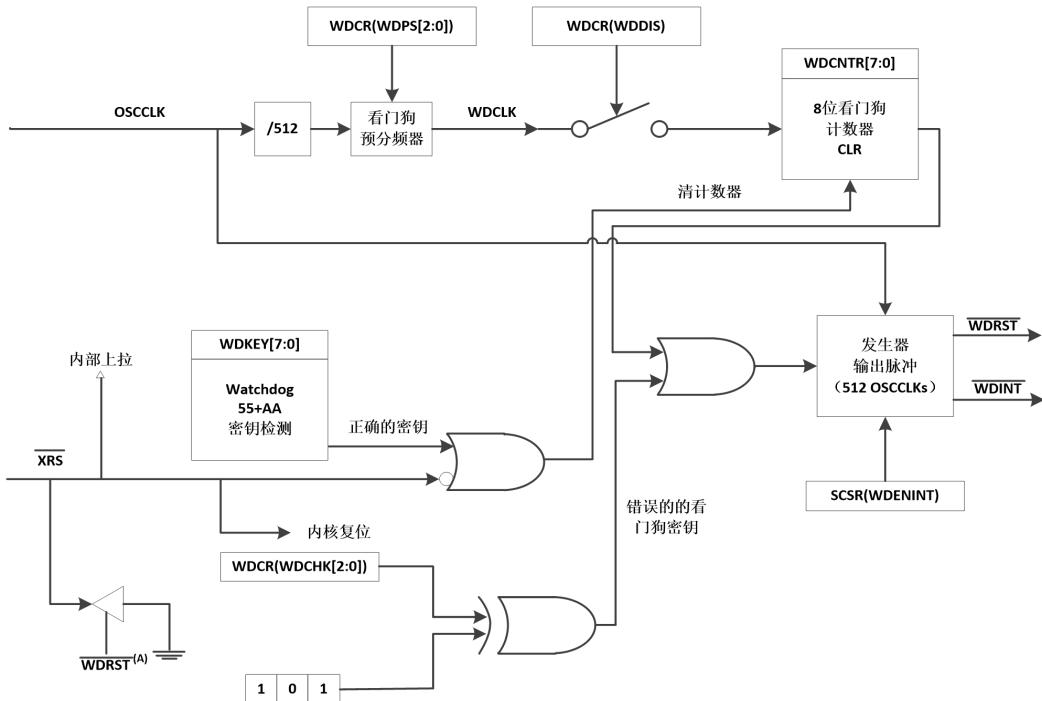

#### 4.2.2. 看门狗模块

RV335 的看门狗模块功能是：只要 8 位看门狗计数器达到了它的最大值，这个看门狗模块就生成一个输出脉冲，512 振荡器时钟宽度(OSCCLK)。要防止这

种情况，用户可以禁用该计数器，或者必须通过软件定期将一个 0x55+0xAA 序列写入至看门狗寄存器中，从而使看门狗计数器复位。

图 4-7 显示了看门狗模块内的各种功能块。

图 4-7 安全装置模块

WDINT 信号使得看门狗模块可被用作一个从 IDEL/STANDY 模式的唤醒。

在 STANDBY 模式中，器件上的所有外设关闭。继续工作的唯一外设是看门狗模块。WATCHDOG 模块将关闭 OSCCLK。WDINT 信号被馈送到 LPM 块以便它可以将器件从 STANDBY 唤醒(如已启用)。

在 IDLE 模式中，WDINT 信号通过生成一个到 DSP 的中断来将 DSP 从 IDEL 模式中唤醒。在 HALT 模式中，不能使用此功能，这是因为振荡器(和 PLL)关闭，因此看门狗模块也关闭。

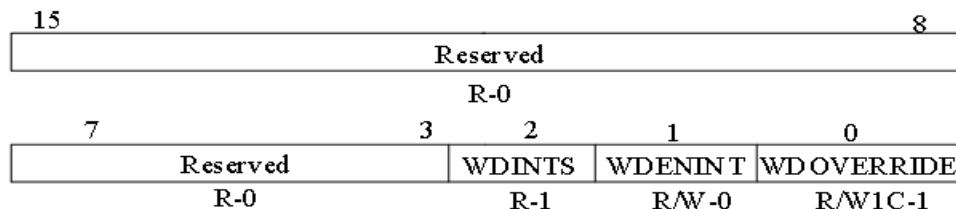

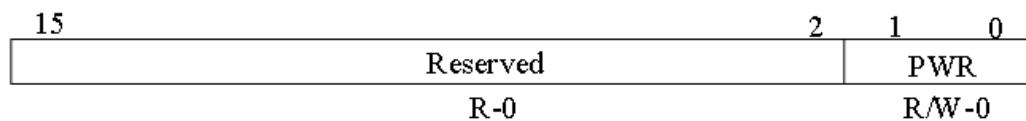

图 4-8 系统控制和状态寄存器 (SCSR)

图例: R/W=读/写; R=只读; -n=重置后的值

表 4-2 系统控制和状态寄存器 (SCSR) 字段说明

| 位域   | 字段         | 值   | 描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-3 | Reserved   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2    | WDINTS     | 0/1 | <p>看门狗中断状态位。WDINTS 反映来自看门狗块的 <math>\overline{\text{WDINT}}</math> 信号的当前状态。WDINTS 跟随 <math>\overline{\text{WDINT}}</math> 的状态两个 <math>\text{SYSCLKOUT}</math> 周期。如果看门狗中断用于将设备从 IDLE (空闲) 或 STANDBY (待机) 低功率模式唤醒, 则在尝试返回 IDLE (待机) 或 STANDBY (待机) 模式之前, 使用此位确保 <math>\overline{\text{WDINT}}</math> 未激活。</p> <p>0 表示看门狗中断信号 (<math>\overline{\text{WDINT}}</math>) 处于激活状态。</p> <p>1 表示看门狗中断信号 (<math>\overline{\text{WDINT}}</math>) 未激活。</p>                                                                                                                                                                                                                                                                                                             |

| 1    | WDENINT    | 0/1 | <p>看门狗中断启用。</p> <p>0 表示看门狗复位 (<math>\overline{\text{WDRST}}</math>) 输出信号被启用, 看门狗中断 (<math>\overline{\text{WDINT}}</math>) 的输出信号被禁用。这是重置时的默认状态 (<math>\overline{\text{XRS}}</math>)。当看门狗中断发生时, <math>\overline{\text{WDRST}}</math> 信号将在 512 个 <math>\text{OSCCLK}</math> 周期内保持低电平。如果 WDENINT 位在 <math>\overline{\text{WDINT}}</math> 为低电平时被清除, 则将立即发生复位。WDINTS 位可以被读取以确定 <math>\overline{\text{WDINT}}</math> 信号的状态。</p> <p>1 表示禁用 <math>\overline{\text{WDRST}}</math> 输出信号, 启用 <math>\overline{\text{WDINT}}</math> 输出信号。当看门狗中断发生时, <math>\overline{\text{WDINT}}</math> 信号将在 512 个 <math>\text{OSCCLK}</math> 周期内保持低电平。如果看门狗中断用于将设备从 IDLE 或 STANDBY 低功率模式唤醒, 请使用 WDINTS 位确保 <math>\overline{\text{WDINT}}</math> 未激活, 然后再尝试返回 IDLE 或 STANDBY 模式。</p> |

| 0    | WDOVERRIDE | 0/1 | <p>看门狗重写。</p> <p>0 表示写入 0 无效。如果此位被清除, 它将保持此状态, 直到发生重置。该位的当前状态可由用户读取。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|  |  |                                                                                       |

|--|--|---------------------------------------------------------------------------------------|

|  |  | 1 表示您可以更改看门狗控制 (WDCR) 寄存器中看门狗禁用 (WDDIS) 位的状态。如果通过写入 1 来清除 WDOVERRIDE 位，则不能修改 WDDIS 位。 |

|--|--|---------------------------------------------------------------------------------------|

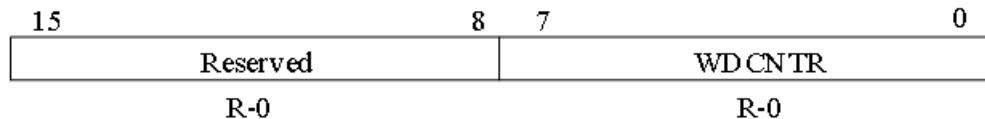

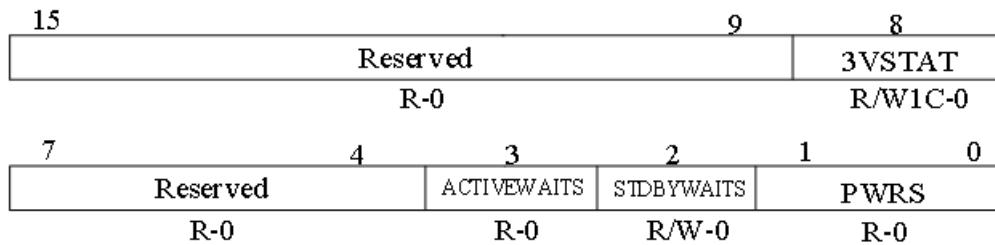

图 4-9 看门狗计数器寄存器 (WDCNTR)

表 4-3 看门狗计数器寄存器 (WDCNTR) 字段说明

| 位域   | 字段       | 描述                                                                                                                  |

|------|----------|---------------------------------------------------------------------------------------------------------------------|

| 15-8 | Reserved | 保留的                                                                                                                 |

| 7-0  | WDCNTR   | 这些位包含 WD 计数器的当前值。8 位计数器以看门狗时钟 (WDCLK) 的速率连续递增。如果计数器溢出，则看门狗启动重置。如果使用有效组合写入 WDKEY 寄存器，则计数器将重置为零。看门狗时钟速率配置在 WDCR 寄存器中。 |

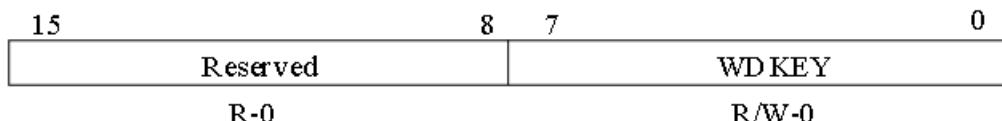

图 4-10 看门狗重置密钥寄存器 (WDKEY)

表 4-4 看门狗重置密钥寄存器 (WDKEY) 字段说明

| 位域   | 字段       | 值                | 描述                                                                                                                                             |

|------|----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-8 | Reserved |                  | 保留的                                                                                                                                            |

| 7-0  | WDKEY    | 0x55+0xAA<br>其他值 | 将 0x55 后 0xAA 写入 WDKEY 会导致 WDCNTR 位被清除。其他值写入 0x55 或 0xAA 以外的任何值都不会导致生成任何操作。如果在 0x55 之后写入 0xAA 以外的任何值，则序列必须以 0x55 重新启动。从 WDKEY 读取返回 WDCR 寄存器的值。 |

图 4-11 看门狗控制寄存器 (WDCR)

图例：R/W=读/写；R=只读；-n=重置后的值

表 4-5 看门狗控制寄存器 (WDCR) 字段说明

| 位域   | 字段       | 值                                      | 描述                                                                                                                                                                                                                                                                                 |

|------|----------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-8 | Reserved |                                        | 保留的                                                                                                                                                                                                                                                                                |

| 7    | WDFLAG   | 0/1                                    | <p>看门狗复位状态标志位 0 复位是由 <u>XRS</u> 引脚或通电引起的。该位保持锁存状态，直到您写入 1 以清除该条件。0 的写入被忽略。</p> <p>1 表示看门狗重置 (WDRST) 生成重置条件。</p>                                                                                                                                                                    |

| 6    | WDDIS    | 0/1                                    | <p>看门狗禁用。重置时，看门狗模块启用。</p> <p>0 启用看门狗模块。只有当 SCSR 寄存器中的 WDOVERRIDE 位设置为 1 时，才能修改 WDDIS。(默认)</p> <p>1 禁用看门狗模块。</p>                                                                                                                                                                    |

| 5-3  | WDCHK    | 0,0,0/其他                               | <p>看门狗检查。</p> <p>0,0,0 每当执行对此寄存器的写入时，您必须始终将 1,0,1 写入这些位，除非意图通过软件重置设备。</p> <p>其他写入任何其他值会导致立即进行设备重置或看门狗中断。请注意，即使看门狗模块被禁用，这种情况也会发生。这三个比特总是作为零 (0,0,0) 读回。此功能可用于生成 DSP 的软件重置。</p>                                                                                                      |

| 2-0  | WDPS     | 000/001010<br>/011/100/10<br>1/110/111 | <p>看门狗预分频，这些位配置相对于 OSCCLK\512 的看门狗计数器时钟 (WDCLK) 速率：</p> <p>000:WDCLK=OSCCLK/512/1 (默认)</p> <p>001: WDCLK=OSCCLK/512/2</p> <p>010:WDCLK=OSCCLK/512/4</p> <p>100:WDCLK=OSCCLK/512/8</p> <p>101:WDCLK=OSCCLK/512/16</p> <p>110:WDCLK=OSCCLK/512/32</p> <p>111:WDCLK=OSCCLK/512/64</p> |

### 4.3. 中断

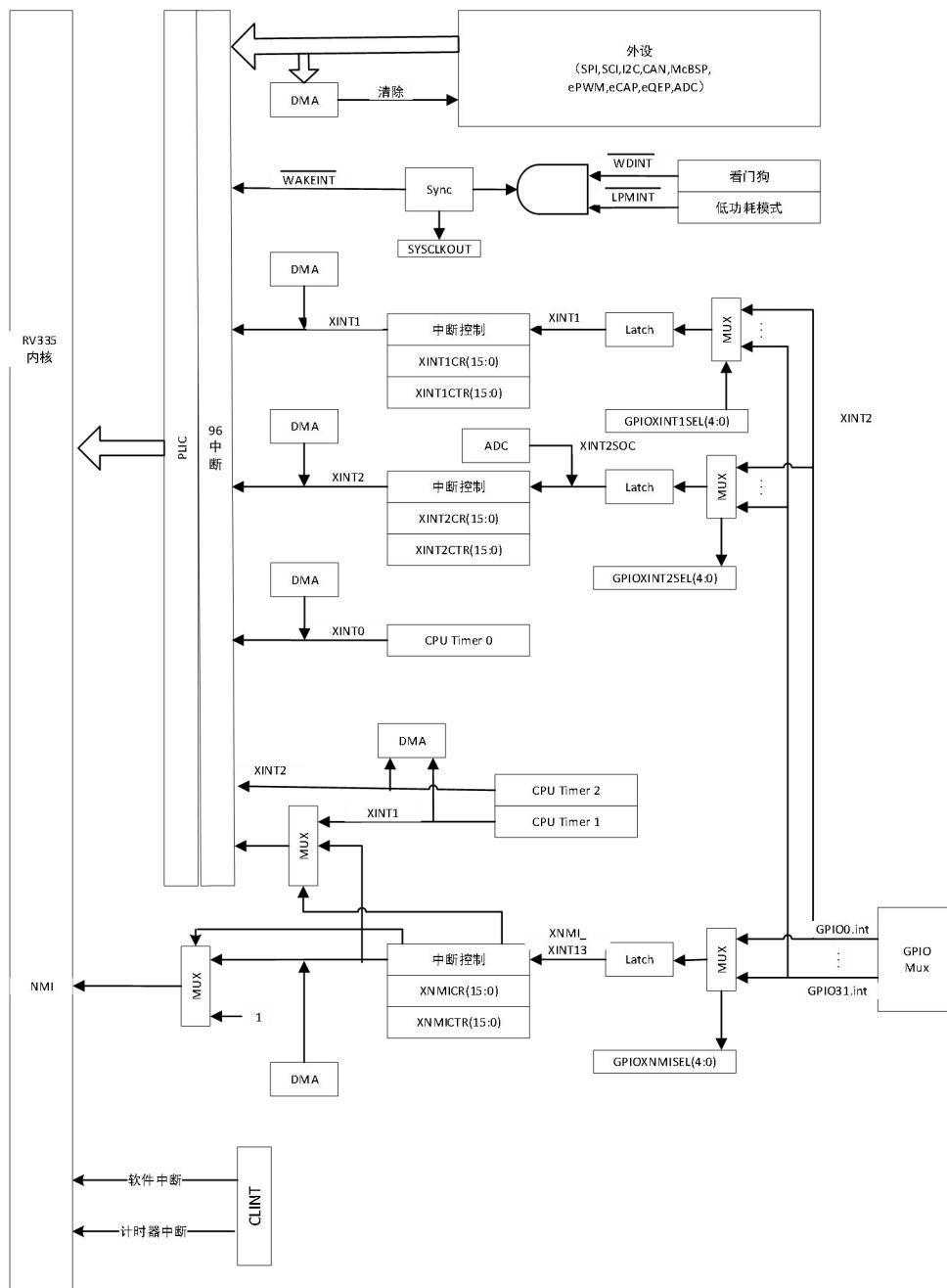

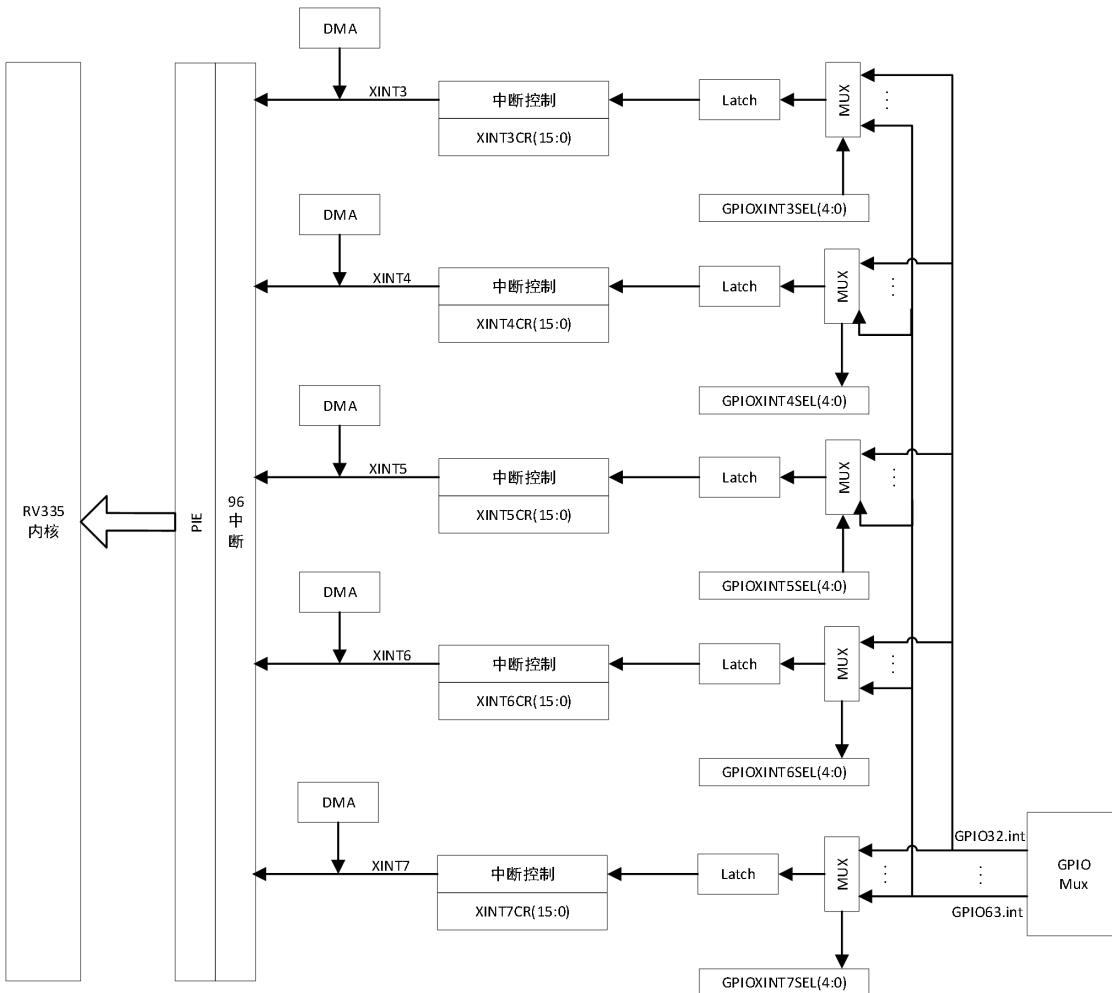

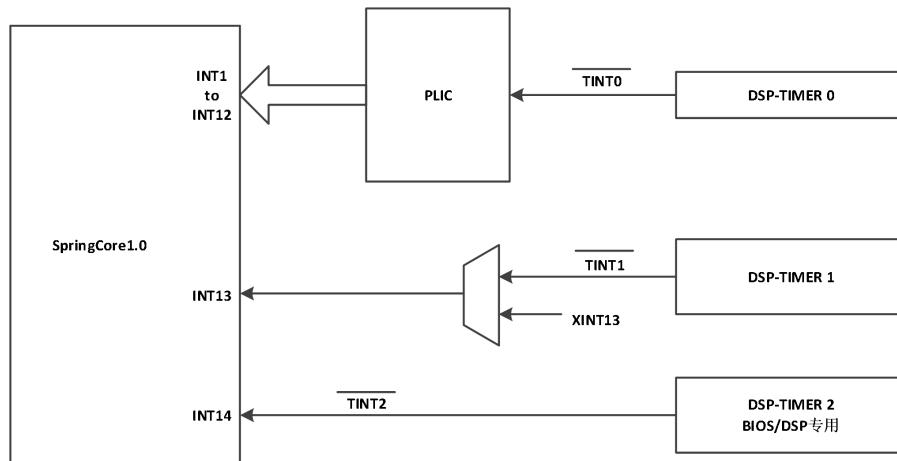

FDM320RV335 的中断控制模块实现处理器核局部中断控制器 (CLINT, Core Local Interrupt Controller)、平台级中断控制器 (PLIC, Platform Level Interrupt Controller)。图 4-12 显示了不同的中断源是如何被复用的。CLINT 模块产生一根软件中断信号和一根计时器中断信号，通给处理器核。PLIC 接入多个外部中断源将其仲裁后生成一根外部中断信号，通给处理器核。

图 4-12 外部和中断源

图 4-13 外部中断

CLINT 完成计时器中断和软件中断，实现了计时器中断和软件中断的产生。

寄存器映射表如表 4-6 所示。

表 4-6 CLINT 寄存器映射表

| 寄存器名称      | 描述                                        | 寄存器地址 (字节) |

|------------|-------------------------------------------|------------|

| MSIP0      | 机器模式软件中断配置寄存器, bit[31:1]固定为 0, bit[0] 有效。 | 0x000018B0 |

| MTIMECMP0  | 机器模式计时器比较值寄存器(低 32 位)                     | 0x000018B4 |

| MTIMECMPH0 | 机器模式计时器比较值寄存器(高 32 位)                     | 0x000018B8 |

| MTIME      | 机器模式计时器寄存器(低 32 位)                        | 0x000018BC |

| MTIMEH     | 机器模式计时器寄存器(高 32 位)                        | 0x000018C0 |

PLIC 是 RISC-V 架构标准定义的系统中断控制器，主要用于多个外部中断源的优先级仲裁和派发。PLIC 理论上最多可以支持 1024 外部中断源。在下表的 99 个可能中断中，目前使用 61 个中断，其余的中断被保留以供未来的设备使

用，其中 98 个中断由 PLIC 进行仲裁和派发，NMI 中断直接连到内核。

表 4-7 中断向量表

| 名字     | 触发方式    | 描述                  | 优先级 | ID |

|--------|---------|---------------------|-----|----|

| 组 1    |         |                     |     |    |

| INT1.1 | 电平触发    | SEQ1INT(ADC)        | 16  | 1  |

| INT1.2 | 电平触发    | SEQ2INT(ADC)        | 16  | 2  |

| INT1.3 |         | 保留                  | 16  | 3  |

| INT1.4 | 上升沿触发   | XINT1(Ext. Int. 1)  | 16  | 4  |

|        | 下降沿触发   |                     |     |    |

|        | 上升下降沿触发 |                     |     |    |

| INT1.5 | 上升沿触发   | XINT2(Ext. Int. 2)  | 16  | 5  |

|        | 下降沿触发   |                     |     |    |

|        | 上升下降沿触发 |                     |     |    |

| INT1.6 | 电平触发    | ADCINT (ADC)        | 16  | 6  |

| INT1.7 | 边沿触发    | TINT0(DSP-Timer0)   | 16  | 7  |

| INT1.8 | 边沿触发    | WAKEINT(LPM/WD)     | 16  | 8  |

| 组 2    |         |                     |     |    |

| INT2.1 | 边沿触发    | EPWM1_TZINT (ePWM1) | 15  | 9  |

| INT2.2 | 边沿触发    | EPWM2_TZINT(ePWM2)  | 15  | 10 |

| INT2.3 | 边沿触发    | EPWM3_TZINT(ePWM3)  | 15  | 11 |

| INT2.4 | 边沿触发    | EPWM4_TZINT(ePWM4)  | 15  | 12 |

| INT2.5 | 边沿触发    | EPWM5_TZINT(ePWM5)  | 15  | 13 |

| INT2.6 | 边沿触发    | EPWM6_TZINT(ePWM6)  | 15  | 14 |

| INT2.7 |         | 保留                  | 15  | 15 |

| INT2.8 |         | 保留                  | 15  | 16 |

| 组 3    |         |                     |     |    |

| INT3.1 | 边沿触发    | EPWM1_INT (ePWM1)   | 14  | 17 |

| INT3.2 | 边沿触发    | EPWM2_INT(ePWM2)    | 14  | 18 |

| INT3.3 | 边沿触发    | EPWM3_INT(ePWM3)    | 14  | 19 |

| INT3.4 | 边沿触发    | EPWM4_INT(ePWM4)    | 14  | 20 |

| INT3.5 | 边沿触发    | EPWM5_INT(ePWM5)    | 14  | 21 |

| INT3.6 | 边沿触发    | EPWM6_INT(ePWM6)    | 14  | 22 |

| INT3.7 |         | 保留                  | 14  | 23 |

| INT3.8 |         | 保留                  | 14  | 24 |

| 组 4    |         |                     |     |    |

|        |      |                  |    |    |

|--------|------|------------------|----|----|

| INT4.1 | 边沿触发 | ECAP1_INT(eCAP1) | 13 | 25 |

| INT4.2 | 边沿触发 | ECAP2_INT(eCAP2) | 13 | 26 |

| INT4.3 | 边沿触发 | ECAP3_INT(eCAP3) | 13 | 27 |

| INT4.4 | 边沿触发 | ECAP4_INT(eCAP4) | 13 | 28 |

| INT4.5 | 边沿触发 | ECAP5_INT(eCAP5) | 13 | 29 |

| INT4.6 | 边沿触发 | ECAP6_INT(eCAP6) | 13 | 30 |

| INT4.7 |      | 保留               | 13 | 31 |

| INT4.8 |      | 保留               | 13 | 32 |

## 组 5

|        |      |                  |    |    |

|--------|------|------------------|----|----|

| INT5.1 | 边沿触发 | EQEP1_INT(eQEP1) | 12 | 33 |

| INT5.2 | 边沿触发 | EQEP2_INT(eQEP2) | 12 | 34 |

| INT5.3 |      | 保留               | 12 | 35 |

| INT5.4 |      | 保留               | 12 | 36 |

| INT5.5 |      | 保留               | 12 | 37 |

| INT5.6 |      | 保留               | 12 | 38 |

| INT5.7 |      | 保留               | 12 | 39 |

| INT5.8 |      | 保留               | 12 | 40 |

## 组 6

|        |      |                  |    |    |

|--------|------|------------------|----|----|

| INT6.1 | 边沿触发 | SPIRXINTA(SPI-A) | 11 | 41 |

| INT6.2 | 边沿触发 | SPITXINTA(SPI-A) | 11 | 42 |

| INT6.3 | 边沿触发 | MRINTB(McBSP-B)  | 11 | 43 |

| INT6.4 | 边沿触发 | MXINTB(McBSP-B)  | 11 | 44 |

| INT6.5 | 边沿触发 | MRINTA(McBSP-A)  | 11 | 45 |

| INT6.6 | 边沿触发 | MXINTA(McBSP-A)  | 11 | 46 |

| INT6.7 |      | 保留               | 11 | 47 |

| INT6.8 |      | 保留               | 11 | 48 |

## 组 7

|        |      |                |    |    |

|--------|------|----------------|----|----|

| INT7.1 | 边沿触发 | DINTCH1 (DMA1) | 10 | 49 |

| INT7.2 | 边沿触发 | DINTCH2 (DMA2) | 10 | 50 |

| INT7.3 | 边沿触发 | DINTCH3 (DMA3) | 10 | 51 |

| INT7.4 | 边沿触发 | DINTCH4 (DMA4) | 10 | 52 |

| INT7.5 | 边沿触发 | DINTCH5 (DMA5) | 10 | 53 |

| INT7.6 | 边沿触发 | DINTCH6 (DMA6) | 10 | 54 |

| INT7.7 |      | 保留             | 10 | 55 |

| INT7.8 |      | 保留             | 10 | 56 |

## 组 8

|        |      |                  |   |    |

|--------|------|------------------|---|----|

| INT8.1 | 边沿触发 | I2CINT1A(I2C-A)  | 9 | 57 |

| INT8.2 | 边沿触发 | I2CINT2A(I2C-A)  | 9 | 58 |

| INT8.3 |      | 保留               | 9 | 59 |

| INT8.4 |      | 保留               | 9 | 60 |

| INT8.5 | 边沿触发 | SCIRXINTC(SCI-C) | 9 | 61 |

| INT8.6 | 边沿触发 | SCITXINTC(SCI-C) | 9 | 62 |

| INT8.7 |      | 保留               | 9 | 63 |

| INT8.8 |      | 保留               | 9 | 64 |

## 组 9

|        |      |                   |   |    |

|--------|------|-------------------|---|----|

| INT9.1 | 边沿触发 | SCIRXINTA(SCI-A)  | 8 | 65 |

| INT9.2 | 边沿触发 | SCITXINTA(SCI-A)  | 8 | 66 |

| INT9.3 | 边沿触发 | SCIRXINTB(SCI-B)  | 8 | 67 |

| INT9.4 | 边沿触发 | SCITXINTB(SCI-B)  | 8 | 68 |

| INT9.5 | 边沿触发 | ECAN0INTA(eCAN-A) | 8 | 69 |

| INT9.6 | 边沿触发 | ECAN1INTA(eCAN-A) | 8 | 70 |

| INT9.7 | 边沿触发 | ECAN0INTB(eCAN-B) | 8 | 71 |

| INT9.8 | 边沿触发 | ECAN1INTB(eCAN-B) | 8 | 72 |

## 组 10

|         |  |    |   |    |

|---------|--|----|---|----|

| INT10.1 |  | 保留 | 7 | 73 |

| INT10.2 |  | 保留 | 7 | 74 |

| INT10.3 |  | 保留 | 7 | 75 |

| INT10.4 |  | 保留 | 7 | 76 |

| INT10.5 |  | 保留 | 7 | 77 |

| INT10.6 |  | 保留 | 7 | 78 |

| INT10.7 |  | 保留 | 7 | 79 |

| INT10.8 |  | 保留 | 7 | 80 |

## 组 11

|         |  |    |   |    |

|---------|--|----|---|----|

| INT11.1 |  | 保留 | 6 | 81 |

| INT11.2 |  | 保留 | 6 | 82 |

| INT11.3 |  | 保留 | 6 | 83 |

| INT11.4 |  | 保留 | 6 | 84 |

| INT11.5 |  | 保留 | 6 | 85 |

| INT11.6 |  | 保留 | 6 | 86 |

| INT11.7 |  | 保留 | 6 | 87 |

| INT11.8 |  | 保留 | 6 | 88 |

## 组 12

|                   |         |                                             |   |     |

|-------------------|---------|---------------------------------------------|---|-----|

| INT12.1           | 上升沿触发   | XINT3(Ext. Int. 3)                          | 5 | 89  |

|                   | 下降沿触发   |                                             |   |     |

|                   | 上升下降沿触发 |                                             |   |     |

| INT12.2           | 上升沿触发   | XINT4(Ext. Int. 4)                          | 5 | 90  |

|                   | 下降沿触发   |                                             |   |     |

|                   | 上升下降沿触发 |                                             |   |     |

| INT12.3           | 上升沿触发   | XINT5(Ext. Int. 5)                          | 5 | 91  |

|                   | 下降沿触发   |                                             |   |     |

|                   | 上升下降沿触发 |                                             |   |     |

| INT12.4           | 上升沿触发   | XINT6(Ext. Int. 6)                          | 5 | 92  |

|                   | 下降沿触发   |                                             |   |     |

|                   | 上升下降沿触发 |                                             |   |     |

| INT12.5           | 上升沿触发   | XINT7(Ext. Int. 7)                          | 5 | 93  |

|                   | 下降沿触发   |                                             |   |     |

|                   | 上升下降沿触发 |                                             |   |     |

| INT12.6           |         | 保留                                          | 5 | 94  |

| INT12.7           | 边沿触发    | LVF(FPU)                                    | 5 | 95  |

| INT12.8           | 边沿触发    | LUF(FPU)                                    | 5 | 96  |

| INT13             | 边沿触发    | External Interrupt 13 (XINT13) or DSPTimer1 | 4 | 97  |

| INT14             | 边沿触发    | DSP-Timer2<br>(for TI/RTOS use)             | 3 | 98  |

| NMI               | 上升沿触发   | External Non-Maskable Interrupt             |   |     |

|                   | 下降沿触发   |                                             |   |     |

|                   | 上升下降沿触发 |                                             |   |     |

| User-Defined Trap |         |                                             |   |     |

| USER1             |         |                                             |   | 99  |

| USER2             |         |                                             |   | 100 |

| USER3             |         |                                             |   | 101 |

| USER4             |         |                                             |   | 102 |

| USER5             |         |                                             |   | 103 |

| USER6             |         |                                             |   | 104 |

| USER7             |         |                                             |   | 105 |

| USER8             |         |                                             |   | 106 |

| USER9             |         |                                             |   | 107 |

| USER10            |         |                                             |   | 108 |

| USER11            |         |                                             |   | 109 |

|        |  |  |  |     |

|--------|--|--|--|-----|

| USER12 |  |  |  | 110 |

|--------|--|--|--|-----|

表 4-8 PLIC 寄存器地址映射表

| 寄存器名称             | 位宽  | 描述                                            | 寄存器地址（字节）  |

|-------------------|-----|-----------------------------------------------|------------|

| <b>PLIC 控制寄存器</b> |     |                                               |            |

| PLIC_PRIO0        | 32  | 保留                                            | 0x00800000 |

| PLIC_PRIO1        | 32  | 中断源 1 的优先级寄存器                                 | 0x00800004 |

| PLIC_PRIO2        | 32  | 中断源 2 的优先级寄存器                                 | 0x00800008 |

| ...               | ... | ...                                           | ...        |

| PLIC_PRIO96       | 32  | 中断源 96 的优先级寄存器                                | 0x00800180 |

| PLIC_PRIO97       | 32  | 中断源 97 的优先级寄存器                                | 0x00800184 |

| PLIC_PRIO98       | 32  | 中断源 98 的优先级寄存器                                | 0x00800188 |

| PLIC_IP0          | 32  | 中断源 0-31 的中断等待寄存器                             | 0x0080018C |

| PLIC_IP1          | 32  | 中断源 32-63 的中断等待寄存器                            | 0x00800190 |

| PLIC_IP2          | 32  | 中断源 64-95 的中断等待寄存器                            | 0x00800194 |

| PLIC_IP3          | 32  | 中断源 96-127 的中断等待寄存器                           | 0x00800198 |

| PLIC_H0_MIE0      | 32  | 中断源 0-31 的机器模式中断使能寄存器<br>(中断源 0 默认不存在, 该位为 0) | 0x0080019C |

| PLIC_H0_MIE1      | 32  | 中断源 32-63 的机器模式中断使能寄存器                        | 0x008001A0 |

| PLIC_H0_MIE2      | 32  | 中断源 64-95 的机器模式中断使能寄存器                        | 0x008001A4 |

| PLIC_H0_MIE3      | 32  | 中断源 96-127 的机器模式中断使能寄存器                       | 0x008001A8 |

| PLIC_H0_MTH       | 32  | 机器模式中断阈值寄存器 (取值范围为 0~31)                      | 0x008001AC |

| PLIC_H0_MCLAIM    | 32  | 机器模式中断响应/完成寄存器                                | 0x008001B0 |

| <b>外部中断控制寄存器</b>  |     |                                               |            |

| XINT1CR           | 16  | XINT1 控制寄存器                                   | 0x008001B4 |

| XINT2CR           | 16  | XINT2 控制寄存器                                   | 0x008001B6 |

| XINT3CR           | 16  | XINT3 控制寄存器                                   | 0x008001B8 |

| XINT4CR           | 16  | XINT4 控制寄存器                                   | 0x008001BA |

| XINT5CR           | 16  | XINT5 控制寄存器                                   | 0x008001BC |

| XINT6CR           | 16  | XINT6 控制寄存器                                   | 0x008001BE |

| XINT7CR           | 16  | XINT7 控制寄存器                                   | 0x008001C0 |

| XNMICR            | 16  | XNMI 控制寄存器                                    | 0x008001C2 |

| <b>外部中断计数器寄存器</b> |     |                                               |            |

|                          |    |                |            |

|--------------------------|----|----------------|------------|

| XINT1CTR                 | 16 | XINT1 计数器寄存器   | 0x008001C4 |

| XINT2CTR                 | 16 | XINT2 计数器寄存器   | 0x008001C6 |

| XNMICTR                  | 16 | XNMI 计数器寄存器    | 0x008001C8 |

| User-Defined Trap 优先级寄存器 |    |                |            |

| PLIC_PRIO99              | 斜杠 | USER1 的优先级寄存器  | 0x008001CC |

| PLIC_PRIO100             | 斜杠 | USER2 的优先级寄存器  | 0x008001D0 |

| PLIC_PRIO101             | 斜杠 | USER3 的优先级寄存器  | 0x008001D4 |

| PLIC_PRIO102             | 斜杠 | USER4 的优先级寄存器  | 0x008001D8 |

| PLIC_PRIO103             | 斜杠 | USER5 的优先级寄存器  | 0x008001DC |

| PLIC_PRIO104             | 斜杠 | USER6 的优先级寄存器  | 0x008001E0 |

| PLIC_PRIO105             | 斜杠 | USER7 的优先级寄存器  | 0x008001E4 |

| PLIC_PRIO106             | 斜杠 | USER8 的优先级寄存器  | 0x008001E8 |

| PLIC_PRIO107             | 斜杠 | USER9 的优先级寄存器  | 0x008001EC |

| PLIC_PRIO108             | 斜杠 | USER10 的优先级寄存器 | 0x008001F0 |

| PLIC_PRIO109             | 斜杠 | USER11 的优先级寄存器 | 0x008001F4 |

| PLIC_PRIO110             | 斜杠 | USER12 的优先级寄存器 | 0x008001F8 |

## 4.4. 外设

RV335 器件的集成外设在以下部分进行了说明：

- 6 通道直接内存存取 (DMA)

- 三个 32 位 DSP 定时器

- 高达 6 个增强型 PWM 模块 (ePWM1, ePWM2, ePWM3, ePWM4, ePWM5, ePWM6)

- 高达 6 个增强型捕获模块 (eCAP1, eCAP2, eCAP3, eCAP4, eCAP5, eCAP6)

- 高达 2 个增强型 QEP 模块 (eQEP1, eQEP2)

- 增强型模数转换器 (ADC) 模块

- 多达 2 个增强型控制器局域网 (eCAN) 模块 (eCAN-A, eCAN-B)

- 多达 3 个串行通信接口模块 (SCI-A, SCI-B, SCI-C)

- 1 个串行外设接口 (SPI) 模块 (SPI-A)

- 内部集成电路模块 (I2C)

- 高达两个多通道缓冲串口 (McBSP-A, McBSP-B) 模块

- 数字 I/O 和共用引脚功能

- 外部接口 (XINTF)

#### 4.4.1. DMA

特性：

- 触发源：

- ePWM SOCA/SOCB

- ADC 序列发生器 1 和序列发生器 2

- McBSP-A 和 McBSP-B 传输和接收逻辑

- XINT1-7 和 XINT13

- DSP 定时器

- 软件

- 数据源/目的地：

- L4-L7 16K × 16 SARAM

- 所有 XINTF 区域

- ADC 内存总线映射结果寄存器

- McBSP-A 和 McBSP-B 发送和接收缓冲区

- ePWM 寄存器

- 字大小：16 位或 32 位(McBSPs 限制到 16 位)

- 吞吐量：4 周期/字(McBSP 读取时为 5 周期/字)

A. ePWM 和 HRPWM 寄存器必须重新映射到 PF3(通过 MAPCNF 寄存器的位0)之后才可以由 DMA 访问。

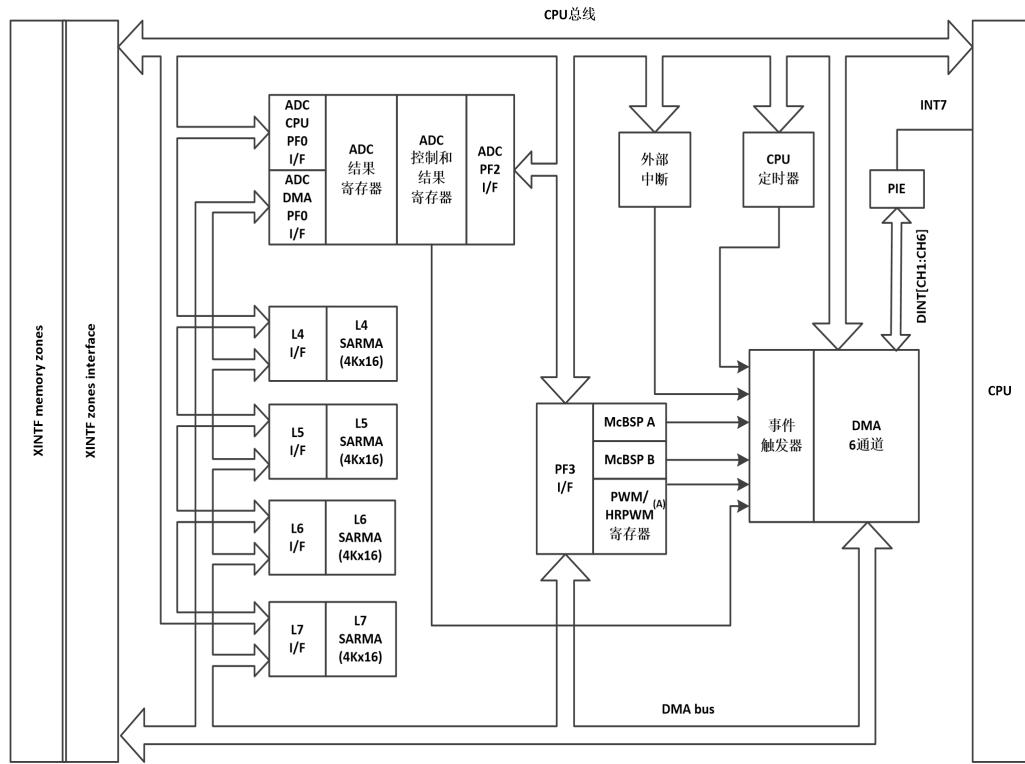

图 4-14 DMA 功能方框图

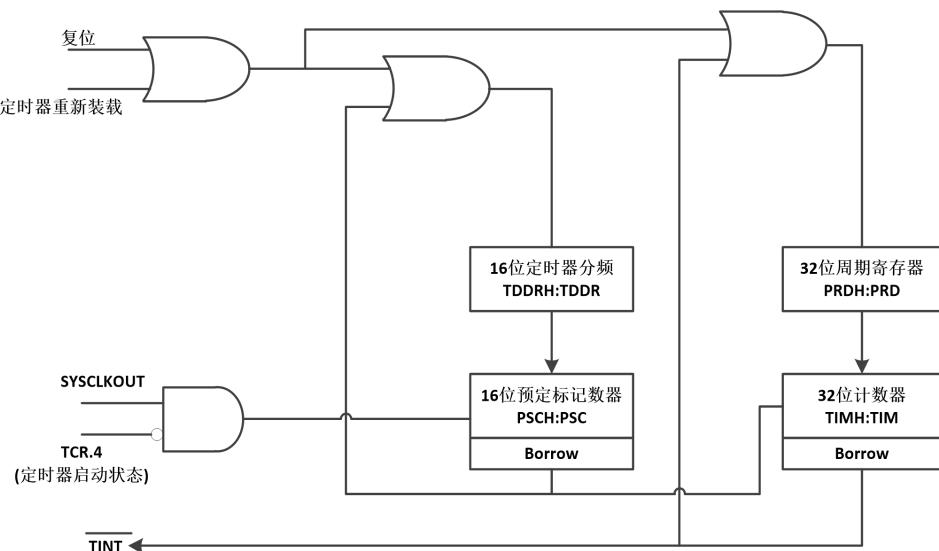

#### 4.4.2. 定时器

在器件上有 3 个 32 位 DSP 定时器 (DSP 定时器 0, DSP 定时器 1, DSP 定时器 2)。定时器 2 为 DSP/BIOS 预留。可以在用户应用程序中使用 DSP 定时器 0 和定时器 1。这些定时器与 ePWM 模块中的定时器不同。

图 4-15 DSP 定时器

定时器中断信号(TINT0, TINT1, TINT2)的连接如图 4-16所示。

- A. 定时器寄存器连接到 DSP 处理器的存储器总线.

- B. 定时器的时序与处理器时钟的 SYSCLKOUT 同步.

图 4-16 DSP 定时器中断信号和输出信号

定时器的通常操作如下: 32 位计数器寄存器 “TIMH:TIM” 被装入周期寄存器 PRDH:PRD 中的值。计数器寄存器按 DSP 的 SYSCLKOUT 速率递减。当计数器到达 0 时, 一个定时器中断输出信号生成一个中断脉冲。表 4-9 中列出的寄存器用于配置定时器。

表 4-9 DSP 定时器 0, 1, 2 配置和控制寄存器

| 名称         | 地址            | 大小 (字节) | 说明                   |

|------------|---------------|---------|----------------------|

| TIMER0TIM  | 0x1800-0x1801 | 2       | DSP 定时器 0, 计数器寄存器    |

| TIMER0TIMH | 0x1802-0x0C03 | 2       | DSP 定时器 0, 计数器寄存器高电平 |

| TIMER0PRD  | 0x1804-0x1805 | 2       | DSP 定时器 0, 周期寄存器     |

| TIMER0PRDH | 0x1806-0x1807 | 2       | DSP 定时器 0, 周期寄存器高电平  |

| TIMER0TCR  | 0x1808-0x1809 | 2       | DSP 定时器 0, 控制寄存器     |

| 保留         | 0x1814-0x1815 | 2       |                      |

| TIMER0TPR  | 0x1816-0x1817 | 2       | DSP 定时器 0, 预分频寄存器    |

| TIMER0TPRH | 0x1818-0x1819 | 2       | DSP 定时器 0, 预分频寄存器高电平 |

| TIMER1TIM  | 0x181A-0x181B | 2       | DSP 定时器 1, 计数器寄存器    |

| TIMER1TIMH | 0x181C-0x181D | 2       | DSP 定时器 1, 计数器寄存器高电平 |

| TIMER1PRD  | 0x181E-0x181F | 2       | DSP 定时器 1, 周期寄存器     |

| TIMER1PRDH | 0x1820-0x1821 | 2       | DSP 定时器 1, 周期寄存器高电平  |

| TIMER1TCR  | 0x1822-0x1823 | 2       | DSP 定时器 1, 控制寄存器     |

| 保留         | 0x1824-0x1825 | 2       |                      |

|            |               |    |                      |

|------------|---------------|----|----------------------|

| TIMER1TPR  | 0x1826-0x1827 | 2  | DSP 定时器 1, 预分频寄存器    |

| TIMER1TPRH | 0x1828-0x1829 | 2  | DSP 定时器 1, 预分频寄存器高电平 |

| TIMER2TIM  | 0x182A-0x182B | 2  | DSP 定时器 2, 计数器寄存器    |

| TIMER2TIMH | 0x182C-0x182D | 2  | DSP 定时器 2, 计数器寄存器高电平 |

| TIMER2PRD  | 0x182E-0x182F | 2  | DSP 定时器 2, 周期寄存器     |

| TIMER2PRDH | 0x1830-0x1831 | 2  | DSP 定时器 2, 周期寄存器高电平  |

| TIMER2TCR  | 0x1832-0x1833 | 2  | DSP 定时器 2, 控制寄存器     |

| 保留         | 0x1834-0x1835 | 2  |                      |

| TIMER2TPR  | 0x1836-0x1837 | 2  | DSP 定时器 2, 预分频寄存器    |

| TIMER2TPRH | 0x1838-0x1839 | 2  | DSP 定时器 2, 预分频寄存器高电平 |

| 保留         | 0x183A-0x1889 | 80 |                      |

#### 4.4.3. 增强型 PWM 模块

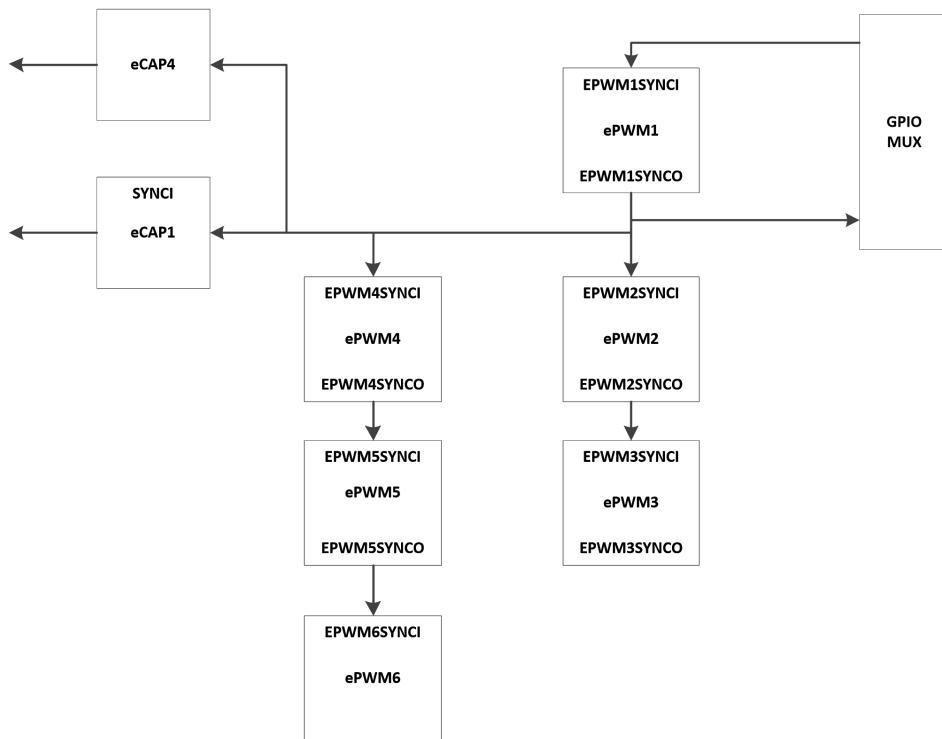

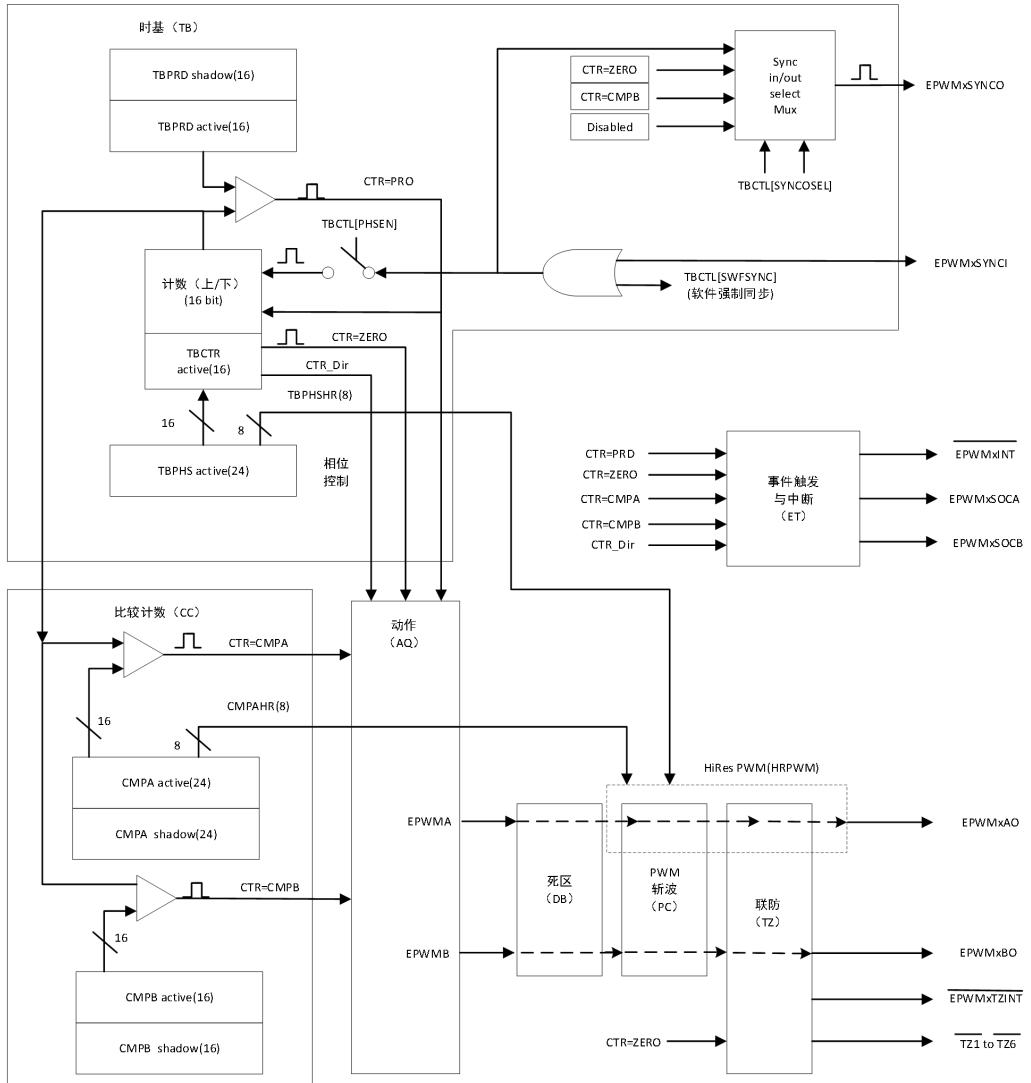

RV335 器件包含高达 6 个增强型 PWM (ePWM) 模块 (ePWM1, ePWM2, ePWM3, ePWM4, ePWM5, ePWM6)。图 4-17 显示时基计数器同步方案 3。图 4-18 显示了与 ePWM 互连的信号。

- A. 默认情况下, ePWM 和 HRPWM 寄存器被映射到外设帧1(PF1)。表18显示该配置。重新映射寄存器至外设帧3(PF3)来启用DMA 访问, MAPCNF 寄存器(地址0x702E)的位0 (MAPEPWM) 必须被设置为1。表19显示重新映射的配置.

图 4-17 时基计数器同步方案 3

表 4-10 ePWM 控制和状态寄存器(PF1 中的默认配置)

| 名称      | ePWM1  | ePWM2   | ePWM3  | ePWM4  | ePWM5  | ePWM6  | 大小(字节)<br>/影子寄存器 | 说明                 |

|---------|--------|---------|--------|--------|--------|--------|------------------|--------------------|

| TBCTL   | 0xD000 | 0x0D80  | 0xD100 | 0xD180 | 0xD200 | 0xD280 | 2/0              | 时基控制寄存器            |

| TBSTS   | 0xD002 | 0x0D82  | 0xD102 | 0xD182 | 0xD202 | 0xD282 | 2/0              | 时基状态寄存器            |

| TBPHSHR | 0xD004 | 0x0D84  | 0xD104 | 0xD184 | 0xD204 | 0xD284 | 2/0              | 时基相位 HRPWM 寄存器     |

| TBPHS   | 0xD006 | 0x0D86  | 0xD106 | 0xD186 | 0xD206 | 0xD286 | 2/0              | 时基相位寄存器            |

| TBCTR   | 0xD008 | 0x0D88  | 0xD108 | 0xD188 | 0xD208 | 0xD288 | 2/0              | 时基计数器寄存器           |

| TBPRD   | 0xD00A | 0x0D8A  | 0xD10A | 0xD18A | 0xD20A | 0xD28A | 2/2              | 时基周期寄存器集           |

| CMPCTL  | 0xD00E | 0x0D8E  | 0xD10E | 0xD18E | 0xD20E | 0xD28E | 2/0              | 计数器比较控制寄存器         |

| CMPAHR  | 0xD010 | 0x0D90  | 0xD110 | 0xD190 | 0xD210 | 0xD290 | 2/2              | 时基比较 A HRPWM 寄存器   |

| CMPA    | 0xD012 | 0x0D92  | 0xD112 | 0xD192 | 0xD212 | 0xD292 | 2/2              | 计数器比较 A 寄存器集       |

| CMPB    | 0xD014 | 0x0D94  | 0xD114 | 0xD194 | 0xD214 | 0xD294 | 2/2              | 计数器比较 B 寄存器集       |

| AQCTLA  | 0xD016 | 0x0D96  | 0xD116 | 0xD196 | 0xD216 | 0xD296 | 2/0              | 用于输出 A 的操作限定器控制寄存器 |

| AQCTLB  | 0xD018 | 0x0D98  | 0xD118 | 0xD198 | 0xD218 | 0xD298 | 2/0              | 用于输出 B 的操作限定器控制寄存器 |

| AQSFRC  | 0xD01A | 0x0D9A  | 0xD11A | 0xD19A | 0xD21A | 0xD29A | 2/0              | 操作限定器软件强制寄存器       |

| AQCSFRC | 0xD01C | 0x0D9C  | 0xD11C | 0xD19C | 0xD21C | 0xD29C | 2/2              | 操作限定器连续 S/W 强制寄存器集 |

| DBCTL   | 0xD01E | 0x0D9E  | 0xD11E | 0xD19E | 0xD21E | 0xD29E | 2/2              | 死区生成器控制寄存器         |

| DBRED   | 0xD020 | 0x0D0A0 | 0xD120 | 0xD1A0 | 0xD220 | 0xD2A0 | 2/0              | 死区生成器上升沿延迟计数寄存器    |

| DBFED   | 0xD022 | 0x0D0A2 | 0xD122 | 0xD1A2 | 0xD222 | 0xD2A2 | 2/0              | 死区生成器下降沿延迟计数寄存器    |

| TZSEL   | 0xD024 | 0x0D0A4 | 0xD124 | 0xD1A4 | 0xD224 | 0xD2A4 | 2/0              | 触发区选择寄存器           |

| TZCTL   | 0xD026 | 0x0D0A6 | 0xD126 | 0xD1A6 | 0xD226 | 0xD2A6 | 2/0              | 触发区控制寄存器           |

| TZEINT  | 0xD028 | 0x0D0A8 | 0xD128 | 0xD1A8 | 0xD228 | 0xD2A8 | 2/0              | 触发区启用中断寄存器         |

| TZFLG   | 0xD02A | 0x0D0AA | 0xD12A | 0xD1AA | 0xD22A | 0xD2AA | 2/0              | 触发区标志寄存器           |

|        |        |        |        |        |        |        |     |              |

|--------|--------|--------|--------|--------|--------|--------|-----|--------------|

| TZCLR  | 0xD02C | 0xD0AC | 0xD12C | 0xD1AC | 0xD22C | 0xD2AC | 2/0 | 触发区清除寄存器     |

| TZFRC  | 0xD02E | 0xD0AE | 0xD12E | 0xD1AE | 0xD22E | 0xD2AE | 2/0 | 触发区强制寄存器     |

| ETSEL  | 0xD030 | 0xD0B0 | 0xD130 | 0xD1B0 | 0xD230 | 0xD2B0 | 2/0 | 事件触发器选择寄存器   |

| ETPS   | 0xD032 | 0xD0B2 | 0xD132 | 0xD1B2 | 0xD232 | 0xD2B2 | 2/0 | 事件触发器预分频寄存器  |

| ETFLG  | 0xD034 | 0xD0B4 | 0xD134 | 0xD1B4 | 0xD234 | 0xD2B4 | 2/0 | 事件触发器标志寄存器   |

| ETCLR  | 0xD036 | 0xD0B6 | 0xD136 | 0xD1B6 | 0xD236 | 0xD2B6 | 2/0 | 事件触发器清除寄存器   |

| ETFRC  | 0xD038 | 0xD0B8 | 0xD138 | 0xD1B8 | 0xD238 | 0xD2B8 | 2/0 | 事件触发器强制寄存器   |

| PCCTL  | 0xD03A | 0xD0BA | 0xD13A | 0xD1BA | 0xD23A | 0xD2BA | 2/0 | PWM 斩波器控制寄存器 |

| HRCNFG | 0xD03C | 0xD0BC | 0xD13C | 0xD1BC | 0xD23C | 0xD2BC | 2/0 | HRPWM 配置寄存器  |

表 4-11 ePWM 控制和状态寄存器(在 PF3 中重新映射的配置-可由 DMA 访问)

| 名称      | ePWM1  | ePWM2  | ePWM3  | ePWM4  | ePWM5  | ePWM6  | 大小(字节)/影子寄存器 | 说明               |

|---------|--------|--------|--------|--------|--------|--------|--------------|------------------|

| TBCTL   | 0xB000 | 0xB080 | 0xB100 | 0xB180 | 0xB200 | 0xB280 | 2/0          | 时基控制寄存器          |

| TBSTS   | 0xB002 | 0xB082 | 0xB102 | 0xB182 | 0xB202 | 0xB282 | 2/0          | 时基状态寄存器          |

| TBPHSHR | 0xB004 | 0xB084 | 0xB104 | 0xB184 | 0xB204 | 0xB284 | 2/0          | 时基相位 HRPWM 寄存器   |

| TBPHS   | 0xB006 | 0xB086 | 0xB106 | 0xB186 | 0xB206 | 0xB286 | 2/0          | 时基相位寄存器          |

| TBCTR   | 0xB008 | 0xB088 | 0xB108 | 0xB188 | 0xB208 | 0xB288 | 2/0          | 时基计数器寄存器         |

| TBPRD   | 0xB00A | 0xB08A | 0xB10A | 0xB18A | 0xB20A | 0xB28A | 2/2          | 时基周期寄存器集         |

| CMPCTL  | 0xB00C | 0xB08C | 0xB10C | 0xB18C | 0xB20C | 0xB28C | 2/0          | 计数器比较控制寄存器       |

| CMPAHR  | 0xB00E | 0xB08E | 0xB10E | 0xB18E | 0xB20E | 0xB28E | 2/2          | 时基比较 A HRPWM 寄存器 |

| CMPA    | 0xB010 | 0xB090 | 0xB110 | 0xB190 | 0xB210 | 0xB290 | 2/2          | 计数器比较 A 寄存器设置    |

| CMPB    | 0xB012 | 0xB092 | 0xB112 | 0xB192 | 0xB212 | 0xB292 | 2/2          | 计数器比较 B 寄存器设置    |

| AQCTLA  | 0xB014 | 0xB094 | 0xB114 | 0xB194 | 0xB214 | 0xB294 | 2/0          | 用于输出 A 的操作限      |

| AQCTLB  | 0xB016 | 0xB096 | 0xB116 | 0xB196 | 0xB216 | 0xB296 | 2/0          | 定器控制寄存器          |

|         |        |        |        |        |        |        |              | 用于输出 B 的操作       |

|         |        |        |        |        |        |        |     |                     |

|---------|--------|--------|--------|--------|--------|--------|-----|---------------------|

|         |        |        |        |        |        |        |     | 限定器控制寄存器            |

| AQSFRC  | 0xB018 | 0xB098 | 0xB118 | 0xB198 | 0xB218 | 0xB298 | 2/0 | 操作限定器软件强制寄存器        |

| AQCSFRC | 0xB01A | 0xB09A | 0xB11A | 0xB19A | 0xB21A | 0xB29A | 2/2 | 操作限定器连续 S/W 强制寄存器设置 |

| DBCTL   | 0xB01C | 0xB09C | 0xB11C | 0xB19C | 0xB21C | 0xB29C | 2/2 | 死区生成器控制寄存器          |

| DBRED   | 0xB01E | 0xB09E | 0xB11E | 0xB19E | 0xB21E | 0xB29E | 2/0 | 死区生成器上升沿延时计数寄存器     |

| DBFED   | 0xB020 | 0xB0A0 | 0xB120 | 0xB1A0 | 0xB220 | 0xB2A0 | 2/0 | 死区生成器下降沿延时计数寄存器     |

| TZSEL   | 0xB022 | 0xB0A2 | 0xB122 | 0xB1A2 | 0xB222 | 0xB2A2 | 2/0 | 触发区选择寄存器            |

| TZCTL   | 0xB024 | 0xB0A4 | 0xB124 | 0xB1A4 | 0xB224 | 0xB2A4 | 2/0 | 触发区控制寄存器            |

| TZEINT  | 0xB026 | 0xB0A6 | 0xB126 | 0xB1A6 | 0xB226 | 0xB2A6 | 2/0 | 触发区启用中断寄存器          |

| TZFLG   | 0xB028 | 0xB0A8 | 0xB128 | 0xB1A8 | 0xB228 | 0xB2A8 | 2/0 | 触发区标志寄存器            |

| TZCLR   | 0xB02A | 0xB0AA | 0xB12A | 0xB1AA | 0xB22A | 0xB2AA | 2/0 | 触发区清除寄存器            |

| TZFRC   | 0xB02C | 0xB0AC | 0xB12C | 0xB1AC | 0xB22C | 0xB2AC | 2/0 | 触发区强制寄存器            |

| ETSEL   | 0xB02E | 0xB0AE | 0xB12E | 0xB1AE | 0xB22E | 0xB2AE | 2/0 | 事件触发器选择寄存器          |

| ETPS    | 0xB030 | 0xB0B0 | 0xB130 | 0xB1B0 | 0xB230 | 0xB2B0 | 2/0 | 事件触发器预分频寄存器         |

| ETFLG   | 0xB032 | 0xB0B2 | 0xB132 | 0xB1B2 | 0xB232 | 0xB2B2 | 2/0 | 事件触发器标志寄存器          |

| ETCLR   | 0xB034 | 0xB0B4 | 0xB134 | 0xB1B4 | 0xB234 | 0xB2B4 | 2/0 | 事件触发器清除寄存器          |

| ETFRC   | 0xB036 | 0xB0B6 | 0xB136 | 0xB1B6 | 0xB236 | 0xB2B6 | 2/0 | 事件触发器强制寄存器          |

| PCCTL   | 0xB038 | 0xB0B8 | 0xB138 | 0xB1B8 | 0xB238 | 0xB2B8 | 2/0 | PWM 斩波器控制寄存器        |

| HRCNFG  | 0xB03A | 0xB0BA | 0xB13A | 0xB1BA | 0xB23A | 0xB2BA | 2/0 | HRPWM 配置寄存器         |

图 4-18 ePWM 子模块显示关键内部信号互连

#### 4.4.4. 高分辨率 PWM(HRPWM)

HRPWM 模块提供 PWM 分辨率(时间粒度)，此分辨率好于使用传统数字 PWM 方法所能实现的分辨率。HRPWM 模块的关键点为：

- 扩展了传统数字 PWM 的时间分辨率能力。

- 通常在有效 PWM 分辨率下降到低于大约 9-10 位时使用。当用一个 100MHz 的DSP / 系统时钟时，PWM 频率大于大约 200kHz 时会发生这种情况。

- 这个功能可被用在占空比和相移控制方法中。

- 通过对 ePWM 模块的比较 A 和相位寄存器的扩展来控制更加精细的时间粒度控制或者边沿定位。

- HRPWM 功能, 只在 ePWM 模块的 A 信号路径上提供(也就是说, 在 EPWMxA 输出上提供)。EPWMxB 输出具有传统 PWM 功能。

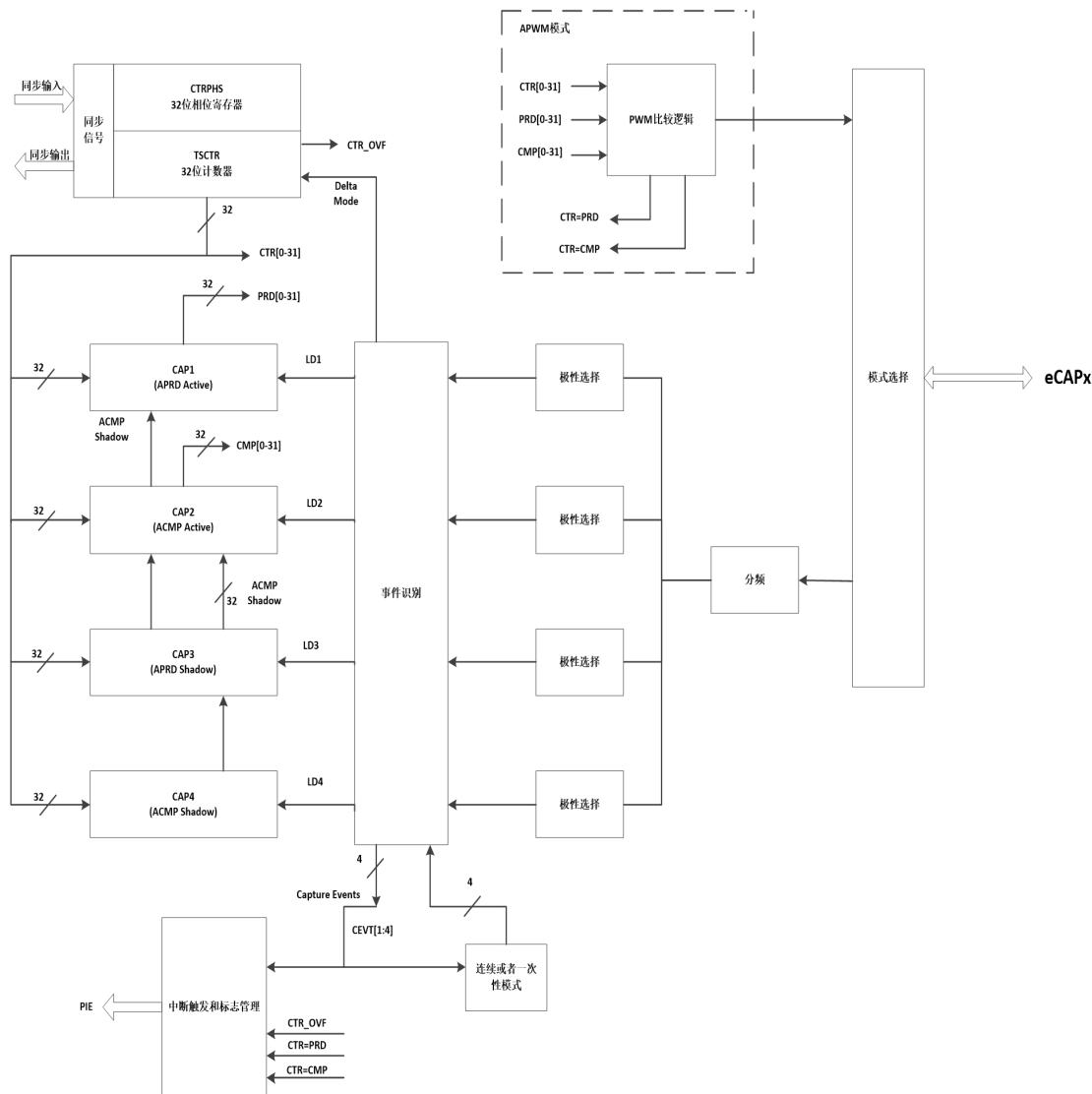

#### 4.4.5. 增强型 CAP 模块

RV335 器件包括6个增强型捕获 (eCAP) 模块 (eCAP1, eCAP2, eCAP3, eCAP4, eCAP5, 和 eCAP6)。图 4-19显示了一个模块的功能方框图。

图 4-19 eCAP 功能方框图

eCAP 模块以 SYSCLKOUT 速率计时。

PCLKCR1 寄存器中的时钟使能位(ECAP1ENCLK, ECAP2ENCLK, ECAP3ENCLK, ECAP4ENCLK, ECAP5ENCLK, ECAP6ENCLK)被单独用来关闭 eCAP 模块(针对低功耗运行)。复位后, ECAP1ENCLK, ECAP2ENCLK,

ECAP3ENCLK, ECAP4ENCLK, ECAP5ENCLK 和 ECAP6ENCLK 被设为低电平, 表明外设时钟关闭。

表 4-12 eCAP 控制和状态寄存器

| 名称     | eCAP1             | eCAP2             | eCAP3             | eCAP4             | eCAP5             | eCAP6             | 大小(字节) | 说明          |

|--------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------|-------------|

| TSCTR  | 0xD400            | 0xD440            | 0xD480            | 0xD4C0            | 0xD500            | 0xD540            | 4      | 时间戳计数器      |

| CTRPHS | 0xD404            | 0xD444            | 0xD484            | 0xD4C4            | 0xD504            | 0xD544            | 4      | 计数器相位偏移值寄存器 |

| CAP1   | 0xD408            | 0xD448            | 0xD488            | 0xD4C8            | 0xD508            | 0xD548            | 4      | 捕捉 1 寄存器    |

| CAP2   | 0xD40C            | 0xD44C            | 0xD48C            | 0xD4CC            | 0xD50C            | 0xD54C            | 4      | 捕捉 2 寄存器    |

| CAP3   | 0xD410            | 0xD450            | 0xD490            | 0xD4D0            | 0xD510            | 0xD550            | 4      | 捕捉 3 寄存器    |

| CAP4   | 0xD414            | 0xD454            | 0xD494            | 0xD4D4            | 0xD514            | 0xD554            | 4      | 捕捉 4 寄存器    |

| 保留     | 0xD418-<br>0xD427 | 0xD458-<br>0xD467 | 0xD498-<br>0xD4A7 | 0xD4D8-<br>0xD4E7 | 0xD518-<br>0xD527 | 0xD558-<br>0xD567 | 16     | 保留          |

| ECCTL1 | 0xD428            | 0xD468            | 0xD4A8            | 0xD4E8            | 0xD528            | 0xD568            | 2      | 捕捉控制寄存器 1   |

| ECCTL2 | 0xD42A            | 0xD46A            | 0xD4AA            | 0xD4EA            | 0xD52A            | 0xD56A            | 2      | 捕捉控制寄存器 2   |

| ECEINT | 0xD42C            | 0xD46C            | 0xD4AC            | 0xD4EC            | 0xD52C            | 0xD45C            | 2      | 捕捉中断使能寄存器   |

| ECFLG  | 0xD42E            | 0xD46E            | 0xD4AE            | 0xD4EE            | 0xD52E            | 0xD45E            | 2      | 捕捉中断标志寄存器   |

| ECCLR  | 0xD430            | 0xD470            | 0xD4B0            | 0xD4F0            | 0xD530            | 0xD460            | 2      | 捕捉中断清除寄存器   |

| ECFRC  | 0xD432            | 0xD472            | 0xD4B2            | 0xD4F2            | 0xD532            | 0xD462            | 2      | 捕捉中断强制寄存器   |

| 保留     | 0xD434-<br>0xD43F | 0xD474-<br>0xD47F | 0xD4B4-<br>0xD4BF | 0xD4F4-<br>0xD4FF | 0xD534-<br>0xD53F | 0xD464-<br>0xD46F | 12     | 保留          |

#### 4.4.6. 增强型 QEP 模块

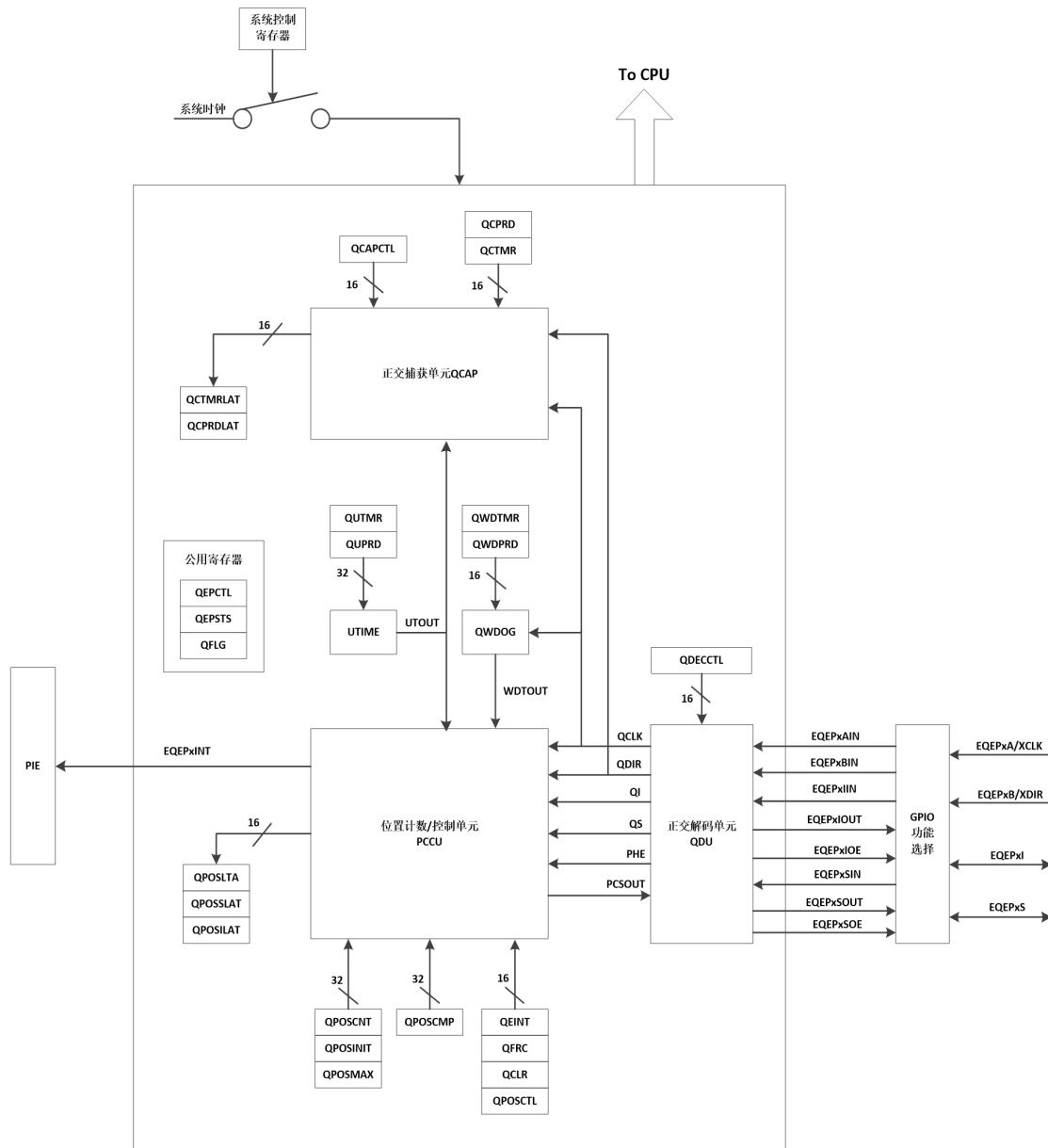

该器件包括高达 2 个增强型正交编码器(eQEP) 模块(eQEP1, eQEP2)。图 4-20 显示了 eQEP 模块的方框图。

图 4-20 eQEP 功能方框图

表 4-13 提供了 eQEP 寄存器的汇总。

表 4-13 eQEP 控制和状态寄存器

| 名称       | eQEP1<br>地址 | eQEP2<br>地址 | eQEP1<br>大小 (字节)<br>#SHADOW | 寄存器说明        |

|----------|-------------|-------------|-----------------------------|--------------|

| QPOSCNT  | 0xD600      | 0xD680      | 4/0                         | eQEP 位置计数器   |

| QPOSINIT | 0xD604      | 0xD684      | 4/0                         | eQEP 初始化位置计数 |

| QPOSMAX  | 0xD608      | 0xD688      | 4/0                         | eQEP 最大位置计数  |

|          |               |               |      |                |

|----------|---------------|---------------|------|----------------|

| QPOSCMP  | 0xD60C        | 0xD68C        | 4/1  | eQEP 位置比较      |

| QPOSILAT | 0xD610        | 0xD690        | 4/0  | eQEP 索引位置锁存    |

| QPOSSLAT | 0xD614        | 0xD694        | 4/0  | eQEP 选通脉冲位置锁存  |

| QPOSLAT  | 0xD618        | 0xD698        | 4/0  | eQEP 位置锁存      |

| QUTMR    | 0xD61C        | 0xD69C        | 4/0  | eQEP 单位定时器     |

| QUPRD    | 0xD620        | 0xD6A0        | 4/0  | eQEP 单位周期寄存器   |

| QWDTMR   | 0xD624        | 0xD6A4        | 2/0  | eQEP 安全装置定时器   |

| QWDPRD   | 0xD626        | 0xD6A6        | 2/0  | eQEP 安全装置周期寄存器 |

| QDECCTL  | 0xD628        | 0xD6A8        | 2/0  | eQEP 解码器控制寄存器  |

| QEPCCTL  | 0xD62A        | 0xD6AA        | 2/0  | eQEP 控制寄存器     |

| QCAPCTL  | 0xD62C        | 0xD6AC        | 2/0  | eQEP 捕捉控制寄存器   |

| QPOSCTL  | 0xD62E        | 0xD6AE        | 2/0  | eQEP 位置比较控制寄存器 |

| QEINT    | 0xD630        | 0xD6B0        | 2/0  | eQEP 中断使能寄存器   |

| QFLG     | 0xD632        | 0xD6B2        | 2/0  | eQEP 中断标志寄存器   |

| QCLR     | 0xD634        | 0xD6B4        | 2/0  | eQEP 中断清除寄存器   |

| QFRC     | 0xD636        | 0xD6B6        | 2/0  | eQEP 中断强制寄存器   |

| QEPESTS  | 0xD638        | 0xD6B8        | 2/0  | eQEP 状态寄存器     |

| QCTMR    | 0xD63A        | 0xD6BA        | 2/0  | eQEP 捕捉定时器     |

| QCPRD    | 0xD63C        | 0xD6BC        | 2/0  | eQEP 捕捉周期寄存器   |

| QCTMRLAT | 0xD63E        | 0xD6BE        | 2/0  | eQEP 捕捉定时器锁存   |

| QCPRDLAT | 0xD640        | 0xD6C0        | 2/0  | eQEP 捕捉周期锁存    |

| 保留       | 0xD642-0xD67F | 0xD6C2-0xD6FF | 62/0 |                |

#### 4.4.7. 模数转换器(ADC 模块)

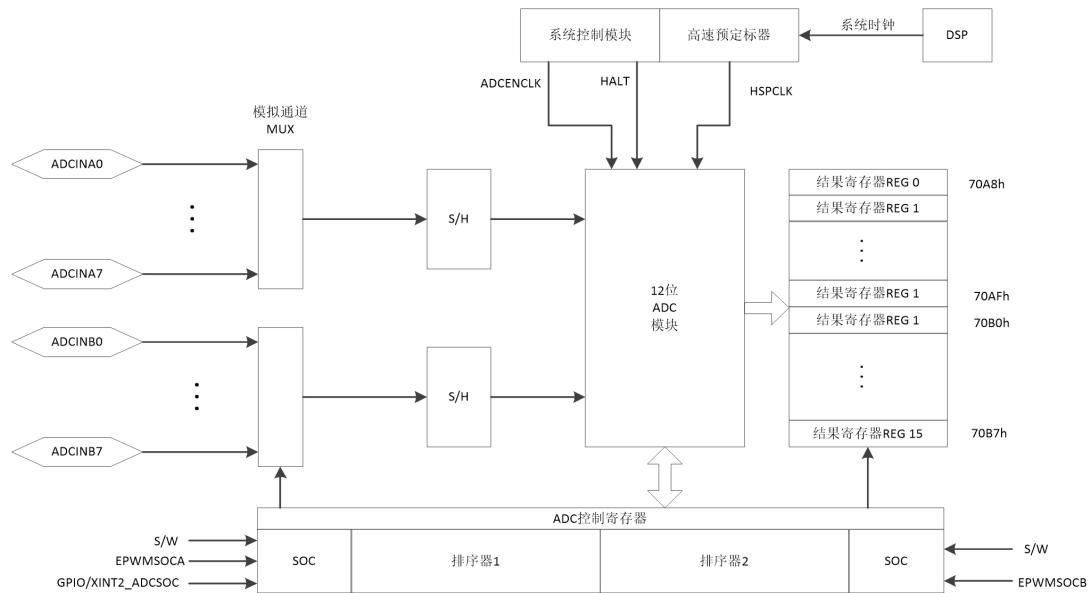

图 4-21 显示了一个 ADC 模块的简化功能方框图 ADC 模块由一个带有内置采样保持 (S/H) 电路的 12 位 ADC 组成。ADC 模块的功能包括：

- 具有内置 S/H 的 12 位 ADC 内核。

- 模拟输入：0.0V 至 3.0V(高于 3.0V 的电压产生满刻度转换结果)。

- 快速转换率：在25MHz ADC 时钟12.5MSPS上时高达80ns。

- 16 个专用 ADC 通道。每次采样/保持都有复用的 8 通道。

- 自动定序功能在单次会话中可提供多达 16 次“自动转换”。可将每次转换编程为选择 16 个输入信道中的任何一个。

- 序列发生器可运行为 2 个独立的 8 状态序列发生器，或作为 1 个较大的 16

态序列发生器(即 2 个级联的 8 态序列发生器)。

- 用于存储转换值的 16 个结果寄存器(可分别寻址)

- 输入模拟电压的数值源自：

Digital Value = 0

When input  $\leq 0V$

Digital Value =  $4096 \times \frac{\text{Input Analog Voltage} - \text{ADCLO}}{3}$

When  $0V < \text{input} < 3V$

Digital Value = 4095

When input  $\geq 3V$

- 作为转换开始 (SOC) 序列源的多个触发器

- S/W - 软件立即启动

- ePWMM 转换开始

- XINT2 ADC 转换开始

- 灵活的中断控制允许每个序列结束 (EOS) 或每个其它 EOS 上的中断请求。

- 序列发生器可运行于“启/停”模式，从而实现多个“时序触发器”同步转换。

- SOCA 和 SOCB 触发器可独立运行在双序列发生器模式中。

- 采样保持 (S/H) 采集时间窗口具有独立的预分频控制。

RV335 器件中的 ADC 模块已经被增强以便为 ePWM 外设提供灵活接口。ADC 接口被建立在一个快速，12 位 ADC 模块上，此模块在 25MHzADC 时钟上的快速转换率高达 80ns。ADC 模块有 16 个通道，可配置为两个独立的 8 通道模块。可将 2 个独立的 8 信道模块级联成 1 个 16 信道模块。尽管有多个输入通道和 2 个序列发生器，但在 ADC 模块中只有一个转换器。图 4-21 显示了 ADC 模块的方框图。

2 个 8 通道模块可自动对一系列转换定序，每个模块可以通过模拟 MUX 选择其中一个可用 8 信道。在级联模式中，自动序列发生器将作为一个单个 16 通道序列发生器使用。在每个序列发生器上，一旦转换完成，所选的通道值将存储在各自的 RESULT 寄存器中。系统可使用自动定序功能多次转换同一信道，以便用户执行过采样算法。这种过采样算法可提供比传统的单一采样转换结果更高的分辨率。

图 4-21 ADC 模块的方框图

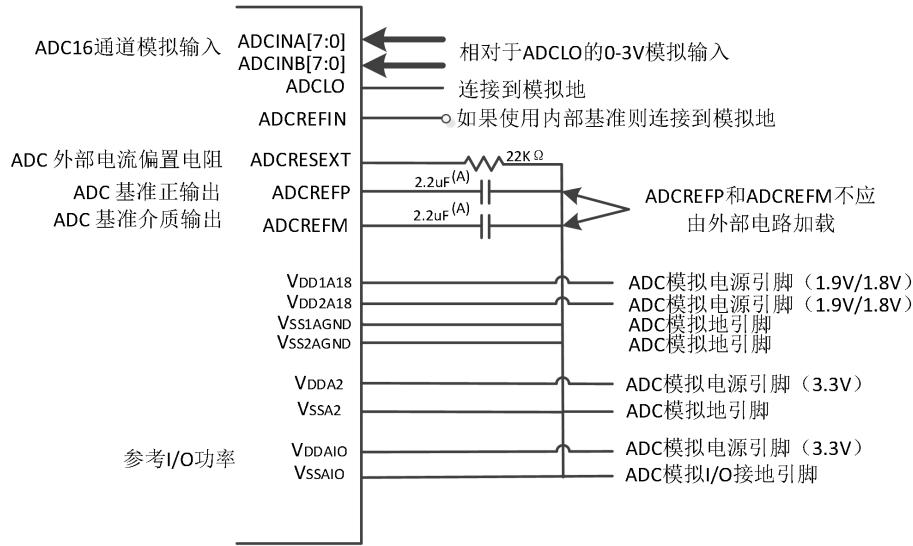

要获得指定的 ADC 精度，正确的电路板布局非常关键。为尽可能达到最佳效果，引入 ADCIN 引脚的走线不应太靠近数字信号通道。这是为了最大程度地减少数字线路上因 ADC 输入耦合而产生的开关噪声。而且，适当的隔离技术必须被用来将数字电源从 ADC 模块电源引脚 (VDD1A18, VDD2A18, VDDA2, VDDAIO) 上隔离。图 4-22 显示针对器件的 ADC 引脚。

- A. TAIYO YUDEN LMK212BJ225MG-T 或等效器件.

- B. 建议在所有电源引脚上使用外部去耦合电容器.

- C. 必须从不会降低 ADC 性能的运算放大器上驱动模拟输入.

图 4-22 带有内部基准的 ADC 引脚连接

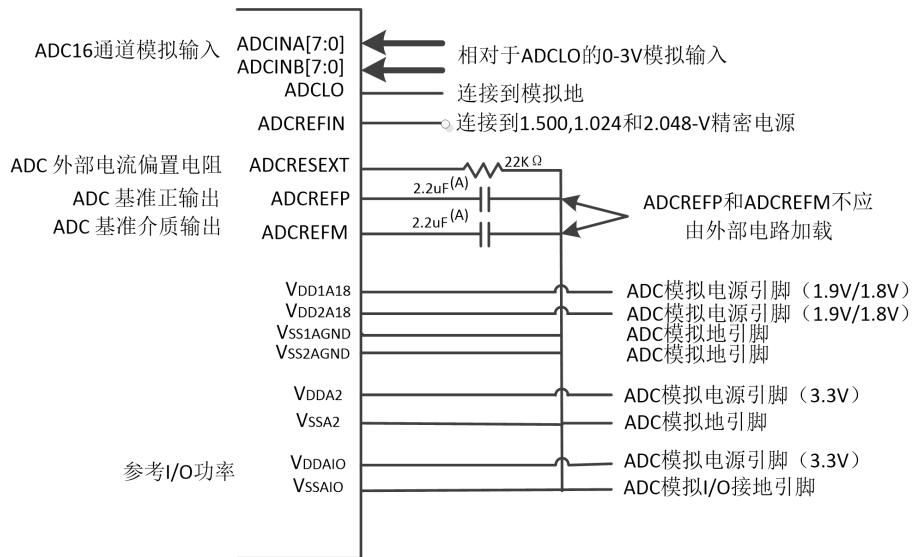

- A. TAIYO YUDEN LMK212BJ225MG-T 或者等效器件.

- B. 建议在所有电源引脚上使用外部去耦合电容器.

- C. 模拟输入必须由一个运算放大器驱动, 此运算放大器不会降低 ADC 性能.

- D. 根据这个引脚上的电压, 通过改变 ADC 基准选择寄存器中的位 15:14 可启用 ADCREFIN 上的外部电压.

- 总体增益精度将由这个电压源的精度确定.

图 4-23 带有外部基准的 ADC 引脚连接

#### 4.4.8. 多通道缓冲串行端口 (McBSP) 模块

McBSP 模块有以下特性:

- 全双工通信

- 允许连续数据流的双缓冲数据寄存器

- 用于接收和发送的独立成帧和时钟

- 外部移位时钟生成或者一个内部可设定频率移位时钟

- 包括8, 12, 16, 20, 24, 或者 32 位在内的宽数据尺寸选择

- 以 LSB 或者 MSB 开头的 8 位数据传输

- 用于帧同步和数据时钟的可编程极性

- 高度可编程内部时钟和帧生成

- 到工业标准 CODEG、模拟接口芯片 (AIC)、和其它串行连接的 A/D 和 D/A 器件的直接接口

- 与 SPI 兼容器件一起工作

- McBSP 上支持下列应用接口:

- T1/E1 成帧器

- 符合 IOM-2 的器件

- AC97 - 兼容器件(提供所需的多相位帧同步功能)

- IIS - 兼容器件

- 串行外设接口 (SPI)

- McBSP 时钟速率,

$$CLKG = \frac{CLKSRG}{1 + CLKGDV}$$

在这里, CLKSRG 时钟源可以是 LSPCLK, CLKX, 或者 CLKR。串行端口性能受到 I/O 缓冲器开关速度的影响。内部预分频器必须被调整, 这样, 外设速度将低于 I/O 缓冲器速度限制。

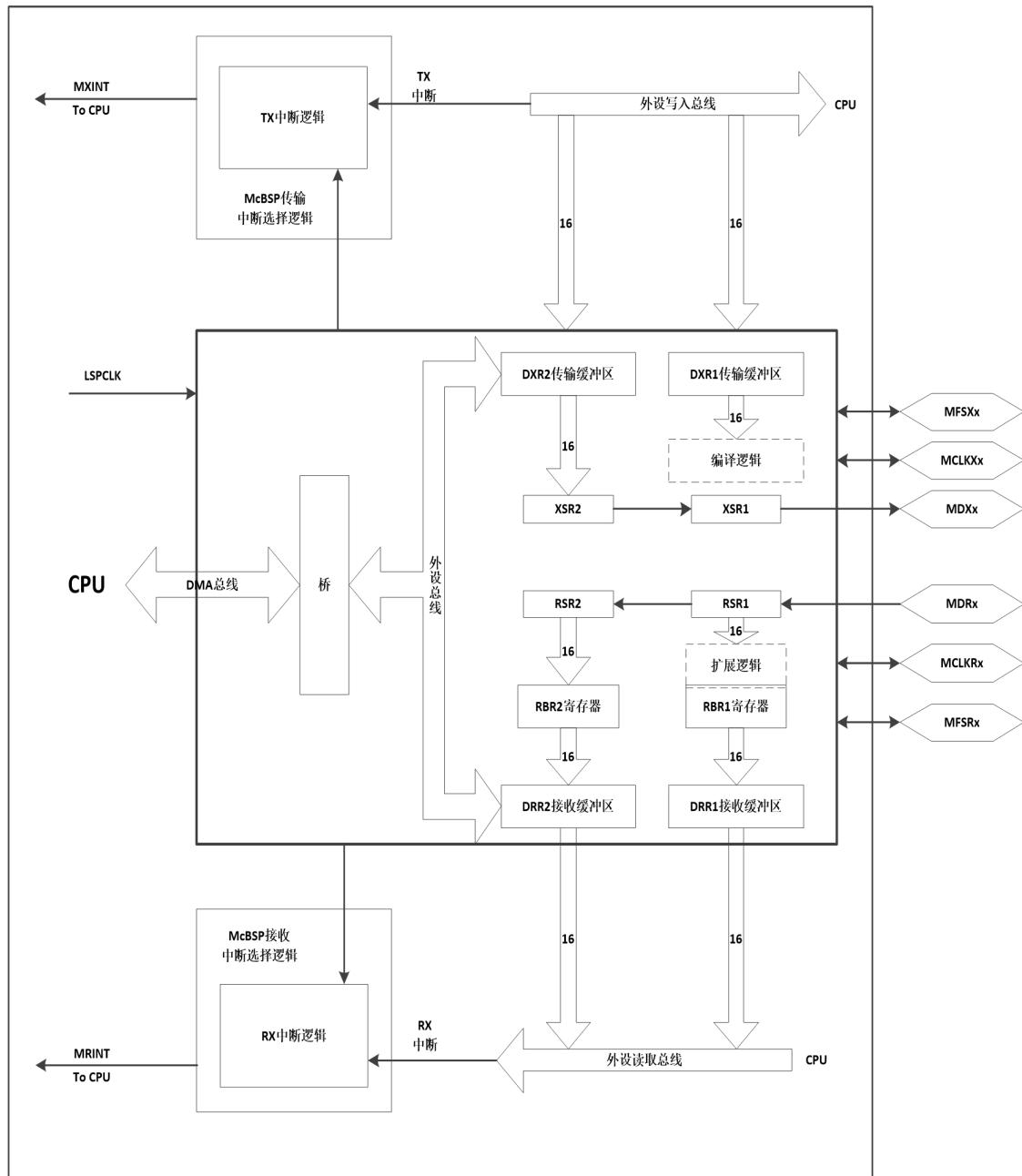

图 4-24显示了 McBSP 模块的方框图。

图 4-24 McBSP 模块

表 4-14 提供了 McBSP 寄存器的汇总。

表 4-14 McBSP 寄存器汇总

| 名称           | McBSP-A<br>地址 | McBSP-B<br>地址 | 类型 | 复位值    | 说明              |

|--------------|---------------|---------------|----|--------|-----------------|

| 数据寄存器, 接收、发送 |               |               |    |        |                 |

| DRR2         | 0xA000        | 0xA080        | R  | 0x0000 | McBSP 数据接收寄存器 2 |

| DRR1         | 0xA002        | 0xA082        | R  | 0x0000 | McBSP 数据接收寄存器 1 |

|             |        |        |     |        |                     |

|-------------|--------|--------|-----|--------|---------------------|

| DXR2        | 0xA004 | 0xA084 | W   | 0x0000 | McBSP 数据发送寄存器 2     |

| DXR1        | 0xA006 | 0xA086 | W   | 0x0000 | McBSP 数据发送寄存器 1     |

| McBSP 控制寄存器 |        |        |     |        |                     |

| SPCR2       | 0xA008 | 0xA088 | 读/写 | 0x0000 | McBSP 串行端口控制寄存器 2   |

| SPCR1       | 0xA00A | 0xA08A | 读/写 | 0x0000 | McBSP 串行端口控制寄存器 1   |

| RCR2        | 0xA00C | 0xA08C | 读/写 | 0x0000 | McBSP 接收控制寄存器 2     |

| RCR1        | 0xA00E | 0xA08E | 读/写 | 0x0000 | McBSP 接收控制寄存器 1     |

| XCR2        | 0xA010 | 0xA090 | 读/写 | 0x0000 | McBSP 发送控制寄存器 2     |

| XCR1        | 0xA012 | 0xA092 | 读/写 | 0x0000 | McBSP 发送控制寄存器 1     |

| SRGR2       | 0xA014 | 0xA094 | 读/写 | 0x0000 | McBSP 采样率发生器寄存器 2   |

| SRGR1       | 0xA016 | 0xA096 | 读/写 | 0x0000 | McBSP 采样率发生器寄存器 1   |

| 多通道控制寄存器    |        |        |     |        |                     |

| MCR2        | 0xA018 | 0xA098 | 读/写 | 0x0000 | McBSP 多通道寄存器 2      |

| MCR1        | 0xA01A | 0xA09A | 读/写 | 0x0000 | McBSP 多通道寄存器 1      |

| RCERA       | 0xA01C | 0xA09C | 读/写 | 0x0000 | McBSP 接收通道使能寄存器分区 A |

| RCERB       | 0xA01E | 0xA09E | 读/写 | 0x0000 | McBSP 接收通道使能寄存器分区 B |

| XCERA       | 0xA020 | 0xA0A0 | 读/写 | 0x0000 | McBSP 发送通道使能寄存器分区 A |

| XCERB       | 0xA022 | 0xA0A2 | 读/写 | 0x0000 | McBSP 发送通道使能寄存器分区 B |

| PCR         | 0xA024 | 0xA0A4 | 读/写 | 0x0000 | McBSP 引脚控制寄存器       |

| RCERC       | 0xA026 | 0xA0A6 | 读/写 | 0x0000 | McBSP 接收通道使能寄存器分区 C |

| RCERD       | 0xA028 | 0xA0A8 | 读/写 | 0x0000 | McBSP 接收通道使能寄存器分区 D |

| XCERC       | 0xA02A | 0xA0AA | 读/写 | 0x0000 | McBSP 发送通道使能寄存器分区 C |

| XCERD       | 0xA02C | 0xA0AC | 读/写 | 0x0000 | McBSP 发送通道使能寄存器分区 D |

| RCERE       | 0xA02E | 0xA0AE | 读/写 | 0x0000 | McBSP 接收通道使能寄存器分区 E |

| RCERF       | 0xA030 | 0xA0B0 | 读/写 | 0x0000 | McBSP 接收通道使能寄存器分区 F |

| XCERE       | 0xA032 | 0xA0B2 | 读/写 | 0x0000 | McBSP 发送通道使能寄存器分区 E |

| XCERF       | 0xA034 | 0xA0B4 | 读/写 | 0x0000 | McBSP 发送通道使能寄存器分区 F |

| RCERG       | 0xA036 | 0xA0B6 | 读/写 | 0x0000 | McBSP 接收通道使能寄存器分区 G |

| RCERH       | 0xA038 | 0xA0B8 | 读/写 | 0x0000 | McBSP 接收通道使能寄存器分区 H |

| XCERG       | 0xA03A | 0xA0BA | 读/写 | 0x0000 | McBSP 发送通道使能寄存器分区 G |

| XCERH       | 0xA03C | 0xA0BC | 读/写 | 0x0000 | McBSP 发送通道使能寄存器分区 H |

| MFFINT      | 0xA046 | 0xA0C6 | 读/写 | 0x0000 | McBSP 中断使能寄存器       |

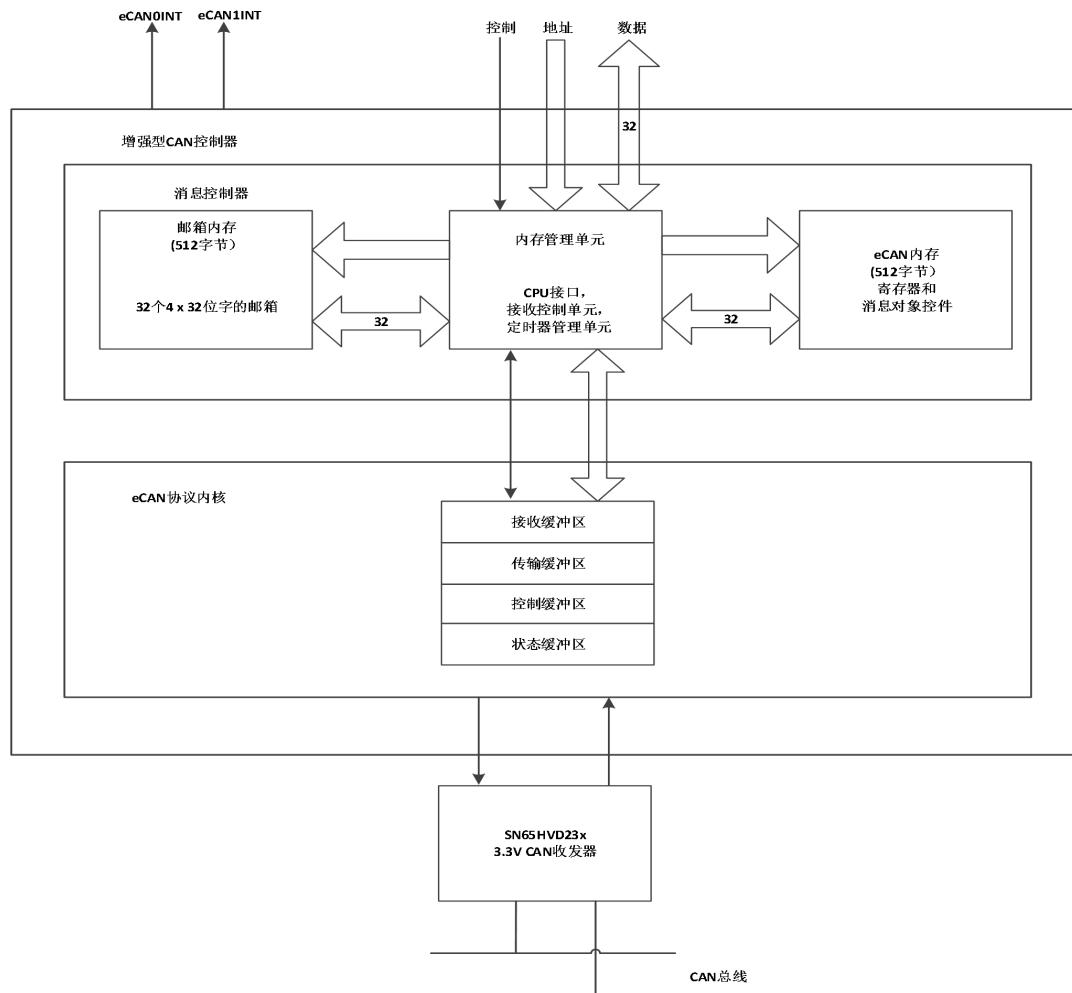

#### 4.4.9. 增强型控制器局域网 (eCAN) 模块(eCAN-A 和 eCAN-B)

CAN 模块有下列特性：

- 与 CAN 协议, 版本 2.0B 完全兼容

- 支持高达 1Mbps 的数据速率

- 32 个邮箱, 每一个邮箱有下列属性:

- 可配置为接收或者发送

- 可使用标准或者扩展标识符进行配置

- 有一个可编辑接收屏蔽

- 支持数据和远程帧

- 由0至8字节数据组成

- 在接收和发送消息上使用一个32位时间戳

- 防止接收新消息

- 保持发送消息的动态可编辑优先级

- 采用一个具有两个中断级别的可编辑中断机制

- 在发送或者接收超时采用一个可编辑报警

- 低功耗模式

- 总线活动上的可编辑唤醒

- 对远程请求消息的自动答复

- 丢失仲裁或者错误情况下的帧自动重传

- 由一个特定消息同步的32位本地网络时间计数器(与邮箱6协同通信)

- 自测模式

- 运行在接收其自身消息的回路模式。 提供一个“假”确认, 从而无需另外节点提供确认位。

图 4-25 eCAN 方框图和接口电路图

表 4-15 3.3V eCAN 收发器

| 器件型号        | 电源电压 | 低功耗模式 | 斜率控制 | VREF | 其它      | TA            |

|-------------|------|-------|------|------|---------|---------------|

| SN65HVD230  | 3.3V | 待机    | 可调节  | 支持   | -       | -40°C 至 85°C  |

| SN65HVD230Q | 3.3V | 待机    | 可调节  | 支持   | -       | -40°C 至 125°C |

| SN65HVD231  | 3.3V | 睡眠    | 可调节  | 支持   | -       | -40°C 至 85°C  |

| SN65HVD231Q | 3.3V | 睡眠    | 可调节  | 支持   | -       | -40°C 至 125°C |

| SN65HVD232  | 3.3V | 无     | 无    | 无    | -       | -40°C 至 85°C  |

| SN65HVD232Q | 3.3V | 无     | 无    | 无    | -       | -40°C 至 125°C |

| SN65HVD233  | 3.3V | 待机    | 可调节  | 无    | 诊断回路    | -40°C 至 125°C |

| SN65HVD234  | 3.3V | 待机和休眠 | 可调节  | 无    | -       | -40°C 至 125°C |

| SN65HVD235  | 3.3V | 待机    | 可调节  | 无    | 自动波特率回路 | -40°C 至 125°C |

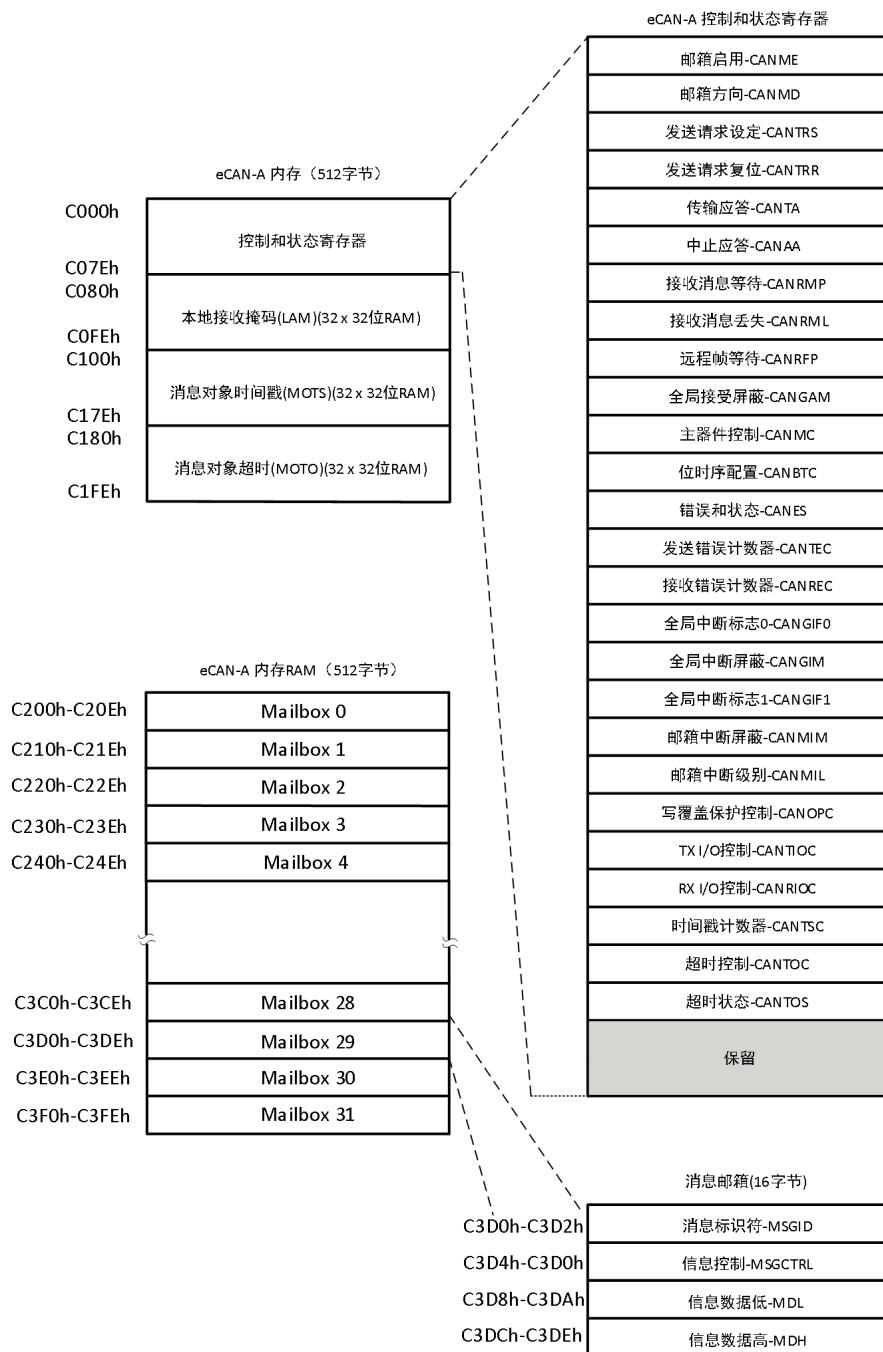

图 4-26 eCAN-A 内存映射

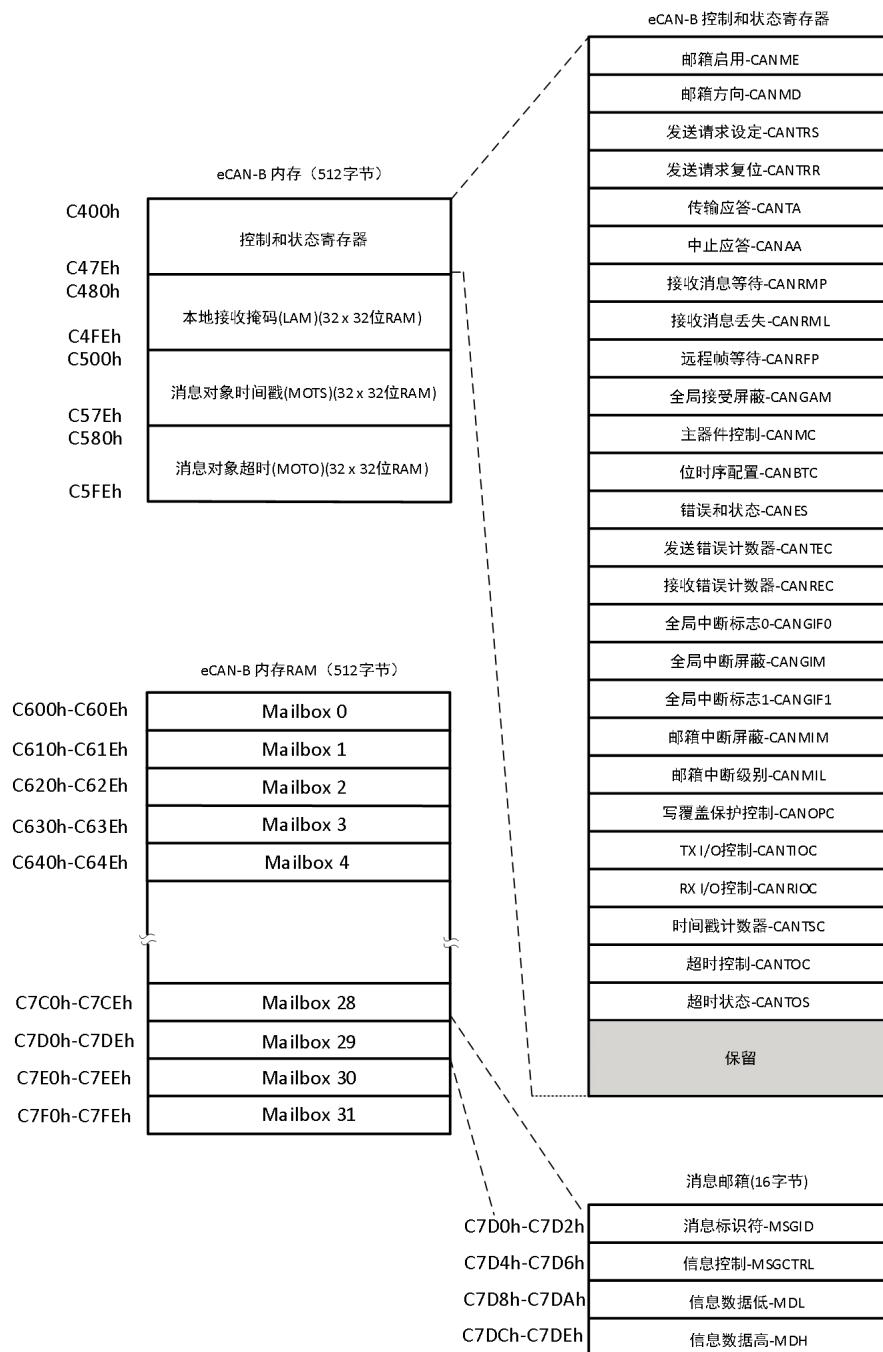

图 4-27 eCAN-B 内存映射

表 4-16 中列出的 CAN 寄存器由 DSP 用于配置和控制 CAN 控制器和消息目标。eCAN 控制寄存器只支持 32 位读取/写入操作。邮箱 RAM 可进行 16 位或者 32 位访问。32 位访问与一个偶边界对齐。

表 4-16 CAN 寄存器映射<sup>(1)</sup>

| 寄存器名称 | eCAN-A 地址 | eCAN-B 地址 | 大小(字节) | 说明 |

|-------|-----------|-----------|--------|----|

|-------|-----------|-----------|--------|----|