# **UMW PCA9535/539/555**

16-bit I2C-bus I/O Expander with Interrupt Output

### 1.Description

The UMW PCA9535 family provides general purpose parallel input and output (GPIO) expansion. Port data is transmitted through the standard I2C protocal, which can support up to 1MHz communication rate (and up to 2MHz when high-speed mode is enabled). The UMW PCA9535 family features a 16-bit totempole I/O ports (P07-P00, P17-P10), which can directly drive LEDs. Each bit of a GPIO port can be individually configured as an input or output. At power on, the I/Os are configured as inputs.

2.Features

- Alternative to UMW PCA9535/9539/9555

- Supply Range: 2.3V~5.5V

- Temperature Range: -40°C ~ +85°C

- Standby Current: 0.5µA

- High-Current Drive Capability

- Open-Drain Active-Low Interrupt Output

### 3.Applications

- Servers

- Routers

- Communication Cabinet

- Industrial Automation

- Products with GPIO-Limited Processors

Jun.2025

16-bit I<sup>2</sup>C-bus I/O Expander with Interrupt Output

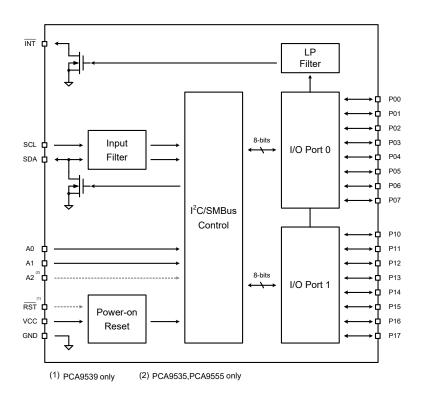

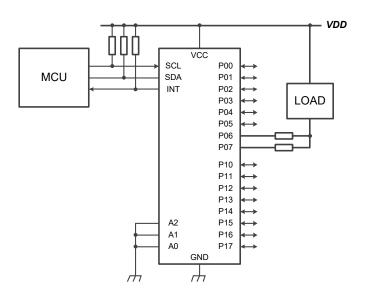

# 4.Block Diagram

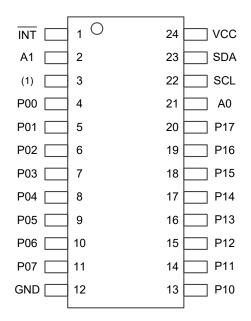

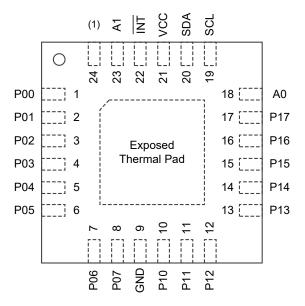

## **5.Pinning Information**

TSSOP-24

**VQFN-24-EP(4x4)**

### (1) RST in PCA9539 . A2 in PCA9535 and PCA9555

|         | PIN   |       | Decerintion                                                                  |

|---------|-------|-------|------------------------------------------------------------------------------|

| Name    | TSSOP | WQFN  | Description                                                                  |

| A0      | 21    | 18    | Address input 0.Connect directly to VCC or GND                               |

| A1      | 2     | 23    | Address input 1. Connect directly to VCC or GND                              |

| A2      | 3     | 24    | Address input 2. Connect directly to VCC or GND                              |

| RST     |       | 24    | Acitve-ow reset input. Connect to VCC through a pull-up resistor if not used |

| GND     | 12    | 9     | Ground.                                                                      |

| INT     | 1     | 22    | Interrupt open-drain output. Connect to VCC through a pull-up resistor       |

| P00~P07 | 4~11  | 1~8   | P-port I/0. At power on, all I/Os are configured as inputs                   |

| P10~P17 | 13~20 | 10~17 | P-port I/0. At power on, all I/Os are configured as inputs                   |

| SCL     | 22    | 19    | Serial clock bus. Connect to VCC through a pull-up resistor                  |

| SDA     | 23    | 20    | Serial data bus. Connect to VCC through a pull-up resistor                   |

| VCC     | 24    | 21    | Supply voltage                                                               |

# **6.Absolute Maximum Ratings**

Over operating free-air temperature range (unless otherwise noted)

| Parameter                      | Min  | Max  | Units |

|--------------------------------|------|------|-------|

| Input Voltage                  | -0.5 | 6    | ٧     |

| Storage Temperature            | -65  | 150  | °C    |

| Input-output Clamp Current     |      | ±20  | mA    |

| Continuous Output Current      |      | ±50  | mA    |

| Continuous Current through GND |      | -250 | mA    |

| Continuous Current through VCC |      | 160  | mA    |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

# 7.ESD Ratings

| Parameter               |                                                   |       | Units |

|-------------------------|---------------------------------------------------|-------|-------|

| Electrostatic Discharge | Human Body Mode (HBM), per ANSI/ESDA/JEDEC JS-001 | ±2000 | V     |

| Latch-up                | Latch-Up, per JESD 78, Class IA                   | ±200  | mA    |

### **8. Electrical Characteristics**

Over temperature range of -40~+85°C and supply range of 1.6~5.5V, unless otherwise noted. Typical values at +25°C and 3.3V.

| Parameter                    | Symbol          | Conditions                                        | Min                | Typ <sup>(1)</sup> | Max                 | Units |

|------------------------------|-----------------|---------------------------------------------------|--------------------|--------------------|---------------------|-------|

| Supply Voltage               | V <sub>cc</sub> |                                                   | 2.3                | 3.3                | 5.5                 | V     |

| Operating Temperature        | T <sub>A</sub>  |                                                   | -40                |                    | 85                  | °C    |

| Quiescent Current            | I <sub>cc</sub> |                                                   |                    | 0.5                | 5                   | μΑ    |

|                              |                 | I <sub>OH</sub> =-8mA, V <sub>CC</sub> =3V        |                    | 2.6                |                     | V     |

| P-port High-level            | V               | I <sub>OH</sub> =-8mA, V <sub>CC</sub> =4.75V     |                    | 4.2                |                     | V     |

| Output Voltage               | $V_{OH}$        | I <sub>OH</sub> =-10mA, V <sub>CC</sub> =3V       |                    | 2.7                |                     | V     |

|                              |                 | I <sub>OH</sub> =-10mA, V <sub>CC</sub> =4.75V    |                    | 4.2                |                     | mA    |

| P-port Low-Level             |                 | V <sub>OL</sub> =0.5V, V <sub>CC</sub> =1.6V~5.5V | 8                  |                    |                     | mA    |

| Output Current               |                 | V <sub>OL</sub> =0.7V, V <sub>CC</sub> =1.6V~5.5V | 10                 |                    |                     | mA    |

| SDA Low-level output Current | I <sub>OL</sub> | V <sub>OL</sub> =0.4V, V <sub>CC</sub> =1.6V~5.5V | 3                  |                    |                     | mA    |

| INT Low-level output Current |                 | V <sub>OL</sub> =0.4V, V <sub>CC</sub> =1.6V~5.5V | 3                  |                    |                     | mA    |

| Input Current                | I <sub>1</sub>  | V <sub>I</sub> =V <sub>CC</sub> or GND            |                    |                    | ±1                  | μA    |

| Input SCL; input/output SDA  |                 |                                                   | •                  | •                  |                     | •     |

| LOW-level input voltage      | V <sub>IL</sub> |                                                   | -0.5               |                    | +0.3V <sub>DD</sub> | V     |

| HIGH-level input voltage     | V <sub>IH</sub> |                                                   | 0.7V <sub>DD</sub> |                    | 5.5                 | V     |

| LOW-level output current     | I <sub>OL</sub> | V <sub>OL</sub> =0.4V                             | 3                  |                    |                     | mA    |

| I/Os                         |                 |                                                   | •                  |                    |                     |       |

| LOW-level input voltage      | V <sub>IL</sub> |                                                   | -0.5               |                    | +0.3V <sub>DD</sub> | V     |

| HIGH-level input voltage     | V <sub>IH</sub> |                                                   | 0.7V <sub>DD</sub> |                    | 5.5                 | V     |

| Select inputs A0, A1, A2     |                 |                                                   | •                  |                    |                     | •     |

| LOW-level input voltage      | $V_{\text{IL}}$ |                                                   | -0.5               |                    | +0.3V <sub>DD</sub> | V     |

| HIGH-level input voltage     | V <sub>IH</sub> |                                                   | 0.7V <sub>DD</sub> |                    | 5.5                 | V     |

### 9. Detailed Description

#### **Port Structure**

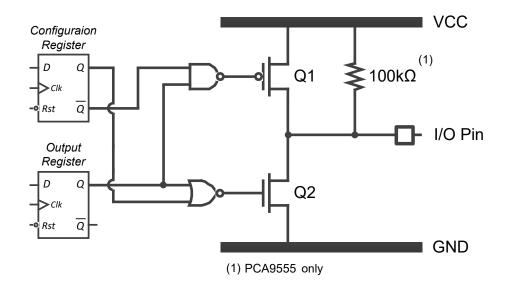

A simplified cicuirt diagram of P-port I/Os is shown in Figure 1.

Figure 1. Simplified Circuit Diagram of P-port I/Os

When an I/O is configured as an input, FETs Q1 and Q2 are off, which create a high-impedance input. The input voltage may be raised above  $V_{cc}$  to a maximum of 5.5V.

When an I/O is configured as an output, Q1 or Q2 is enabled, depending on the state of the Output Port register. In this case, there are low-impedance paths between the I/O pin and either  $V_{CC}$  or GND. The external voltage applied to this I/O pin must not exceed the recommended levels for proper operation.

#### **Register Map**

The PCA95xx register file consists of two sets of symmetric registers that control ports 0 and 1, respectively, in bytes. Each set comprises four 8-bit registers where each bit corresponds to a specific I/O pin; for instance, bit 0 at port 0 corresponds to P00 and so forth. Table 1 lists the pointer address of the register map.

Table 1. Pointer Address and Register Map

| Pointer | Register Name             | Attribution | Default Value |

|---------|---------------------------|-------------|---------------|

| 0x00    | Input Port 0              | R only      | 0xFF          |

| 0x01    | Input Port 1              | R only      | 0xFF          |

| 0x02    | Output Port 0             | R/W         | 0xFF          |

| 0x03    | Output Port 1             | R/W         | 0xFF          |

| 0x04    | Polarity Inversion Port 0 | R/W         | 0x00          |

| 0x05    | Polarity Inversion Port 1 | R/W         | 0x00          |

| 0x06    | Configuration Port 0      | R/W         | 0xFF          |

| 0x07    | Configuration Port 1      | R/W         | 0xFF          |

The Input Port X registers reflect the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by the Configuration Port X register. It only acts on read operation. Writes to these registers have no effect. The power-on default value of this register is all 1.

The Output Port X registers reflect the outgoing logic levels of the pins defined as outputs by the Configuration Port X register. Bit values in this register have no effect on pins defined as inputs. In turn, reads from this register reflect the value that is in the flip-flop controlling the output selection, not the actual pin value.

The Polarity Inversion Port X registers allow the user to invert the polarity of the Input Port X register data. If a bit in this register is set to 1, the Input Port X register data polarity is inverted. If a bit in this register is cleared to 0, the Input Port X register data polarity is retained.

The Configuration Port X registers configure the directions of the I/O pins. If a bit in this register is set to 1, the corresponding port pin is enabled as an input with a high-impedance output driver. If a bit in this register is cleared to 0, the corresponding port pin is enabled as an output.

### 10.Serial Interface

#### **Bus Overview**

I2C/SMBus is a two-wire serial communication interface supporting multi-master and multi-slave. The device that initiates the communication is called the master, and the device controlled by the master is called the slave. The master is responsible for generating the serial clock (SCL) and controlling the bus access.

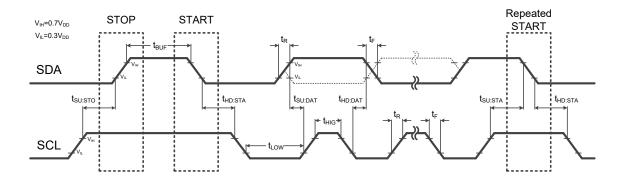

Data transfer is sent over eight clock pulses followed by an acknowledge bit. During data transfer, SDA must remain stable when SCL is high because any change in SDA while SCL is high is interpreted as a START or STOP conditions. Parameters for Figure 2 are defined in Table 2.

Table 2. Timing Diagram Requirements

| Symbol              | Parameter                            | Fast Mode |     | High-speed Mode |      |      |

|---------------------|--------------------------------------|-----------|-----|-----------------|------|------|

| Зупівої             | raiailietei                          | Min       | Max | Min             | Max  | Unit |

| f <sub>SCL</sub>    | SCL operating frequency              | 1         | 400 | 1               | 2000 | us   |

| t <sub>su:sta</sub> | Repeated START condition setup time  | 0.6       | -   | 0.26            | -    | us   |

| t <sub>HD:STA</sub> | Repeated START condition hold time   | 0.6       | -   | 0.26            | -    | us   |

| t <sub>su:sto</sub> | STOP condition setup time            | 0.6       | -   | 0.26            | -    | us   |

| t <sub>BUF</sub>    | Bus free time between STOP and START | 1.3       | -   | 0.5             | -    | us   |

| t <sub>su:dat</sub> | Data setup time                      | 0.1       | -   | 0.05            | -    | us   |

| t <sub>HD:DAT</sub> | Data hold time                       | 0         | -   | 0               | -    | us   |

| t <sub>HIG</sub>    | SCL clock high period                | 0.6       | -   | 0.26            | -    | us   |

| t <sub>Low</sub>    | SCL clock low period                 | 1.3       | -   | 0.5             | -    | us   |

| t <sub>R</sub>      | Clock and data rise time             | -         | 300 | -               | 120  | ns   |

| t <sub>F</sub>      | Clock and data fall time             | -         | 300 | -               | 120  | ns   |

16-bit I<sup>2</sup>C-bus I/O Expander with Interrupt Output

Figure 2. Two-Wire Timing Diagram

#### **Serial Bus Address**

The PCA9535 and PCA9555 feature three address pins that allow up to eight devices to be addressed on a single bus. The PCA9539 features two address pins that allow up to four devices to be addressed on a single bus. Table 2 describes the pin logic levels and the corresponding address values. It is crucial for the logic level of the address pin to remain consistent throughout communication in order to avoid potential failures. The address pin must be connected either to VCC or GND and should not be left in a suspended state.

The slave address byte consists of seven address bits, and a direction bit indicating the intent of executing either a read or write operation. All data bytes are transmitted MSB first.

Table 3. Address Pin Connection and Slave Address

| Device Name | A2  | <b>A</b> 1 | Α0  | Device Two-wire Address   |

|-------------|-----|------------|-----|---------------------------|

|             | GND | GND        | GND | 0x40 (write),0x41(read)   |

|             | GND | GND        | VCC | 0x42 (write),0x43 (read)  |

|             | GND | VCC        | GND | 0x44 (write),0x45 (read)  |

| PCA9535     | GND | VCC        | VCC | 0x46 (write), 0x47 (read) |

| PCA9555     | VCC | GND        | GND | 0x48 (write), 0x49 (read) |

|             | VCC | GND        | VCC | 0x4A (write), 0x4B(read)  |

|             | VCC | VCC        | GND | 0x4C (write), 0x4D (read) |

|             | VCC | VCC        | VCC | 0x4E (write), 0x4F(read)  |

|             | -   | GND        | GND | 0xE8 (write), 0xE9 (read) |

| DOAO520     | -   | GND        | VCC | 0xEA (write), 0xEB (read) |

| PCA9539     | -   | VCC        | GND | 0xEC (write), 0xED (read) |

|             | -   | VCC        | VCC | 0xEE (write), 0xEF(read)  |

### **Writing and Reading Operation**

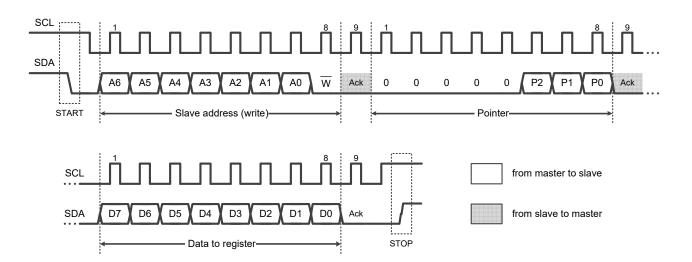

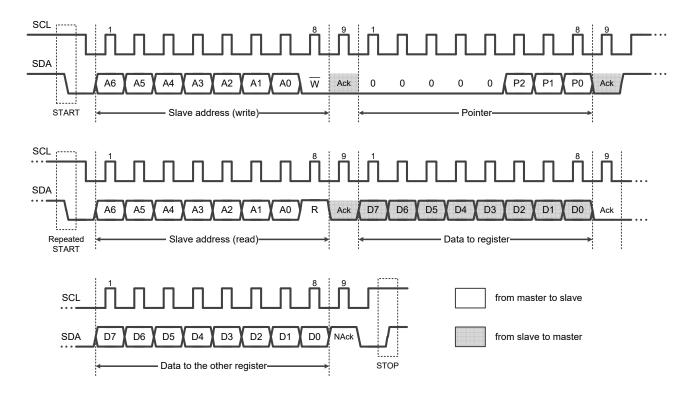

If the R/W bit is 0b, the first byte sent by the host after the slave address byte is recognized as a pointer. The PCA9535 family uses the pointer to specify the target register of the current read or write operation. The data byte follows the pointer byte and represents the data to be written to the specified register. The specific bus timing is shown in Figure 3 and consists of start condition, address byte, pointer byte, data byte and stop condition. The PCA9535 family pulls down the SDA bus at the ninth clock pulse to indicate that the byte has been received and is ready to receive a new byte.

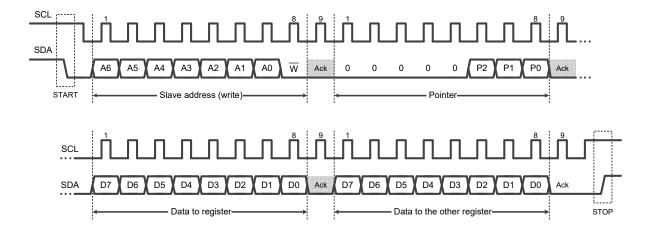

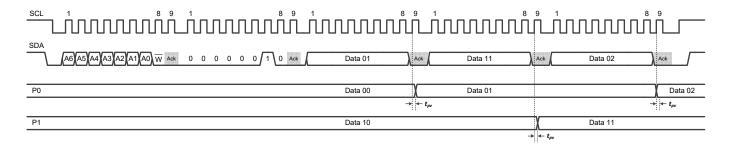

The PCA9535 family features a pointer automatic shift function. After each register access is completed, the pointer points to the other register of the same type. For example, after the current byte is written to the Output Port 0 register, the next byte is written to the Output Port 1 register, the next byte is written back to the Output Port 0 register, and so on. The specific bus timing is shown in Figure 4.

Figure 3. Two-Wire Timing Diagram for Write One Byte

Figure 4. Two-Wire Timing Diagram for Write Two Bytes

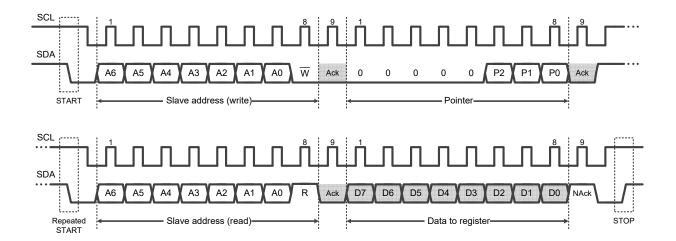

If the R/W bit is 1b, then the host can start reading data bytes after the slave address byte. The content of the data is determined by the pointer. Therefore, in the read operation, the host needs to modify the pointer first, and then restart a round of communication to read the target data. The specific bus timing is shown in Figure 5.

Figure 5. Two-Wire Timing Diagram for Read One Byte

Read operations support multi-byte access. The specific bus timing is shown in Figure 6.

Figure 6. Two-Wire Timing Diagram for Read Two Bytes

#### **Port Control**

The PCA9535 family controls the output of an I/O pin assuming that the pin has been configured in output mode. The impact of the Output Port X register on the control of the I/O ports is illustrated in Figure 7. The PCA9535 family flushes the received data to the I/O pins at the rising edge of SCL for each Ack of data bytes

Figure 7. Write to Output Port X Registers

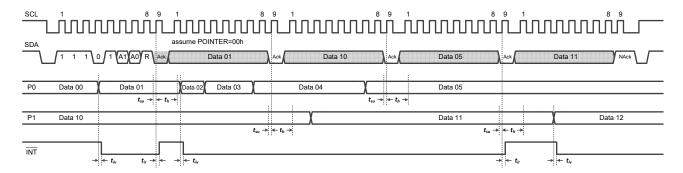

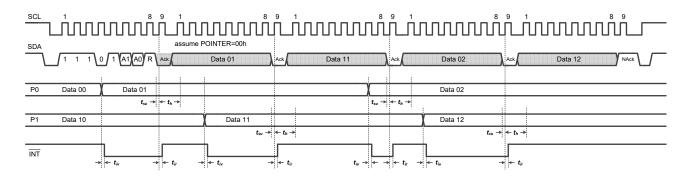

The PCA9535 family is capable of acquiring the logic level of the I/O pin in both input and output configurations. The impact of reading the input register on the interrupt signal can be observed in Figures 8 and 9. During each Ack of data bytes, the PCA9535 family samples the logic level of the I/O pin into the input register at the rising edge of SCL, subsequently clearing the interrupt.

Figure 8. Read Input Port Registers, Scenario 1

Figure 9. Read Input Port Registers, Scenario 2

Table 4. Switching Characteristics

| Symbol          | Parameter              | From | То   | Min | Тур | Max | Unit |

|-----------------|------------------------|------|------|-----|-----|-----|------|

| t <sub>pv</sub> | Outpu Data Valid Time  | SCL  | GPIO |     |     | 1   | us   |

| t <sub>su</sub> | Input Data Setupt Time | GPIO | SCL  |     | 1   |     | us   |

| t <sub>h</sub>  | Input Data Hold Time   | GPIO | SCL  |     | 1   |     | us   |

| t <sub>iv</sub> | Interrupt Valid Time   | GPIO | INT  |     |     | 4   | us   |

| t <sub>ir</sub> | Interrupt Reset Delay  | SCL  | INT  |     |     | 4   | us   |

| t <sub>w</sub>  | Reset Pulse Duration   | -    | -    | 10  |     |     | ns   |

#### High-Speed (Hs) Mode

For the I<sup>2</sup>C bus to operate at frequencies above 1 MHz, the master device must issue an Hs-mode master code (0000 1xxx) as the first byte after a START condition to switch the bus to high-speed operation. The PCA9535 family does not acknowledge this byte, but switches the input filters on the SDA and SCL pins and the output filters on the SDA pin to operate in Hs-mode, thus allowing transfers at up to 2 MHz. After the Hs-mode master code has been issued, the master transmits an I <sup>2</sup>C slave address to initiate a data-transfer operation. The bus continues to operate in Hs-mode until a STOP condition occurs on the bus. Upon receiving the STOP condition, the PCA9535 family switches the input and output filters back to fast-mode operation.

#### **Interrupt Output**

The PCA9535 family features an open-drain output interrupt pin that can be directly connected to the microprocessor's interrupt input. By transmitting an interrupt signal, the chip can actively notify the microprocessor of any changes in logic level on the remote I/O pin.

There are three crucial aspects to consider regarding the establishment and removal of interrupt signals:

- The interrupt signal will only be triggered by a change in the logic level of the I/O pin configured as input.

- The interrupt signal is not latched. If the I/O pin logic level is restored to its previous sampled state, the interrupt signal will be immediately cleared.

- An interrupt signal set that occurs near the Ack bit may be lost.

#### **Reset Input**

The has an external reset input pin. By pulling down the RST and maintaining the tw time, the host can realize the reset operation to the chip. The chip will reset all the communication state machine and internal register file to the power-on default state. If no reset operation is required, the RST pin must be connected to V<sub>CC</sub>.

#### **Quick Feature Guide**

Table 5. Selection Table

| Device  | Туре       | I/O | Address   | Built-in | Reset Input |

|---------|------------|-----|-----------|----------|-------------|

| PCA9535 | Totem-pole | 16  | 0100 xxxb |          |             |

| PCA9539 | Totem-pole | 16  | 1110 1xxb |          | √           |

| PCA9555 | Totem-pole | 16  | 0100 xxxb | V        |             |

#### **High Current-Drive Load Application**

The I/O pins of the PCA9535 family are capable of driving with a minimum perfusion current of 10mA. Additionally, it is possible to connect multiple I/O pins together through short-wiring in order to enhance the current-driven capability. As illustrated in Figure 10, individual current limiting resistors are necessary for each I/O pin and proper synchronization of switches is required to prevent any potential damage to the chip.

Figure 10. High Current-Drive Load Application

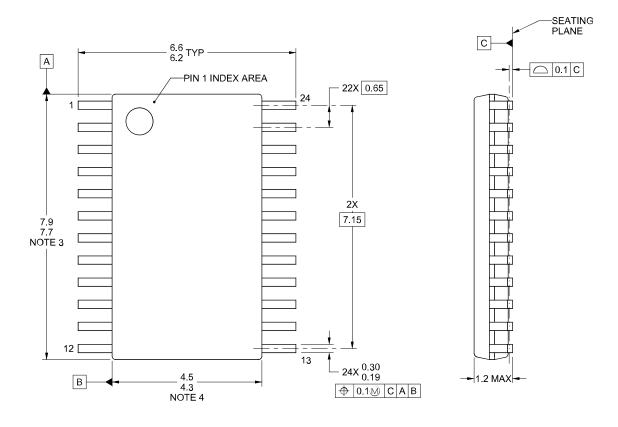

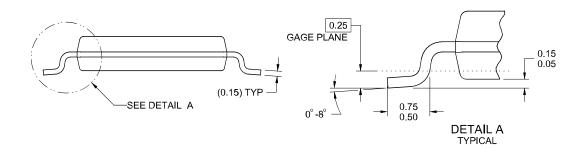

# 11.1 TSSOP-24 Package Outline Dimensions

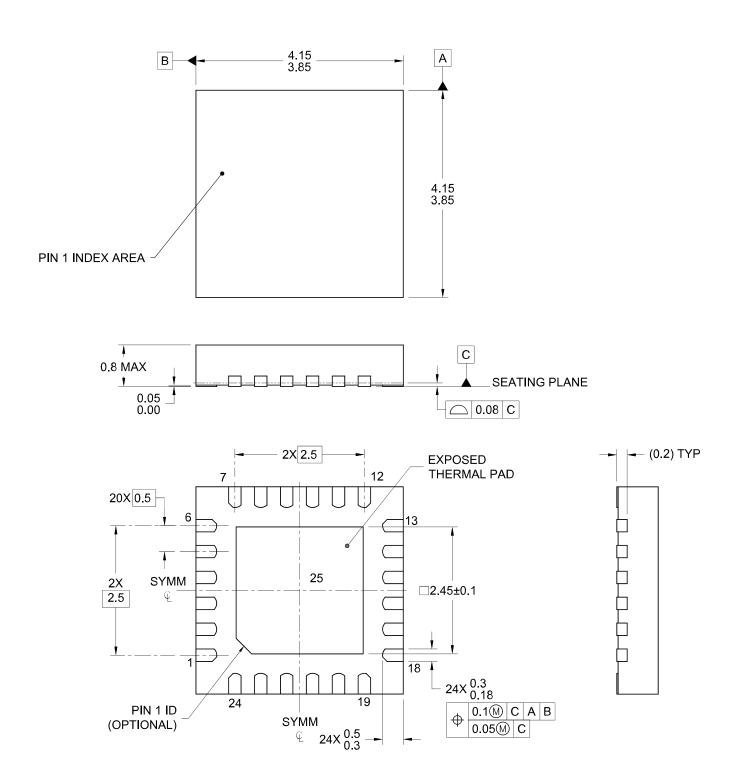

# 11.2 WQFN-24-EP(4x4) Package Outline Dimensions

# 12. Ordering information

PCA9535PW UMW yyww

yy: Year Code ww: Week Code

| Order Code      | Marking   | Package         | Base QTY | Delivery Mode |

|-----------------|-----------|-----------------|----------|---------------|

| UMW PCA9535PW   | PCA9535PW | TSSOP-24        | 4000     | Tape and reel |

| UMW PCA9539PW   | PCA9539PW | TSSOP-24        | 4000     | Tape and reel |

| UMW PCA9555PW   | PCA9555PW | TSSOP-24        | 4000     | Tape and reel |

| UMW PCA9555RGER | PCA9555RG | VQFN-24-EP(4x4) | 4000     | Tape and reel |

### 13.Disclaimer

UMW reserves the right to make changes to all products, specifications. Customers should obtain the latest version of product documentation and verify the completeness and currency of the information before placing an order.

When applying our products, please do not exceed the maximum rated values, as this may affect the reliability of the entire system. Under certain conditions, any semiconductor product may experience faults or failures. Buyers are responsible for adhering to safety standards and implementing safety measures during system design, prototyping, and manufacturing when using our products to prevent potential failure risks that could lead to personal injury or property damage.

Unless explicitly stated in writing, UMW products are not intended for use in medical, life-saving, or life-sustaining applications, nor for any other applications where product failure could result in personal injury or death. If customers use or sell the product for such applications without explicit authorization, they assume all associated risks.

When reselling, applying, or exporting, please comply with export control laws and regulations of China, the United States, the United Kingdom, the European Union, and other relevant countries, regions, and international organizations.

This document and any actions by UMW do not grant any intellectual property rights, whether express or implied, by estoppel or otherwise. The product names and marks mentioned herein may be trademarks of their respective owners.