# 16-Channel, 12-/16-Bit Voltage Output SoftSpan DAC

## **FEATURES**

- ▶ 16 independent SoftSpan DAC channels

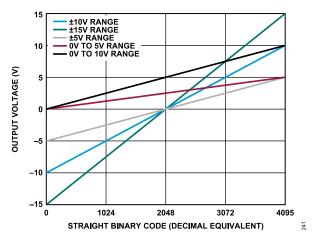

- ▶ Independently programmable output ranges: 0 V to 5 V, 0 V to 10 V, ±5 V, ±10 V, ±15 V

- ▶ Full 12-/16-bit resolution at all ranges

- ▶ Flexible single- or dual-supply operation

- ▶ Maximum INL error: ±3 LSB<sub>16</sub>, ±0.75 LSB<sub>12</sub>

- ▶ Precision 4.096 V reference, ±5 ppm/°C maximum

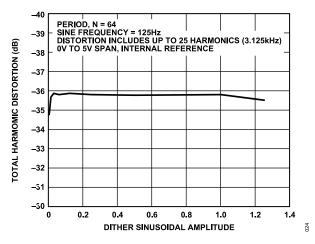

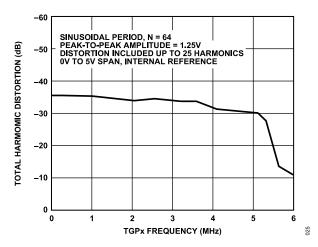

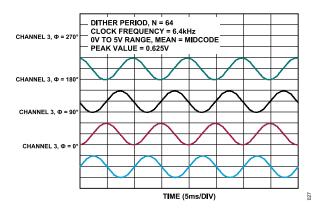

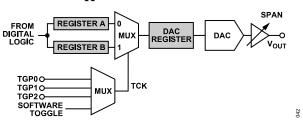

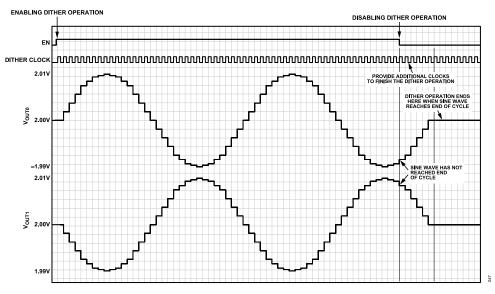

- ▶ A/B toggle or sinusoidal dither using up to 3 toggle pins

- ▶ Multiplexer for output voltage and load current sense

- ▶ Outputs drive ±20 mA guaranteed

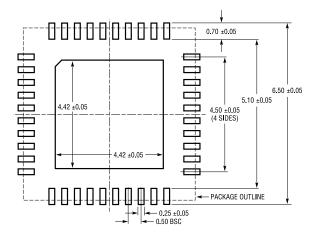

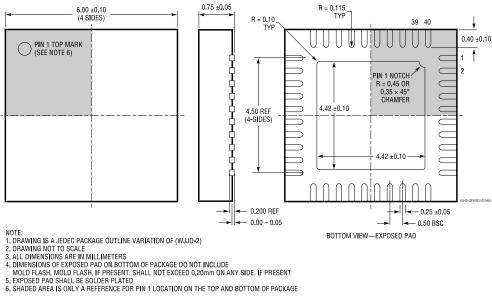

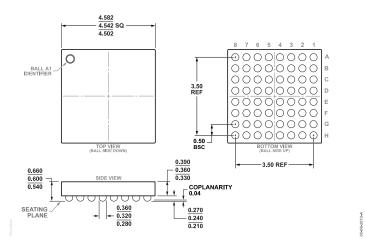

- ▶ 6 mm × 6 mm, 40-lead LFCSP and 4.5 mm × 4.5 mm, 64-ball WLCSP

## **APPLICATIONS**

- Optical networking

- Instrumentation

- ▶ Data acquisition

- Automatic test equipment

- Process control and industrial automation

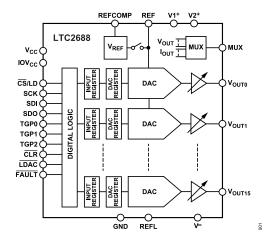

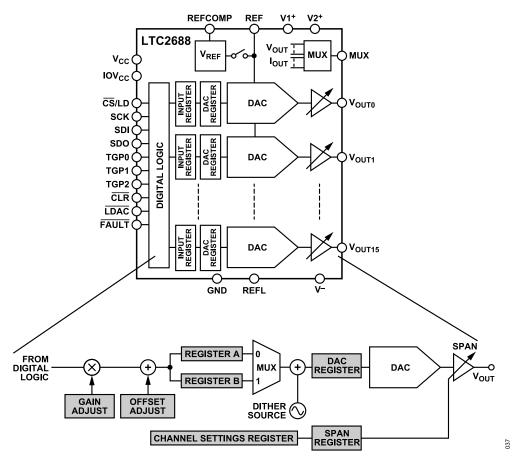

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

## **GENERAL DESCRIPTION**

The LTC2688 is a 16-channel,12-/16-bit, ±15 V digital-to-analog converter (DAC) with an integrated precision reference. The LTC2688 is guaranteed monotonic and has built in rail-to-rail output buffers that can source or sink up to 20 mA. This SoftSpan™ DAC offers five output ranges up to ±15 V. The range of each channel is independently programmable.

The internal 4.096 V precision reference sets the accuracy of the output voltage. An external reference can be used for additional range options. Three toggle pins support Input Register A and Input Register B toggle or sinusoidal dither at multiple frequencies. An analog multiplexer simplifies measurement of pin voltages, load currents, and junction temperature.

Programmable offset and gain registers improve the accuracy of the DAC outputs.

The serial peripheral interface (SPI) and MICROWIRE<sup>™</sup>-compatible, 3-wire serial interface operates on logic levels as low as 1.71 V and clock rates up to 50 MHz.

# **TABLE OF CONTENTS**

| Features                                    | 1 | Read Commands                      | 24 |

|---------------------------------------------|---|------------------------------------|----|

| Applications                                | 1 | Offset and Gain Adjustment         | 26 |

| Functional Block Diagram                    | 1 | Analog Mux                         |    |

| General Description                         |   | Toggle and Dither Operation        |    |

| Specifications                              |   | Daisy-Chain Mode                   |    |

| Timing Characteristics                      |   | Power-Down Mode                    | 36 |

| Absolute Maximum Ratings                    |   | Asynchronous DAC Update Using LDAC |    |

| Thermal Resistance                          |   | Fault Detection                    | 38 |

| Electrostatic Discharge (ESD) Ratings       |   | Configuration Register             |    |

| ESD Caution                                 |   | Reference Modes                    |    |

| Pin Configuration and Function Descriptions |   | Voltage Outputs                    |    |

| Typical Performance Characteristics         |   | Thermal Overload Protection        |    |

| Terminology                                 |   | Applications Information           |    |

| Theory of Operation                         |   | Printed Circuit Board Layout       |    |

| Power-On Reset                              |   | Command Addresses                  |    |

| Power Supply Sequencing                     |   | Outline Dimensions                 |    |

| Serial Interface                            |   | Ordering Guide                     |    |

| Writing Codes to DACs                       |   | Evaluation Boards                  |    |

| Span Selection and Channel Settings         |   | LValidation Boards                 | 40 |

| REVISION HISTORY                            |   |                                    |    |

| 1/2023—Rev. B to Rev. C                     |   |                                    | _  |

| Changes to Table 2                          |   |                                    | 6  |

| 11/2022—Rev. A to Rev. B                    |   |                                    |    |

|                                             |   |                                    | 1  |

| •                                           |   |                                    |    |

| •                                           |   |                                    |    |

| ·                                           |   |                                    |    |

| <u> </u>                                    |   |                                    |    |

| •                                           |   | nd Figure 28 Caption               |    |

|                                             |   | 3; Renumbered Sequentially         |    |

|                                             | • | -, ·,                              |    |

| ·                                           |   |                                    |    |

| •                                           |   |                                    |    |

| •                                           |   |                                    |    |

|                                             |   |                                    |    |

|                                             |   |                                    |    |

|                                             |   |                                    |    |

|                                             |   |                                    |    |

|                                             |   |                                    |    |

|                                             |   |                                    |    |

|                                             |   |                                    |    |

| •                                           |   |                                    |    |

| · · ·                                       |   |                                    |    |

| Onanges to Evaluation boards                |   |                                    | 4c |

| 8/2022—Rev. 0 to Rev. A                     |   |                                    |    |

| Added 64-Ball WLCSP (Universal)             |   |                                    | 1  |

# **TABLE OF CONTENTS**

| Changes to Features Section                                                              | 1  |

|------------------------------------------------------------------------------------------|----|

| Changes to Figure 1                                                                      | 1  |

| Changes to Reference Temperature Coefficient Parameter and Output Noise Spectral Density |    |

| Parameter, Table 1                                                                       | 4  |

| Added Electrostatic Discharge (ESD) Ratings Section                                      |    |

| Changes to Table 4                                                                       |    |

| Added ESD Ratings for LTC2688 Section and Table 5; Renumbered Sequentially               | 8  |

| Added Figure 4 and Table 7; Renumbered Sequentially                                      | 10 |

| Changes to Figure 5 Caption                                                              |    |

| Changes to Figure 43                                                                     |    |

| Changes to Power Supply Sequencing Section                                               | 20 |

| Changes to Figure 44                                                                     |    |

| Changes to Figure 47 Caption                                                             |    |

| Changes to Analog Mux Section                                                            | 28 |

| Changes to Figure 48                                                                     | 29 |

| Changes to Toggle Operations Example Section                                             |    |

| Changes to Figure 50                                                                     | 30 |

| Changes to Printed Circuit Board Layout Section                                          |    |

| Change to Table 39                                                                       | 42 |

| Updated Outline Dimensions                                                               | 44 |

| Changes to Ordering Guide                                                                | 45 |

| Changes to Evaluation Boards                                                             | 45 |

# 6/2021—Revision 0: Initial Version

# **SPECIFICATIONS**

All specifications apply over the full operating temperature range, unless otherwise noted. Typical values are at  $T_A$  = 25°C.  $V_{CC}$  = 5 V,  $IOV_{CC}$  = 5 V,  $V^+$  = 15 V,  $V^-$  = -15 V,  $V_{REF}$  = 4.096 V,  $V_{OUT}$  unloaded, unless otherwise specified. For ±15 V range,  $V^+$  = 18 V,  $V^-$  = -18 V.

Table 1.

| Parameter                                                                                         | Symbol           | Test Conditions/Comments                                                                                                       | Min       | Тур           | Max                  | Unit               |

|---------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|----------------------|--------------------|

| OC PERFORMANCE                                                                                    |                  |                                                                                                                                |           |               |                      |                    |

| LTC2688-16                                                                                        |                  |                                                                                                                                |           |               |                      |                    |

| Resolution                                                                                        |                  |                                                                                                                                | 16        |               |                      | Bits               |

| Monotonicity                                                                                      |                  | All ranges <sup>1</sup>                                                                                                        | 16        |               |                      | Bits               |

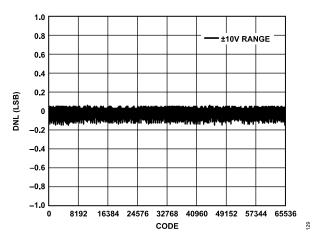

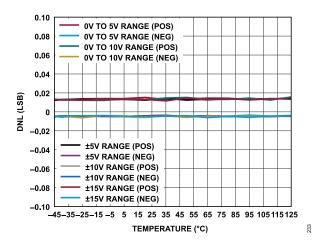

| Differential Nonlinearity                                                                         | DNL              | All ranges <sup>1</sup>                                                                                                        |           |               | ±1                   | LSB                |

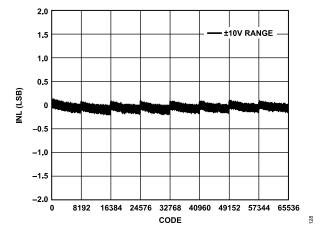

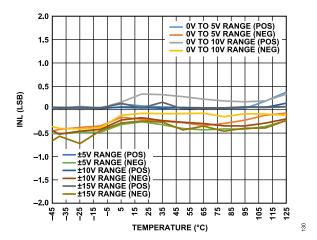

| Integral Nonlinearity                                                                             | INL              | All ranges <sup>1</sup>                                                                                                        |           |               | ±3                   | LSB                |

| LTC2688-12                                                                                        |                  |                                                                                                                                |           |               |                      |                    |

| Resolution                                                                                        |                  |                                                                                                                                | 12        |               |                      | Bits               |

| Monotonicity                                                                                      |                  | All ranges <sup>1</sup>                                                                                                        | 12        |               |                      |                    |

| Differential Nonlinearity                                                                         | DNL              | All ranges <sup>1</sup>                                                                                                        |           |               | ±0.25                | LSB                |

| Integral Nonlinearity                                                                             | INL              | All ranges <sup>1</sup>                                                                                                        |           |               | ±0.75                | LSB                |

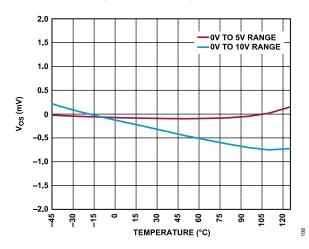

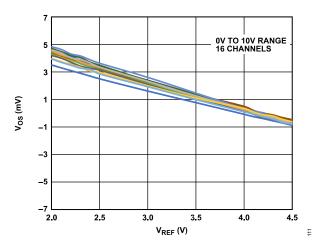

| Unipolar Offset Error                                                                             | Vos              | 0 V to 5 V range                                                                                                               |           | ±0.5          | <u>±2</u>            | mV                 |

|                                                                                                   |                  | 0 V to 10 V range                                                                                                              |           | ±1            | <u>±</u> 4           | mV                 |

| V <sub>OS</sub> Temperature Coefficient                                                           |                  | All unipolar ranges                                                                                                            |           | 1             |                      | ppm/°C             |

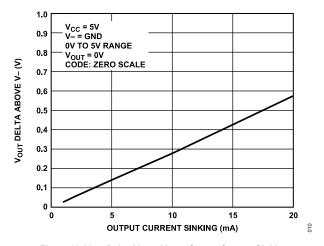

| Single-Supply Zero-Scale Error                                                                    | ZSE              | All unipolar ranges, V⁻ = GND                                                                                                  |           | 2             | 4                    | mV                 |

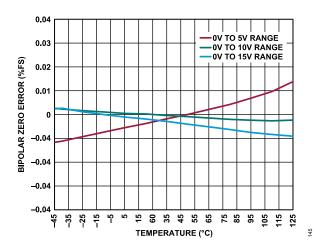

| Bipolar Zero Error                                                                                | BZE              | All bipolar ranges                                                                                                             |           |               | ±0.04                | % FSR <sup>2</sup> |

| BZE Temperature Coefficient                                                                       |                  | All bipolar ranges                                                                                                             |           | 2             |                      | ppm/°C             |

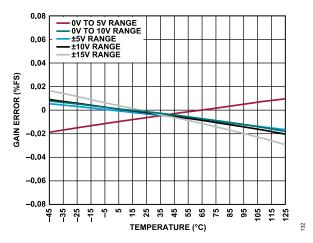

| Gain Error                                                                                        | GE               | All ranges, external reference                                                                                                 |           |               | ±0.08                | % FSR              |

| Gain Temperature Coefficient                                                                      |                  |                                                                                                                                |           | 2             |                      | ppm/°C             |

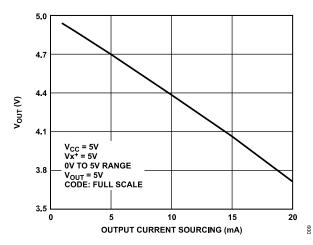

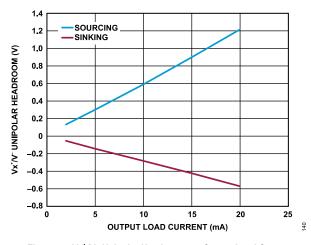

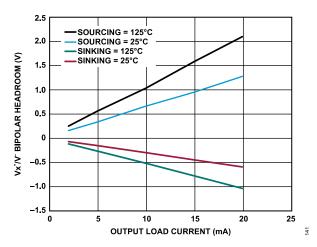

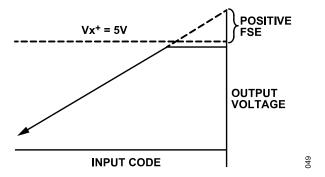

| Output Voltage Swing                                                                              | V <sub>OUT</sub> | To V⁻ (unloaded)                                                                                                               |           | $V^- + 0.004$ |                      | V                  |

|                                                                                                   |                  | To Vx <sup>+</sup> (unloaded)                                                                                                  |           | Vx+ - 0.004   |                      | V                  |

|                                                                                                   |                  | To V <sup>-</sup> (-20 mA $\leq$ output current (I <sub>OUT</sub> ) $\leq$ +20 mA), $\pm$ 15 V range                           |           |               | V <sup>-</sup> + 2.2 | V                  |

|                                                                                                   |                  | To Vx <sup>+</sup> (-20 mA $\leq$ I <sub>OUT</sub> $\leq$ +20 mA), ±15 V range                                                 | Vx+ - 2.2 |               |                      | V                  |

| Power Supply Rejection                                                                            | PSR              | $V_{CC} = 5 V \pm 5\%$                                                                                                         |           | -80           |                      | dB                 |

|                                                                                                   |                  | $Vx^{+}/V^{-} = 15 V \pm 5\%$                                                                                                  |           | -80           |                      | dB                 |

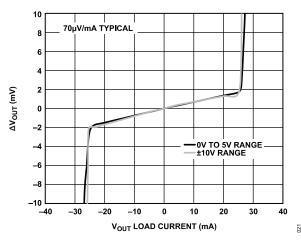

| Load Regulation                                                                                   |                  | $-20 \text{ mA} \le I_{OUT} \le +20 \text{ mA}, Vx^+ = +17.2 \text{ V}, V^- = -17.2 \text{ V}, \pm 15 \text{ V} \text{ range}$ |           | 70            | 150                  | μV/mA              |

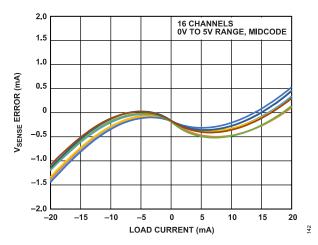

| DC Crosstalk <sup>3</sup> , 0 V to 5 V Range                                                      |                  | Due to full-scale output change                                                                                                |           | ±2            |                      | μV                 |

| -                                                                                                 |                  | Due to load current change                                                                                                     |           | ±1            |                      | μV/mA              |

|                                                                                                   |                  | Due to powering down (per channel)                                                                                             |           | ±4            |                      | μV                 |

| Vx <sup>+</sup> /V <sup>-</sup> Short-Circuit Output Current <sup>4</sup> , ±15 V<br>Output Range | I <sub>SC</sub>  | Negative full scale, forcing output to GND                                                                                     | -41       |               |                      | mA                 |

|                                                                                                   |                  | Positive full scale, forcing output to GND                                                                                     |           |               | 41                   | mA                 |

| REFERENCE                                                                                         |                  |                                                                                                                                |           |               |                      |                    |

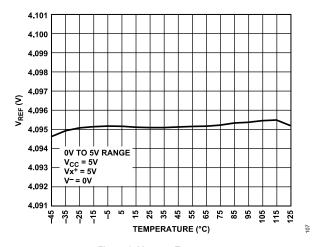

| Reference Output Voltage <sup>5</sup>                                                             |                  |                                                                                                                                | 4.094     | 4.096         | 4.098                | V                  |

|                                                                                                   |                  | $T_A = T_{MIN}$ to $T_{MAX}$                                                                                                   | 4.092     | 4.096         | 4.100                | V                  |

| Reference Temperature Coefficient <sup>6</sup>                                                    |                  |                                                                                                                                |           |               |                      |                    |

| LFCSP Package                                                                                     |                  |                                                                                                                                |           | ±2            | ±5                   | ppm/°C             |

| WLCSP Package                                                                                     |                  |                                                                                                                                |           | ±5            |                      | ppm/°C             |

| Line Regulation                                                                                   |                  | V <sub>CC</sub> ± 5%                                                                                                           |           | -80           |                      | dB                 |

| Short-Circuit Current                                                                             |                  | Forcing output to GND                                                                                                          |           | 0.1           |                      | mA                 |

| REFCOMP Pin Short-Circuit Current                                                                 |                  | Forcing output to GND                                                                                                          |           | 10            |                      | μA                 |

| Load Regulation                                                                                   |                  | I <sub>OUT</sub> = 1 μA                                                                                                        |           | 320           |                      | mV/mA              |

| Output Voltage Noise Density                                                                      |                  | REFCOMP, capacitor (C <sub>REFCOMP</sub> ) = REF<br>capacitor (C <sub>REF</sub> ) = 0.1 µF, at f = 10 kHz                      |           | 32            |                      | nV/√Hz             |

analog.com Rev. C | 4 of 45

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter                                 | Symbol              | Test Conditions/Comments                                       | Min                   | Тур  | Max                   | Unit           |

|-------------------------------------------|---------------------|----------------------------------------------------------------|-----------------------|------|-----------------------|----------------|

| REFERENCE INPUT                           |                     |                                                                |                       |      |                       |                |

| Range                                     |                     | External reference mode <sup>7</sup>                           | 2.0                   |      | $V_{CC} - 0.6$        | V              |

| Current                                   |                     |                                                                |                       | 10   | 15                    | μA             |

| Capacitance                               |                     |                                                                |                       | 8    |                       | pF             |

| POWER SUPPLY                              |                     |                                                                |                       |      |                       | † <del>`</del> |

| Analog Supply Voltage                     | V <sub>CC</sub>     |                                                                | 4.75                  |      | 5.25                  | V              |

| Analog Positive Supply                    | V1 <sup>+</sup>     |                                                                | V <sub>CC</sub> - 0.3 |      | V <sup>-</sup> + 42   | V              |

| rulaing recitive cupping                  | V2 <sup>+</sup>     |                                                                | V <sub>CC</sub> - 0.3 |      | V1 <sup>+</sup> + 0.3 | V              |

| Analog Negative Supply                    | V-                  |                                                                | -21                   |      | 0                     | V              |

|                                           |                     |                                                                | 1.71                  |      | -                     | V              |

| Digital Input/Output (I/O) Supply Voltage | IOV <sub>CC</sub>   |                                                                | 1.71                  |      | $V_{CC}$ + 0.3        | \ \ \          |

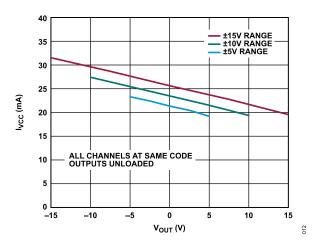

| Supply Current                            | N/                  | V 5V 0V 5V                                                     |                       | 04.0 |                       | ١.             |

| V <sub>CC</sub> <sup>8</sup>              | IV <sub>CC</sub>    | V <sub>CC</sub> = 5 V; 0 V to 5 V range                        |                       | 21.9 |                       | mA             |

|                                           |                     | V <sub>CC</sub> = 5 V; 0 V to 10 V range                       |                       | 22.3 |                       | mA             |

|                                           |                     | V <sub>CC</sub> = 5 V; ±5 V range                              |                       | 25.6 |                       | mA             |

|                                           |                     | V <sub>CC</sub> = 5 V; ±10 V range                             |                       | 29.6 |                       | mA             |

|                                           |                     | V <sub>CC</sub> = 5 V; ±15 V range                             |                       | 33.6 | 37.0                  | mA             |

| Vx+/V <sup>-9</sup>                       | Is                  | Vx <sup>+</sup> /V <sup>-</sup> = ±15 V; 0 V to 5 V range      |                       | 6.4  |                       | mA             |

|                                           |                     | Vx <sup>+</sup> /V <sup>-</sup> = ±15 V; 0 V to 10 V range     |                       | 6.4  |                       | mA             |

|                                           |                     | Vx <sup>+</sup> /V <sup>-</sup> = ±15 V; ±5 V range            |                       | 8.3  |                       | mA             |

|                                           |                     | $Vx^{+}/V^{-} = \pm 15 \text{ V}; \pm 10 \text{ V range}$      |                       | 10.8 |                       | mA             |

|                                           |                     | $Vx^{+}/V^{-} = \pm 15 \text{ V}; \pm 15 \text{ V range}$      |                       | 13   | 15                    | mA             |

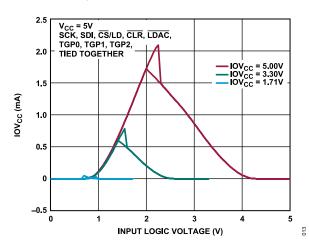

| IOV <sub>CC</sub>                         | 1                   | $IOV_{CC} = 5 \text{ V}$ , digital inputs at $IOV_{CC}$ or GND |                       | 0.05 | 1                     | μA             |

|                                           | I <sub>IOVCC</sub>  | 10 v CC = 3 v, digital lilputs at 10 v CC of GND               |                       | 0.03 | 1                     | μΑ             |

| Shutdown Supply Current                   |                     | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                          |                       | 00   |                       | ١.             |

| V <sub>CC</sub>                           |                     | $V_{CC} = 5 V$                                                 |                       | 20   |                       | μA             |

| V <sup>+</sup>                            |                     | $V^+/V^- = \pm 15 V$                                           |                       | 30   |                       | μA             |

| V-                                        |                     | $V^+/V^- = \pm 15 V$                                           |                       | -30  |                       | μA             |

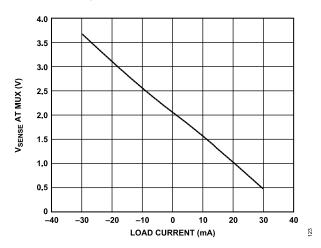

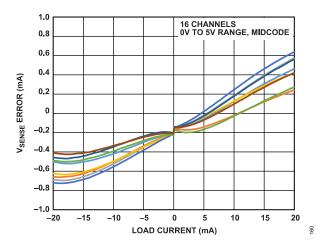

| ANALOG MUX                                |                     |                                                                |                       |      |                       |                |

| MUX DC Output Impedance                   |                     |                                                                |                       | 3.5  |                       | kΩ             |

| MUX Leakage Current                       |                     |                                                                |                       |      | 1                     | μA             |

| MUX Output Voltage Range                  |                     |                                                                | V-                    |      | V1+ - 1.4             | V              |

| MUX Continuous Current <sup>10</sup>      |                     |                                                                |                       |      | 0.2                   | mA             |

| Junction Temperature Sense Slope          |                     |                                                                |                       | 7.95 |                       | mV/°C          |

| Junction Temperature Accuracy             |                     |                                                                |                       | ±5   |                       | °C             |

| AC PERFORMANCE                            |                     |                                                                |                       |      |                       |                |

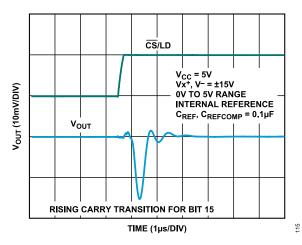

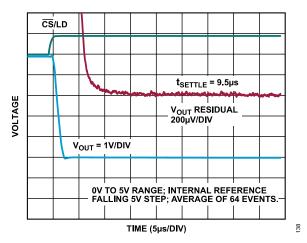

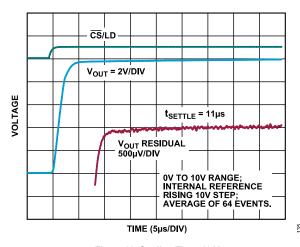

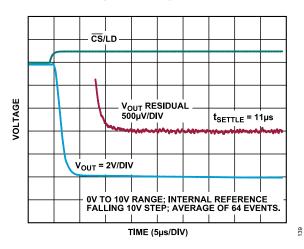

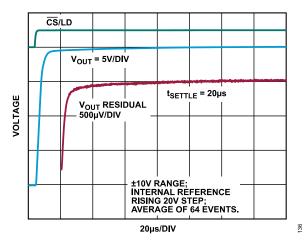

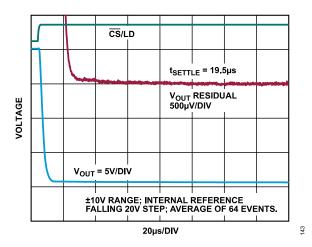

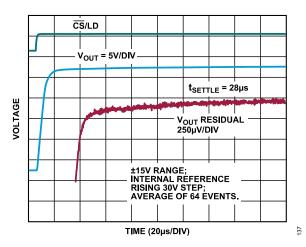

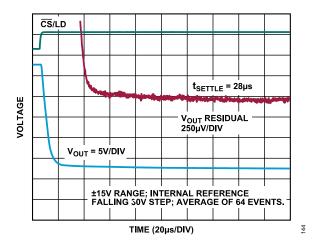

| Settling Time                             | t <sub>SETTLE</sub> |                                                                |                       |      |                       |                |

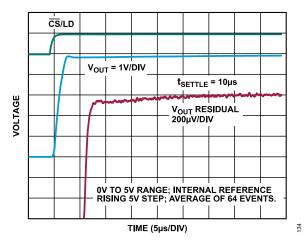

| 0 V to 5 V Range, ±5 V Step               | SETTLE              | 0.0015% (±1 LSB <sub>16</sub> )                                |                       | <10  |                       | 110            |

| o v to o v range, to v step               |                     | 1 127                                                          |                       | 6.5  |                       | μs             |

| 0.V.t- 40.V.D-=== !5.V.D-==- !40.V        |                     | 0.024% (±1 LSB <sub>12</sub> )                                 |                       |      |                       | μs             |

| 0 V to 10 V Range or ±5 V Range, ±10 V    |                     | 0.0015% (±1 LSB <sub>16</sub> )                                |                       | <11  |                       | μs             |

| Step                                      |                     | 0.024% (±1 LSB <sub>12</sub> )                                 |                       | 8.6  |                       | μs             |

| ±10 V Range, ±20 V Step                   |                     | 0.0015% (±1 LSB <sub>16</sub> )                                |                       | <20  |                       | μs             |

|                                           |                     | 0.024% (±1 LSB <sub>12</sub> )                                 |                       | 15   |                       | μs             |

| ±15 V Range, ±30 V Step                   |                     | 0.0015% (±1 LSB <sub>16</sub> )                                |                       | <28  |                       | μs             |

|                                           |                     | 0.024% (±1 LSB <sub>12</sub> )                                 |                       | 21   |                       | μs             |

| Voltage Output Slew Rate                  | SR                  |                                                                |                       | >3.5 |                       | V/µs           |

| Capacitive Load Driving                   |                     |                                                                |                       | 1000 |                       | pF             |

| Glitch Impulse <sup>11</sup>              |                     | At midscale transition, 0 V to 5 V range                       |                       | 7    |                       | nV-sec         |

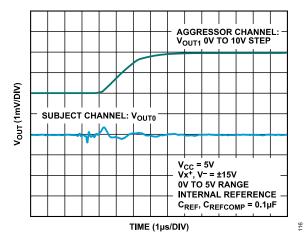

| DAC to DAC Crosstalk <sup>12</sup>        |                     | Due to full-scale output change, 0 V to 5 V                    |                       | 1    |                       | nV-sec         |

|                                           |                     | range                                                          |                       |      |                       |                |

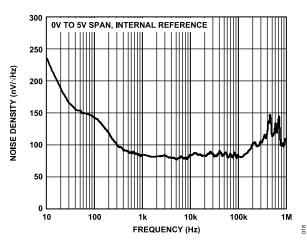

| Output Noise Spectral Density             | e <sub>n</sub>      | 0 V to 5 V output range, internal reference                    |                       |      |                       |                |

analog.com Rev. C | 5 of 45

#### **SPECIFICATIONS**

Table 1. (Continued)

| Parameter                               | Symbol          | Test Conditions/Comments                   | Min                     | Тур | Max | Unit   |

|-----------------------------------------|-----------------|--------------------------------------------|-------------------------|-----|-----|--------|

|                                         |                 | At f = 1 kHz                               |                         | 60  |     | nV/√Hz |

|                                         |                 | At f = 10 kHz                              |                         | 45  |     | nV/√Hz |

|                                         |                 | 0.1 Hz to 10 Hz                            |                         | 1.7 |     | μV rms |

|                                         |                 | 0.1 Hz to 200 kHz                          |                         | 30  |     | μV rms |

| DIGITAL INPUT/OUTPUT (I/O)              |                 |                                            |                         |     |     |        |

| Digital Output High Voltage             | V <sub>OH</sub> | SDO pin, load current = −100 µA            | IOV <sub>CC</sub> - 0.2 |     |     | V      |

| Digital Output Low Voltage              | V <sub>OL</sub> | SDO pin, load current = 100 µA             |                         |     | 0.2 | V      |

|                                         |                 | FAULT pin, load current = 100 μA           |                         |     | 0.2 | V      |

| Digital High-Z Output Leakage           | I <sub>OZ</sub> | SDO pin leakage current (CS/LD high)       |                         |     | ±1  | μA     |

|                                         |                 | FAULT pin leakage current (not asserted)   |                         |     | 1   | μA     |

| Digital Input Leakage                   | I <sub>LK</sub> | V <sub>IN</sub> = GND to IOV <sub>CC</sub> |                         |     | ±1  | μA     |

| Digital Input Capacitance <sup>10</sup> | C <sub>IN</sub> |                                            |                         |     | 8   | pF     |

| $IOV_{CC}$ = 2.7 V to $V_{CC}$          |                 |                                            |                         |     |     |        |

| Digital Input High Voltage              | V <sub>IH</sub> |                                            | 0.8 × IOV <sub>CC</sub> |     |     | V      |

| Digital Input Low Voltage               | V <sub>IL</sub> |                                            |                         |     | 0.5 | V      |

| IOV <sub>CC</sub> = 1.71 V to 2.7 V     |                 |                                            |                         |     |     |        |

| Digital Input High Voltage              | V <sub>IH</sub> |                                            | 0.8 × IOV <sub>CC</sub> |     |     | V      |

| Digital Input Low Voltage               | V <sub>IL</sub> |                                            |                         |     | 0.3 | V      |

<sup>1</sup> Output ranges include 0 V to 5 V, 0 V to 10 V, ±5 V, ±10 V, and ±15 V.

- <sup>4</sup> This IC includes current limiting that is intended to protect the device during momentary overload conditions. Junction temperature can exceed the rated maximum during current limiting. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

- <sup>5</sup> Reference voltage output is production tested using a socket. Mechanical stress caused by soldering parts to a printed circuit board may cause the output voltage to shift and temperature coefficient to change. See the Printed Circuit Board Layout section.

- <sup>6</sup> Temperature coefficient is calculated by dividing the maximum change in output voltage by the specified temperature range.

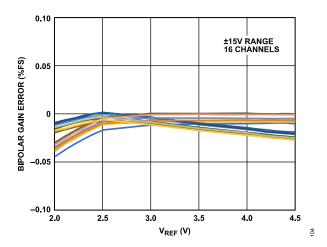

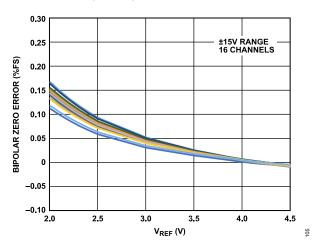

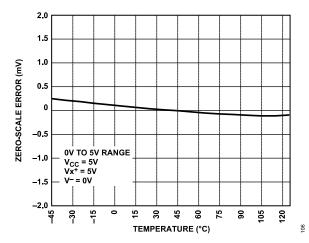

- <sup>7</sup> GE, BZE, and V<sub>OS</sub> specifications can degrade for reference input voltages less than 3 V. See Figure 5, Figure 6, and Figure 12 in the Typical Performance Characteristics section.

- 8 Internal reference on. IV<sub>CC</sub> measured with all channels at zero scale for unipolar ranges and negative full scale for bipolar ranges.

- 9 Vx<sup>+</sup> current (I<sub>V</sub><sup>+</sup>) is measured with all channels at full scale. V<sup>-</sup> current (I<sub>V</sub><sup>-</sup>) is measured with all channels at zero scale for unipolar ranges and negative full scale for bipolar ranges.

- <sup>10</sup> Guaranteed by design; not production tested.

- 11 0 V to 5 V range, internal reference mode. DAC is stepped ±1 LSB between half scale and half scale 1 LSB. Load is 2 kΩ in parallel with 200 pF to GND.

- 12 DAC to DAC crosstalk is the glitch that appears at the output of one DAC due to full-scale change at the output of another DAC. 0 V to 5 V range with internal reference.

The measured DAC is at midscale.

## **TIMING CHARACTERISTICS**

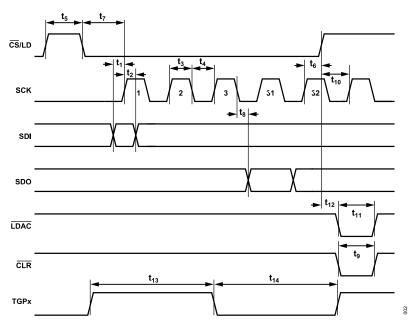

All specifications apply over the full operating temperature range, unless otherwise noted. Typical values are at  $T_A$  = 25°C.  $V_{CC}$  = 4.75 V to 5.25 V,  $IOV_{CC}$  = 1.71 V to  $V_{CC}$ .  $C_{LOAD}$  is load capacitance.  $IOV_{CC}$  = 2.7 V to  $V_{CC}$ , unless otherwise noted. See Figure 2.

Table 2.

| Parameter      | Description            | Min | Тур | Max | Unit |

|----------------|------------------------|-----|-----|-----|------|

| t <sub>1</sub> | SDI valid to SCK setup | 3   |     |     | ns   |

| $t_2$          | SDI valid to SCK hold  | 3   |     |     | ns   |

| t <sub>3</sub> | SCK high time          | 6   |     |     | ns   |

analog.com Rev. C | 6 of 45

<sup>&</sup>lt;sup>2</sup> FSR is full-scale range.

<sup>3</sup> DC crosstalk is measured using the internal reference. The conditions of one DAC channel are changed as specified, and the output of an adjacent channel (at midscale) is measured before and after the change.

# **SPECIFICATIONS**

Table 2. (Continued)

| Parameter      | Description                                                                                           | Min | Тур  | Max | Unit |

|----------------|-------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| t <sub>4</sub> | SCK low time                                                                                          | 6   |      |     | ns   |

| t <sub>5</sub> | CS/LD pulse width                                                                                     | 8   |      |     | ns   |

| 6              | LSB SCK high to CS/LD high                                                                            | 5   |      |     | ns   |

| 7              | CS/LD low to SCK high                                                                                 | 5   |      |     | ns   |

| t <sub>8</sub> | SDO propagation delay from SCK falling edge, $C_{LOAD}$ = 10 pF, $IOV_{CC}$ = 2.7 V to 5.25 V         |     |      | 25  | ns   |

|                | SDO propagation delay from SCK falling edge, $C_{LOAD}$ = 10 pF, $IOV_{CC}$ = 1.7 1 V to 2.7 V        |     |      | 60  | ns   |

| 9              | CLR pulse width                                                                                       | 8   |      |     | ns   |

| 10             | CS/LD high to SCK positive edge                                                                       | 4   |      |     | ns   |

| 11             | LDAC pulse width                                                                                      | 8   |      |     | ns   |

| 12             | $\overline{\text{CS}}/\text{LD}$ high to $\overline{\text{LDAC}}$ high or low transition <sup>1</sup> | 8   |      |     | ns   |

| SCK            | SCK frequency                                                                                         |     |      | 50  | MHz  |

| 13             | TGPx high time                                                                                        |     | 0.25 |     | μs   |

| 14             | TGPx low time <sup>2</sup>                                                                            |     | 0.25 |     | μs   |

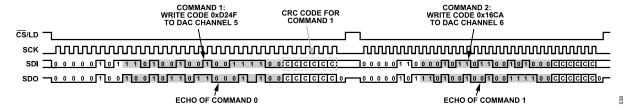

$<sup>^{1}</sup>$  Value of  $t_{12}$  is not valid for write code to all DAC channels. For write code to all DAC channels, the typical value of  $t_{12}$  is 320 ns.

# **Timing Diagram**

Figure 2. Serial Interface Timing Diagram

analog.com Rev. C | 7 of 45

<sup>&</sup>lt;sup>2</sup> Guaranteed by design but not production tested.

#### **ABSOLUTE MAXIMUM RATINGS**

Table 3

| Parameter                                            | Rating                                                                       |

|------------------------------------------------------|------------------------------------------------------------------------------|

| V <sub>CC</sub> to GND                               | -0.3 V to +6 V                                                               |

| IOV <sub>CC</sub> to GND                             | -0.3 V to +6 V                                                               |

| REFL to GND                                          | -0.3 V to +0.3V                                                              |

| V1 <sup>+</sup> to GND                               | -0.3 V to +22 V                                                              |

| V2+ to GND                                           | -0.3 V to V1 <sup>+</sup> , or -0.3 V to +22 V (whichever is smaller)        |

| V⁻ to GND                                            | -22V to +0.3 V                                                               |

| V1 <sup>+</sup> to V <sup>-</sup>                    | -0.3 V to +44 V                                                              |

| V2 <sup>+</sup> to V <sup>-</sup>                    | -0.3 V to +44 V                                                              |

| Mux Continuous DC Output Current                     | ±200 μA                                                                      |

| CS/LD, SCK, SDI                                      | -0.3 V to IOV <sub>CC</sub> + 0.3 V or -0.3 V to +6 V (whichever is smaller) |

| LDAC, CLR, FAULT to GND                              | -0.3 V to IOV <sub>CC</sub> + 0.3 V or -0.3 V to +6 V (whichever is smaller) |

| TGP0, TGP1, TGP2 to GND                              | -0.3 V to IOV <sub>CC</sub> + 0.3 V or -0.3 V to +6 V (whichever is smaller) |

| V <sub>OUT0</sub> to V <sub>OUT15</sub> , MUX to GND | $V^ 0.3 \text{ V to Vx}^+ + 0.3 \text{ V, or } \pm 22 \text{ V}$             |

| REF, REFCOMP                                         | -0.3 V to V <sub>CC</sub> + 0.3 V or -0.3 V to 6 V (whichever is smaller)    |

| SDO                                                  | -0.3 V to IOV <sub>CC</sub> + 0.3 V or -0.3 V to 6 V (whichever is smaller)  |

| Temperature                                          |                                                                              |

| Operating Range                                      |                                                                              |

| LTC2688C                                             | 0°C to 70°C                                                                  |

| LTC2688I                                             | -40°C to +85°C                                                               |

| LTC2688H                                             | -40°C to +125°C                                                              |

| Storage Range                                        | −65°C to +150°C                                                              |

| Junction, T <sub>JMAX</sub>                          | 150°C                                                                        |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one-cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

Table 4. Thermal Resistance

| Package Type            | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|-------------------------|---------------|---------------|------|

| 05-08-1728 <sup>1</sup> | 33            | 2             | °C/W |

| CB-64-5                 | 32.2          | 0.2           | °C/W |

Thermal impedance simulated values are based on JEDEC 2S2P thermal test board with no bias. See JEDEC JESD-51.

# **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Field induced charged device model (FICDM) per ANSI/ESDA/JEDEC JS-002.

# **ESD Ratings for LTC2688**

Table 5. LTC2688, 40-Lead LFCSP and 64-Ball WLCSP

| ESD Model | ESD Model Withstand Threshold (V) |    |

|-----------|-----------------------------------|----|

| HBM       | 3500                              | 2  |

| FICDM     | 500                               | C4 |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. C | 8 of 45

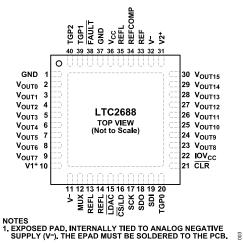

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. LFCSP Pin Configuration

Table 6. Pin Function Descriptions—LFCSP

| Pin No.          | Mnemonic                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 37            | GND                                     | Analog Ground. Tie GND to a clean analog ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2 to 9, 23 to 30 | V <sub>OUT0</sub> to V <sub>OUT15</sub> | DAC Analog Voltage Outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10               | V1 <sup>+</sup>                         | Analog Positive Supply for the $V_{OUT0}$ to $V_{OUT7}$ DAC Outputs. Bypass V1 <sup>+</sup> to GND with a 1 $\mu$ F capacitor. V1 <sup>+</sup> must be greater than or equal to V2 <sup>+</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11, 32           | V-                                      | Analog Negative Supply. Bypass V <sup>-</sup> to GND with a 1 µF capacitor unless V <sup>-</sup> is connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12               | MUX                                     | Analog Multiplexer Output. Any of the 16 DAC output pin voltages, current load sense voltages (V <sub>SENSE</sub> ), and junction temperatures can be monitored by measuring the voltage at the MUX pin. When the mux is disabled, the MUX pin becomes high impedance. A full listing of available mux functions is given in Table 26.                                                                                                                                                                                                                                                                                   |

| 13, 14, 35       | REFL                                    | Reference Low Pins. Signal ground for all DAC channels and internal reference. Tie the REFL pins to a clean analog ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15               | <u>LDAC</u>                             | Active Low Asynchronous DAC Update Pin. When $\overline{\text{CS}}/\text{LD}$ is high, a falling edge on $\overline{\text{LDAC}}$ updates all DAC registers with the contents of the input registers. When $\overline{\text{LDAC}}$ is low, a rising edge on $\overline{\text{CS}}/\text{LD}$ similarly updates all DAC registers. Logic levels are determined by IOV <sub>CC</sub> . If the $\overline{\text{LDAC}}$ pin is not used, tie it high to IOV <sub>CC</sub> . Updates can then be performed through SPI commands.                                                                                            |

| 16               | CS/LD                                   | Serial Interface Chip Select/Load Input. When $\overline{\text{CS}}/\text{LD}$ is low, SCK is enabled for shifting data on SDI into the register. When $\overline{\text{CS}}/\text{LD}$ is taken high, SCK is disabled and the specified command (see Table 8 and Table 9) is executed. Logic levels are determined by IOV <sub>CC</sub> .                                                                                                                                                                                                                                                                               |

| 17               | SCK                                     | Serial Interface Clock Input. Logic levels are determined by IOV <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 18               | SDO                                     | Serial Interface Data Output. Data is clocked out onto SDO by the falling edge of SCK. SDO is high impedance when $\overline{\text{CS}}\text{/LD}$ is high. Logic levels are determined by IOV <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                           |

| 19               | SDI                                     | Serial Interface Data Input. Data on SDI is clocked into the DAC on the rising edge of SCK. The LTC2688 accepts input word lengths of 24 bits or 32 bits. Logic levels are determined by IOV <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                             |

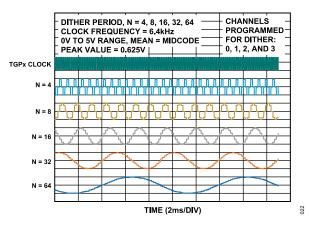

| 20, 39, 40       | TGP0, TGP1, TGP2                        | Asynchronous Toggle and Sinusoidal Dither Multifunctional Pins. In toggle mode, a falling edge updates the DAC register with data from Input Register A and a rising edge updates the DAC register with data from Input Register B. In sinusoidal dither mode, the toggle pins function as dither clock inputs. DAC outputs update on the rising edge. Toggle and dither operations only affect those DAC channels with their toggle/dither enable bit (ENx) set to 1. When neither toggle nor dither operations are used, tie the TGPx pins to GND, and set EN to 0. Logic levels are determined by IOV <sub>CC</sub> . |

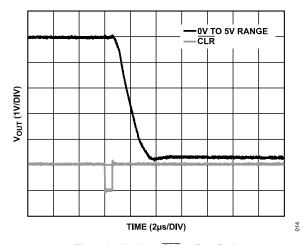

| 21               | CLR                                     | Active Low Asynchronous Clear Input. A logic low at this level-triggered input clears the device to zero-scale code and a 0 V to 5 V span range. The control registers are cleared to default values. Logic levels are determined by IOV <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                 |

| 22               | IOV <sub>CC</sub>                       | Digital Input/Output Supply Voltage. 1.71 V $\leq$ IOV <sub>CC</sub> $\leq$ V <sub>CC</sub> + 0.3 V. Bypass IOV <sub>CC</sub> to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 31               | V2 <sup>+</sup>                         | Analog Positive Supply for the $V_{OUT8}$ to $V_{OUT15}$ DAC Outputs. Bypass the V2 <sup>+</sup> pin to GND with a 1 $\mu$ F capacitor. V2 <sup>+</sup> must be less than or equal to V1 <sup>+</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 33               | REF                                     | Reference Input/Output. The voltage at the REF pin sets the full-scale range of all channels. By default, the internal reference is routed to this pin. The REF pin must be buffered when driving external dc load currents. When set to external reference mode, the internal reference is disconnected, and the REF pin becomes a high impedance input to which a precision external reference can be applied. For low noise and reference stability, tie a capacitor from the REF pin to GND. The value must be                                                                                                       |

analog.com Rev. C | 9 of 45

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 6. Pin Function Descriptions—LFCSP (Continued)

| Pin No. | Mnemonic        | Description                                                                                                                                                                                                                                                                                                                     |

|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                 | less than the capacitance at the REFCOMP pin. In external reference mode, the allowable reference input voltage range is 2.0 $V$ to $V_{CC}$ – 0.6 $V$ .                                                                                                                                                                        |

| 34      | REFCOMP         | Internal Reference Compensation. For low noise and reference stability, tie REFCOMP to a 0.1 µF capacitor to GND. Tying REFCOMP to GND causes the device to power up with the internal reference disabled, allowing the use of an external reference at startup.                                                                |

| 36      | V <sub>CC</sub> | Analog Supply Voltage Input. 4.75 V $\leq$ V <sub>CC</sub> $\leq$ 5.25 V. Bypass V <sub>CC</sub> to GND with a 1 $\mu$ F capacitor.                                                                                                                                                                                             |

| 38      | FAULT           | Fault Indicator. FAULT is an open-drain, N channel output that pulls low when a fault condition occurs. A fault condition is detected when the junction temperature exceeds 160°C or when a SPI transaction error occurs. The FAULT pin is released on the next CS/LD rising edge. A pull-up resistor of ≥10 kΩ is recommended. |

| 41      | EPAD            | Exposed Pad. Internally tied to analog negative supply (V <sup>-</sup> ). The EPAD must be soldered to the PCB.                                                                                                                                                                                                                 |

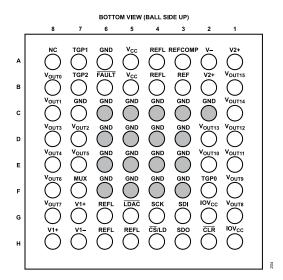

Figure 4. WLCSP Pin Configuration

Table 7. Pin Function Descriptions—WLCSP

| Pin No.                                                                             | Mnemonic                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, B2                                                                              | V2 <sup>+</sup>                         | Analog Positive Supply for the $V_{OUT8}$ to $V_{OUT15}$ DAC Outputs. Bypass the V2 <sup>+</sup> pin to GND with a 1 $\mu$ F capacitor. V2 <sup>+</sup> must be less than or equal to V1 <sup>+</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A2, H7                                                                              | V-                                      | Analog Negative Supply. Bypass V <sup>-</sup> to GND with a 1 µF capacitor unless V <sup>-</sup> is connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A3                                                                                  | REFCOMP                                 | Internal Reference Compensation. For low noise and reference stability, tie REFCOMP to a 0.1 µF capacitor to GND. Tying REFCOMP to GND causes the device to power up with the internal reference disabled, allowing the use of an external reference at startup.                                                                                                                                                                                                                                                                                                                                                         |

| A4, B4, G6, H5, H6                                                                  | REFL                                    | Reference Low Pins. Signal ground for all DAC channels and internal reference. Tie the REFL pins to a clean analog ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A5, B5                                                                              | V <sub>CC</sub>                         | Analog Supply Voltage Input. 4.75 V $\leq$ V <sub>CC</sub> $\leq$ 5.25 V. Bypass V <sub>CC</sub> to GND with a 1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A6, C2, C3, C4, C5,<br>C6, C7, D3, D4, D5,<br>D6, E3, E4, E5, E6,<br>F3, F4, F5, F6 | GND                                     | Analog Ground. Tie GND to a clean analog ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A7, B7, F2                                                                          | TGP0, TGP1, TGP2                        | Asynchronous Toggle and Sinusoidal Dither Multifunctional Pins. In toggle mode, a falling edge updates the DAC register with data from Input Register A and a rising edge updates the DAC register with data from Input Register B. In sinusoidal dither mode, the toggle pins function as dither clock inputs. DAC outputs update on the rising edge. Toggle and dither operations only affect those DAC channels with their toggle/dither enable bit (ENx) set to 1. When neither toggle nor dither operations are used, tie the TGPx pins to GND, and set EN to 0. Logic levels are determined by IOV <sub>CC</sub> . |

| A8                                                                                  | NC                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| B8, C8, D7, D8, E8,<br>E7, F8, G8, G1, F1,                                          | V <sub>OUT0</sub> to V <sub>OUT15</sub> | DAC Analog Voltage Outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

analog.com Rev. C | 10 of 45

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 7. Pin Function Descriptions—WLCSP (Continued)

| Pin No.                 | Mnemonic          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E2, E1, D1, D2, 0<br>B1 | C1,               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| B3                      | REF               | Reference Input/Output. The voltage at the REF pin sets the full-scale range of all channels. By default, the internal reference is routed to this pin. The REF pin must be buffered when driving external dc load currents. When set to external reference mode, the internal reference is disconnected, and the REF pin becomes a high impedance input to which a precision external reference can be applied. For low noise and reference stability, tie a capacitor from the REF pin to GND. The value must be less than the capacitance at the REFCOMP pin. In external reference mode, the allowable reference input voltage range is $2.0  \text{V}$ to $V_{\text{CC}} - 0.6  \text{V}$ . |

| B6                      | FAULT             | Fault Indicator. FAULT is an open-drain, N channel output that pulls low when a fault condition occurs. A fault condition is detected when the junction temperature exceeds 160°C or when a SPI transaction error occurs. The FAULT pin is released on the next CS/LD rising edge. A pull-up resistor of ≥10 kΩ is recommended.                                                                                                                                                                                                                                                                                                                                                                  |

| F7                      | MUX               | Analog Multiplexer Output. Any of the 16 DAC output pin voltages, current load sense voltages (V <sub>SENSE</sub> ), and junction temperatures can be monitored by measuring the voltage at the MUX pin. When the mux is disabled, the MUX pin becomes high impedance. A full listing of available mux functions is given in Table 26.                                                                                                                                                                                                                                                                                                                                                           |

| G7, H8                  | V1 <sup>+</sup>   | Analog Positive Supply for the $V_{OUT0}$ to $V_{OUT7}$ DAC Outputs. Bypass V1 <sup>+</sup> to GND with a 1 $\mu$ F capacitor. V1 <sup>+</sup> must be greater than or equal to V2 <sup>+</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| G2, H1                  | IOV <sub>CC</sub> | Digital Input/Output Supply Voltage. 1.71 V $\leq$ IOV <sub>CC</sub> $\leq$ V <sub>CC</sub> + 0.3 V. Bypass IOV <sub>CC</sub> to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

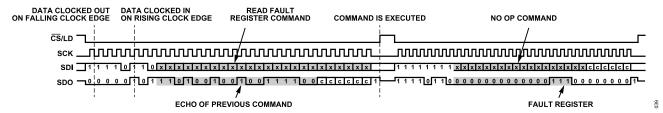

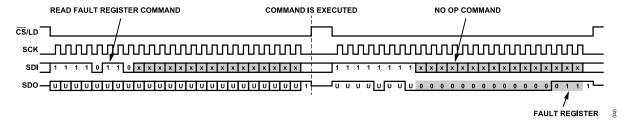

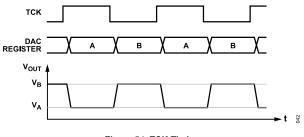

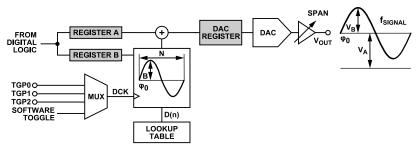

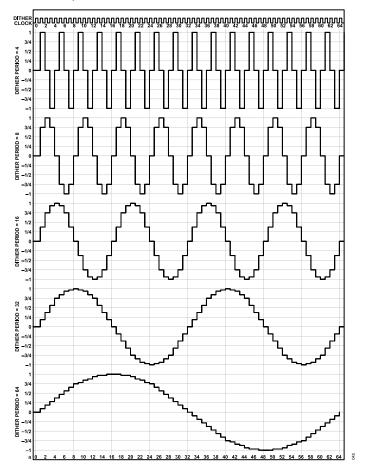

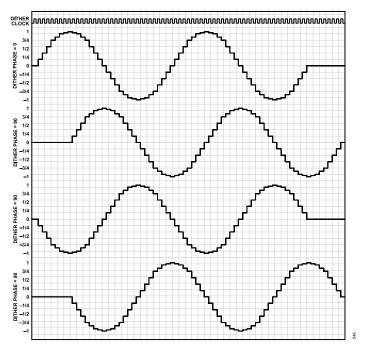

| G3                      | SDI               | Serial Interface Data Input. Data on SDI is clocked into the DAC on the rising edge of SCK. The LTC2688 accepts input word lengths of 24 bits or 32 bits. Logic levels are determined by IOV <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |