## **MAX V Device Handbook**

101 Innovation Drive San Jose, CA 95134 www.altera.com

MAX V Device Handbook June 2017 Altera Corporation

### **Contents**

### **Section I. MAX V Device Core**

| Chapter 1. MAX V Device Family Overview |      |

|-----------------------------------------|------|

| Feature Summary                         | 1–1  |

| Integrated Software Platform            |      |

| Device Pin-Outs                         | 1–3  |

| Ordering Information                    | 1–4  |

| Document Revision History               | 1–4  |

| Chapter 2. MAX V Architecture           |      |

| Functional Description                  | 2–1  |

| Logic Array Blocks                      |      |

| LAB Interconnects                       |      |

| LAB Control Signals                     | 2–6  |

| Logic Elements                          |      |

| LUT Chain and Register Chain            |      |

| addnsub Signal                          | 2–9  |

| LE Operating Modes                      |      |

| Normal Mode                             | 2–10 |

| Dynamic Arithmetic Mode                 | 2–10 |

| Carry-Select Chain                      | 2–11 |

| Clear and Preset Logic Control          | 2–13 |

| LE RAM                                  |      |

| MultiTrack Interconnect                 |      |

| Global Signals                          |      |

| User Flash Memory Block                 |      |

| UFM Storage                             |      |

| Internal Oscillator                     |      |

| Program, Erase, and Busy Signals        | 2–23 |

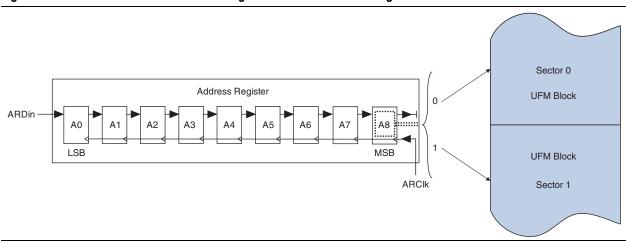

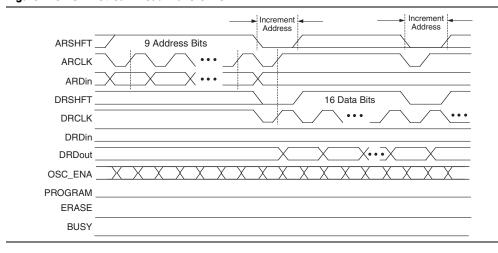

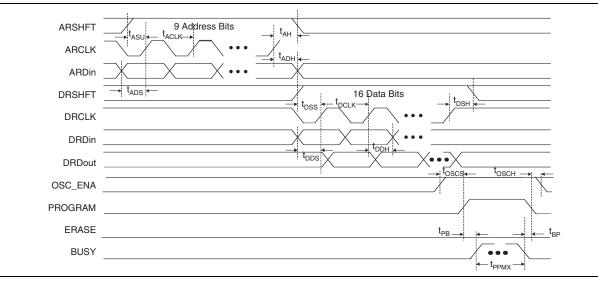

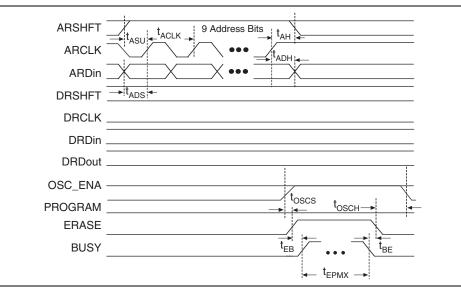

| Auto-Increment Addressing               | 2–23 |

| Serial Interface                        |      |

| UFM Block to Logic Array Interface      |      |

| Core Voltage                            |      |

| I/O Structure                           |      |

| Fast I/O Connection                     |      |

| I/O Blocks                              |      |

| I/O Standards and Banks                 |      |

| PCI Compliance                          |      |

| LVDS and RSDS Channels                  |      |

| Schmitt Trigger                         |      |

| Output Enable Signals                   |      |

| Programmable Drive Strength             |      |

| Slew-Rate Control                       |      |

| Open-Drain Output                       |      |

| Programmable Ground Pins                |      |

| Bus-Hold                                |      |

| Programmable Pull-Up Resistor           |      |

| Programmable Input Delay                | 2-35 |

iv Contents

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 200000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| Chantar 2 DC and Switching Characteristics for MAY V Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| Chapter 3. DC and Switching Characteristics for MAX V Devices  Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2 1 |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| Programming/Erasure Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| DC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

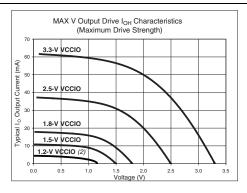

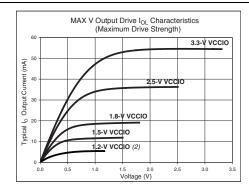

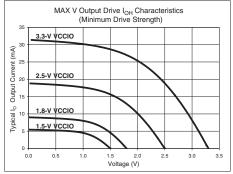

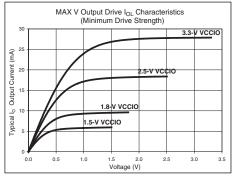

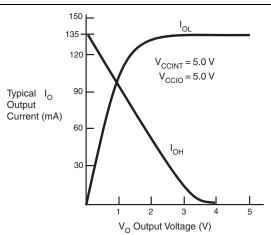

| Output Drive Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| I/O Standard Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| Bus Hold Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| Power-Up Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| Timing Model and Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| Preliminary and Final Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| Internal Timing Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| External Timing Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| External Timing I/O Delay Adders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| Maximum Input and Output Clock Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| LVDS and RSDS Output Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

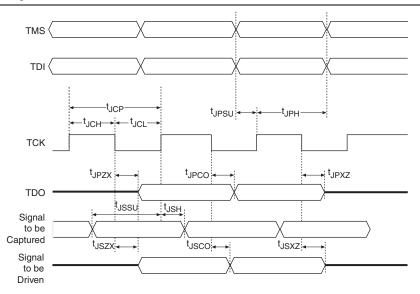

| JTAG Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| Section II. System Integration in MAX V Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| Chapter 4. Hot Socketing and Power-On Reset in MAX V Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| MAX V Hot-Socketing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Devices Can Be Driven Before Power Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| I/O Pins Remain Tri-Stated During Power Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| I/O Pins Remain Tri-Stated During Power Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| Signal Pins Do Not Drive the $V_{CCIO}$ or $V_{CCINT}$ Power Supplies AC and DC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| Signal Pins Do Not Drive the $V_{CCIO}$ or $V_{CCINT}$ Power Supplies AC and DC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| Signal Pins Do Not Drive the $V_{CCIO}$ or $V_{CCINT}$ Power Supplies AC and DC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

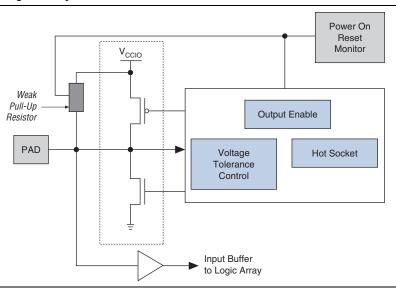

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies  AC and DC Specifications  Hot-Socketing Feature Implementation in MAX V Devices  Power-On Reset Circuitry  Power-Up Characteristics  Document Revision History                                                                                                                                                                                                                                                                                                                                                                                               |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems                                                                                                                                                                                                                                                                                                                                           |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems I/O Standards                                                                                                                                                                                                                                                                                                                             |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems                                                                                                                                                                                                                                                                                                                                           |     |

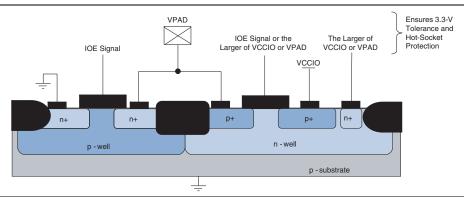

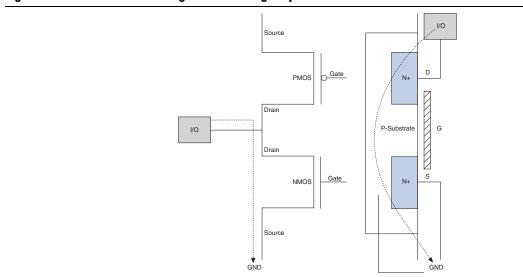

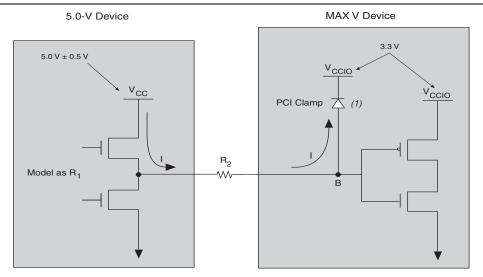

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems I/O Standards MultiVolt I/O Operation 5.0-V Device Compatibility                                                                                                                                                                                                                                                                          |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems I/O Standards MultiVolt I/O Operation                                                                                                                                                                                                                                                                                                     |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems I/O Standards MultiVolt I/O Operation 5.0-V Device Compatibility Recommended Operating Conditions for 5.0-V Compatibility Power-Up Sequencing                                                                                                                                                                                             |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems I/O Standards MultiVolt I/O Operation 5.0-V Device Compatibility Recommended Operating Conditions for 5.0-V Compatibility                                                                                                                                                                                                                 |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems I/O Standards MultiVolt I/O Operation 5.0-V Device Compatibility Recommended Operating Conditions for 5.0-V Compatibility Power-Up Sequencing Document Revision History                                                                                                                                                                   |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems I/O Standards MultiVolt I/O Operation 5.0-V Device Compatibility Recommended Operating Conditions for 5.0-V Compatibility Power-Up Sequencing Document Revision History  Chapter 6. JTAG and In-System Programmability in MAX V Devices                                                                                                   |     |

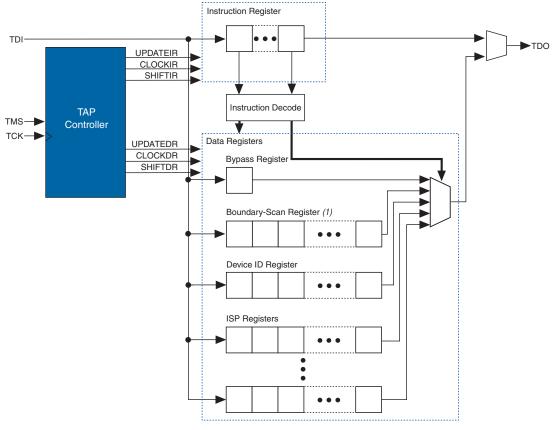

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications  Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems I/O Standards MultiVolt I/O Operation 5.0-V Device Compatibility Recommended Operating Conditions for 5.0-V Compatibility Power-Up Sequencing Document Revision History  Chapter 6. JTAG and In-System Programmability in MAX V Devices IEEE Std. 1149.1 Boundary-Scan Support                                                           |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications  Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems I/O Standards MultiVolt I/O Operation 5.0-V Device Compatibility Recommended Operating Conditions for 5.0-V Compatibility Power-Up Sequencing Document Revision History  Chapter 6. JTAG and In-System Programmability in MAX V Devices IEEE Std. 1149.1 Boundary-Scan Support JTAG Block                                                |     |

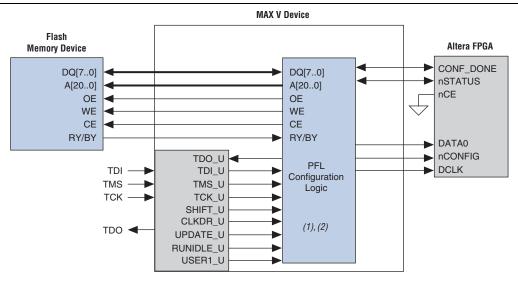

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems I/O Standards MultiVolt I/O Operation 5.0-V Device Compatibility Recommended Operating Conditions for 5.0-V Compatibility Power-Up Sequencing Document Revision History  Chapter 6. JTAG and In-System Programmability in MAX V Devices IEEE Std. 1149.1 Boundary-Scan Support JTAG Block Parallel Flash Loader                           |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems I/O Standards MultiVolt I/O Operation 5.0-V Device Compatibility Recommended Operating Conditions for 5.0-V Compatibility Power-Up Sequencing Document Revision History  Chapter 6. JTAG and In-System Programmability in MAX V Devices IEEE Std. 1149.1 Boundary-Scan Support JTAG Block Parallel Flash Loader In-System Programmability |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies AC and DC Specifications Hot-Socketing Feature Implementation in MAX V Devices Power-On Reset Circuitry Power-Up Characteristics Document Revision History  Chapter 5. Using MAX V Devices in Multi-Voltage Systems I/O Standards MultiVolt I/O Operation 5.0-V Device Compatibility Recommended Operating Conditions for 5.0-V Compatibility Power-Up Sequencing Document Revision History  Chapter 6. JTAG and In-System Programmability in MAX V Devices IEEE Std. 1149.1 Boundary-Scan Support JTAG Block Parallel Flash Loader                           |     |

| Programming Sequence                                                                      |              |

|-------------------------------------------------------------------------------------------|--------------|

| User Flash Memory Programming                                                             |              |

| In-System Programming Clamp                                                               | 6–7          |

| Real-Time ISP                                                                             | 6–8          |

| Design Security                                                                           |              |

| Programming with External Hardware                                                        | 6–8          |

| Document Revision History                                                                 | 6–9          |

|                                                                                           |              |

| Chapter 7. User Flash Memory in MAX V Devices                                             |              |

| UFM Array Description                                                                     |              |

| Memory Organization Map                                                                   |              |

| Using and Accessing UFM Storage                                                           |              |

| UFM Functional Description                                                                |              |

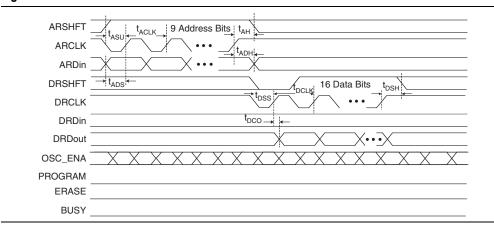

| UFM Address Register                                                                      |              |

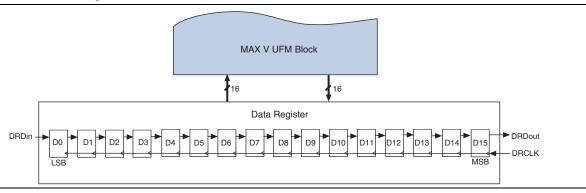

| UFM Data Register                                                                         |              |

| UFM Program/Erase Control Block                                                           |              |

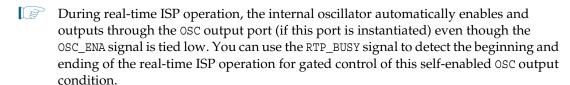

| Oscillator                                                                                | 7–7          |

| Instantiating the Oscillator without the UFM                                              | 7–7          |

| UFM Operating Modes                                                                       | 7–8          |

| Read/Stream Read                                                                          |              |

| Program                                                                                   |              |

| Erase                                                                                     |              |

| Programming and Reading the UFM with JTAG                                                 |              |

| Jam Files                                                                                 |              |

| Jam Players                                                                               |              |

| Software Support for UFM Block                                                            |              |

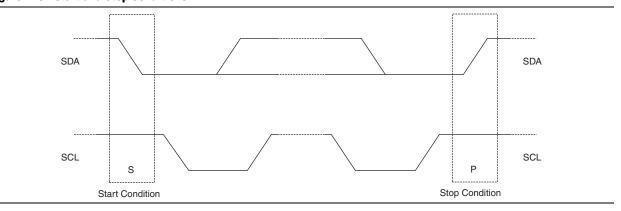

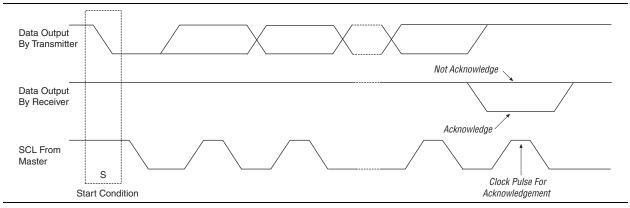

| Inter-Integrated Circuit                                                                  |              |

| I <sup>2</sup> C Protocol                                                                 |              |

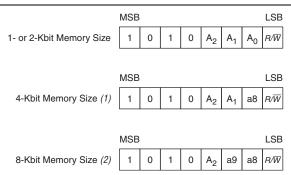

| Device Addressing                                                                         |              |

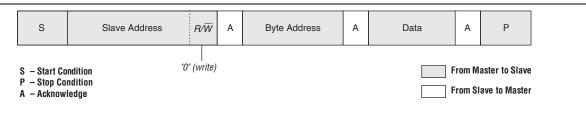

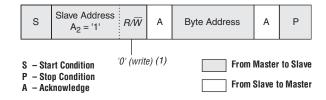

| Byte Write Operation                                                                      |              |

|                                                                                           |              |

| Page Write Operation                                                                      |              |

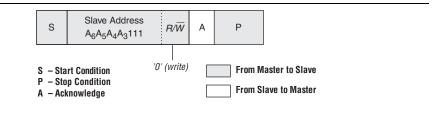

| Acknowledge Polling                                                                       |              |

| Write Protection                                                                          |              |

| Erase Operation                                                                           |              |

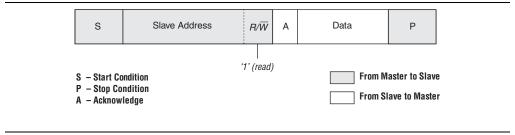

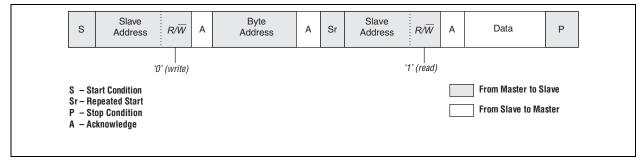

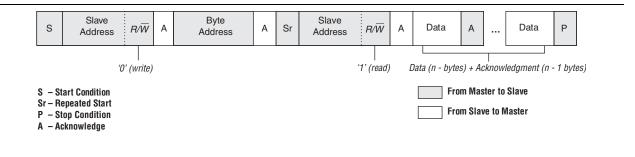

| Read Operation                                                                            |              |

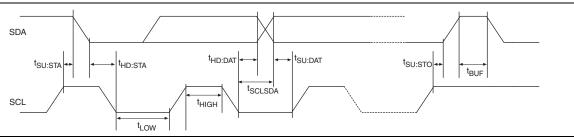

| ALTUFM_I2C Interface Timing Specification                                                 |              |

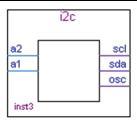

| Instantiating the I <sup>2</sup> C Interface Using the Quartus II ALTUFM_I2C Megafunction |              |

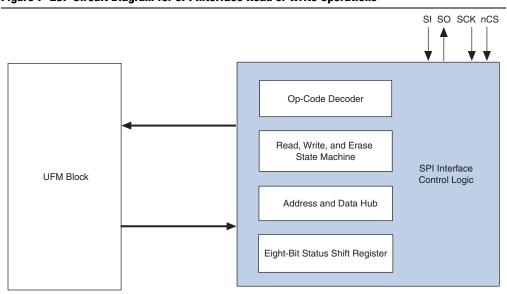

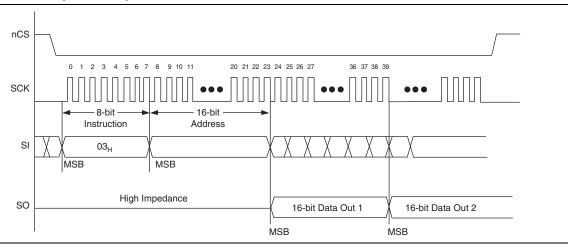

| Serial Peripheral Interface                                                               |              |

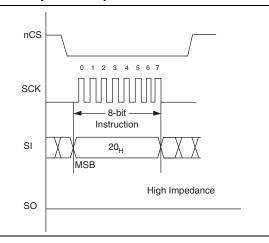

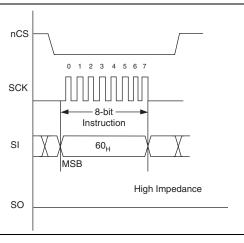

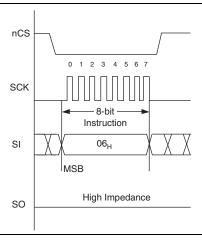

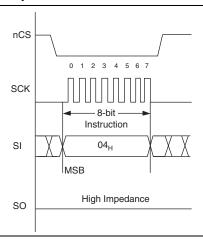

| Opcodes                                                                                   |              |

| ALTUFM SPI Timing Specification                                                           |              |

| Instantiating SPI Using Quartus II ALTUFM_SPI Megafunction                                | 7–35         |

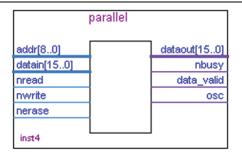

| Parallel Interface                                                                        | 7–36         |

| ALTUFM Parallel Interface Timing Specification                                            | 7–37         |

| Instantiating Parallel Interface Using Quartus II ALTUFM_PARALLEL Megafunction            |              |

| None (Altera Serial Interface)                                                            |              |

| Instantiating None Using Quartus II ALTUFM_NONE Megafunction                              |              |

| Creating Memory Content File                                                              |              |

| Memory Initialization for the ALTUFM_PARALLEL Megafunction                                |              |

| Memory Initialization for the ALTUFM_SPI Megafunction                                     |              |

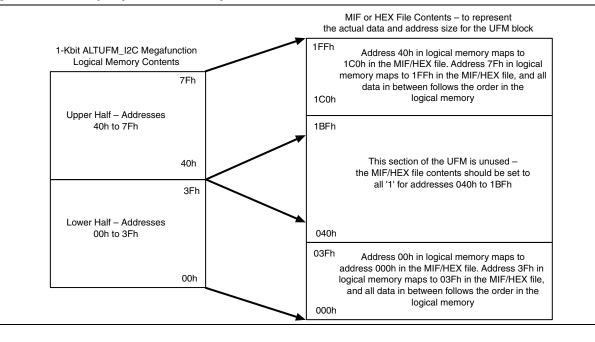

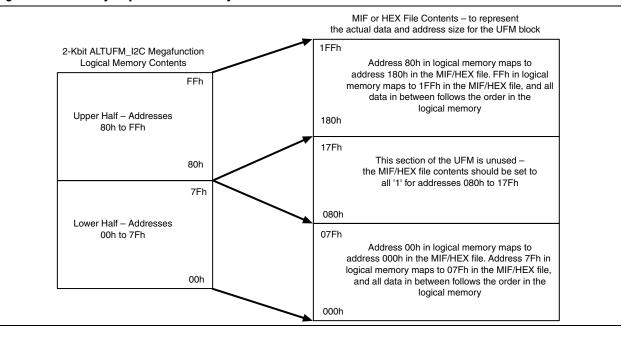

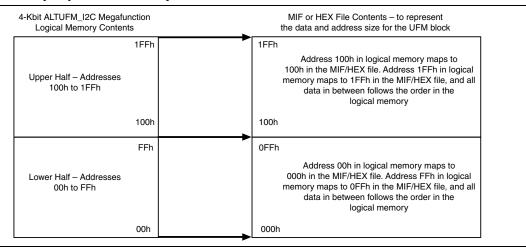

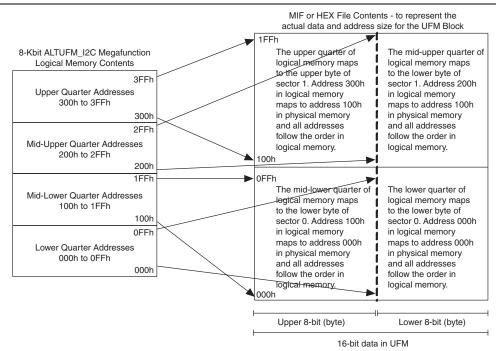

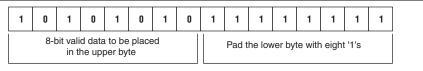

| Memory Initialization for the ALTUFM_I2C Megafunction                                     |              |

| Simulation Parameters                                                                     |              |

| Document Revision History                                                                 | 7-40<br>7-40 |

|                                                                                           |              |

vi Contents

| Chapter 8. JTAG Boundary-Scan Testing in MAX V Devices |       |

|--------------------------------------------------------|-------|

| IEEE Std. 1149.1 BST Architecture                      |       |

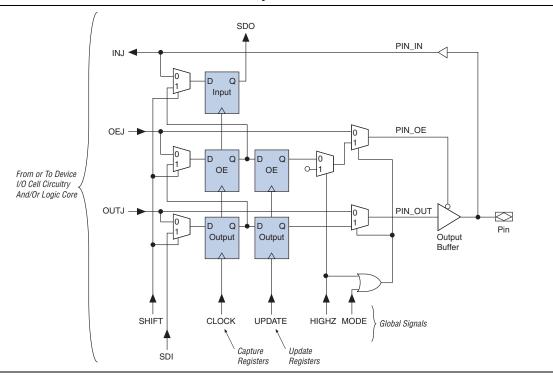

| IEEE Std. 1149.1 Boundary-Scan Register                |       |

| Boundary-Scan Cells of a MAX V Device I/O Pin          |       |

| JTAG Pins and Power Pins                               |       |

| IEEE Std. 1149.1 BST Operation Control                 |       |

| SAMPLE/PRELOAD Instruction Mode                        |       |

| EXTEST Instruction Mode                                |       |

| BYPASS Instruction Mode                                |       |

| IDCODE Instruction Mode                                |       |

| USERCODE Instruction Mode                              |       |

| CLAMP Instruction Mode                                 |       |

| HIGHZ Instruction Mode                                 | 8–13  |

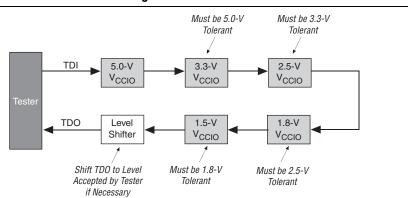

| I/O Voltage Support in the JTAG Chain                  | 8–13  |

| Boundary-Scan Test for Programmed Devices              | 8–14  |

| Disabling IEEE Std. 1149.1 BST Circuitry               | 8–15  |

| Guidelines for IEEE Std. 1149.1 Boundary-Scan Testing  | 8–15  |

| Boundary-Scan Description Language Support             | 8–15  |

| Document Revision History                              | 8–16  |

| Additional Information                                 |       |

| Document Revision History                              | Info– |

| How to Contact Altera                                  |       |

| Typographic Conventions                                |       |

### **Section I. MAX V Device Core**

This section provides a complete overview of all features relating to the  $MAX^{\otimes} V$  device family.

This section includes the following chapters:

- Chapter 1, MAX V Device Family Overview

- Chapter 2, MAX V Architecture

- Chapter 3, DC and Switching Characteristics for MAX V Devices

I–2 Section I: MAX V Device Core

### 1. MAX V Device Family Overview

MV51001-1.2

The MAX® V family of low cost and low power CPLDs offer more density and I/Os per footprint versus other CPLDs. Ranging in density from 40 to 2,210 logic elements (LEs) (32 to 1,700 equivalent macrocells) and up to 271 I/Os, MAX V devices provide programmable solutions for applications such as I/O expansion, bus and protocol bridging, power monitoring and control, FPGA configuration, and analog IC interface.

MAX V devices feature on-chip flash storage, internal oscillator, and memory functionality. With up to 50% lower total power versus other CPLDs and requiring as few as one power supply, MAX V CPLDs can help you meet your low power design requirement.

This chapter contains the following sections:

- "Feature Summary" on page 1–1

- "Integrated Software Platform" on page 1–3

- "Device Pin-Outs" on page 1–3

- "Ordering Information" on page 1–4

### **Feature Summary**

The following list summarizes the MAX V device family features:

- Low-cost, low-power, and non-volatile CPLD architecture

- Instant-on (0.5 ms or less) configuration time

- Standby current as low as 25 μA and fast power-down/reset operation

- Fast propagation delay and clock-to-output times

- Internal oscillator

- Emulated RSDS output support with a data rate of up to 200 Mbps

- Emulated LVDS output support with a data rate of up to 304 Mbps

- Four global clocks with two clocks available per logic array block (LAB)

- User flash memory block up to 8 Kbits for non-volatile storage with up to 1000 read/write cycles

- Single 1.8-V external supply for device core

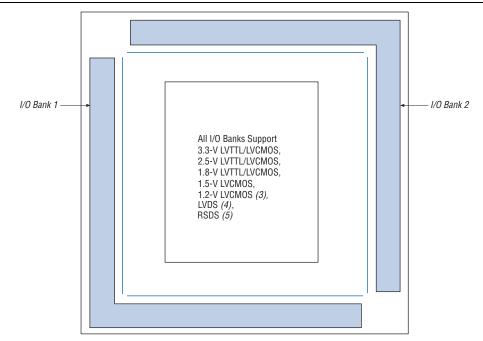

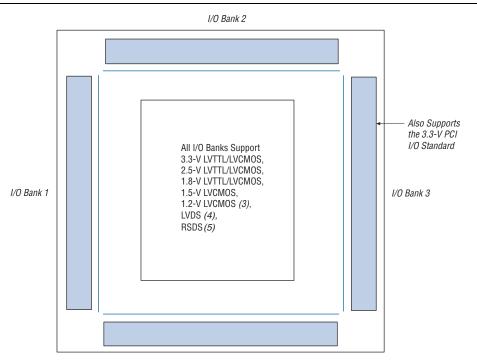

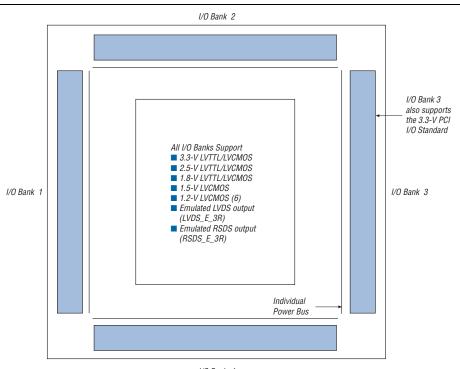

- MultiVolt I/O interface supporting 3.3-V, 2.5-V, 1.8-V, 1.5-V, and 1.2-V logic levels

- Bus-friendly architecture including programmable slew rate, drive strength, bus-hold, and programmable pull-up resistors

- Schmitt triggers enabling noise tolerant inputs (programmable per pin)

- **Feature Summary**

- I/Os are fully compliant with the PCI-SIG® PCI Local Bus Specification, revision 2.2 for 3.3-V operation

- Hot-socket compliant

- Built-in JTAG BST circuitry compliant with IEEE Std. 1149.1-1990

Table 1–1 lists the MAX V family features.

Table 1-1. MAX V Family Features

| Feature                       | 5M40Z | 5M80Z | 5M160Z | 5M240Z | 5M570Z | 5M1270Z | 5M2210Z |

|-------------------------------|-------|-------|--------|--------|--------|---------|---------|

| LEs                           | 40    | 80    | 160    | 240    | 570    | 1,270   | 2,210   |

| Typical Equivalent Macrocells | 32    | 64    | 128    | 192    | 440    | 980     | 1,700   |

| User Flash Memory Size (bits) | 8,192 | 8,192 | 8,192  | 8,192  | 8,192  | 8,192   | 8,192   |

| Global Clocks                 | 4     | 4     | 4      | 4      | 4      | 4       | 4       |

| Internal Oscillator           | 1     | 1     | 1      | 1      | 1      | 1       | 1       |

| Maximum User I/O pins         | 54    | 79    | 79     | 114    | 159    | 271     | 271     |

| t <sub>PD1</sub> (ns) (1)     | 7.5   | 7.5   | 7.5    | 7.5    | 9.0    | 6.2     | 7.0     |

| f <sub>CNT</sub> (MHz) (2)    | 152   | 152   | 152    | 152    | 152    | 304     | 304     |

| t <sub>SU</sub> (ns)          | 2.3   | 2.3   | 2.3    | 2.3    | 2.2    | 1.2     | 1.2     |

| t <sub>CO</sub> (ns)          | 6.5   | 6.5   | 6.5    | 6.5    | 6.7    | 4.6     | 4.6     |

#### Notes to Table 1–1:

- (1) t<sub>PD1</sub> represents a pin-to-pin delay for the worst case I/O placement with a full diagonal path across the device and combinational logic implemented in a single LUT and LAB that is adjacent to the output pin.

- (2) The maximum global clock frequency, f<sub>CNT</sub>, is limited by the I/O standard on the clock input pin. The 16-bit counter critical delay will run faster than this number.

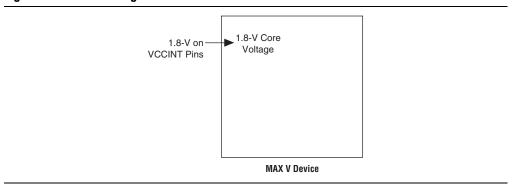

MAX V devices accept 1.8 V on their VCCINT pins. The 1.8-V  $V_{CCINT}$  external supply powers the device core directly. MAX V devices operate internally at 1.8 V. The supported MultiVolt I/O interface voltage levels ( $V_{CCIO}$ ) are 1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V.

MAX V devices are available in two speed grades: –4 and –5, with –4 being the fastest. For commercial applications, speed grades –C4 and –C5 are available. For industrial and automotive applications, speed grade –I5 and –A5 are available, respectively. These speed grades represent the overall relative performance, not any specific timing parameter.

For propagation delay timing numbers within each speed grade and density, refer to the *DC and Switching Characteristics for MAX V Devices* chapter.

MAX V devices are available in space-saving FineLine BGA (FBGA), Micro FineLine BGA (MBGA), plastic enhanced quad flat pack (EQFP), and thin quad flat pack (TQFP) packages (refer to Table 1–2 and Table 1–3). MAX V devices support vertical migration within the same package (for example, you can migrate between the 5M570Z, 5M1270Z, and 5M2210Z devices in the 256-pin FineLine BGA package). Vertical migration means that you can migrate to devices whose dedicated pins and JTAG pins are the same and power pins are subsets or supersets for a given package across device densities. The largest density in any package has the highest number of power pins; you must lay out for the largest planned density in a package to provide

the necessary power pins for migration. For I/O pin migration across densities, cross reference the available I/O pins using the device pin-outs for all planned densities of a given package type to identify which I/O pins can be migrated. The Quartus<sup>®</sup> II software can automatically cross-reference and place all pins for you when given a device migration list.

Table 1-2. MAX V Packages and User I/O Pins (Note 1)

| Device  | 64-Pin<br>MBGA | 64-Pin<br>EQFP | 68-Pin<br>MBGA | 100-Pin<br>TQFP | 100-Pin<br>MBGA | 144-Pin<br>TQFP | 256-Pin<br>FBGA | 324-Pin<br>FBGA |

|---------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 5M40Z   | ▲ 30           | <b>\$</b> 54   | _              | _               | _               | _               | _               | _               |

| 5M80Z   | ▼ 30           | 54             | <b>▲</b> 52    | <b>1</b> 79     | _               | _               | _               | _               |

| 5M160Z  | _              | ▼ 54           | 52             | 79              | <b>1</b> 79     | _               | _               | _               |

| 5M240Z  | _              | _              | 52             | 79              | 79              | <b>114</b>      | _               | _               |

| 5M570Z  | _              | _              | _              | 74              | 74              | 114             | 159             | _               |

| 5M1270Z | _              | _              | _              | _               | _               | <b>114</b>      | 211             | 271             |

| 5M2210Z | _              | _              | _              | _               | _               | _               | 203             | <b>271</b>      |

#### Note to Table 1-2:

Table 1-3. MAX V Package Sizes

| Package                  | 64-Pin<br>MBGA | 64-Pin<br>EQFP | 68-Pin<br>MBGA | 100-Pin<br>TQFP | 100-Pin<br>MBGA | 144-Pin<br>TQFP | 256-Pin<br>FBGA | 324-Pin<br>FBGA |

|--------------------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Pitch (mm)               | 0.5            | 0.4            | 0.5            | 0.5             | 0.5             | 0.5             | 1               | 1               |

| Area (mm²)               | 20.25          | 81             | 25             | 256             | 36              | 484             | 289             | 361             |

| Length × width (mm × mm) | 4.5 × 4.5      | 9 × 9          | 5 × 5          | 16 × 16         | 6 × 6           | 22 × 22         | 17 × 17         | 19 × 19         |

### **Integrated Software Platform**

The Quartus II software provides an integrated environment for HDL and schematic design entry, compilation and logic synthesis, full simulation and advanced timing analysis, and programming of MAX V devices.

For more information about the Quartus II software features, refer to the *Quartus II Handbook*.

You can debug your MAX V designs using In-System Sources and Probes Editor in the Quartus II software. This feature allows you to easily control any internal signal and provides you with a completely dynamic debugging environment.

For more information about the In-System Sources and Probes Editor, refer to the Design Debugging Using In-System Sources and Probes chapter of the Quartus II Handbook.

### **Device Pin-Outs**

For more information, refer to the MAX V Device Pin-Out Files page.

<sup>(1)</sup> Device packages under the same arrow sign have vertical migration capability.

#### Ordering Information

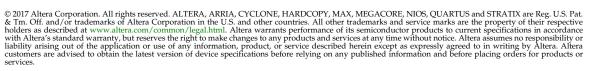

# **Ordering Information**Figure 1–1 shows the ordering codes for MAX V devices.

Figure 1-1. MAX V Device Packaging Ordering Information

### **Document Revision History**

Table 1–4 lists the revision history for this chapter.

Table 1-4. Document Revision History

| Date          | Version | Changes                            |

|---------------|---------|------------------------------------|

| May 2011      | 1.2     | ■ Updated Figure 1–1.              |

| May 2011      | 1.2     | ■ Updated Table 1–3.               |

| January 2011  | 1.1     | Updated "Feature Summary" section. |

| December 2010 | 1.0     | Initial release.                   |

### 2. MAX V Architecture

MV51002-1.0

This chapter describes the architecture of the MAX® V device and contains the following sections:

- "Functional Description" on page 2–1

- "Logic Array Blocks" on page 2–4

- "Logic Elements" on page 2–8

- "MultiTrack Interconnect" on page 2–14

- "Global Signals" on page 2–19

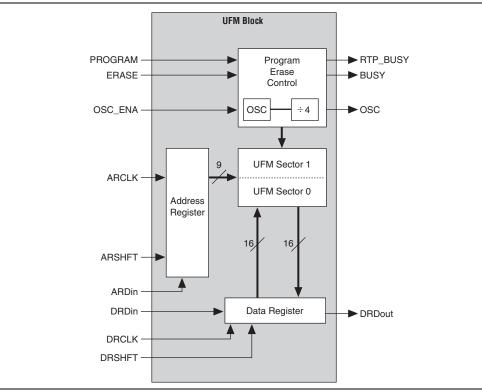

- "User Flash Memory Block" on page 2–21

- "Internal Oscillator" on page 2–22

- "Core Voltage" on page 2–25

- "I/O Structure" on page 2–26

### **Functional Description**

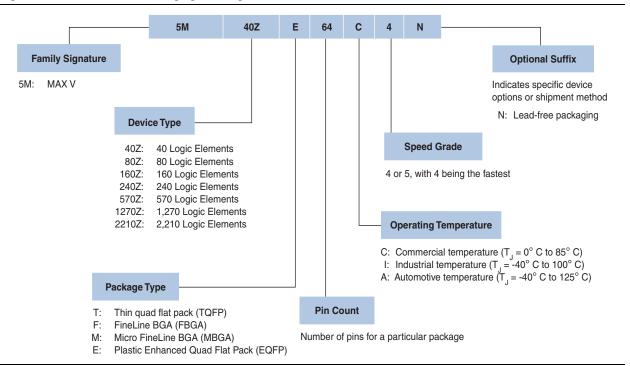

MAX V devices contain a two-dimensional row- and column-based architecture to implement custom logic. Row and column interconnects provide signal interconnects between the logic array blocks (LABs).

Each LAB in the logic array contains 10 logic elements (LEs). An LE is a small unit of logic that provides efficient implementation of user logic functions. LABs are grouped into rows and columns across the device. The MultiTrack interconnect provides fast granular timing delays between LABs. The fast routing between LEs provides minimum timing delay for added levels of logic versus globally routed interconnect structures.

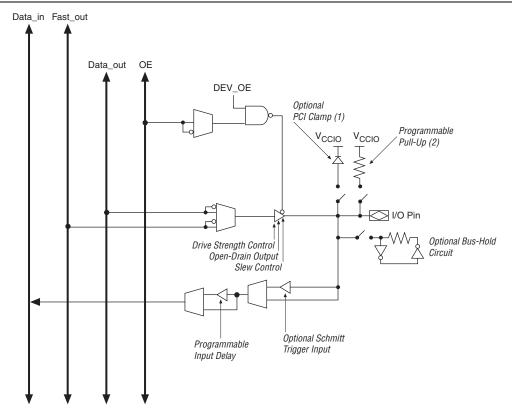

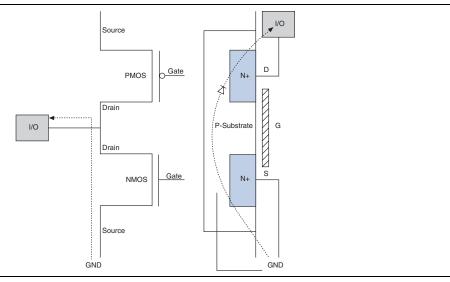

The I/O elements (IOEs) located after the LAB rows and columns around the periphery of the MAX V device feeds the I/O pins. Each IOE contains a bidirectional I/O buffer with several advanced features. I/O pins support Schmitt trigger inputs and various single-ended standards, such as 33-MHz,  $32\text{-bit PCI}^{\text{TM}}$ , and LVTTL.

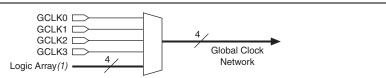

MAX V devices provide a global clock network. The global clock network consists of four global clock lines that drive throughout the entire device, providing clocks for all resources within the device. You can also use the global clock lines for control signals such as clear, preset, or output enable.

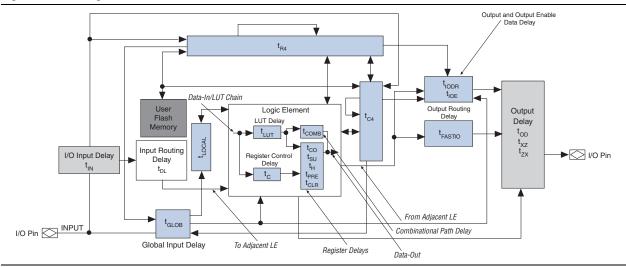

Figure 2–1 shows a functional block diagram of the MAX V device.

Figure 2-1. Device Block Diagram

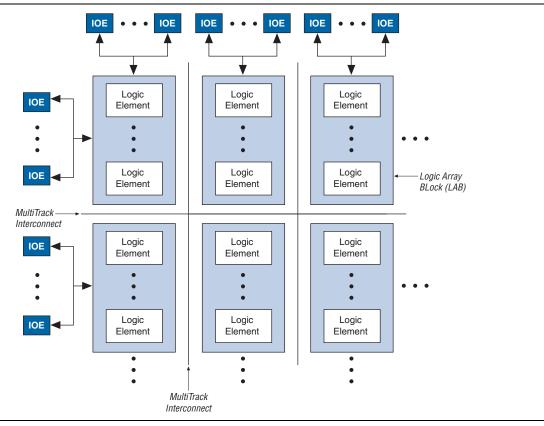

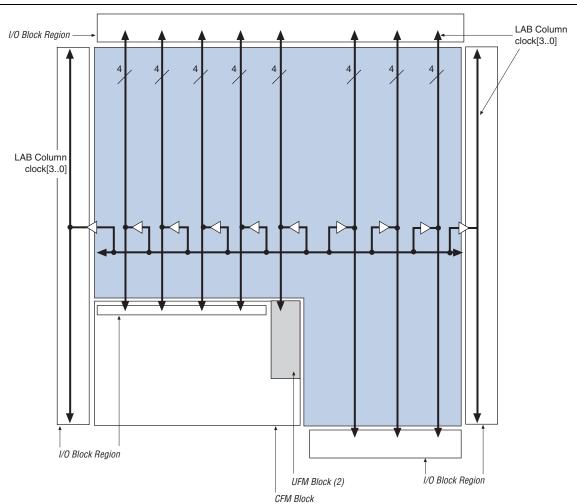

Each MAX V device contains a flash memory block within its floorplan. This block is located on the left side of the 5M40Z, 5M80Z, 5M160Z, and 5M240Z devices. On the 5M240Z (T144 package), 5M570Z, 5M1270Z, and 5M2210Z devices, the flash memory block is located on the bottom-left area of the device. The majority of this flash memory storage is partitioned as the dedicated configuration flash memory (CFM) block. The CFM block provides the non-volatile storage for all of the SRAM configuration information. The CFM automatically downloads and configures the logic and I/O at power-up, providing instant-on operation.

For more information about configuration upon power-up, refer to the *Hot Socketing* and *Power-On Reset for MAX V Devices* chapter.

A portion of the flash memory within the MAX V device is partitioned into a small block for user data. This user flash memory (UFM) block provides 8,192 bits of general-purpose user storage. The UFM provides programmable port connections to the logic array for reading and writing. There are three LAB rows adjacent to this block, with column numbers varying by device.

Table 2–1 lists the number of LAB rows and columns in each device, as well as the number of LAB rows and columns adjacent to the flash memory area. The long LAB rows are full LAB rows that extend from one side of row I/O blocks to the other. The short LAB rows are adjacent to the UFM block; their length is shown as width in LAB columns.

Table 2-1. Device Resources for MAX V Devices

| Doving      | UFM Blocks LAB Columns |               |               | Total LABs                 |            |

|-------------|------------------------|---------------|---------------|----------------------------|------------|

| Device      | UFINI DIUCKS           | LAD GUIUIIIIS | Long LAB Rows | Short LAB Rows (Width) (1) | TUIAI LADS |

| 5M40Z       | 1                      | 6             | 4             | _                          | 24         |

| 5M80Z       | 1                      | 6             | 4             | _                          | 24         |

| 5M160Z      | 1                      | 6             | 4             | _                          | 24         |

| 5M240Z (2)  | 1                      | 6             | 4             | _                          | 24         |

| 5M240Z (3)  | 1                      | 12            | 4             | 3 (3)                      | 57         |

| 5M570Z      | 1                      | 12            | 4             | 3 (3)                      | 57         |

| 5M1270Z (4) | 1                      | 16            | 7             | 3 (5)                      | 127        |

| 5M1270Z (5) | 1                      | 20            | 10            | 3 (7)                      | 221        |

| 5M2210Z     | 1                      | 20            | 10            | 3 (7)                      | 221        |

#### Notes to Table 2-1:

- (1) The width is the number of LAB columns in length.

- (2) Not applicable to T144 package of the 5M240Z device.

- (3) Only applicable to T144 package of the 5M240Z device.

- (4) Not applicable to F324 package of the 5M1270Z device.

- (5) Only applicable to F324 package of the 5M1270Z device.

Figure 2–2 shows a floorplan of a MAX V device.

Figure 2–2. Device Floorplan for MAX V Devices (Note 1)

#### Note to Figure 2-2:

(1) The device shown is a 5M570Z device. 5M1270Z and 5M2210Z devices have a similar floorplan with more LABs. For 5M40Z, 5M80Z, 5M160Z, and 5M240Z devices, the CFM and UFM blocks are located on the left side of the device.

### **Logic Array Blocks**

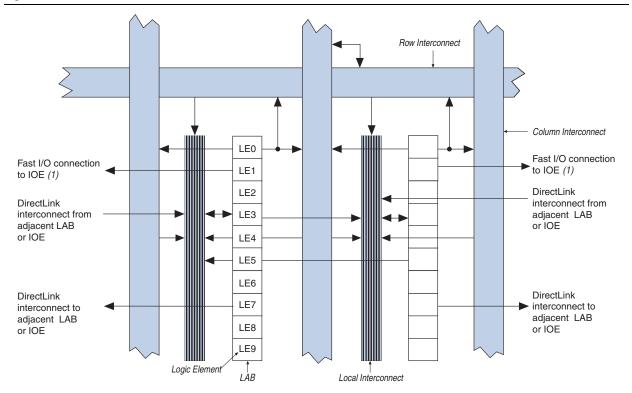

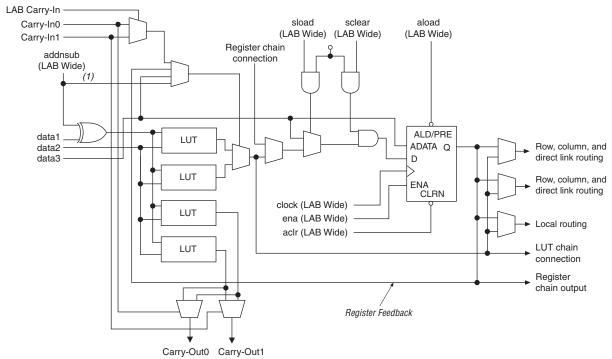

Each LAB consists of 10 LEs, LE carry chains, LAB control signals, a local interconnect, a look-up table (LUT) chain, and register chain connection lines. There are 26 possible unique inputs into an LAB, with an additional 10 local feedback input lines fed by LE outputs in the same LAB. The local interconnect transfers signals between LEs in the same LAB. LUT chain connections transfer the LUT output from one LE to the

adjacent LE for fast sequential LUT connections within the same LAB. Register chain connections transfer the output of one LE's register to the adjacent LE's register within an LAB. The Quartus<sup>®</sup> II software places associated logic within an LAB or adjacent LABs, allowing the use of local, LUT chain, and register chain connections for performance and area efficiency. Figure 2–3 shows the MAX V LAB.

Figure 2–3. LAB Structure for MAX V Devices

#### Note to Figure 2-3:

(1) Only from LABs adjacent to IOEs.

#### **LAB Interconnects**

Column and row interconnects and LE outputs within the same LAB drive the LAB local interconnect. Adjacent LABs, from the left and right, can also drive an LAB's local interconnect through the DirectLink connection. The DirectLink connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each LE can drive 30 other LEs through fast local and DirectLink interconnects. Figure 2–4 shows the DirectLink connection.

DirectLink interconnect from DirectLink interconnect from right LAB or IOE output left LAB or IOE output LE0 LE1 LE2 LE3 LE4 LE5 DirectLink DirectLink LE6 interconnect < interconnect to left to right LE7 I ocal LE8 Interconnect LE9 Logic Element LAB

Figure 2-4. DirectLink Connection

### **LAB Control Signals**

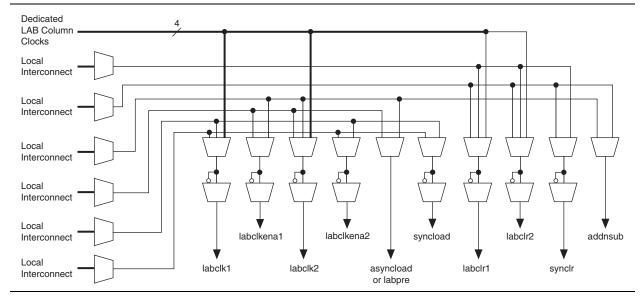

Each LAB contains dedicated logic for driving control signals to its LEs. The control signals include two clocks, two clock enables, two asynchronous clears, a synchronous clear, an asynchronous preset/load, a synchronous load, and add/subtract control signals, providing a maximum of 10 control signals at a time. Synchronous load and clear signals are generally used when implementing counters but they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked. For example, any LE in a particular LAB using the labclk1 signal also uses labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses both LAB-wide clock signals. Deasserting the clock enable signal turns off the LAB-wide clock.

Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. By default, the Quartus II software uses a NOT gate push-back technique to achieve preset. If you disable the NOT gate push-back option or assign a given register to power-up high using the Quartus II software, the preset is then achieved using the asynchronous load signal with asynchronous load data input tied high.

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This signal saves LE resources and improves performance for logic functions such as correlators and signed multipliers that alternate between addition and subtraction depending on data.

The LAB column clocks [3..0], driven by the global clock network, and LAB local interconnect generate the LAB-wide control signals. The MultiTrack interconnect structure drives the LAB local interconnect for non-global control signal generation. The MultiTrack interconnect's inherent low skew allows clock and control signal distribution in addition to data signals. Figure 2–5 shows the LAB control signal generation circuit.

Figure 2-5. LAB-Wide Control Signals

### **Logic Elements**

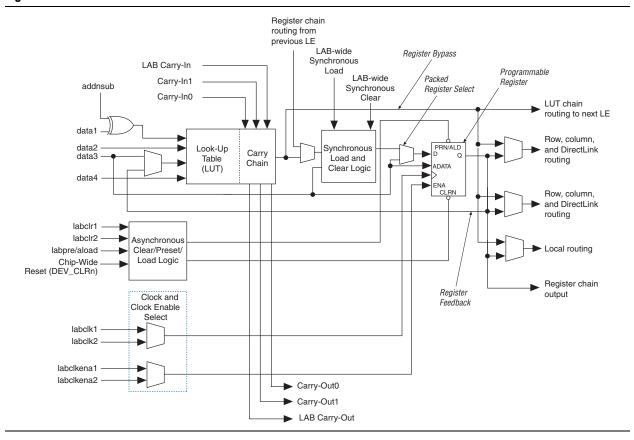

The smallest unit of logic in the MAX V architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry-select capability. A single LE also supports dynamic single-bit addition or subtraction mode that is selected by an LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and DirectLink interconnects as shown in Figure 2–6.

Figure 2-6. LE for MAX V Devices

You can configure each LE's programmable register for D, T, JK, or SR operation. Each register has data, true asynchronous load data, clock, clock enable, clear, and asynchronous load/preset inputs. Global signals, general purpose I/O (GPIO) pins, or any LE can drive the register's clock and clear control signals. Either GPIO pins or LEs can drive the clock enable, preset, asynchronous load, and asynchronous data. The asynchronous load data input comes from the data3 input of the LE. For combinational functions, the LUT output bypasses the register and drives directly to the LE outputs.

Each LE has three outputs that drive the local, row, and column routing resources. The LUT or register output can drive these three outputs independently. Two LE outputs drive either a column or row and DirectLink routing connections while one output drives the local interconnect resources. This configuration allows the LUT to drive one output while the register drives another output. This register packing feature

improves device utilization because the device can use the register and the LUT for unrelated functions. Another special packing mode allows the register output to feed back into the LUT of the same LE so that the register is packed with its own fan-out LUT. This mode provides another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

### **LUT Chain and Register Chain**

In addition to the three general routing outputs, the LEs within a LAB have LUT chain and register chain outputs. LUT chain connections allow LUTs within the same LAB to cascade together for wide input functions. Register chain outputs allow registers within the same LAB to cascade together. The register chain output allows a LAB to use LUTs for a single combinational function and the registers for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources. For more information about LUT chain and register chain connections, refer to "MultiTrack Interconnect" on page 2–14.

### addnsub Signal

The LE's dynamic adder/subtractor feature saves logic resources by using one set of LEs to implement both an adder and a subtractor. This feature is controlled by the LAB-wide control signal addnsub. The addnsub signal sets the LAB to perform either A+B or A-B. The LUT computes addition; subtraction is computed by adding the two's complement of the intended subtractor. The LAB-wide signal converts to two's complement by inverting the B bits within the LAB and setting carry-in to 1, which adds one to the LSB. The LSB of an adder/subtractor must be placed in the first LE of the LAB, where the LAB-wide addnsub signal automatically sets the carry-in to 1. The Quartus II Compiler automatically places and uses the adder/subtractor feature when using adder/subtractor parameterized functions.

### **LE Operating Modes**

The MAX V LE can operate in one of the following modes:

- "Normal Mode"

- "Dynamic Arithmetic Mode"

Each mode uses LE resources differently. In each mode, eight available inputs to the LE, the four data inputs from the LAB local interconnect, carry-in0 and carry-in1 from the previous LE, the LAB carry-in from the previous carry-chain LAB, and the register chain connection are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, asynchronous preset/load, synchronous clear, synchronous load, and clock enable control for the register. These LAB-wide signals are available in all LE modes. The addnsub control signal is allowed in arithmetic mode.

The Quartus II software, along with parameterized functions such as the library of parameterized modules (LPM) functions, automatically chooses the appropriate mode for common functions such as counters, adders, subtractors, and arithmetic functions.

#### **Normal Mode**

The normal mode is suitable for general logic applications and combinational functions. In normal mode, four data inputs from the LAB local interconnect are inputs to a four-input LUT as shown in Figure 2–7. The Quartus II Compiler automatically selects the carry-in or the data3 signal as one of the inputs to the LUT. Each LE can use LUT chain connections to drive its combinational output directly to the next LE in the LAB. Asynchronous load data for the register comes from the data3 input of the LE. LEs in normal mode support packed registers.

Figure 2-7. LE in Normal Mode

#### Note to Figure 2-7:

(1) This signal is only allowed in normal mode if the LE is after an adder/subtractor chain.

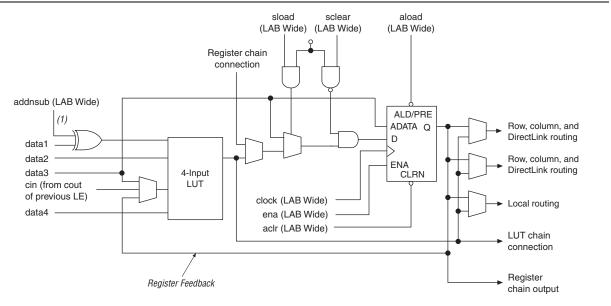

#### **Dynamic Arithmetic Mode**

The dynamic arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. A LE in dynamic arithmetic mode uses four 2-input LUTs configurable as a dynamic adder/subtractor. The first two 2-input LUTs compute two summations based on a possible carry-in of 1 or 0; the other two LUTs generate carry outputs for the two chains of the carry-select circuitry. As shown in Figure 2–8, the LAB carry-in signal selects either the carry-in0 or carry-in1 chain. The selected chain's logic level in turn determines which parallel sum is generated as a combinational or registered output. For example, when implementing an adder, the sum output is the selection of two possible calculated sums:

```

data1 + data2 + carry-in0

or

data1 + data2 + carry-in1

```

The other two LUTs use the data1 and data2 signals to generate two possible carry-out signals: one for a carry of 1 and the other for a carry of 0. The carry-in0 signal acts as the carry-select for the carry-out0 output and carry-in1 acts as the carry-select for the carry-out1 output. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The dynamic arithmetic mode also offers clock enable, counter enable, synchronous up/down control, synchronous clear, synchronous load, and dynamic adder/subtractor options. The LAB local interconnect data inputs generate the counter enable and synchronous up/down control signals. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs. The addnsub LAB-wide signal controls whether the LE acts as an adder or subtractor.

Figure 2–8. LE in Dynamic Arithmetic Mode

#### Note to Figure 2-8:

(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

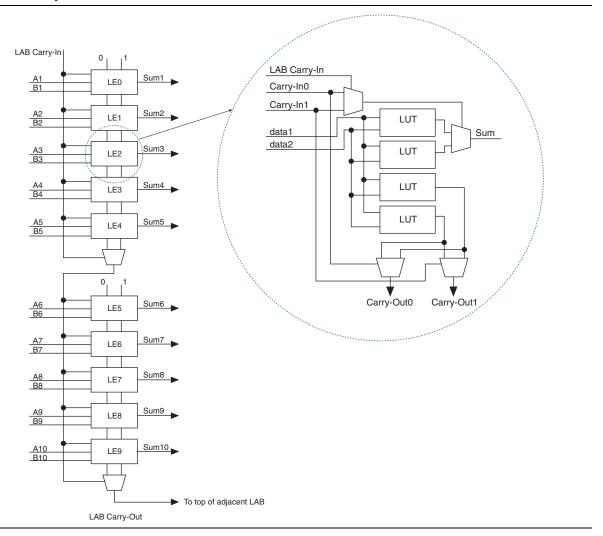

#### **Carry-Select Chain**

The carry-select chain provides a very fast carry-select function between LEs in dynamic arithmetic mode. The carry-select chain uses the redundant carry calculation to increase the speed of carry functions. The LE is configured to calculate outputs for a possible carry-in of 0 and carry-in of 1 in parallel. The carry-in0 and carry-in1 signals from a lower-order bit feed forward into the higher-order bit via the parallel carry chain and feed into both the LUT and the next portion of the carry chain. Carry-select chains can begin in any LE within an LAB.

The speed advantage of the carry-select chain is in the parallel pre-computation of carry chains. Because the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delays between LAB carry-in generation (LE5 and LE10) are now part of the critical path. This feature allows the MAX V architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

Figure 2–9 shows the carry-select circuitry in an LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT generates carry-out bits. An LAB-wide carry-in bit selects which chain is used for the addition of given inputs. The carry-in signal for each chain, carry-in0 or carry-in1, selects the carry-out to carry forward to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is fed to local, row, or column interconnects.

Figure 2-9. Carry-Select Chain

The Quartus II software automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions. The Quartus II software creates carry chains longer than 10 LEs by linking adjacent LABs within the same row together automatically. A carry chain can extend horizontally up to one full LAB row, but does not extend between LAB rows.

#### **Clear and Preset Logic Control**

LAB-wide signals control the logic for the register's clear and preset signals. The LE directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. MAX V devices support simultaneous preset/asynchronous load and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one preset signal.

In addition to the clear and preset ports, MAX V devices provide a chip-wide reset pin (DEV CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals and uses its own dedicated routing resources without using any of the four global resources. Driving this signal low before or during power-up prevents user mode from releasing clears within the design. This allows you to control when clear is released on a device that has just been powered-up. If not set for its chip-wide reset function, the DEV CLRn pin is a regular I/O pin.

By default, all registers in MAX V devices are set to power-up low. However, this power-up state can be set to high on individual registers during design entry using the Quartus II software.

#### LE RAM

The Quartus II memory compiler can configure the unused LEs as LE RAM.

MAX V devices support the following memory types:

- FIFO synchronous R/W

- FIFO asynchronous R/W

- 1 port SRAM

- 2 port SRAM

- 3 port SRAM

- shift registers

For more information about memory, refer to the *Internal Memory* (RAM and ROM) User Guide.

### **MultiTrack Interconnect**

In the MAX V architecture, connections between LEs, the UFM, and device I/O pins are provided by the MultiTrack interconnect structure. The MultiTrack interconnect consists of continuous, performance-optimized routing lines used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical design paths on faster interconnects to improve design performance.

The MultiTrack interconnect consists of row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and short delays between logic levels instead of large delays associated with global or long routing lines. Dedicated row interconnects route signals to and from LABs within the same row. These row resources include:

- DirectLink interconnects between LABs

- R4 interconnects traversing four LABs to the right or left

The DirectLink interconnect allows an LAB to drive into the local interconnect of its left and right neighbors. The DirectLink interconnect provides fast communication between adjacent LABs and blocks without using row interconnect resources.

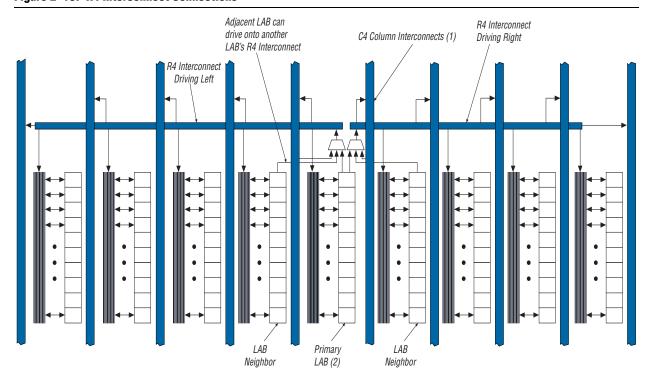

The R4 interconnects span four LABs and are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–10 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by row IOEs. For LAB interfacing, a primary LAB or horizontal LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnects. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 interconnects for connections from one row to another.

Figure 2-10. R4 Interconnect Connections

#### Notes to Figure 2-10:

- (1) C4 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

The column interconnect operates similarly to the row interconnect. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs and row and column IOEs. These column resources include:

- LUT chain interconnects within an LAB

- Register chain interconnects within an LAB

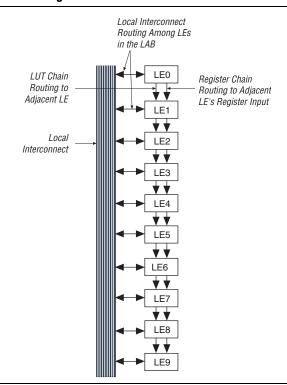

- C4 interconnects traversing a distance of four LABs in an up and down direction

MAX V devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using LUT chain connections and register chain connections. The LUT chain connection allows the combinational output of an LE to directly drive the fast input of the LE right below it, bypassing the local interconnect. These resources can be used as a high-speed connection for wide fan-in functions from LE 1 to LE 10 in the same LAB. The register chain connection allows the register output of one LE to connect directly to the register input of the next LE in the LAB for fast shift registers. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–11 shows the LUT chain and register chain interconnects.

Figure 2-11. LUT Chain and Register Chain Interconnects

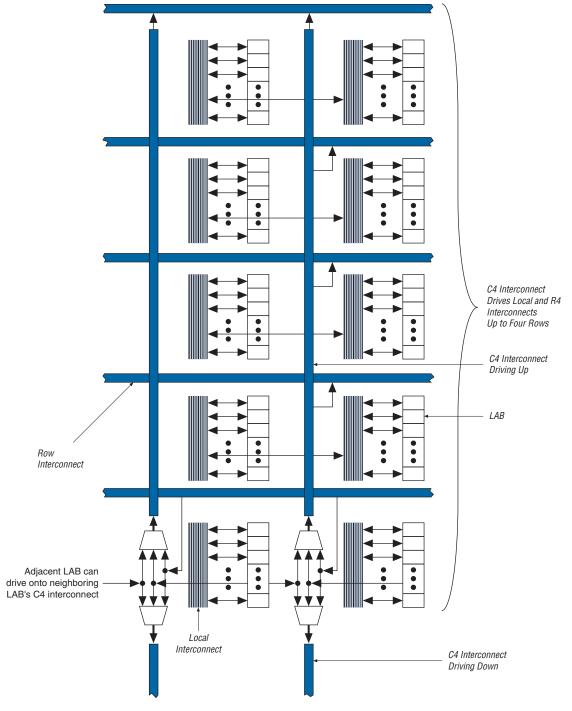

The C4 interconnects span four LABs up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–12 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by column and row IOEs. For LAB interconnection, a primary LAB or its vertical LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

Figure 2–12. C4 Interconnect Connections (Note 1)

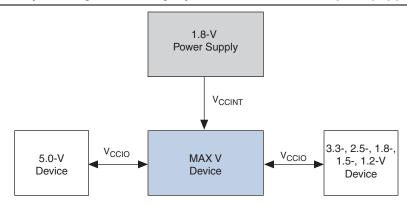

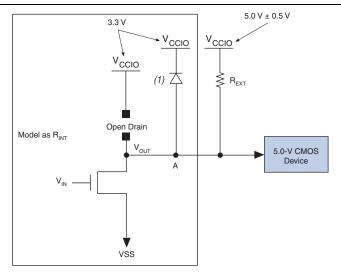

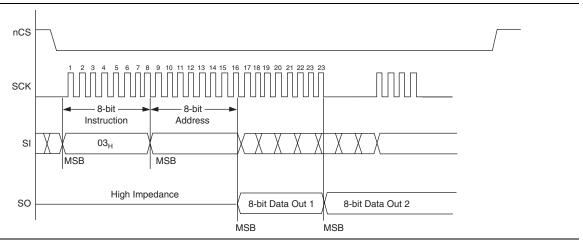

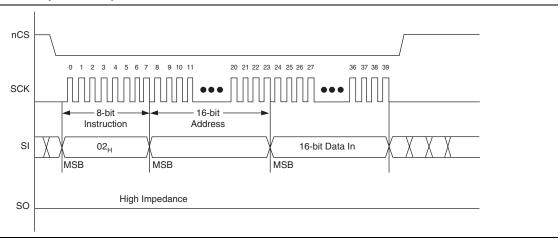

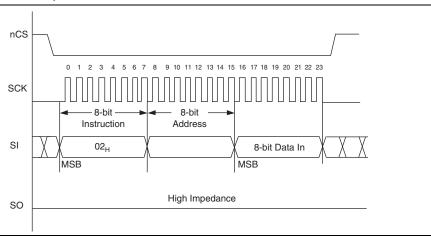

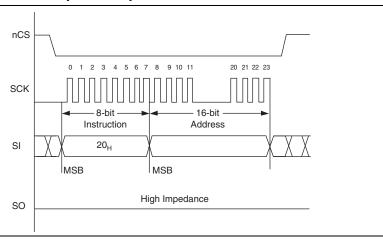

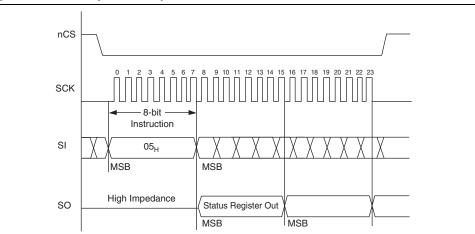

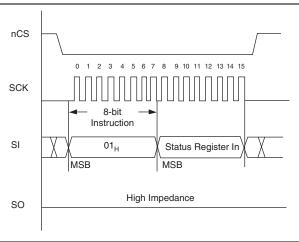

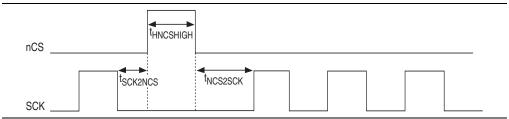

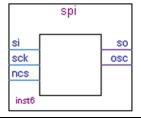

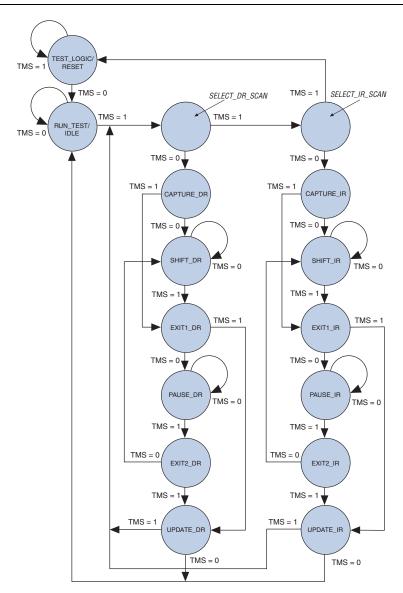

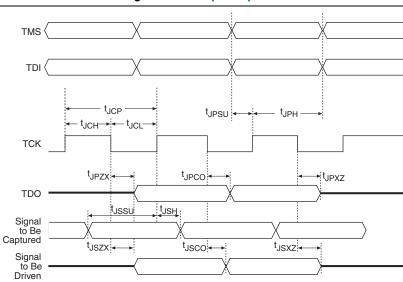

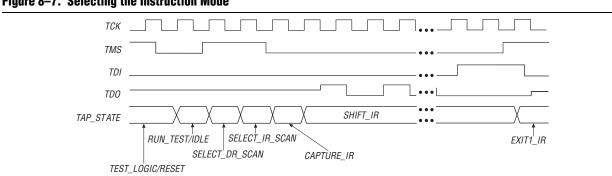

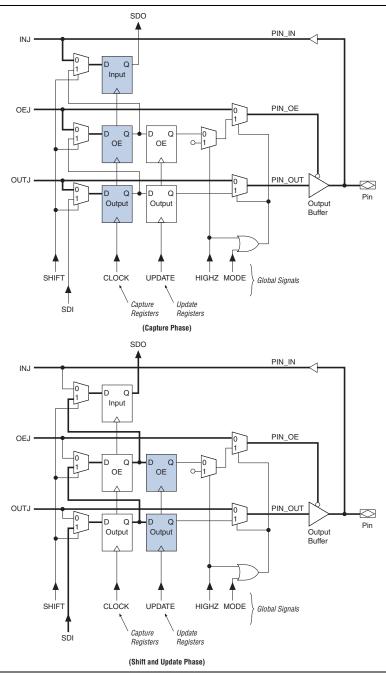

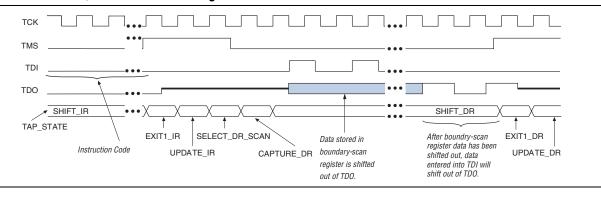

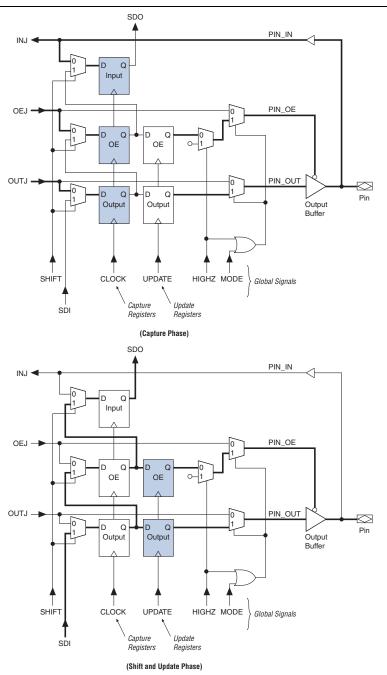

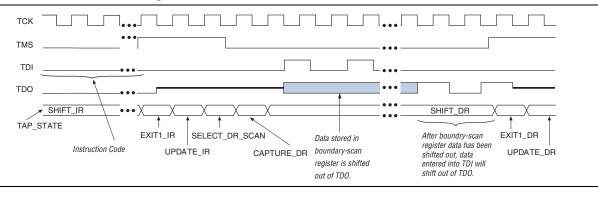

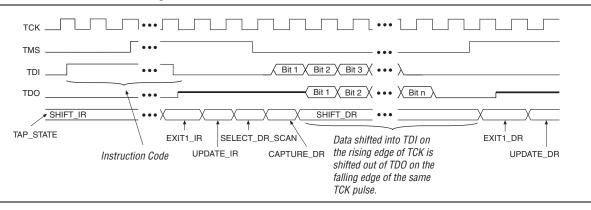

#### Note to Figure 2–12: