# LVPECL, LVDS, and HCSL Crystal Oscillator

#### **Features**

- 40 fs<sub>RMS</sub> Phase Jitter Typical, 12 kHz to 20 MHz

- 3rd OT or Fundamental Crystal Design

- Extended Operating Temperature Range: –40°C to +105°C

- 100 MHz to 200 MHz Output Frequencies

- Excellent Power Supply Rejection Ratio

- · Glitch Free Output upon Power-Up and Enable

- Hermetically Sealed 3.2 mm × 2.5 mm Ceramic Package

- Product is Compliant to RoHS Directive and Fully Compatible with Lead-Free Assembly

### **Applications**

- · Medical, Ultrasound

- · Ethernet, GbE, SynchE

- · Fibre Channel

- PON

- · Clock Source for A/Ds, D/As, FPGAs

- · Test and Measurement

- Storage Area Network

#### **General Description**

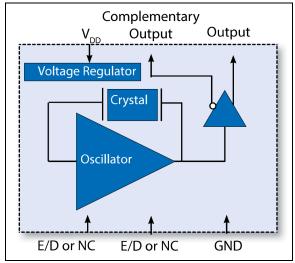

Microchip's VC-830 crystal oscillator is a quartz-stabilized, differential output oscillator that operates off a 1.8V, 2.5V, or 3.3V power supply in a hermetically sealed 3.2 mm × 2.5 mm ceramic package.

# **Block Diagram**

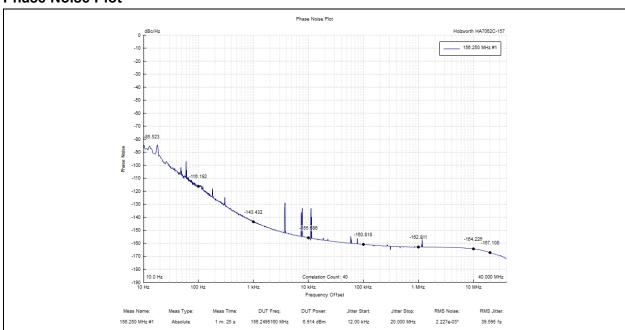

#### **Phase Noise Plot**

FIGURE 0-1: RMS Jitter, 40 fs<sub>RMS</sub> at 156.25 MHz, over 12 kHz to 20 MHz.

#### 1.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| Supply Voltage                            |  |

|-------------------------------------------|--|

| Enable Disable Voltage                    |  |

| ESD Rating, Human Body Model (Note 1)     |  |

| ESD Rating, Charged Device Model (Note 1) |  |

| Storage Temperature (T <sub>S</sub> )     |  |

| Junction Temperature (T <sub>1</sub> )    |  |

† **Notice:** Stresses in excess of the Absolute Maximum Ratings can permanently damage the device. Functional operation is not implied at these or any other conditions in excess of conditions represented in the operational sections of this data sheet. Exposure to Absolute Maximum Ratings for extended periods may adversely affect device reliability.

Note 1: Although ESD protection circuitry has been designed into the VC-830, proper precautions should be taken when handling and mounting. Microchip employs a Human Body Model (HBM) and a Charged Device Model (CDM) for ESD susceptibility testing and design protection evaluation. ESD thresholds are dependent on the circuit parameters used to define the model. Although no industry standard has been adopted for the CDM, a standard resistance of 1.5 kΩ and capacitance of 100 pF is widely used and therefore can be used for comparison purposes.

### **ELECTRICAL CHARACTERISTICS, LVPECL OPTION**

| Parameter                        | Sym.            | Min.                       | Тур. | Max.                       | Units | Conditions              |  |

|----------------------------------|-----------------|----------------------------|------|----------------------------|-------|-------------------------|--|

| Cumply Voltage (Note 1)          | \/              | 2.375                      | 2.5  | 2.625                      | V     | Oud a visu or Oution    |  |

| Supply Voltage (Note 1)          | $V_{DD}$        | 3.135                      | 3.3  | 3.465                      | V     | Ordering Option         |  |

| Current Consumption              | I <sub>DD</sub> | _                          | 1    | 66                         | mA    | _                       |  |

| Frequency                        |                 |                            |      |                            |       |                         |  |

| Nominal Frequency                | $f_N$           | 100                        | 1    | 200                        | MHz   | Ordering Option         |  |

|                                  |                 | _                          | 1    | ±25                        |       |                         |  |

| Stability (Nata 2)               | _               | _                          | 1    | ±30                        | ppm   | Ordering Option         |  |

| Stability (Note 2)               |                 | _                          | 1    | ±50                        |       |                         |  |

|                                  |                 | _                          | _    | ±100                       |       |                         |  |

| Outputs                          |                 |                            |      |                            |       |                         |  |

| Output Logic Level High (Note 3) | V <sub>OH</sub> | V <sub>DD</sub> –<br>1.085 | _    | V <sub>DD</sub> –<br>0.880 | V     |                         |  |

| Output Logic Level Low (Note 3)  | V <sub>OL</sub> | V <sub>DD</sub> –<br>1.810 | _    | V <sub>DD</sub> –<br>1.620 | V     | V <sub>DD</sub> = +2.5V |  |

| Output Logic Level High (Note 3) | V <sub>OH</sub> | V <sub>DD</sub> –<br>1.085 | _    | V <sub>DD</sub> –<br>0.880 | .,,   | V <sub>DD</sub> = +3.3V |  |

| Output Logic Level Low (Note 3)  | V <sub>OL</sub> | V <sub>DD</sub> –<br>1.810 | _    | V <sub>DD</sub> –<br>1.620 | V     |                         |  |

- Note 1: The VC-830 power supply should be filtered. For example, a 10 μF, 0.1 μF, and 0.01 μF capacitor.

- 2: Includes calibration tolerance, operating temperature, supply voltage variations, aging, and IR reflow.

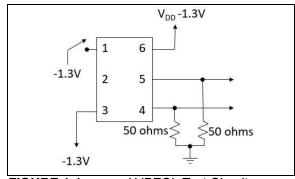

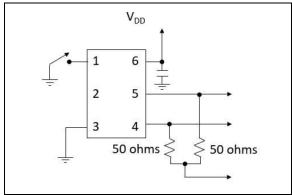

- 3: Figure 1-1 defines the test circuit and Figure 1-2 defines these parameters.

- 4: Output rise and fall time will be 600 ps (max.) for -40°C to +105°C operating temperature range.

- 5: Duty Cycle is measured as On/Time Period.

- **6:** Measured using an Agilent E5052 Signal Source Analyzer at 25°C.

- 7: Outputs will be enabled if Enable/Disable is left open. There is an oscillation detection circuit that ensures glitch free output upon power-up or enable.

- 8: In order to reduce current, the pull-up resistance is higher when V<sub>DD</sub> is set to ground.

# **ELECTRICAL CHARACTERISTICS, LVPECL OPTION (CONTINUED)**

| Parameter                                              | Sym.                           | Min.                  | Тур.                     | Max.                  | Units       | Conditions      |  |

|--------------------------------------------------------|--------------------------------|-----------------------|--------------------------|-----------------------|-------------|-----------------|--|

| Output Rise and Fall Time (Note 3)                     | t <sub>r</sub> /t <sub>f</sub> | _                     | _                        | 400                   | ps          | Note 4          |  |

| Load                                                   | _                              | 50Ω                   | into V <sub>DD</sub> – 2 | 2.0V                  | _           | _               |  |

| Duty Cycle (Note 5)                                    | DC                             | 45                    | _                        | 55                    | %           | _               |  |

|                                                        |                                | _                     | -79                      | _                     |             | 10 Hz           |  |

|                                                        |                                | _                     | -110                     | _                     |             | 100 Hz          |  |

|                                                        |                                | _                     | -130                     | _                     |             | 1 kHz           |  |

| Phase Noise, 3.3V, 156.25 MHz                          |                                | _                     | -154                     | _                     | 4D - /I I - | 10 kHz          |  |

| (Note 6)                                               | φ <sub>N</sub>                 | _                     | -160                     | _                     | dBc/Hz      | 100 kHz         |  |

|                                                        |                                | _                     | -163                     | _                     |             | 1 MHz           |  |

|                                                        |                                | _                     | -163                     | _                     |             | 10 MHz          |  |

|                                                        |                                | _                     | -167                     | _                     |             | 20 MHz          |  |

| Phase Jitter, 156.25 MHz,<br>12 kHz to 20 MHz (Note 6) | фЈ                             | _                     | 40                       | 60                    | fs          | _               |  |

| Enable/Disable                                         |                                |                       |                          |                       |             |                 |  |

| Outputs Enabled (Note 7)                               | V <sub>IH</sub>                | 0.7 * V <sub>DD</sub> | _                        | _                     | V           | _               |  |

| Outputs Disabled                                       | V <sub>IL</sub>                | _                     | _                        | 0.3 * V <sub>DD</sub> | V           | _               |  |

| Disable Time                                           | t <sub>D</sub>                 | _                     | _                        | 200                   | ns          | _               |  |

| E/D Pull-Up Resistance (Note 8)                        | _                              | 0.5                   | _                        | 2                     | ΜΩ          | E/D = GND       |  |

| E/D Pull-Up Resistance                                 | _                              | 30                    | _                        | 150                   | kΩ          | $E/D = V_{DD}$  |  |

| Start-Up Time                                          | t <sub>SU</sub>                |                       |                          | 10                    | ms          | _               |  |

|                                                        |                                | -10                   | _                        | 70                    |             |                 |  |

| Operating Temperature                                  | $T_OP$                         | -40                   | _                        | 85                    | °C          | Ordering Option |  |

|                                                        |                                | -40                   | _                        | 105                   |             |                 |  |

- Note 1: The VC-830 power supply should be filtered. For example, a 10 μF, 0.1 μF, and 0.01 μF capacitor.

- 2: Includes calibration tolerance, operating temperature, supply voltage variations, aging, and IR reflow.

- 3: Figure 1-1 defines the test circuit and Figure 1-2 defines these parameters.

- 4: Output rise and fall time will be 600 ps (max.) for -40°C to +105°C operating temperature range.

- 5: Duty Cycle is measured as On/Time Period.

- **6:** Measured using an Agilent E5052 Signal Source Analyzer at 25°C.

- 7: Outputs will be enabled if Enable/Disable is left open. There is an oscillation detection circuit that ensures glitch free output upon power-up or enable.

- 8: In order to reduce current, the pull-up resistance is higher when  $V_{DD}$  is set to ground.

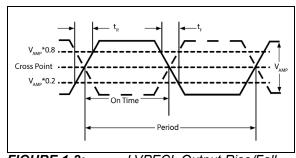

FIGURE 1-2: LVPECL Output Rise/Fall Time.

### **ELECTRICAL CHARACTERISTICS, LVDS OPTION**

| Parameter                                   | Sym.                           | Min.              | Тур. | Max.  | Units | Conditions      |

|---------------------------------------------|--------------------------------|-------------------|------|-------|-------|-----------------|

|                                             |                                | 1.71              | 1.8  | 1.89  |       |                 |

| Supply Voltage (Note 1)                     | $V_{DD}$                       | 2.37              | 2.5  | 2.625 | V     | Ordering Option |

|                                             |                                | 3.135             | 3.3  | 3.465 |       |                 |

|                                             |                                | 1                 | _    | 25    |       | 1.8V            |

| Current Consumption                         | $I_{DD}$                       | 1                 | _    | 29    | mA    | 2.5V            |

|                                             |                                | 1                 | _    | 30    |       | 3.3V            |

| Frequency                                   |                                |                   |      |       |       |                 |

| Nominal Frequency                           | $f_N$                          | 100               | _    | 200   | MHz   | Ordering Option |

|                                             |                                | _                 | _    | ±25   |       |                 |

| Stability (Note 2)                          |                                | _                 | _    | ±30   | nnm   | Ordering Option |

| Stability (Note 2)                          | _                              | _                 | _    | ±50   | ppm   | Ordering Option |

|                                             |                                | _                 | _    | ±100  |       |                 |

| Outputs                                     |                                |                   |      |       |       |                 |

| Output Logic Level High (Note 3)            | $V_{OH}$                       | _                 | 1.43 | 1.6   | V     |                 |

| Output Logic Level Low (Note 3)             | $V_{OL}$                       | 0.9               | 1.10 | _     | V     |                 |

| Output Amplitude                            | _                              | 247               | 350  | 454   | mV    | _               |

| Differential Output Error                   | _                              | _                 | _    | 50    | mV    | _               |

| Offset Voltage                              | _                              | 1.125             | 1.25 | 1.375 | V     | _               |

| Offset Voltage Error                        | _                              | _                 | _    | 50    | mV    | _               |

| Output Leakage Current, Outputs<br>Disabled | _                              | _                 | _    | 30    | μA    | _               |

| Output Rise and Fall Time (Note 3)          | t <sub>r</sub> /t <sub>f</sub> | _                 | _    | 300   | ps    | Note 4          |

| Load                                        | _                              | 100Ω Differential |      |       | _     | _               |

| Duty Cycle (Note 5)                         | DC                             | 45                | _    | 55    | %     | _               |

- Note 1: The VC-830 power supply should be filtered. For example, a 10  $\mu$ F, 0.1  $\mu$ F, and 0.01  $\mu$ F capacitor.

- 2: Includes calibration tolerance, operating temperature, supply voltage variations, aging, and IR reflow.

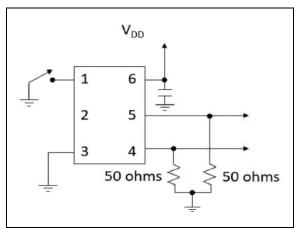

- 3: Figure 1-3 defines the test circuit and Figure 1-2 defines these parameters.

- 4: Output rise and fall time will be 600 ps (max.) for -40°C to +105°C operating temperature range.

- 5: Duty Cycle is measured as On/Time Period.

- **6:** Measured using an Agilent E5052 Signal Source Analyzer at 25°C.

- 7: Outputs will be enabled if Enable/Disable is left open. There is an oscillation detection circuit that ensures glitch free output upon power-up or enable.

- 8: In order to reduce current, the pull-up resistance is higher when V<sub>DD</sub> is set to ground.

# **ELECTRICAL CHARACTERISTICS, LVDS OPTION (CONTINUED)**

| Parameter                                              | Sym.            | Min.                  | Тур. | Max.                  | Units  | Conditions      |  |

|--------------------------------------------------------|-----------------|-----------------------|------|-----------------------|--------|-----------------|--|

|                                                        |                 | _                     | -79  | _                     |        | 10 Hz           |  |

|                                                        |                 | _                     | -110 | _                     |        | 100 Hz          |  |

|                                                        |                 | _                     | -130 | _                     |        | 1 kHz           |  |

| Phase Noise, 3.3V, 156.25 MHz                          |                 | _                     | -154 | _                     | dDa/Uz | 10 kHz          |  |

| (Note 6)                                               | φ <sub>N</sub>  | _                     | -160 | _                     | dBc/Hz | 100 kHz         |  |

|                                                        |                 | _                     | -162 | _                     |        | 1 MHz           |  |

|                                                        |                 | _                     | -163 | _                     |        | 10 MHz          |  |

|                                                        |                 | _                     | -164 | _                     |        | 20 MHz          |  |

| Phase Jitter, 156.25 MHz,<br>12 kHz to 20 MHz (Note 6) | φЈ              | _                     | 43   | 64                    | fs     | _               |  |

| Enable/Disable                                         |                 |                       |      |                       |        |                 |  |

| Outputs Enabled (Note 7)                               | V <sub>IH</sub> | 0.7 * V <sub>DD</sub> | _    | _                     | V      | _               |  |

| Outputs Disabled                                       | $V_{IL}$        | _                     | _    | 0.3 * V <sub>DD</sub> | V      | _               |  |

| Disable Time                                           | t <sub>D</sub>  | _                     | _    | 200                   | ns     | _               |  |

| E/D Pull-Up Resistance (Note 8)                        | 1               | 0.5                   | _    | 2                     | МΩ     | E/D = GND       |  |

| E/D Pull-Up Resistance                                 | 1               | 30                    | _    | 150                   | kΩ     | $E/D = V_{DD}$  |  |

| Start-Up Time                                          | t <sub>SU</sub> | _                     | _    | 10                    | ms     | _               |  |

|                                                        |                 | -10                   | _    | 70                    |        |                 |  |

| Operating Temperature                                  | T <sub>OP</sub> | -40                   | _    | 85                    | °C     | Ordering Option |  |

|                                                        |                 | -40                   | _    | 105                   |        |                 |  |

- **Note 1:** The VC-830 power supply should be filtered. For example, a 10  $\mu$ F, 0.1  $\mu$ F, and 0.01  $\mu$ F capacitor.

- 2: Includes calibration tolerance, operating temperature, supply voltage variations, aging, and IR reflow.

- **3:** Figure 1-3 defines the test circuit and Figure 1-2 defines these parameters.

- 4: Output rise and fall time will be 600 ps (max.) for -40°C to +105°C operating temperature range.

- 5: Duty Cycle is measured as On/Time Period.

- **6:** Measured using an Agilent E5052 Signal Source Analyzer at 25°C.

- **7:** Outputs will be enabled if Enable/Disable is left open. There is an oscillation detection circuit that ensures glitch free output upon power-up or enable.

- 8: In order to reduce current, the pull-up resistance is higher when V<sub>DD</sub> is set to ground.

FIGURE 1-3: LVDS Test Circuit.

# **ELECTRICAL CHARACTERISTICS, HCSL OPTION**

| Parameter                                               | Sym.                           | Min.                  | Тур.       | Max.                  | Units       | Conditions       |  |

|---------------------------------------------------------|--------------------------------|-----------------------|------------|-----------------------|-------------|------------------|--|

|                                                         |                                | 1.71                  | 1.8        | 1.81                  |             |                  |  |

| Supply Voltage (Note 1)                                 | $V_{DD}$                       | 2.375                 | 2.5        | 2.625                 | V           | Ordering Option  |  |

|                                                         |                                | 3.135                 | 3.3        | 3.465                 |             |                  |  |

| Current Consumption                                     | I <sub>DD</sub>                | _                     | _          | 46                    | mA          | 1.8V, 2.5V, 3.3V |  |

| Frequency                                               |                                |                       |            |                       |             |                  |  |

| Nominal Frequency                                       | f <sub>N</sub>                 | 100                   | _          | 200                   | MHz         | Ordering Option  |  |

|                                                         |                                | _                     | _          | ±25                   |             |                  |  |

| 0, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1,               |                                | _                     | _          | ±30                   |             | 0 1 : 0 ::       |  |

| Stability (Note 2)                                      | _                              | _                     | _          | ±50                   | ppm         | Ordering Option  |  |

|                                                         |                                | _                     | _          | ±100                  |             |                  |  |

| Outputs                                                 |                                |                       |            |                       |             |                  |  |

| Output Logic Level High (Note 3)                        | V <sub>OH</sub>                | 0.6                   | _          | 0.9                   | .,          |                  |  |

| Output Logic Level Low (Note 3)                         | V <sub>OL</sub>                | -0.15 — 0.15          |            | 0.15                  | V           |                  |  |

| Output Leakage Current, Outputs<br>Disabled             | _                              | 30                    |            | 30                    | μA          | _                |  |

| Output Rise and Fall Time (Note 3)                      | t <sub>r</sub> /t <sub>f</sub> | _                     | _          | 600                   | ps          | _                |  |

| Load                                                    | _                              | ,                     | 50Ω to GNE | )                     | _           | _                |  |

| Duty Cycle (Note 4)                                     | DC                             | 45                    | _          | 55                    | %           | _                |  |

|                                                         |                                | _                     | -79        | _                     |             | 10 Hz            |  |

|                                                         |                                | _                     | -110       | _                     |             | 100 Hz           |  |

|                                                         |                                | _                     | -130       | _                     |             | 1 kHz            |  |

| Phase Noise, 3.3V, 156.25 MHz                           |                                | _                     | -154       | _                     | -ID - /I I- | 10 kHz           |  |

| (Note 5)                                                | φ <sub>N</sub>                 | _                     | -160       | _                     | dBc/Hz      | 100 kHz          |  |

|                                                         |                                | _                     | -162       | _                     |             | 1 MHz            |  |

|                                                         |                                | _                     | -163       | _                     |             | 10 MHz           |  |

|                                                         |                                | _                     | -164       | _                     |             | 20 MHz           |  |

| Phase Jitter, 100.000 MHz,<br>12 kHz to 20 MHz (Note 5) | φЈ                             | _                     | 55         | _                     | fs          | _                |  |

| Enable/Disable                                          |                                |                       |            |                       |             |                  |  |

| Outputs Enabled (Note 6)                                | $V_{IH}$                       | 0.7 * V <sub>DD</sub> |            | _                     | V           |                  |  |

| Outputs Disabled                                        | $V_{IL}$                       | _                     | _          | 0.3 * V <sub>DD</sub> | V           | _                |  |

- Note 1: The VC-830 power supply should be filtered. For example, a 10 μF, 0.1 μF, and 0.01 μF capacitor.

- 2: Includes calibration tolerance, operating temperature, supply voltage variations, aging, and IR reflow.

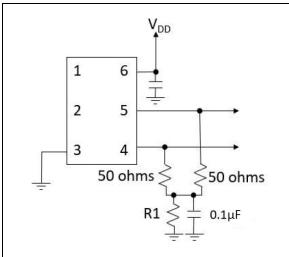

- **3:** Figure 1-3 defines the test circuit and Figure 1-2 defines these parameters.

- 4: Duty Cycle is measured as On/Time Period.

- **5**: Measured using an Agilent E5052 Signal Source Analyzer at 25°C.

- **6:** Outputs will be enabled if Enable/Disable is left open. There is an oscillation detection circuit that ensures glitch free output upon power-up or enable.

- 7: In order to reduce current, the pull-up resistance is higher when  $V_{\mbox{\scriptsize DD}}$  is set to ground.

# **ELECTRICAL CHARACTERISTICS, HCSL OPTION (CONTINUED)**

| Parameter                       | Sym.            | Min. | Тур. | Max. | Units | Conditions      |

|---------------------------------|-----------------|------|------|------|-------|-----------------|

| Disable Time                    | t <sub>D</sub>  | _    | _    | 200  | ns    | _               |

| E/D Pull-Up Resistance (Note 7) | _               | 0.5  | _    | 2    | МΩ    | E/D = GND       |

| E/D Pull-Up Resistance          | _               | 30   | _    | 150  | kΩ    | $E/D = V_{DD}$  |

| Start-Up Time                   | t <sub>SU</sub> | _    | _    | 10   | ms    | _               |

|                                 |                 | -10  | _    | 70   |       |                 |

| Operating Temperature           | T <sub>OP</sub> | -40  | _    | 85   | °C    | Ordering Option |

|                                 |                 | -40  | _    | 105  |       |                 |

- Note 1: The VC-830 power supply should be filtered. For example, a 10  $\mu$ F, 0.1  $\mu$ F, and 0.01  $\mu$ F capacitor.

- 2: Includes calibration tolerance, operating temperature, supply voltage variations, aging, and IR reflow.

- 3: Figure 1-3 defines the test circuit and Figure 1-2 defines these parameters.

- 4: Duty Cycle is measured as On/Time Period.

- **5:** Measured using an Agilent E5052 Signal Source Analyzer at 25°C.

- **6:** Outputs will be enabled if Enable/Disable is left open. There is an oscillation detection circuit that ensures glitch free output upon power-up or enable.

- 7: In order to reduce current, the pull-up resistance is higher when  $V_{\mbox{\scriptsize DD}}$  is set to ground.

FIGURE 1-4: HCSL Test Circuit.

# 2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

TABLE 2-1: PIN FUNCTION TABLE

| Pin Number | Pin Name        | Description                     |

|------------|-----------------|---------------------------------|

| 1          | E/D or NC       | Enable/Disable or No Connect.   |

| 2          | E/D or NC       | Enable/Disable or No Connect.   |

| 3          | GND             | Electrical and lid ground.      |

| 4          | f <sub>O</sub>  | Output frequency.               |

| 5          | Cf <sub>O</sub> | Complementary output frequency. |

| 6          | $V_{DD}$        | Supply voltage.                 |

Note: Pin 2 can be E/D and Pin 1 will be NC. Use Ordering Option B.

TABLE 2-2: ENABLE/DISABLE FUNCTION

| E/D Pin | Output         |

|---------|----------------|

| High    | Clock Output   |

| Open    | Clock Output   |

| Low     | High Impedance |

#### 3.0 APPLICATION DIAGRAMS

### 3.1 LVPECL Application Diagrams

The VC-830 incorporates a standard PECL output scheme, which are unterminated FET drains. There are numerous application notes on terminating and interfacing PECL logic and the two most common methods are a single resistor to ground (Figure 3-1) and a pull-up/pull-down scheme as shown in Figure 3-2. AC-coupling capacitors are optional, depending on the application and the input logic requirements of the next stage.

One of the most important considerations is terminating the Output and Complementary Outputs equally. An unused output should not be left unterminated because if one of the two outputs is left open, it will result in excessive jitter on both. PCB layout must take this and  $50\Omega$  impedance matching into account. Load matching and power supply noise are the main contributors to jitter related problems.

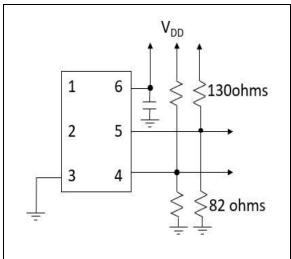

FIGURE 3-1: LVPECL Pull-Down Resistor Termination Scheme.

Figure 3-1 shows one option to terminate LVPECL outputs and is optimized to reduce common mode noise. R1 is  $50\Omega$  for 3.3V supply voltage and  $18\Omega$  for 2.5V.

FIGURE 3-2: LVPECL Pull-Up/Pull-Down Termination.

Resistor values shown are typical for 3.3V operation. For 2.5V operation, the resistor to ground is  $62\Omega$  and the resistor to supply is  $250\Omega$ .

### 3.2 LVDS Application Diagrams

One of the most important considerations is terminating the Output and Complementary Outputs equally. An unused output should not be left unterminated because if one of the two outputs is left open, it will result in excessive jitter on both. PCB layout must take this and  $50\Omega$  impedance matching into account. Load matching and power supply noise are the main contributors to jitter related problems.

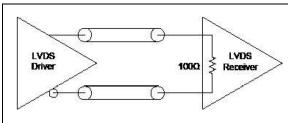

**FIGURE 3-3:** LVDS-to-LVDS Connection, Internal  $100\Omega$  Resistor.

Some LVDS structures have an internal  $100\Omega$  resistor on the input and do not need additional components. AC blocking capacitors can be used if the DC levels are incompatible.

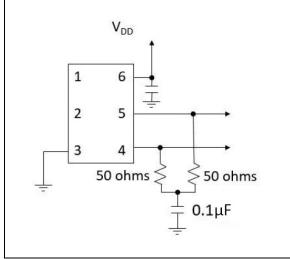

FIGURE 3-4: LVDS-to-LVDS Connection.

Some input structures may not have an internal  $100\Omega$  resistor on the input and will need an external  $100\Omega$  resistor located at the receiver for impedance matching. Figure 3-4 is optimized to reduce common mode noise. Additionally, the input may have an internal DC bias that may not be compatible with LVDS levels. AC blocking capacitors, such as  $0.1~\mu F$ , should be used in this case.

### 4.0 RELIABILITY

Microchip qualification will include aging at various extreme temperatures, shock and vibration, temperature cycling, and IR reflow simulation. The VC-830 family is capable of meeting the following qualification tests.

TABLE 4-1: ENVIRONMENTAL COMPLIANCE

| Parameter                        | Conditions                                  |  |  |  |  |  |

|----------------------------------|---------------------------------------------|--|--|--|--|--|

| Mechanical Shock                 | MIL-STD-883, Method 2002                    |  |  |  |  |  |

| Mechanical Vibration             | MIL-STD-883, Method 2007                    |  |  |  |  |  |

| Temperature Cycle                | MIL-STD-883, Method 1010                    |  |  |  |  |  |

| Solderability                    | MIL-STD-883, Method 2003                    |  |  |  |  |  |

| Gross and Fine Leak              | MIL-STD-883, Method 1014                    |  |  |  |  |  |

| Resistance to Solvents           | MIL-STD-883, Method 2015                    |  |  |  |  |  |

| Moisture Sensitivity Level       | MSL 1                                       |  |  |  |  |  |

| Contact Pads                     | Gold (0.3 μm min., 1.0 μm max.) over Nickel |  |  |  |  |  |

| θ <sub>JC</sub> (Bottom of Case) | 28°C/W                                      |  |  |  |  |  |

| Maximum Junction Temperature     | 150°C                                       |  |  |  |  |  |

| Weight                           | 23 mg                                       |  |  |  |  |  |

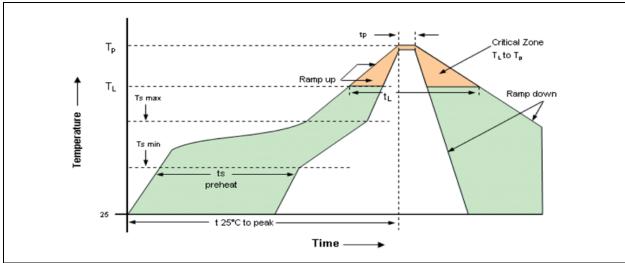

### 5.0 IR REFLOW

Devices are built using lead-free epoxy and can be subjected to standard lead-free IR reflow conditions shown in Table 5-1. Contact pads are gold over nickel and lower maximum temperatures can also be used, such as 220°C.

FIGURE 5-1: Reflow Solder Profile.

TABLE 5-1: REFLOW PROFILE

| Parameter                | Symbol             | Value               |

|--------------------------|--------------------|---------------------|

| Pre-Heat Time            | t <sub>S</sub>     | 200 seconds maximum |

| Ramp Up                  | R <sub>UP</sub>    | 3°C/sec. maximum    |

| Time above 217°C         | t <sub>L</sub>     | 150 seconds maximum |

| Time to Peak Temperature | T <sub>AMB-P</sub> | 480 seconds maximum |

| Time at 260°C            | t <sub>P</sub>     | 30 seconds maximum  |

| Time at 240°C            | t <sub>P2</sub>    | 60 seconds maximum  |

| Ramp Down                | R <sub>DN</sub>    | 6°C/sec. maximum    |

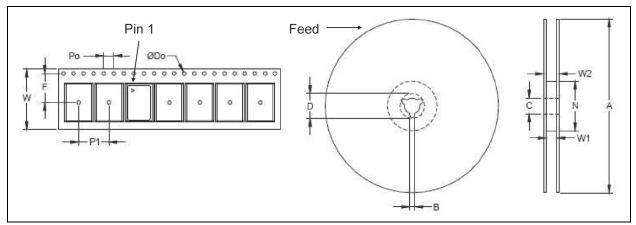

# 6.0 TAPE AND REEL

TABLE 6-1: TAPE AND REEL DIMENSIONS

| Tape Dimensions (mm) |     |     |     | Reel Dimensions (mm) |     |     |     |     |     |     |     |     |       |

|----------------------|-----|-----|-----|----------------------|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| Dimension            | W   | F   | Do  | Ро                   | P1  | Α   | В   | С   | D   | N   | W1  | W2  | # per |

| Tolerance            | Тур | Тур | Тур | Тур                  | Тур | Тур | Тур | Тур | Тур | Тур | Тур | Max | Reel  |

| VC-830               | 8   | 3.5 | 1.5 | 4                    | 4   | 178 | 2   | 13  | 21  | 60  | 10  | 14  | 3000  |

FIGURE 6-1: Tape and Reel Diagram.

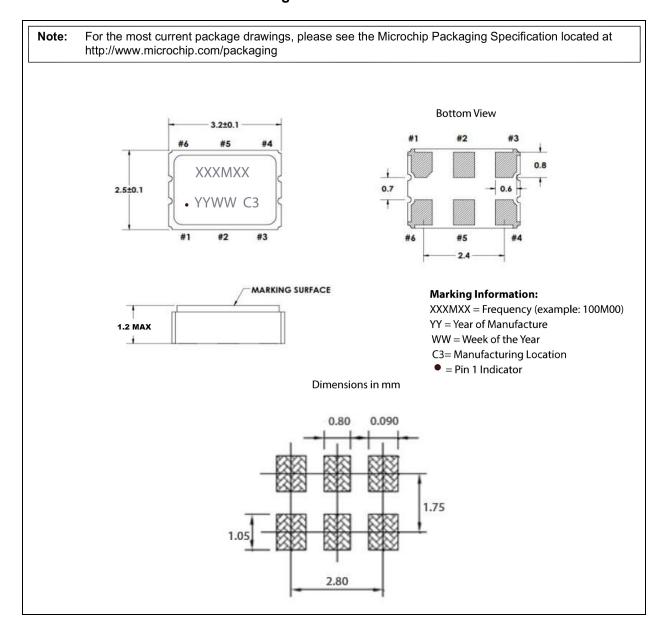

# 7.0 PACKAGING INFORMATION

# 6-Lead 3.2 mm × 2.5 mm VDFN Package Outline and Recommended Land Pattern

NOTES:

#### APPENDIX A: REVISION HISTORY

## Revision A (May 2021)

- Converted Vectron document VC-830 to Microchip data sheet template DS20006510A.

- Minor grammatical text changes throughout.

# **Revision B (August 2021)**

- Added a plus/minus (±) symbol to each value listed for Output Amplitude in the Electrical Characteristics, LVDS Option table.

- Updated maximum package height to 1.2 mm.

### Revision C (April 2024)

- Corrected the Storage Temperature range in the Absolute Maximum Ratings section.

- Added new HCSL ordering option details throughout document, including but not limited to the Electrical Characteristics, HCSL Option, table and Figure 1-4.

NOTES:

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

| <u>Device</u>            | - <u>X</u>                  | <u>X</u>                                         | <u>X</u>                   | - <u>X</u>      | <u>X</u>  | <u>X</u>                     | <u>X</u>                                 | -XXXXXXXXXX                                                                           | <u>XX</u>                           |

|--------------------------|-----------------------------|--------------------------------------------------|----------------------------|-----------------|-----------|------------------------------|------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------|

| Part No.                 | Power<br>Supply             | Output                                           | Temp.<br>Range             | Stability       | E/D Logic | E/D Pin                      | Custom<br>Options                        | Frequency                                                                             | Packaging                           |

| Device:                  | VC-830:                     | LVPECL, LVDS Crystal O<br>6-Lead 3.2 mm x 2.5 mm |                            |                 | 1         | <b>Examples:</b> a) VC-830-E | CF-GAAN-15                               | 6M250000TR:<br>/DC, LVPECL Ou                                                         | tput, –40°C to                      |

| Power Supply:            | E =<br>H =<br>J =           | 3.3VDC ±59<br>2.5VDC ±59<br>1.8VDC ±59           | 6                          |                 |           |                              | Output Enal<br>Standard Opt              | np Range, ±30<br>bled, Pin 1 E<br>ion, 156.25 MHz,                                    | nable/Disable                       |

| Output:                  | C =<br>D =<br>H =           | LVPECL<br>LVDS<br>HCSL                           |                            |                 |           | b) VC-830-F                  | VC-830, 2.5°<br>+70°C Temp<br>Output Ena | 25M000000TR:<br>VDC, LVDS Out<br>p Range, ±50  <br>bled, Pin 1 E<br>tion, 125 MHz, 30 | opm Stability<br>nable/Disable      |

| Temperature<br>Range:    | E = F = W =                 | -40°C to +8<br>-40°C to +1<br>-10°C to +7        | 05°C                       |                 |           |                              |                                          |                                                                                       |                                     |

| Stability:               | F = G = K = S =             | ±25 ppm<br>±30 ppm<br>±50 ppm<br>±100 ppm        |                            |                 |           |                              |                                          |                                                                                       |                                     |

| Enable/Disable<br>Logic: | A =                         | Output Enal                                      | oled with a Lo             | gic High or Ope | n         |                              |                                          |                                                                                       |                                     |

| Enable/Disable<br>Pin:   | A =<br>B =                  |                                                  | = No Connec<br>= No Connec |                 |           |                              |                                          |                                                                                       |                                     |

| Custom<br>Options:       | N =                         | Standard or                                      | otion                      |                 |           |                              |                                          |                                                                                       |                                     |

| Frequency:               | xxxMxxxxxx=Frequency in MHz |                                                  |                            |                 |           | C                            | atalog part nun                          | dentifier only appea<br>nber description. Th<br>g purposes and is                     | nis identifier is<br>not printed on |

| Packaging:               | TR =<br><blank></blank>     | 3,000/Reel<br>Cut Tape/ n                        | on-TR quantiti             | es              |           | 5                            |                                          | age. Check with yo<br>package availabilit                                             |                                     |

Note: Not all combinations of options are available. Other specifications may be available upon request.

NOTES:

#### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable" Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">https://www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPlC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, TimeCesium, TimeHub, TimePictra, TimeProvider, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, EyeOpen, GridTime, IdealBridge, IGaT, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, MarginLink, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mSiC, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, Power MOS IV, Power MOS 7, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, Turing, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2023, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

ISBN: 978-1-6683-4372-2

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support Web Address:

www.microchip.com

Atlanta Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983 Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

China - Shenzhen

Tel: 86-755-8864-2200 China - Suzhou

Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

**China - Xiamen** Tel: 86-592-2388138

China - Zhuhai Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

Japan - Osaka

Tel: 81-6-6152-7160 Japan - Tokyo

Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4485-5910

Fax: 45-4485-2829 Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79 **Germany - Garching**

Tel: 49-8931-9700 Germany - Haan

Tel: 49-2129-3766400 Germany - Heilbronn

Tel: 49-7131-72400 Germany - Karlsruhe

Tel: 49-721-625370 Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Rosenheim** Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

**Italy - Padova** Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820