# WF200 Data Sheet: Wi-Fi<sup>®</sup> Network Co-Processor

The Silicon Labs WF200 is an Ultra Low Power Wi-Fi<sup>®</sup> transceiver or network co-processor (NCP) targeted for applications where optimal RF performance, low-power consumption, and secure end-to-end solution, together with fast time to market, are key requirements.

The WF200 integrates the Balun, T/R switch, LNA and PA for best possible RF performance. Co-existence with other external 2.4GHz radios is supported.

WF200 has been optimized for resource and power constrained devices at the RF, protocol, and firmware levels. Power conscious devices can take advantage of these features in both active and sleep modes.

For security sensitive applications, WF200 provides secure boot and a secure & encrypted host interface. Robust security is made possible with a native integrated True Random Number Generator and OTP memory for confidential encryption key storage.

The WF200 fits well with Linux-based and RTOS-based host processors. WF200 supports both the 802.11 lower MAC and the 802.11 full MAC architectures. It communicates with the external host controller over the SPL or SDIO interface.

### **KEY POINTS**

- IEEE 802.11 b/g/n compliant

- TX power: +17 dBm (at pin)

- RX sensitivity: -96.7 dBm (at pin)

- · Integrated antenna diversity support

- · Ultra low power consumption

- · Secure and signed software

- Encrypted host interface communication

- · Linux and RTOS host support

- 4x4 QFN32 package

# **Table of Contents**

| 1. | Features List                                                                                                                                        | 4      |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 2. | Ordering Guide                                                                                                                                       | 5      |

| 3. | System Overview                                                                                                                                      | 6      |

|    | 3.1 Introduction                                                                                                                                     | 6      |

|    | 3.2 Wi-Fi Supported 2.4 GHz Bandwidth and Channels                                                                                                   | 6      |

| 4. | Electrical Specifications                                                                                                                            | 7      |

|    | 4.1 Absolute Maximum Ratings                                                                                                                         | 7      |

|    | 4.2 Operating Conditions                                                                                                                             | 8      |

|    | 4.3 Power Consumption                                                                                                                                | 9      |

|    | 4.4 RF Transmitter General Characteristics                                                                                                           |        |

|    | 4.5 RF Receiver General Characteristics                                                                                                              |        |

|    | 4.6 Reference Oscillator and Clock Characteristics                                                                                                   | 6<br>7 |

|    | 4.6.3 Low Power 32.768 kHz Clock Input Requirements                                                                                                  |        |

|    | 4.7.1 Supply Terminal Specifications                                                                                                                 | 8      |

|    | 4.8 Host Interface       .1         4.8.1 SPI Specification       .2         4.8.2 SDIO Specification       .2                                       | 0      |

| 5. | Typical Applications and Connections                                                                                                                 | 2      |

|    | 5.1 Typical Application Circuit for SDIO Host Interface                                                                                              | 2      |

|    | 5.2 Typical Application Circuit for SPI Host Interface                                                                                               | 3      |

|    | 5.3 Power States and Low-Power Modes                                                                                                                 | 4      |

|    | 5.4 RF Connections          5.4.1 Antenna Ports          5.4.2 Antenna Diversity          5.4.3 FEM Support                                          | 4<br>4 |

|    | 5.5 Clocks          5.5.1 XTAL_I and XTAL_O connections for Crystal          5.5.2 XTAL_I and XTAL_O connections for TCXO          5.5.3 LP_CLK Port | 6<br>6 |

|    | 5.6 Multi-Protocol Coexistence                                                                                                                       |        |

| 6. | Pin Descriptions                                                                                                                                     |        |

|    | Package Outline                                                                                                                                      |        |

|    |                                                                                                                                                      | _      |

| 8. Land Pattern                    |  |  |  |  |  |  |  | • |  | • | • | .31  |

|------------------------------------|--|--|--|--|--|--|--|---|--|---|---|------|

| 9. Top Marking                     |  |  |  |  |  |  |  |   |  |   |   | 32   |

| 10. Software Reference             |  |  |  |  |  |  |  |   |  |   |   | . 33 |

| 10.1 Host and Device Software      |  |  |  |  |  |  |  |   |  |   |   | .33  |

| 10.1.1 Split MAC                   |  |  |  |  |  |  |  |   |  |   |   | .33  |

| 10.1.2 Full MAC                    |  |  |  |  |  |  |  |   |  |   |   | .34  |

| 10.1.3 Software Documentation      |  |  |  |  |  |  |  |   |  |   |   | .34  |

| 10.2 Security                      |  |  |  |  |  |  |  |   |  |   |   | .34  |

| 10.2.1 Secure Device               |  |  |  |  |  |  |  |   |  |   |   | .34  |

| 10.2.2 Secure Boot                 |  |  |  |  |  |  |  |   |  |   |   | .35  |

| 10.2.3 Secure Link (WF200SD only)  |  |  |  |  |  |  |  |   |  |   |   | .35  |

| 10.3 Startup, Sleep and Shutdown . |  |  |  |  |  |  |  |   |  |   |   | .35  |

| 10.3.1 Power On, Reset, and Boot.  |  |  |  |  |  |  |  |   |  |   |   |      |

| 10.3.2 Sleep and Snooze Modes .    |  |  |  |  |  |  |  |   |  |   |   | .35  |

| 10.3.3 Shutdown Mode               |  |  |  |  |  |  |  |   |  |   |   | .36  |

| 11. Revision History               |  |  |  |  |  |  |  |   |  |   |   | 37   |

### 1. Features List

The key features of the WF200 Wi-Fi transceiver are listed below.

### **Applications**

- · Industrial, Home and Buidling automation

- · Home appliances

- · Security solutions

- · Retail and Commercial

- · Commercial transportation

- · Consumer medical

- · Sports and Fitness

### **Features**

- 802.11 b/g/n Wi-Fi NCP including the radio, baseband, MAC, security and host interface

- · Superior link budget with integrated LNA, PA and Balun

- · OTP included removing the need for an external EEPROM

- · Ultra low power optimized solution

- End-to-end security with hardware protected secure boot and encrypted host interface (optional)

- · 802.11 split and full MAC architecture support

- Complete Network Co-Processor (NCP) support for Linux and RTOS external hosts

### Standards/IEEE 802.11 and WFA

- b symbol rates: up to 11 Mbps

- g symbol rates: up to 54 Mbps

- n symbol rates: up to 72.2Mbps

- · d regulatory domains

- · e QoS as per definition in WMM specification

- · i as per definition in WPA2 specification

- · w protected management frames

- · WMM Power save

- · WPA/WPA2 Personal/WPA3 Personal

- · Supported with Linux UMAC:

- WPA2 Enterprise

- · WPS Wi-Fi Protected Setup

# **Key MAC and Baseband Features**

- 1x1 802.11n (20 MHz) with full 802.11 b/g compatibility, 72.2Mbps

- Greenfield Tx/Rx for 802.11n optimal performance

- Short Guard Interval (SGI) for 802.11n optimal throughput

- A-MPDU Rx and Tx for high MAC throughput

- · Block acknowledgement for several frames

- Rx Defragmentation

- · Roaming supported

- · Client, SoftAP modes supported

- Concurrent AP + STA supported on different channels

### **RF Features**

- Tx Power: +17 dBm

- Rx Sensitivity: -96.7 dBm

- 2 x 2.4GHz antenna pads for full antenna diversity support or FEM support

- 2.4GHz co-existence; 2-, 3- and 4-wire PTA support

- Integrated Balun, T/R switch, LNA and PA for 2.4GHz

### **Power Consumption**

- Rx (@DSSS-1Mbps): 41.6mA

- Tx (17 dBm @DSSS-1Mbps): 153mA

- Associated DTIM3 average current : 298 μA

- Associated Sleep Current : 22 μA

- Shutdown mode: 0.5 μA

### **Security and Encryption Features**

- · Secure boot with roll-back prevention

- Encrypted host interface, dedicated hardware acceleration block

- · Integrated True Random Number Generator

- · Secure key storage using protected OTP technology

- · AES/WEP hardware acceleration

### **Host Interfaces**

- SDIO (1-bit and 4-bit SD mode @ 26MHz)

- SPI (1-bit @ 52MHz)

### **Peripheral Interfaces**

- · External 32kHz crystal for low power

- GPIOs (including wake-up and Tx/Rx activity monitoring)

### **ROHS/REACH Compliant**

### **Electrical Characteristics**

- 1.62V 3.6V (VDD<sub>D</sub>, VDD<sub>IO</sub>, VDD<sub>RF</sub>)

- 3.0 3.6V (VDD<sub>PA</sub>)

### **Packaging**

- 4x4 QFN32

- Temperature range: -40°C to +105°C

# 2. Ordering Guide

Table 2.1. WF200 Ordering Information (R Indicates Full Reel)

| Part Number | Description                                           |

|-------------|-------------------------------------------------------|

| WF200D(R)   | WF200 802.11bgn NCP, 4x4 QFN32                        |

| WF200SD(R)  | WF200 802.11bgn NCP, Secure link interface, 4x4 QFN32 |

# 3. System Overview

### 3.1 Introduction

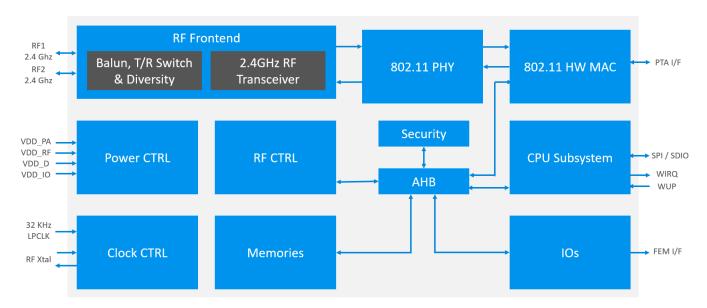

WF200 is a Wi-Fi network co-processor optimized for RF performance, low energy, and low cost, with two antenna ports, Crystal Oscillator, One Time Programmable Memory, and several GPIOs for interfacing with multi-protocol and RF Front End Module controls.

Figure 3.1. WF200 Block Diagram

### 3.2 Wi-Fi Supported 2.4 GHz Bandwidth and Channels

Supported operating frequencies and bandwidth

Table 3.1. Supported Wi-Fi Modulations, BW, and Channels

| Parameter                | Symbol | Test Condition               | Min  | Тур | Max  | Unit |

|--------------------------|--------|------------------------------|------|-----|------|------|

| Channel Center Frequency | CHAN   | Subject to Regulatory Agency | 2412 |     | 2484 | MHz  |

| Channel Bandwidth        | BW     |                              | _    | 20  | _    | MHz  |

# 4. Electrical Specifications

All electrical parameters in all tables are specified under the following conditions, unless stated otherwise:

- Typical values are based on  $T_A$  = 25 °C;  $V_{VDD\ IO}$ ,  $V_{VDD\ D}$ ,  $V_{VDD\_RF}$  = 1.8 V;  $V_{VDD\_PA}$ = 3.3V

- · Radio performance numbers are measured in conducted mode, based on Silicon Labs reference designs

- WF200 features and benefits depend on system configuration and may require specific driver, firmware or service activation. Learn more at https://www.silabs.com/products/wireless/wi-fi

Refer to Section 4.2 Operating Conditions for more details about operational supply and temperature limits.

### 4.1 Absolute Maximum Ratings

Stresses above those listed below may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at <a href="http://www.silabs.com/support/quality/pages/default.aspx">http://www.silabs.com/support/quality/pages/default.aspx</a>.

**Table 4.1. Absolute Maximum Ratings**

| Parameter                                                              | Symbol                | Test Condition                                                                                        | Min  | Тур | Max                       | Unit |

|------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------|------|-----|---------------------------|------|

| Storage temperature                                                    | T <sub>STG</sub>      |                                                                                                       | -40  | _   | 150                       | °C   |

| Junction temperature                                                   | TJ <sub>MAX</sub>     |                                                                                                       | -40  | _   | 125                       | °C   |

| RF power level at RF1 and RF2 ports                                    | P <sub>RFMAX</sub>    | Max power that can be applied to input of recommended matching network connected to RF1 and RF2 pins. | _    | _   | 10                        | dBm  |

| Supply voltage to VDD_PA, VDD_RF, VDD_IO, VDD_D                        | VDD <sub>MAX</sub>    |                                                                                                       | -0.3 | _   | 3.6                       | V    |

| Voltage on XTAL_I and XTAL_O pins                                      | VXO <sub>MAX</sub>    |                                                                                                       | -0.3 | _   | 1.25                      | V    |

| Voltage on all other pins<br>(GPIO, Host interface, FEM,<br>PTA, etc.) | VG <sub>MAX</sub>     |                                                                                                       | -0.3 | _   | VDD <sub>IO</sub> + 0.3 V | V    |

| Current into any GPIO pin                                              | IO <sub>MAX</sub>     |                                                                                                       | _    | _   | 20                        | mA   |

| Sum of current into all GPIO pins                                      | IO <sub>ALL_MAX</sub> |                                                                                                       | _    | _   | 150                       | mA   |

| Range of load impedance at RF1 and RF2 pins during TX                  | LOAD <sub>TX</sub>    |                                                                                                       | _    | _   | 10:1                      | VSWR |

# 4.2 Operating Conditions

**Table 4.2. Recommended Operating Conditions**

| Parameter                                     | Symbol              | Test Condition | Min  | Тур | Max | Unit |

|-----------------------------------------------|---------------------|----------------|------|-----|-----|------|

| Ambient operating temperature                 | T <sub>A</sub>      |                | -40  | _   | 105 | °C   |

| Junction operating temperature                | TJ                  |                | -40  | _   | 125 | °C   |

| DC supply voltage to VDD_PA <sup>1</sup>      | V <sub>VDD_PA</sub> |                | 3.0  | 3.3 | 3.6 | V    |

| Nominal supply voltage to VDD_RF <sup>1</sup> | V <sub>VDD_RF</sub> |                | 1.62 | 1.8 | 3.6 | V    |

| Nominal supply voltage to VDD_D               | V <sub>VDD_D</sub>  |                | 1.62 | 1.8 | 3.6 | V    |

| Nominal supply voltage to VDD_IO              | V <sub>VDD_IO</sub> |                | 1.62 | 1.8 | 3.6 | V    |

# Note:

<sup>1.</sup> VDD\_PA must always be greater than or equal to VDD\_RF.

# 4.3 Power Consumption

Unless otherwise indicated,  $V_{VDD\_PA}$  = 3.3 V,  $V_{VDD\_D}$  =  $V_{VDD\_RF}$  =  $V_{VDD\_IO}$  = 1.8 V.

**Table 4.3. Power Consumption**

| Parameter       | Symbol          | Test Condition                                                       | Min | Тур  | Max | Unit |

|-----------------|-----------------|----------------------------------------------------------------------|-----|------|-----|------|

| TX mode current | I <sub>TX</sub> | 802.11.b: 1 Mbps, from VDD_PA at 3.3 V                               | _   | 108  | _   | mA   |

|                 |                 | 802.11.b: 11 Mbps, from VDD_PA at 3.3 V                              | _   | 104  | _   | mA   |

|                 |                 | 802.11.g: 6 Mbps, from VDD_PA at 3.3 V                               | _   | 101  | _   | mA   |

|                 |                 | 802.11.g: 54 Mbps, from VDD_PA at 3.3 V                              | _   | 95   | _   | mA   |

|                 |                 | 802.11.n: MCS = 0, from VDD_PA at 3.3 V                              | _   | 100  | _   | mA   |

|                 |                 | 802.11.n: MCS = 7, from VDD_PA at 3.3 V                              | _   | 94   | _   | mA   |

|                 |                 | 802.11.b: 1 Mbps, from 1.8 V supplies (VDD_RF, VDD_D, VDD_IO)        | _   | 44.6 | _   | mA   |

|                 |                 | 802.11.b: 11 Mbps, from 1.8 V supplies (VDD_RF, VDD_D, VDD_IO)       | _   | 44.7 | _   | mA   |

|                 |                 | 802.11.g: 6 Mbps, from 1.8 V supplies (VDD_RF, VDD_D, VDD_IO)        | _   | 46.2 | _   | mA   |

|                 |                 | 802.11.g: 54 Mbps, from 1.8 V supplies (VDD_RF, VDD_D, VDD_IO)       | _   | 46.8 | _   | mA   |

|                 |                 | 802.11.n: MCS = 0, from 1.8 V supplies (VDD_RF, VDD_D, VDD_IO)       | _   | 46.1 | _   | mA   |

|                 |                 | 802.11.n: MCS = 7, from 1.8 V supplies (VDD_RF, VDD_D, VDD_IO)       | _   | 46.8 | _   | mA   |

| RX mode current | I <sub>RX</sub> | 802.11.b: 1 Mbps, from 1.8 V supplies (VDD_RF, VDD_D, VDD_IO)        | _   | 41.6 | _   | mA   |

|                 |                 | 802.11.b: 11 Mbps, from 1.8 V supplies (VDD_RF, VDD_D, VDD_IO)       | _   | 42.3 | _   | mA   |

|                 |                 | 802.11.g: 6 Mbps, from 1.8 V supplies (VDD_RF, VDD_D, VDD_IO)        | _   | 44.7 | _   | mA   |

|                 |                 | 802.11.g: 54 Mbps, from 1.8 V supplies (VDD_RF, VDD_D, VDD_IO)       | _   | 47.1 | _   | mA   |

|                 |                 | 802.11.n: MCS = 0, from 1.8 V supplies (VDD_RF, VDD_D, VDD_IO)       | _   | 44.5 | _   | mA   |

|                 |                 | 802.11.n: MCS = 7, from 1.8 V<br>supplies (VDD_RF, VDD_D,<br>VDD_IO) | _   | 47.6 | _   | mA   |

| Parameter                     | Symbol                 | Test Condition                          | Min | Тур  | Max | Unit |

|-------------------------------|------------------------|-----------------------------------------|-----|------|-----|------|

| Sleep current on power sup-   | I <sub>SLEEP</sub>     | VDD_PA pin, V <sub>VDD_PA</sub> = 3.3 V | _   | 66   | _   | nA   |

| ply pins <sup>1</sup>         |                        | VDD_RF pin, V <sub>VDD_RF</sub> = 1.8 V | _   | 87   | _   | nA   |

|                               |                        | VDD_D pin, V <sub>VDD_D</sub> = 1.8 V   | _   | 18.6 | _   | μA   |

|                               |                        | VDD_IO pin, V <sub>VDD_IO</sub> = 3.3 V | _   | 3.5  | _   | μA   |

| Snooze current on power       | I <sub>SNOOZE</sub>    | VDD_PA pin, V <sub>VDD_PA</sub> = 3.3 V | _   | 66   | _   | nA   |

| supply pins <sup>2</sup>      |                        | VDD_RF pin, V <sub>VDD_RF</sub> = 1.8 V | _   | 536  | _   | μA   |

|                               |                        | VDD_D pin, V <sub>VDD_D</sub> = 1.8 V   | _   | 610  | _   | μA   |

|                               |                        | VDD_IO pin, V <sub>VDD_IO</sub> = 3.3 V | _   | 51   | _   | μA   |

| Shutdown current on power     | I <sub>SHUTDOWN</sub>  | VDD_PA pin, V <sub>VDD_PA</sub> = 3.3 V | _   | 67   | _   | nA   |

| supply pins <sup>3</sup>      |                        | VDD_RF pin, V <sub>VDD_RF</sub> = 1.8 V | _   | 67.4 | _   | nA   |

|                               |                        | VDD_D pin, V <sub>VDD_D</sub> = 1.8 V   | _   | 16.4 | _   | nA   |

|                               |                        | VDD_IO pin, V <sub>VDD_IO</sub> = 3.3 V | _   | 49   | _   | nA   |

| Average current for DTIM=1    | I <sub>LP_DTIM1</sub>  | VDD_PA pin, V <sub>VDD_PA</sub> = 3.3 V | _   | 154  | _   | nA   |

| Interval Profile <sup>4</sup> |                        | VDD_RF pin, V <sub>VDD_RF</sub> = 1.8 V | _   | 437  | _   | μA   |

|                               |                        | VDD_D pin, V <sub>VDD_D</sub> = 1.8 V   | _   | 454  | _   | μA   |

|                               |                        | VDD_IO pin, V <sub>VDD_IO</sub> = 3.3 V | _   | 3.7  | _   | μA   |

| Average current for DTIM=3    | I <sub>LP_DTIM3</sub>  | VDD_PA pin, V <sub>VDD_PA</sub> = 3.3 V | _   | 128  | _   | nA   |

| Interval Profile <sup>4</sup> |                        | VDD_RF pin, V <sub>VDD_RF</sub> = 1.8 V | _   | 128  | _   | μA   |

|                               |                        | VDD_D pin, V <sub>VDD_D</sub> = 1.8 V   | _   | 166  | _   | μA   |

|                               |                        | VDD_IO pin, V <sub>VDD_IO</sub> = 3.3 V | _   | 3.6  | _   | μA   |

| Average current for DTIM=10   | I <sub>LP_DTIM10</sub> | VDD_PA pin, V <sub>VDD_PA</sub> = 3.3 V | _   | 118  | _   | nA   |

| Interval Profile <sup>4</sup> |                        | VDD_RF pin, V <sub>VDD_RF</sub> = 1.8 V | _   | 38   | _   | μA   |

|                               |                        | VDD_D pin, V <sub>VDD_D</sub> = 1.8 V   | _   | 65   | _   | μA   |

|                               |                        | VDD_IO pin, V <sub>VDD_IO</sub> = 3.3 V | _   | 3.7  | _   | μA   |

### Note:

- 1. All memory is retained in sleep mode. WUP on timer and/or interrupt.

- 2. All memory is retained and Xtal oscillator is kept on if no 32 kHz clock is provided.

- 3. Requires complete start-up sequence to resume operation.

- 4. All DTIM currents assume a 1 ms beacon time duration with a beacon interval of 102.4ms from the AP.

### 4.4 RF Transmitter General Characteristics

Unless otherwise indicated, typical conditions are: Operating Ambient Temp = 25 °C,  $V_{VDD\_IO} = V_{VDD\_D} = V_{VDD\_RF} = 1.8 \text{ V}$ ;  $V_{VDD\_PA} = 3.3 \text{ V}$ , center frequency = 2,442 MHz, and measured in 50  $\Omega$  test equipment attached at antenna port.

Measurements for this specification are made using the RF\_1 port. See Section 5.4.1 Antenna Ports.

# 4.4.1 RF Transmitter Characteristics

**Table 4.4. RF Transmitter Characteristics**

| Parameter                                    | Symbol                     | Test Condition                                      | Min | Тур  | Max | Unit |

|----------------------------------------------|----------------------------|-----------------------------------------------------|-----|------|-----|------|

| Maximum RMS Output Pow-                      | POUT <sub>MAX_RMS_</sub>   | 802.11b: 1 Mbps                                     | _   | 17.0 | _   | dBm  |

| er at pin <sup>1 2</sup>                     | HPPA_PIN                   | 802.11b: 11 Mbps                                    | _   | 16.0 | _   | dBm  |

|                                              |                            | 802.11g: 6 Mbps                                     | _   | 15.6 | _   | dBm  |

|                                              |                            | 802.11g: 54 Mbps                                    | _   | 12.1 | _   | dBm  |

|                                              |                            | 802.11n: MCS=0                                      | _   | 15.3 | _   | dBm  |

|                                              |                            | 802.11n: MCS=7                                      | _   | 10.7 | _   | dBm  |

| Maximum RMS Output Pow-                      | POUT <sub>MAX_RMS_</sub>   | 802.11b: 1 Mbps                                     | _   | 16.7 | _   | dBm  |

| er at Antenna (High Power PA) <sup>2</sup>   | HPPA                       | 802.11b: 11 Mbps                                    | _   | 15.6 | _   | dBm  |

| ,                                            |                            | 802.11g: 6 Mbps                                     | _   | 15.2 | _   | dBm  |

|                                              |                            | 802.11g: 54 Mbps                                    | _   | 11.7 | _   | dBm  |

|                                              |                            | 802.11n: MCS=0                                      | _   | 14.9 | _   | dBm  |

|                                              |                            | 802.11n: MCS=7                                      | _   | 10.3 | _   | dBm  |

| Second Harmonic Level for                    | H2 <sub>MAX</sub>          | 802.11b: 1 Mbps                                     | _   | -48  | _   | dBm  |

| POUT_MAX_PA Setting                          |                            | 802.11b: 11 Mbps                                    | _   | -52  | _   | dBm  |

|                                              |                            | 802.11g: 6 Mbps                                     | _   | -48  | _   | dBm  |

|                                              |                            | 802.11g: 54 Mbps                                    | _   | -50  | _   | dBm  |

|                                              |                            | 802.11n: MCS=0                                      | _   | -49  | _   | dBm  |

|                                              |                            | 802.11n: MCS=7                                      | _   | -51  |     | dBm  |

| Carrier Suppression per                      | C <sub>SUP</sub>           | 802.11b: 1 Mbps                                     | _   | -50  | _   | dBr  |

| 802.11-2012 for POUT_MAX PA setting          |                            | 802.11b: 11 Mbps                                    | _   | -45  | _   | dBr  |

|                                              |                            | 802.11g: 6 Mbps                                     | _   | -32  | _   | dBr  |

|                                              |                            | 802.11g: 54 Mbps                                    | _   | -42  | _   | dBr  |

|                                              |                            | 802.11n: MCS=0                                      | _   | -33  | _   | dBr  |

|                                              |                            | 802.11n: MCS=7                                      | _   | -38  | _   | dBr  |

| POUT variation from VDD_PA=3.0 V to 3.6 V    | POUT <sub>MAX_VAR_</sub> v | VDD_PA = 3.0 V to 3.6 V, Measured on single channel | _   | 1.1  | _   | dB   |

| POUT variation across tempeature             | POUT <sub>MAX_VAR_</sub>   | 25C to 85C                                          | _   | 1.7  | _   | dB   |

| POUT backoff variation from                  | VSWR                       | up to 2:1 VSWR                                      | _   | _    | 3.0 | dB   |

| 50 $\Omega$ load specified VSWR <sup>3</sup> |                            | up to 3:1 VSWR                                      | _   | _    | 5.0 | dB   |

| Parameter | Symbol | Test Condition | Min | Тур | Max | Unit |

|-----------|--------|----------------|-----|-----|-----|------|

|           |        |                |     |     |     |      |

### Note:

- 1. This is the maximum output level at the RF pin with optimum load impedance of 18.6-j9.6  $\Omega$ .

- 2. Rated power levels may not apply to the edge channels, which may need additional backoff for FCC compliance.

- 3. The maximum backoff levels are for MCS7 and channels 2 to 10. Backoff for channels 1 and 11 to ensure band-edge compliance are detailed in UG382: WF200 Hardware Design User's Guide.

### 4.5 RF Receiver General Characteristics

Unless otherwise indicated, typical conditions are: Operating Ambient Temp = 25 °C,  $V_{VDD\_IO} = V_{VDD\_D} = V_{VDD\_RF} = 1.8 \text{ V}$ ;  $V_{VDD\_PA} = 3.3 \text{ V}$ , center frequency = 2,442 MHz, and measured in 50  $\Omega$  test equipment attached at antenna port.

Measurements for this specification are made using the RF\_1 port. See Section 5.4.1 Antenna Ports.

# 4.5.1 RF Receiver Characteristics

**Table 4.5. RF Receiver Characteristics**

| Parameter                                                                                                    | Symbol             | Test Condition               | Min | Тур   | Max | Unit |

|--------------------------------------------------------------------------------------------------------------|--------------------|------------------------------|-----|-------|-----|------|

| RX Sensitivity for 8% FER                                                                                    | SENS <sub>B</sub>  | 802.11b: 1 Mbps, at antenna  | _   | -96.3 | _   | dBm  |

| (1024 Octet)                                                                                                 |                    | 802.11b: 1 Mbps, at pin      | _   | -96.7 | _   | dBm  |

|                                                                                                              |                    | 802.11b: 11 Mbps, at antenna | _   | -88.3 | _   | dBm  |

|                                                                                                              |                    | 802.11b: 11 Mbps, at pin     | _   | -88.7 | _   | dBm  |

| RX Sensitivity for 10% PER                                                                                   | SENS <sub>G</sub>  | 802.11g: 6 Mbps, at antenna  | _   | -91.6 | _   | dBm  |

| (1024 Octet)                                                                                                 |                    | 802.11g: 6 Mbps, at pin      | _   | -92   | _   | dBm  |

|                                                                                                              |                    | 802.11g: 54 Mbps, at antenna | _   | -74.8 | _   | dBm  |

|                                                                                                              |                    | 802.11g: 54 Mbps, at pin     | _   | -75.2 | _   | dBm  |

| RX Sensitivity for 10% PER                                                                                   | SENSEN             | 802.11n: MCS=0, at antenna   | _   | -91.1 | _   | dBm  |

| (4096 Octet)                                                                                                 |                    | 802.11n: MCS=0, at pin       | _   | -91.5 | _   | dBm  |

|                                                                                                              |                    | 802.11n: MCS=7, at antenna   | _   | -71.8 | _   | dBm  |

|                                                                                                              |                    | 802.11n: MCS=7, at pin       | _   | -72.2 | _   | dBm  |

| Adjacent Channel ( ± 30                                                                                      | ACS <sub>WB</sub>  | 802.11b: 1 Mbps              | _   | 54.4  | _   | dBc  |

| MHz) Selectivity with desired signal at 6 dB above reference sensitivity for 8% FER (1024 Octet)             |                    | 802.11b: 11 Mbps             | _   | 40.4  | _   | dBc  |

| Adjacent Channel ( ± 25                                                                                      | ACS <sub>WG</sub>  | 802.11g: 6 Mbps              | _   | 45.4  | _   | dBc  |

| MHz) Selectivity with desired<br>signal at 3 dB above refer-<br>ence sensitivity for 10% PER<br>(1024 Octet) |                    | 802.11g: 54 Mbps             | _   | 32.9  | _   | dBc  |

| Adjacent Channel ( ± 25                                                                                      | ACS <sub>WN</sub>  | 802.11n: MCS=0               | _   | 45.9  | _   | dBc  |

| MHz) Selectivity with desired<br>signal at 3 dB above refer-<br>ence sensitivity for 10% FER<br>(4096 Octet) |                    | 802.11n: MCS=7               | _   | 30.5  | _   | dBc  |

| 2nd Adjacent Channel Sele-                                                                                   | A2CS <sub>WB</sub> | 802.11b: 1 Mbps              | _   | 59.7  | _   | dBc  |

| citivity ( ± 50 MHz) with desired at 6 dB above reference sensitivity 8% FER (1024 Octet)                    |                    | 802.11b: 11 Mbps             | _   | 52.1  | _   | dBc  |

| 2nd Adjacent Channel Sele-                                                                                   | A2CS <sub>WG</sub> | 802.11g: 6 Mbps              | _   | 55.1  | _   | dBc  |

| citivity ( ± 50 MHz) with desired at 3 dB above reference sensitivity 10% PER (1024 Octet)                   |                    | 802.11g: 54 Mbps             | _   | 38.2  | _   | dBc  |

| 2nd Adjacent Channel Sele-                                                                                   | A2CS <sub>WN</sub> | 802.11n: MCS=0               | _   | 54.8  | _   | dBc  |

| citivity ( ± 50 MHz) with desired at 3 dB above reference sensitivity 10% PER (4096Octet)                    |                    | 802.11n: MCS=7               | _   | 35.7  | _   | dBc  |

| Parameter                                            | Symbol              | Test Condition                                 | Min | Тур   | Max | Unit |

|------------------------------------------------------|---------------------|------------------------------------------------|-----|-------|-----|------|

| RX Max Strong Signal for                             | RX <sub>SAT_B</sub> | 802.11b: 1 Mbps                                | _   | -4.0  | _   | dBm  |

| 8% FER (1024 Octet)                                  |                     | 802.11b: 11 Mbps                               | _   | -10.0 | _   | dBm  |

| RX Max Strong Signal for                             | RX <sub>SAT_G</sub> | 802.11g: 6 Mbps                                | _   | -9.0  | _   | dBm  |

| 10% PER (1024 Octet)                                 |                     | 802.11g: 54 Mbps                               | _   | -9.0  | _   | dBm  |

| RX Max Strong Signal for                             | RX <sub>SAT_N</sub> | 802.11n: MCS=0                                 | _   | -9.0  | _   | dBm  |

| 10% PER (4096 Octet)                                 |                     | 802.11n: MCS=7                                 | _   | -9.0  | _   | dBm  |

| U/D wtih desired at 6 dB above reference sensitivity | OOBBB               | 802.11b: 1 Mbps : GSM Blocker at 893.8 MHz     | _   | 76.0  | _   | dB   |

| for 8% FER (1024 Octet)                              |                     | 802.11b: 1 Mbps : GSM Blocker at 960 MHz       | _   | 75.0  | _   | dB   |

|                                                      |                     | 802.11b: 1 Mbps : GSM Blocker<br>at 1879.8 MHz | _   | 64.0  | _   | dB   |

|                                                      |                     | 802.11b: 1 Mbps : GSM Blocker<br>at 1989.8 MHz | _   | 63.0  | _   | dB   |

|                                                      |                     | 802.11b: 1 Mbps : LTE Blocker at 893.8 MHz     | _   | 76.0  | _   | dB   |

|                                                      |                     | 802.11b: 1 Mbps : LTE Blocker at 960 MHz       | _   | 75.0  | _   | dB   |

|                                                      |                     | 802.11b: 1 Mbps : LTE Blocker at 1879.8 MHz    | _   | 65.0  | _   | dB   |

|                                                      |                     | 802.11b: 1 Mbps : LTE Blocker at 2506 MHz      | _   | 56.0  | _   | dB   |

| U/D with desired at 3 dB above reference sensitivity | OOBB <sub>G</sub>   | 802.11g: 6 Mbps : GSM Blocker at 893.8 MHz     | _   | 81.0  | _   | dB   |

| for 10% PER (1024 Octet)                             |                     | 802.11g: 6 Mbps : GSM Blocker at 960 MHz       | _   | 80.0  | _   | dB   |

|                                                      |                     | 802.11g: 6 Mbps : GSM Blocker<br>at 1879.8 MHz | _   | 69.0  | _   | dB   |

|                                                      |                     | 802.11g: 6 Mbps : GSM Blocker<br>at 1989.8 MHz | _   | 67.0  | _   | dB   |

|                                                      |                     | 802.11g: 6 Mbps : LTE Blocker at 893.8 MHz     | _   | 75.0  | _   | dB   |

|                                                      |                     | 802.11g: 6 Mbps : LTE Blocker at 960 MHz       | _   | 74.0  | _   | dB   |

|                                                      |                     | 802.11g: 6 Mbps : LTE Blocker at 1879.8 MHz    | _   | 62.0  | _   | dB   |

|                                                      |                     | 802.11g: 6 Mbps : LTE Blocker at 2506 MHz      | _   | 57.0  | _   | dB   |

| Parameter                                                                     | Symbol               | Test Condition                               | Min          | Тур  | Max | Unit |

|-------------------------------------------------------------------------------|----------------------|----------------------------------------------|--------------|------|-----|------|

| U/D with desired at 3 dB above reference sensitivity for 10% PER (4096 Octet) | OOBB <sub>N</sub>    | 802.11n: MCS=7 : GSM Blocker<br>at 893.8 MHz | _            | 55.0 | _   | dB   |

|                                                                               |                      | 802.11n: MCS=7 : GSM Blocker at 960 MHz      | <del>_</del> | 54.0 | _   | dB   |

|                                                                               |                      | 802.11n: MCS=7: GSM Blocker at 1879.8 MHz    | <del>_</del> | 45.0 | _   | dB   |

|                                                                               |                      | 802.11n: MCS=7: GSM Blocker at 1989.8 MHz    | _            | 44.0 | _   | dB   |

|                                                                               |                      | 802.11n: MCS=7: LTE Blocker at 893.8 MHz     | _            | 54.0 | _   | dB   |

|                                                                               |                      | 802.11n: MCS=7 : LTE Blocker at 960 MHz      | _            | 53.0 | _   | dB   |

|                                                                               |                      | 802.11n: MCS=7 : LTE Blocker at 1879.8 MHz   | _            | 42.0 | _   | dB   |

|                                                                               |                      | 802.11n: MCS=7 : LTE Blocker at 2506 MHz     | _            | 38.0 | _   | dB   |

| RX Channel power Indicator                                                    | RCPI <sub>STEP</sub> | 802.11b: 1 Mbps                              | _            | 0.5  | _   | dBm  |

| Step Size                                                                     |                      | 802.11g: 6 Mbps                              | _            | 0.5  | _   | dBm  |

|                                                                               |                      | 802.11n: MCS=7                               | _            | 0.5  | _   | dBm  |

### 4.6 Reference Oscillator and Clock Characteristics

There are two options for the 38.4 MHz Reference Oscillator. Use an external oscillator like a TCXO, or use a crystal with the internal oscillator. The operating temperature range of the application will be limited by the selected component's operating temperature specification. To achieve lowest power operation during power save modes, a 32.768 KHz clock is also required.

### 4.6.1 Crystal Requirements for using Internal Oscillator

The choice of the crystal affects several parameters including control settings, RF performance, frequency accuracy, and average current consumption in applications that incorporate periodic wake and sleep states. The frequency accuracy of the crystal is the main contributor to Wi-Fi frequency accuracy which must be within +/-25ppm tolerance for 802.11 b, g, and n, in 20MHz channel operation over all of the operating conditions. Refer to UG382: WF200 Hardware Design User's Guide for more details.

Table 4.6. Crystal Requirements for Using Internal Oscillator

| Parameter                                          | Symbol               | Test Condition                   | Min   | Тур  | Max | Unit   |

|----------------------------------------------------|----------------------|----------------------------------|-------|------|-----|--------|

| Nominal Frequency of HF<br>Crystal Oscillator      | XTAL <sub>FNOM</sub> |                                  | _     | 38.4 | _   | MHz    |

| Frequency tolerance of crystal over all conditions | XTAL <sub>FTOL</sub> |                                  | -25   | _    | 25  | ppm    |

| Crystal Load Cap                                   | HFX <sub>CL</sub>    |                                  | 8     | 10   | 12  | pF     |

| Equivalent Series Resistance                       | HFX <sub>ESR</sub>   |                                  | _     | 20   | 40  | Ω      |

| Motional Capacitance                               | HFX <sub>CM</sub>    |                                  | 2     | _    | 4   | fF     |

| Motional Inductance                                | HFX <sub>LM</sub>    |                                  | 4     | _    | 8   | mH     |

| Shunt Capacitance                                  | HFX <sub>CS</sub>    |                                  | _     | 0.8  | 2   | pF     |

| Pulling Sensitivity                                | HFX <sub>PULL</sub>  |                                  | 8     | 12   | 20  | ppm/pF |

| Crystal withstanding drive strength                | HFX <sub>DL</sub>    |                                  | _     | _    | 200 | uW     |

| Quality Factor                                     | HFX <sub>Q</sub>     |                                  | 35000 | _    | _   |        |

| Spurious Mode Series Resistance                    | HFX <sub>SPUR</sub>  | ± 0.7 MHz away from<br>XTAL_FNOM | 1100  | _    | _   | Ω      |

| Insulation Resistance 100 V                        | HFX <sub>IR</sub>    |                                  | 500   | _    | _   | МΩ     |

### 4.6.2 External Oscillator Required Characteristics

An external oscillator, like a TCXO, must provide a stable and high quality signal in order for this IC to meet its performance specifications. This section lists some of the requirements. If the host powers down the TCXO when going into a low power state, the host must also turn on the TCXO in advance of any transceiver activity.

Table 4.7. Reference Oscillator Requirements

| Parameter                                       | Symbol                | Test Condition | Min | Тур  | Max  | Unit   |

|-------------------------------------------------|-----------------------|----------------|-----|------|------|--------|

| Nominal frequency of HF crystal oscillator      | TCXO <sub>FNOM</sub>  |                | _   | 38.4 | _    | MHz    |

| Frequency tolerance of TCXO over all conditions | TCXO <sub>FTOL</sub>  |                | -20 | _    | 20   | ppm    |

| Load Resistance of TCXO                         | TCXO <sub>RL</sub>    |                | 7   | 10   | 15   | KOhm   |

| Load capacitance of TCXO                        | TCXO <sub>CL</sub>    |                | 6   | 10   | 15   | pF     |

| Output level of TCXO                            | TCXO <sub>LEVEL</sub> |                | 0.7 | 0.9  | 1.2  | V p-p  |

| Symmetry of TCXO                                | TCXO <sub>SYMT</sub>  |                | 45  | 50   | 55   | %      |

| Startup time of TCXO                            | TCXO <sub>START</sub> |                | _   | _    | 2    | ms     |

| SSB Phase Noise of TCXO                         | SSB1                  | 10Hz offset    | _   | _    | -100 | dBc/Hz |

| SSB Phase Noise of TCXO                         | SSB2                  | 100Hz offset   | _   | _    | -110 | dBc/Hz |

| SSB Phase Noise of TCXO                         | SSB3                  | 1KHz offset    | _   | _    | -130 | dBc/Hz |

| SSB Phase Noise of TCXO                         | SSB4                  | 10KHz offset   |     | _    | -145 | dBc/Hz |

| SSB Phase Noise of TCXO                         | SSB5                  | 100KHz offset  | _   | _    | -150 | dBc/Hz |

| SSB Phase Noise of TCXO                         | SSB6                  | 1 MHz offset   | _   | _    | -150 | dBc/Hz |

### 4.6.3 Low Power 32.768 kHz Clock Input Requirements

Table 4.8. Low Power 32.768 kHz Clock Input Requirements

| Parameter                                                      | Symbol                | Test Condition | Min             | Тур    | Max    | Unit  |

|----------------------------------------------------------------|-----------------------|----------------|-----------------|--------|--------|-------|

| Nominal Frequency of LP_CLK                                    | FNOM <sub>LPCLK</sub> |                | _               | 32.768 | _      | KHz   |

| Frequency Tolerance of LP_CLK over all conditions <sup>1</sup> | FTOL <sub>LPCLK</sub> |                | -1000           | _      | 1000   | ppm   |

| Load of LP_CLK pin                                             | R <sub>LPCLK</sub>    |                | _               | 30     | _      | KOhm  |

| Input Level at LP_CLK                                          | SIGL <sub>LPCLK</sub> |                | 0.7 *<br>VDD_IO | _      | VDD_IO | V p-p |

| Symmetry of LP_CLK                                             | DUTY <sub>LPCLK</sub> |                | _               | 50     | _      | %     |

### Note:

<sup>1.</sup> To optimize power consumption in DTIM modes, it is recommended that the frequency drift of LP\_CLK within 1 second be lower than +- 100ppm.

### 4.7 Interface Terminal Characteristics

Unless otherwise indicated, typical conditions are: Operating Ambient Temp = 25 °C,  $V_{VDD\_IO} = V_{VDD\_D} = V_{VDD\_RF} = 1.8 \text{ V}$ ;  $V_{VDD\_PA} = 3.3 \text{ V}$ , center frequency = 2,442 MHz, and measured by 50  $\Omega$  test equipment attached at antenna port.

### 4.7.1 Supply Terminal Specifications

There are four supply pins to attach to DC power sources: VDD\_PA, VDD\_RF, VDD\_D and VDD\_IO.

Please refer to the section on 4.2 Operating Conditions for details on allowed voltages on these pins.

### 4.7.2 Digital I/O Terminal Specifications

Table 4.9. Digital I/O Terminal Specifications

| Parameter                                                    | Symbol            | Test Condition                              | Min | Тур | Max | Unit |

|--------------------------------------------------------------|-------------------|---------------------------------------------|-----|-----|-----|------|

| Voltage input low (relative to V <sub>VDD_IO</sub> )         | V <sub>IL</sub>   |                                             | _   | _   | 30  | %    |

| Voltage input high (relative to V <sub>VDD_IO</sub> )        | V <sub>IH</sub>   |                                             | 70  | _   | _   | %    |

| Logic low output voltage (relative to V <sub>VDD_IO</sub> )  | V <sub>OL</sub>   | Sinking 5 mA, V <sub>VDD_IO</sub> ≥ 1.62 V  |     | _   | 25  | %    |

| Logic high output voltage (relative to V <sub>VDD_IO</sub> ) | V <sub>OH</sub>   | Sourcing 5 mA, V <sub>VDD_IO</sub> ≥ 1.62 V | 80  | _   | _   | %    |

| Input leakage current                                        | I <sub>Leak</sub> |                                             | _   | 1   | _   | nA   |

| Pullup resistance                                            | R <sub>PU</sub>   |                                             | 30  | 43  | 65  | kΩ   |

| Pulldown resistance <sup>1</sup>                             | R <sub>PD</sub>   |                                             | 30  | 43  | 65  | kΩ   |

| Output fall time from $V_{OH}$ to $V_{OL}$                   | T <sub>OF</sub>   | 50 pF load, V <sub>VDD_IO</sub> = 1.62 V    | _   | 15  | _   | ns   |

| Output rise time from $V_{OL}$ to $V_{OH}$                   | T <sub>OR</sub>   | 50 pF load, V <sub>VDD_IO</sub> = 1.62 V    | _   | 15  | _   | ns   |

|                                                              |                   | ·                                           |     |     |     |      |

### Note:

### 4.8 Host Interface

The host interface allows control of WF200 by an MCU or SoC using either SPI or SDIO. Selection between SPI and SDIO is done upon the logic state on SDIO\_DAT2/HIF\_SEL pin during the rising edge of RESETn signal. If this signal is HIGH, the host interface is configured as SDIO, otherwise it is configured as SPI. The tables below summarizes the pin configurations for the two modes and the achievable speeds on both interfaces

Table 4.10. WF200 SPI and SDIO interface pin configuration

| WF200 Pin Name    | SPI Mode |          | SDIO   | Mode      |

|-------------------|----------|----------|--------|-----------|

| RESETn            | 0 -> 1   | 1        | 0 -> 1 | 1         |

| SDIO_DAT2/HIF_SEL | 0        | x        | 1      | SDIO_DAT2 |

| SDIO_CLK/SPI_CLK  | x        | SPI_CLK  | x      | SDIO_CLK  |

| SDIO_CMD/SPI_MOSI | x        | SPI_MOSI | x      | SDIO_CMD  |

<sup>1.</sup> RESETn pin has only pull-up resistance.

| WF200 Pin Name     | SPI Mode |                                     | SDIO | Mode      |

|--------------------|----------|-------------------------------------|------|-----------|

| SDIO_DAT0/SPI_MISO | x        | SPI_MISO                            | х    | SDIO_DAT0 |

| SDIO_DAT1/SPI_WIRQ | x        | WIRQ                                | x    | SDIO_DAT1 |

|                    |          | (interrupt request to the SPI host) |      |           |

| SDIO_DAT3/SPI_CSn  | x        | SPI_CSn                             | х    | SDIO_DAT3 |

Table 4.11. Host Interface Speeds

| Parameter            | Symbol              | Test Condition              | Min | Тур | Max | Unit |

|----------------------|---------------------|-----------------------------|-----|-----|-----|------|

| SDIO V2.0 clock rate | SD <sub>Rate</sub>  | Host Interface SDIO DS Mode | _   | _   | 26  | MHz  |

|                      |                     | Host Interface SDIO HS Mode | _   | _   | 52  | MHz  |

| SPI clock rate       | SPI <sub>Rate</sub> | Host Interface SPI          | _   | _   | 52  | MHz  |

Besides the main host interface signals, a couple of other pins also complement the host interface. See AN1219 for more details:

- The GPIO/WUP pin should be used by the host to wake up the WF200 when in power-save mode. This pin is programmable and if power save is not enabled on the device, this pin can be configured as a GPIO. Note that this pin should be LOW to enable the WF200 to reach sleep or shutdown modes.

- GPIO/WIRQ can also optionally be used as a duplication of the IRQ signal from SPI or SDIO. If this is not required, the pin can be configured as a GPIO.

# 4.8.1 SPI Specification

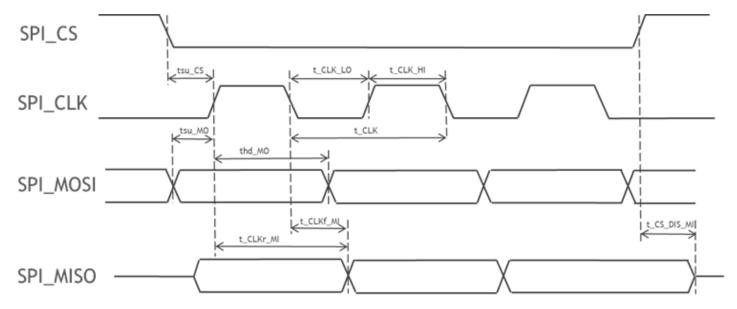

Figure 4.1. SPI Interface Timing Parameters

Table 4.12. SPI Interface Timing Specifications

| Symbol                                      | Description                                  | Min.               | Тур. | Max. | Unit |

|---------------------------------------------|----------------------------------------------|--------------------|------|------|------|

| t <sub>CLK</sub>                            | Clock period                                 | 19.23 <sup>1</sup> |      |      | ns   |

| t <sub>CLK_HI</sub>                         | Clock high                                   | 9                  |      |      | ns   |

| t <sub>CLK_LO</sub>                         | Clock low                                    | 9                  |      |      | ns   |

| tcs_dis_mi                                  | CS disable to MISO. VDD <sub>IO</sub> = 3.3V |                    |      | 8    | ns   |

|                                             | CS disable to MISO. VDD <sub>IO</sub> = 1.8V |                    |      | 10   | ns   |

| t <sub>su_cs</sub>                          | CS setup time                                | 3                  |      |      | ns   |

| t <sub>SU_MO</sub>                          | MOSI setup time                              | 3                  |      |      | ns   |

| t <sub>HD_MO</sub>                          | MOSI hold time                               | 3                  |      |      | ns   |

| t <sub>CLKr_MI</sub> , t <sub>CLKf_MI</sub> | CLK to MISO out; VDD <sub>IO</sub> = 3.3V    |                    |      | 10   | ns   |

|                                             | CLK to MISO out; VDD <sub>IO</sub> = 1.8V    |                    |      | 21   | ns   |

### Note:

- 1.19.23 ns = 1/52 MHz

- 2. MISO can optionally be latched either on rising edge or falling edge of CLK

- 3. All timing parameters valid for output load up to 2 mA

# 4.8.2 SDIO Specification

Figure 4.2. SDIO Interface Timing Parameters

**Table 4.13. SDIO Interface Timing Specifications**

| Symbol                                             | Description                                                            | Min   | Тур | Max | Unit | Conditions                            |

|----------------------------------------------------|------------------------------------------------------------------------|-------|-----|-----|------|---------------------------------------|

| t <sub>CLK_HS</sub>                                | Clock period in high speed mode                                        | 19.23 |     |     | ns   | CL ≤ 20pF                             |

| t <sub>CLK_DS</sub>                                | Clock period in default speed mode                                     | 38.46 |     |     | ns   | CL ≤ 20pF                             |

| t <sub>CLK_LO</sub>                                | Clock low time                                                         | 9     |     |     | ns   | CL≤ 20pF                              |

| t <sub>CLK_HI</sub>                                | Clock high time                                                        | 9     |     |     | ns   | CL≤ 20pF                              |

| CMD, DAT0                                          | -3 Inputs (with reference to SDIO_CL                                   | ()    |     |     |      |                                       |

| t <sub>SU</sub>                                    | Input Set time                                                         | 3     |     |     | ns   | CL≤ 20pF                              |

| t <sub>HD</sub>                                    | Input Hold time                                                        | 3     |     |     | ns   | CL≤ 20pF                              |

| CMD, DAT0                                          | ~3 Outputs (with reference to SDIO_C                                   | LK)   |     |     |      |                                       |

| t <sub>ODLY_CLKr</sub> ,<br>t <sub>ODLY_CLKf</sub> | Output delay time (relative to rising and falling edge) for VDD = 3.3V |       |     | 11  | ns   | VDD <sub>IO</sub> = 3.3V;<br>CL≤ 20pF |

|                                                    | Output delay time (relative to rising and falling edge) for VDD = 1.8V |       |     | 22  | ns   | VDD <sub>IO</sub> = 1.8V;<br>CL≤ 20pF |

| t <sub>OH</sub>                                    | Output Hold time                                                       | 3     |     |     | ns   | CL≤ 20pF                              |

<sup>1.</sup> Output data can be latched either on rising edge (HS mode) or falling edge (DS mode) of CLK

<sup>2.</sup> All timing parameters valid for output load of up to 2 mA

# 5. Typical Applications and Connections

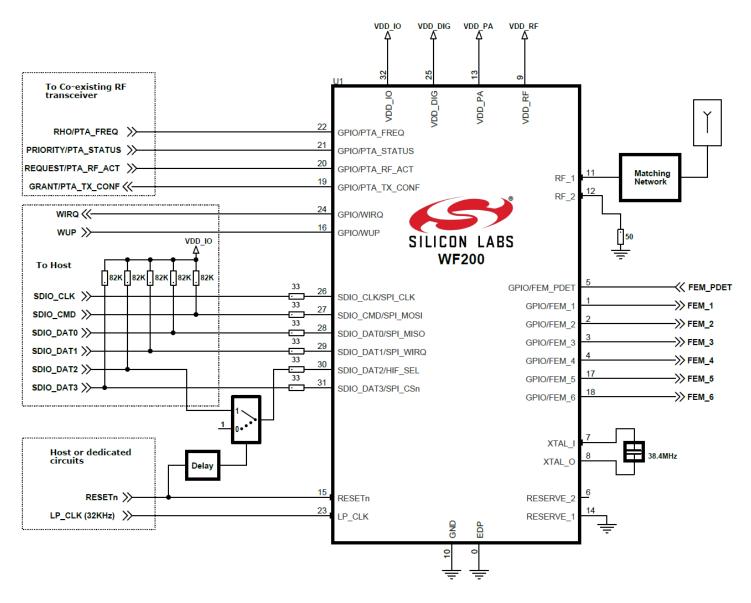

### 5.1 Typical Application Circuit for SDIO Host Interface

Figure 5.1. Typical Application Circuit SDIO Host Interface

### Note:

- The SDIO pin pullup resistors are only required if the Host does not integrate internal pull-ups on SDIO signals as required by the SDIO standard.

- Refer to UG382: WF200 Hardware Design User's Guide for more details on the application circuit.

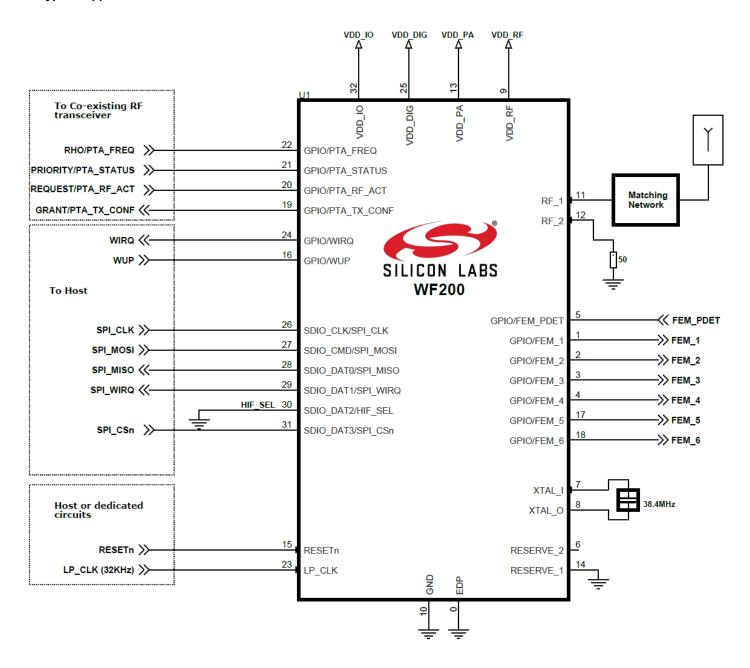

### 5.2 Typical Application Circuit for SPI Host Interface

Figure 5.2. Typical Application Circuit SPI Host Interface

### Note:

• Refer to UG382: WF200 Hardware Design User's Guide for more details on the application circuit.

### 5.3 Power States and Low-Power Modes

The current consumption on WF200 is highly dynamic. It varies significantly depending on its activity, the activation of power-save modes, and when it is in shutdown.

There are four main modes, each of them having several power states as detailed below.

**Traffic mode**: The Traffic mode is defined as the mode when WF200 is transmitting data, receiving data, or listening to the channel. If power save is not activated, the device stays in listen mode when there is no traffic. Current consumption is similar between receive and listen modes, while it is higher during transmission.

**Power save modes**: When power save mode is activated, the device goes to a low-consumption mode and wakes-up periodically to listen to network beacons, so the device stays associated to the network. The current consumption, while receiving beacons, is as mentioned above for reception.

There are three power-save/low-power consumption cases:

- 1. Sleep: If a 32 KHz clock is available at LP\_CLK input, then the device goes in sleep mode between reception of beacons. In this mode, most of the chip is turned off (including Xtal oscillator and host interface) to reduce the power consumption as much as possible. Given that the host interface is shut down in this mode, the host should assert the WUP pin to wake up the device before any communication with the host can be achieved.

- 2. Sleep with XO on: If low-power clock is not available on LP\_CLK or if the Xtal oscillator cannot be shut down if the Xtal is shared, then the device goes in "Sleep with XO on" mode between reception of beacons. In this mode, the Xtal oscillator is active, so the typical consumption is higher.

- 3. Snooze: If low-power clock is not available on LP\_CLK then the device goes in snooze mode between reception of beacons. In this mode, a smaller part of the device is shut down and the XO is always enabled, so the typical consumption is higher.

The sleep or snooze state/mode can also be achieved when not associated if the firmware decides there are no tasks to perform when the wake-up signal (pin GPIO/WUP) from host is low.

**Shutdown mode:** Shutdown mode is the case where the transceiver is shut down and reaches the lowest power consumption while still being connected to the power supplies. Getting out of stand-by requires a complete start-up sequence triggered by RESETn pin being set from low to high.

Reset mode: When RESETn is low, the consumption is typically 76 μA, mainly due to the RESETn pull-up resistor within the device.

### 5.4 RF Connections

### 5.4.1 Antenna Ports

This device has two RF ports to allow antenna diversity using an internal switch. In applications with only one antenna, the un-used port should be terminated to ground through a resistor between 47 to 51 Ohm. In applications desiring to use a Front End Module (FEM), one of these ports could be used for Transmit, and the other RF Port for Receive.

### 5.4.2 Antenna Diversity

In Applications where the main antenna is subject to obstruction or de-tuning, a second antenna can be used at the alternate antenna port by using the switched antenna diversity report. The location of this second antenna should be such that both cannot be prevented from operating satisfactorily by the same event. A firmware feature can be invoked to determine which antenna has a better path to the remote WiFi Device.

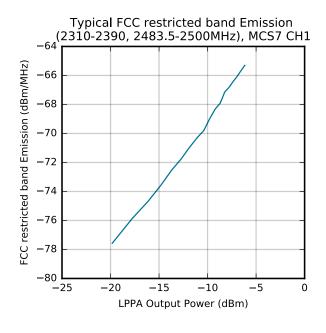

### 5.4.3 FEM Support

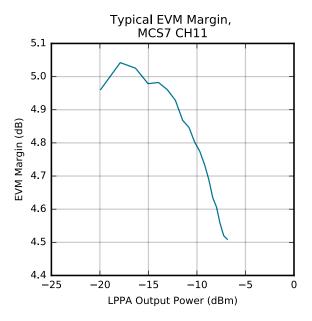

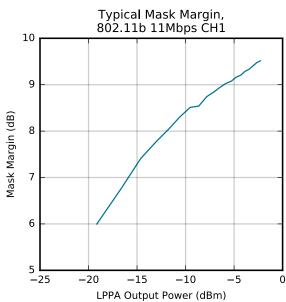

WF200 supports the use of an external Front End Module (FEM) for customers desiring higher output power than what is provided by the built-in RF front end inside WF200. The device has a low power PA that can be used to drive an external FEM. The following plots can be used to help configure the FEM power levels and settings so that the system has adequate margin to EVM, FCC restricted band emission and mask margin.

Figure 5.3. Low Power PA Emissions and Margin

### 5.5 Clocks

### 5.5.1 XTAL I and XTAL O connections for Crystal

Connect the signal pins of a 38.4MHz crystal to the XTAL\_O and XTAL\_I pins with very short traces. These traces on the PCB should have short length, and minimal parasitic load. There is normally no need for external parallel capacitors because this IC includes internal load capacitors which have programmable values. The value of these load capacitors will have to be determined which center the operating frequency for the design of the crystal and PCB. This value will have to be included in firmware. Firmware will program the prescribe load capacitance prior to startup, and the value should not change during operation. See UG382: WF200 Hardware Design Users Guide for more details of the crystal connections to this IC.

### 5.5.2 XTAL\_I and XTAL\_O connections for TCXO

When using a TCXO to provide 38.4MHz clock input, a series 1000pF capacitor is required between the TCXO output pin and XTAL\_I pin to block DC. The XTAL\_O pin can be left unconnected.

### 5.5.3 LP\_CLK Port

A 32.768KHz clock source should be supplied to LP\_CLK pin to enable the lowest power operation in power save modes. The frequency tolerance of this source affects wake up scheduling.

### 5.6 Multi-Protocol Coexistence

In case an RF transceiver using the same 2.4 GHz band (e.g. Bluetooth, Zigbee, or Thread) is co-located with the WF200 Wi-Fi transceiver, the Packet Traffic Arbitration (PTA) interface can be used to minimize mutual interference. In this case, PTA pins are connected to the other transceiver. The PTA interface is highly programmable and can use 1, 2, 3, or 4 pins upon configuration. WF200 embeds a Packet Traffic Arbitration block in order to share the access to the RF medium between WLAN and another standard.

Depending on manufacturer, PTA signal names can vary and the table below shows some alternative naming:

**Table 5.1. PTA Alternative Naming**

| WF200 Pin Name | Alternative Names         |

|----------------|---------------------------|

| PTA_TX_CONF    | GRANT, WL_ACTIVE, WL_DENY |

| PTA_RF_ACT     | REQUEST, BT_ACTIVE        |

| PTA_STATUS     | PRIORITY, BT_STATUS       |

| PTA_FREQ       | FREQ, BT_FREQ             |

PTA interface configuration is also achieved via the configuration file.

See https://docs.silabs.com/wifi/wf200/additional-resources#documentation for more information regarding PTA and coexistence management on WF200, as well as AN1017 and AN1128 for EFR32BGx and EFR32MGx devices supporting BLE, Zigbee, and Thread.

# 6. Pin Descriptions

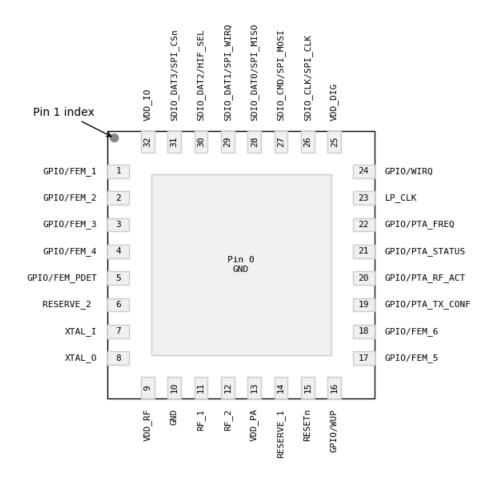

Figure 6.1. WF200 Pinout

Table 6.1. Pin Definitions

| Pin # | Pin Name      | I/O | Description / Default                                                                                                                                                                    |

|-------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GPIO/FEM_1    | I/O | This pin can be used for dynamic control of an external front-end module (FEM), otherwise this can be used as GPIO.                                                                      |

| 2     | GPIO/FEM_2    | I/O | This pin can be used for dynamic control of an external front-end module (FEM), otherwise this can be used as GPIO.                                                                      |

| 3     | GPIO/FEM_3    | I/O | This pin can be used for dynamic control of an external front-end module (FEM), otherwise this can be used as GPIO.                                                                      |

| 4     | GPIO/FEM_4    | I/O | This pin can be used for dynamic control of an external Power amplifier detector output (Vdet) in case an external power amplifier or a FEM is used. Otherwise this can be used as GPIO. |

| 5     | GPIO/FEM_PDET | I/O | Programmable Pins / FEM Power detector Interface                                                                                                                                         |

| 6     | RESERVE_2     | I/O | Reserved. This pin should be left unconnected.                                                                                                                                           |

| 7     | XTAL_I        | I   | Crystal pin 1 (or reference clock input if driven by TCXO)                                                                                                                               |

| 8     | XTAL_O        | 0   | Crystal pin 2 (leave floating if XTAL_I driven by TCXO)                                                                                                                                  |

| 9     | VDD_RF        | I   | RF power supply                                                                                                                                                                          |

| Pin# | Pin Name             | I/O | Description / Default                                                                                                                                                                 |  |

|------|----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 10   | GND                  | GND | Ground                                                                                                                                                                                |  |

| 11   | RF_1                 | I/O | RF Port 1 to connect to main antenna                                                                                                                                                  |  |

| 12   | RF_2                 | I/O | RF Port 2 to connect to diversity antenna                                                                                                                                             |  |

| 13   | VDD_PA               | I   | PA Power Supply                                                                                                                                                                       |  |

| 14   | RESERVE_1            | GND | Reserved. For normal operation, this pin must be grounded                                                                                                                             |  |

| 15   | RESETn               | I   | Reset pin, active low                                                                                                                                                                 |  |

| 16   | GPIO/WUP             | I/O | This pin can be used to wake up the device from sleep mode, or used as a GPIO                                                                                                         |  |

| 17   | GPIO/FEM_5           | I/O | This pin can be used to dynamically control an external front-end module (FEM), otherwise this can be used as GPIO.                                                                   |  |

| 18   | GPIO/FEM_6           | I/O | This pin can be used to dynamically control an external front-end module (FEM), otherwise this can be used as GPIO.                                                                   |  |

| 19   | GPIO/PTA_TX_CONF     | I/O | As part of PTA interface, this pin can be used to manage co-existence with another 2.4 GHz radio or can be used as a GPIO                                                             |  |

| 20   | GPIO/PTA_RF_ACT      | I/O | As part of PTA interface, this pin can be used to manage co-existence with another 2.4 GHz radio or can be used as a GPIO                                                             |  |

| 21   | GPIO/PTA_STATUS      | I/O | As part of PTA interface, this pin can be used to manage co-existence with another 2.4 GHz radio or can be used as a GPIO                                                             |  |

| 22   | GPIO/PTA_FREQ        | I/O | As part of PTA interface, this pin can be used to manage co-existence with another 2.4 GHz radio or can be used as a GPIO                                                             |  |

| 23   | GPIO/LP_CLK          | I   | Low Power clock input. This pin is typically connected to the 32 KHz reference clock.                                                                                                 |  |

| 24   | GPIO/WIRQ            | I/O | In SDIO mode, this pin is an interrupt pin from WF200 to host to indicate a message or data should be read. In SPI mode, this pin can be used as a GPIO.                              |  |

| 25   | VDD_DIG              | I   | Digital Power Supply. Identical to VDD_D                                                                                                                                              |  |

| 26   | SDIO_CLK/ SPI_CLK    | I   | Host interface: SDIO_CLK or SPI_CLK                                                                                                                                                   |  |

| 27   | SDIO_CMD/ SPI_MOSI   | I/O | Host interface: SDIO_CMD or SPI_MOSI                                                                                                                                                  |  |

| 28   | SDIO_DAT0/ SPI_MISO  | I/O | Host interface: SDIO_DAT0 or SPI_MISO                                                                                                                                                 |  |

| 29   | SDIO_DAT1 / SPI_WIRQ | I/O | Host interface: SDIO_DAT1 or WIRQ                                                                                                                                                     |  |

| 30   | SDIO_DAT2/ HIF_SEL   | I/O | Host interface selection: Used to select the host interface during reset rising edge. If Low, selects SPI interface. When High, selects SDIO interface and this pin becomes SDIO_DAT2 |  |

| 31   | SDIO_DAT3/ SPI_CSn   | I/O | Host interface: SDIO_DAT3 or SPI_CSn                                                                                                                                                  |  |

| 32   | VDD_IO               | I   | IO Power Supply                                                                                                                                                                       |  |

| 0    | GND                  | GND | Exposed Die Pad                                                                                                                                                                       |  |

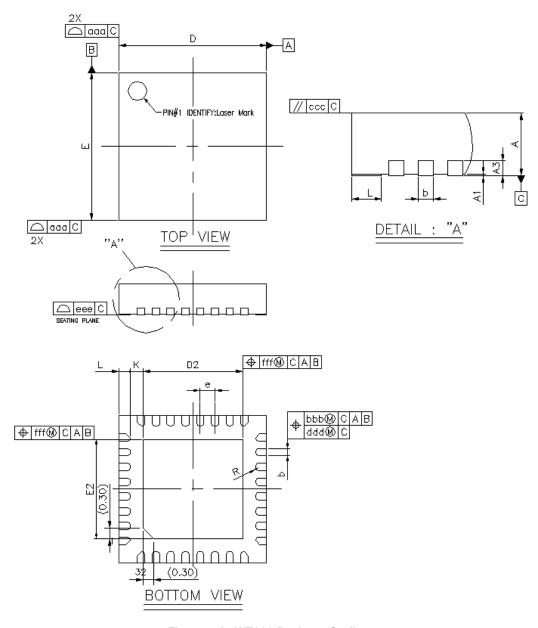

# 7. Package Outline

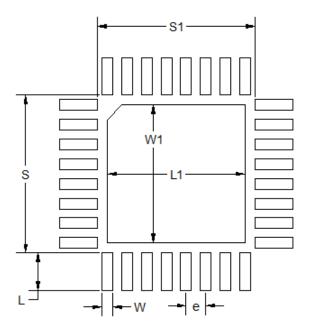

Figure 7.1. WF200 Package Outline

Table 7.1. WF200 Package Diagram Dimensions

| Dimension | MIN      |          | NOM      |       | MAX  |

|-----------|----------|----------|----------|-------|------|

| Α         | 0.80     |          | 0.85     |       | 0.90 |

| A1        | A1 0.00  |          | 0.02     |       | 0.05 |

| A3        | 0.20 REF |          |          |       |      |

| b         | 0.15     |          | 0.20     |       | 0.25 |

| D         | 3.90     |          | 4.00     |       | 4.10 |

| E         | 3.90     |          | 4.00     |       | 4.10 |

| D2        | 2.60     |          | 2.70     |       | 2.80 |

| E2        | 2.60     |          | 2.70     |       | 2.80 |

| е         |          | 0.40 BSC |          |       |      |

| L         | 0.20     | 0.       | 0.30 0.4 |       | 40   |

| K         | 0.20     |          |          |       |      |

| R         | 0.075    |          |          | 0.125 |      |

| aaa       | 0.10     |          |          |       |      |

| bbb       | 0.07     |          |          |       |      |

| ccc       | 0.10     |          |          |       |      |

| ddd       | 0.05     |          |          |       |      |

| eee       | 0.08     |          |          |       |      |

| fff       | 0.10     |          |          |       |      |

### 8. Land Pattern

Figure 8.1. WF200 Land Pattern

| Dimension | mm   |

|-----------|------|

| L         | 0.76 |

| W         | 0.22 |

| е         | 0.40 |

| S         | 3.21 |

| S1        | 3.21 |

| L1        | 2.80 |

| W1        | 2.80 |

### **General**

- · All dimensions shown are in millimeters (mm) unless otherwise noted.

- · This land pattern design is based on the IPC-7351 guidelines.

### Solder Mask Design

• All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

### **Stencil Design**

- A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- The stencil thickness should be 0.101mm (4 mils).

- The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- A 2x2 array of 1.10mm x 1.10mm openings on 1.30mm pitch should be used for the center ground pad.

### Card Assembly

- A No-Clean, Type-3 solder paste is recommended.

- The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

**Note:** Above notes and stencil design are shared as recommendations only. A customer or user may find it necessary to use different parameters and fine tune their SMT process as required for their application and tooling.

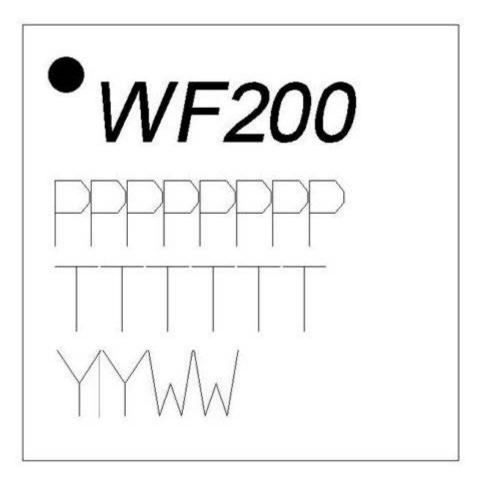

# 9. Top Marking

Figure 9.1. WF200 Top Marking

Table 9.1. Top Marking for WF200

| OPN                             | РРРРРРР | ттттт |

|---------------------------------|---------|-------|

| WF200SD                         | SD      |       |

| WF200D                          | D       |       |

| Note: YY = Year. WW = Work Week |         |       |

### 10. Software Reference

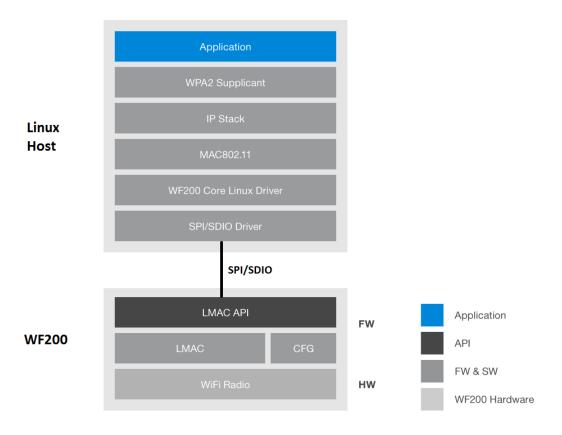

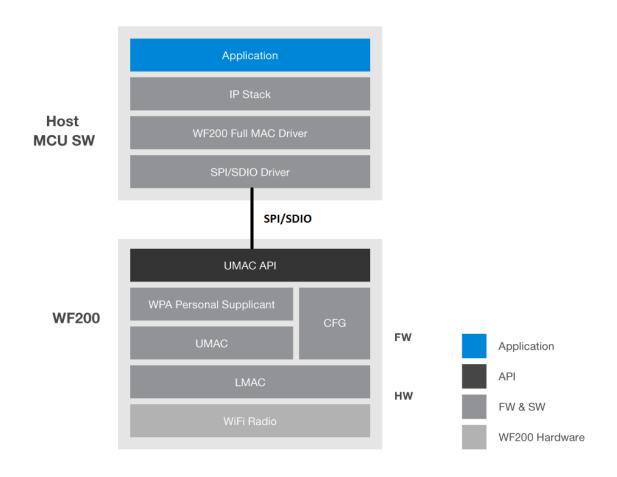

This section gives a short overview of the software involved to run applications based on this device. The firmware running in the WF200 allows it to be used at Lower MAC level (in split MAC) or at the Upper Mac level (in Full MAC).

### 10.1 Host and Device Software

This device is intended to be used as a Network Co-Processor (NCP) which means that it requires a host processor to run the application. Depending on architecture choices based on required throughput, host memory size and power, the MAC layer can be split between WF200 and its host or fully ran in WF200.

### 10.1.1 Split MAC